Professional Documents

Culture Documents

Ieee IEEE - STD - LOGIC - 1164 Ieee - STD - Logic - Arith Ieee - STD - Logic - Unsigned STD - Logic STD - Logic STD - Logic STD - Logic

Ieee IEEE - STD - LOGIC - 1164 Ieee - STD - Logic - Arith Ieee - STD - Logic - Unsigned STD - Logic STD - Logic STD - Logic STD - Logic

Uploaded by

Bisz BetaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ieee IEEE - STD - LOGIC - 1164 Ieee - STD - Logic - Arith Ieee - STD - Logic - Unsigned STD - Logic STD - Logic STD - Logic STD - Logic

Ieee IEEE - STD - LOGIC - 1164 Ieee - STD - Logic - Arith Ieee - STD - Logic - Unsigned STD - Logic STD - Logic STD - Logic STD - Logic

Uploaded by

Bisz BetaCopyright:

Available Formats

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity motores is

Port ( a,b,c,d : in STD_LOGIC;

w,x,y,z : out STD_LOGIC);

end motores;

architecture structural of motores is

signal n1,n2 : std_logic;

----------------------------------------------------------declaro compuerta

-----------------------------------------------------component and_2

port (f,g: in std_logic;

j: out std_logic);

end component;

---------------------------------------------------declaro compuerta

-------------------------------------------------component and_3

port (f,g,h: in std_logic;

j: out std_logic);

end component;

---------------------------------------------------declaro compuerta

-------------------------------------------------component or_2

port (f,g: in std_logic;

j: out std_logic);

end component;

-------------------------------------------------declaro las entradas y salidas para cada

caso

---------------------------------------------begin

U0:and_3 port map (a,b,(not d),w);

U1:and_3 port map (a,b,(not d),x);

U2:and_2 port map (c,(not d),y);

U3:and_3 port map ((not a),(not c),d,n1);

U4:and_3 port map ((not b),(not c),d,n2);

U5:or_2 port map (n1,n2,z)

end structural;

Despus de haber sintetizado cada compuerta me dirijo al link:

Asigno pines y sintetizo el proyecto

You might also like

- SR - To - T Flip Flop Conversion VHDL CodeDocument2 pagesSR - To - T Flip Flop Conversion VHDL CodeOP2RNo ratings yet

- J-K - To - D Flip-Flop Conversion VHDL CodeDocument2 pagesJ-K - To - D Flip-Flop Conversion VHDL CodeOP2RNo ratings yet

- Pedroni MITPress 1stedition SolutionSamplesDocument14 pagesPedroni MITPress 1stedition SolutionSamplesTrần Anh DũngNo ratings yet

- Half Subtractor VHDL Code Using Structrucral ModelingDocument2 pagesHalf Subtractor VHDL Code Using Structrucral ModelingOP2R0% (3)

- Half Adder VHDL Code Using Structrucral ModelingDocument1 pageHalf Adder VHDL Code Using Structrucral ModelingOP2R100% (2)

- New Microsoft Word DocumentDocument15 pagesNew Microsoft Word DocumentVijay NadimpalliNo ratings yet

- Full Adder VHDL Code Using Structural ModelingDocument2 pagesFull Adder VHDL Code Using Structural ModelingOP2R91% (11)

- 1's Complement VHDL Code Using Structrucral ModelingDocument1 page1's Complement VHDL Code Using Structrucral ModelingOP2RNo ratings yet

- 1's Complement VHDL Code Using Dataflow ModelingDocument1 page1's Complement VHDL Code Using Dataflow ModelingOP2RNo ratings yet

- DDL Codes LabsDocument31 pagesDDL Codes LabssaimNo ratings yet

- NAND Gate Beh - ModelingDocument1 pageNAND Gate Beh - ModelingOP2RNo ratings yet

- Decoder VHDL Code Using Behavioural Flow ModelingDocument1 pageDecoder VHDL Code Using Behavioural Flow ModelingOP2RNo ratings yet

- And Gate Beh - ModelingDocument1 pageAnd Gate Beh - ModelingOP2RNo ratings yet

- Full Subtractor VHDL Code Using Structural ModelingDocument2 pagesFull Subtractor VHDL Code Using Structural ModelingOP2RNo ratings yet

- VHDL - Lab SolutionDocument33 pagesVHDL - Lab Solutionmdhuq1No ratings yet

- 2's Complement VHDL Code Using Structrucral ModelingDocument2 pages2's Complement VHDL Code Using Structrucral ModelingOP2RNo ratings yet

- Half Subtractor VHDL Code Using Dataflow ModelingDocument1 pageHalf Subtractor VHDL Code Using Dataflow ModelingOP2RNo ratings yet

- Full Subtractor VHDL Code Using Data Flow ModelingDocument1 pageFull Subtractor VHDL Code Using Data Flow ModelingOP2R100% (1)

- VHDL ProgDocument52 pagesVHDL Progરાહુલ મેહ્તાNo ratings yet

- Half Adder VHDL Code Using Dataflow ModelingDocument1 pageHalf Adder VHDL Code Using Dataflow ModelingOP2RNo ratings yet

- Half Subtractor VHDL Code Using Behavioural ModelingDocument1 pageHalf Subtractor VHDL Code Using Behavioural ModelingOP2RNo ratings yet

- Untitled DocumentDocument4 pagesUntitled Documentkatuwalnawaraj76No ratings yet

- Demux VHDL Code Using Behavioural ModelingDocument1 pageDemux VHDL Code Using Behavioural ModelingOP2RNo ratings yet

- Half Adder VHDL Code Using Behavioural ModelingDocument1 pageHalf Adder VHDL Code Using Behavioural ModelingOP2R100% (5)

- Xnor Gate Beha - ModelingDocument1 pageXnor Gate Beha - ModelingOP2RNo ratings yet

- T Flip-Flop VHDL Code Using Behavioural ModelingDocument2 pagesT Flip-Flop VHDL Code Using Behavioural ModelingOP2R100% (1)

- Full Adder VHDL Code Using Data Flow ModelingDocument1 pageFull Adder VHDL Code Using Data Flow ModelingOP2RNo ratings yet

- 2's Complement VHDL Code Using Data Flow ModelingDocument1 page2's Complement VHDL Code Using Data Flow ModelingOP2R67% (3)

- Untitled DocumentDocument3 pagesUntitled Documentkatuwalnawaraj76No ratings yet

- 1.1) Design All Basic Gates and Simulate ThemDocument10 pages1.1) Design All Basic Gates and Simulate ThemShalin DoshiNo ratings yet

- Department of Electronics and Communication Software Are Lab-II-Hardware Description Languages (EC-506)Document17 pagesDepartment of Electronics and Communication Software Are Lab-II-Hardware Description Languages (EC-506)Usha PandeyNo ratings yet

- NOR Gate Beha - ModelingDocument1 pageNOR Gate Beha - ModelingOP2RNo ratings yet

- D - To - J-K Flip Flop Conversion VHDL CodeDocument2 pagesD - To - J-K Flip Flop Conversion VHDL CodeOP2RNo ratings yet

- ArithmaticDocument2 pagesArithmaticMiraz AhmedNo ratings yet

- Adder CompoDocument4 pagesAdder Compobhslegion1498No ratings yet

- Ripple Carry Adder VHDL Code Using Structural ModellingDocument1 pageRipple Carry Adder VHDL Code Using Structural ModellingOP2R0% (1)

- td2 2022Document5 pagestd2 2022hamidadaoudi2000No ratings yet

- D Flip Flop - Structural ModelingDocument2 pagesD Flip Flop - Structural ModelingOP2RNo ratings yet

- LabDocument4 pagesLabSouvik PalNo ratings yet

- AbedDocument3 pagesAbedAbed Abu SdamNo ratings yet

- D - To - S-R Flip-Flop Conversion VHDL CodeDocument1 pageD - To - S-R Flip-Flop Conversion VHDL CodeOP2RNo ratings yet

- AbedDocument3 pagesAbedAbed Abu SdamNo ratings yet

- OR Gate Beha - ModelingDocument1 pageOR Gate Beha - ModelingOP2RNo ratings yet

- Sop - Form STD - Logic STD - Logic Sop - Form Arch Sop - FormDocument4 pagesSop - Form STD - Logic STD - Logic Sop - Form Arch Sop - FormKshitij GurjarNo ratings yet

- Configuracion de La PlataformaDocument12 pagesConfiguracion de La PlataformaJose Mauricio Pulgarin LoteroNo ratings yet

- SR - To - JK Flip Flop Conversion VHDL CodeDocument2 pagesSR - To - JK Flip Flop Conversion VHDL CodeOP2RNo ratings yet

- Verification of and GateDocument7 pagesVerification of and Gatesiddhant5031No ratings yet

- Solucionario MT 127 Sustitutorio 2019 3Document15 pagesSolucionario MT 127 Sustitutorio 2019 3Abdigal Gabriel Camargo BarraNo ratings yet

- 3 Program CodeDocument15 pages3 Program Codergkusumba100% (1)

- Comparative Analysis of Low Power 4-Bit Multipliers Using 120nm CMOS TechnologyDocument28 pagesComparative Analysis of Low Power 4-Bit Multipliers Using 120nm CMOS TechnologyRevanth DondapatiNo ratings yet

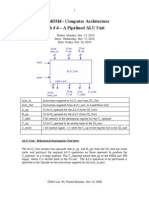

- ECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitDocument8 pagesECE 4DM4 - Computer Architecture Lab # 4 - A Pipelined ALU UnitsantoshmphilNo ratings yet

- PIC Microcontroller, Timer0, Hello World, PIC16F1823Document3 pagesPIC Microcontroller, Timer0, Hello World, PIC16F1823Nolan Manteufel100% (3)

- Xor Gate Beha - ModelingDocument1 pageXor Gate Beha - ModelingOP2RNo ratings yet

- FFTDocument40 pagesFFTsreekuttymsNo ratings yet

- Component, Package, Function & ProcedureDocument12 pagesComponent, Package, Function & ProcedureAmmar AlkindyNo ratings yet

- Verilog CodesDocument4 pagesVerilog CodesHusnain AliNo ratings yet

- Codigo Compuerta andDocument4 pagesCodigo Compuerta andjustjuank2010No ratings yet

- 1.logic Gates: OR GateDocument70 pages1.logic Gates: OR GateDinesh SharmaNo ratings yet

- SynthesisDocument5 pagesSynthesisTej CharanNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet