Professional Documents

Culture Documents

74 Ls 390

74 Ls 390

Uploaded by

Yoga AdiCopyright:

Available Formats

You might also like

- 74LS393-Dual 4-Bit Binary CounterDocument6 pages74LS393-Dual 4-Bit Binary Counterkakashi116No ratings yet

- DM7490A Decade and Binary Counters: General Description FeaturesDocument6 pagesDM7490A Decade and Binary Counters: General Description FeaturesamrspNo ratings yet

- DM 74 Ls 90Document6 pagesDM 74 Ls 90Clesio MichaelNo ratings yet

- Datasheet 74LS83Document6 pagesDatasheet 74LS83Álvaro PinedaNo ratings yet

- DM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesDocument5 pagesDM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesRoby Adi WibowoNo ratings yet

- 74LS73Document5 pages74LS73Cristin BarnesNo ratings yet

- DM74LS83A 4-Bit Binary Adder With Fast Carry: General Description FeaturesDocument6 pagesDM74LS83A 4-Bit Binary Adder With Fast Carry: General Description Featurescorpses88No ratings yet

- DM74LS393 Dual 4-Bit Binary Counter: General Description FeaturesDocument6 pagesDM74LS393 Dual 4-Bit Binary Counter: General Description Featuresjnax101No ratings yet

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNo ratings yet

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- 74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionMalik Mian Manzer MithaNo ratings yet

- DM74LS193 Synchronous 4-Bit Binary Counter With Dual Clock: General DescriptionDocument7 pagesDM74LS193 Synchronous 4-Bit Binary Counter With Dual Clock: General DescriptionsabarithasNo ratings yet

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002No ratings yet

- 74LS374Document8 pages74LS374Bechtel LanutanNo ratings yet

- 74ls193-Contador Binario de 4 BitsDocument8 pages74ls193-Contador Binario de 4 BitsEspartano HernándezNo ratings yet

- 74 Ls 175Document8 pages74 Ls 175AndrescronqueNo ratings yet

- 74LS574Document6 pages74LS574aminotepNo ratings yet

- DM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionDocument6 pagesDM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionNicolas Yesenia VictorNo ratings yet

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument8 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeatureshuvillamilNo ratings yet

- sn74138 PDFDocument7 pagessn74138 PDFdujobozinovicNo ratings yet

- 74LS245Document7 pages74LS245Francisco Raúl DelgadoNo ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDocument8 pagesMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuNo ratings yet

- 74LCX16245 Low Voltage 16-Bit Bidirectional Transceiver With 5V Tolerant Inputs and OutputsDocument9 pages74LCX16245 Low Voltage 16-Bit Bidirectional Transceiver With 5V Tolerant Inputs and Outputsmichaelliu123456No ratings yet

- DatasheetDocument8 pagesDatasheetMaizatul Hanisah RoziNo ratings yet

- Adc 0808Document14 pagesAdc 0808Vikas PatelNo ratings yet

- TC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderDocument9 pagesTC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderAndrea DispoNo ratings yet

- 74LS47 PDFDocument6 pages74LS47 PDFJhill-Jhill Jimenez Dela PeñaNo ratings yet

- 74ACT244Document9 pages74ACT244ThanhNo ratings yet

- CD4553 Datasheet OKDocument13 pagesCD4553 Datasheet OKCong ThoNo ratings yet

- y 74158Document9 pagesy 74158Roberto Kaled Silva ValdiviaNo ratings yet

- 74VHC14 Hex Schmitt Inverter: Features General DescriptionDocument8 pages74VHC14 Hex Schmitt Inverter: Features General DescriptionAriel NavarreteNo ratings yet

- 74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BDocument7 pages74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BRishabh PariharNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocument20 pagesADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982No ratings yet

- Datasheet - 74LS283 - Somador Binário Completo de 4 BitsDocument7 pagesDatasheet - 74LS283 - Somador Binário Completo de 4 BitsLucas CarvalhoNo ratings yet

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNo ratings yet

- 74LS86P PDFDocument6 pages74LS86P PDFOsman KoçakNo ratings yet

- 74LS75 PDFDocument4 pages74LS75 PDFDeni KhanNo ratings yet

- 74ls245 (3-State Octal Bus Transceiver)Document7 pages74ls245 (3-State Octal Bus Transceiver)thanhdang8xNo ratings yet

- DM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesDocument6 pagesDM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesNegru P. PlantatieNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Digital Signal Processing Using the ARM Cortex M4From EverandDigital Signal Processing Using the ARM Cortex M4Rating: 1 out of 5 stars1/5 (1)

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- 7 Types of AbnormalitiesDocument34 pages7 Types of AbnormalitiesYoga Adi100% (1)

- The New Standard To Analyse Risks Within The Automotive Supply ChainDocument8 pagesThe New Standard To Analyse Risks Within The Automotive Supply ChainYoga AdiNo ratings yet

- SCE en 030-020 R1209 Timers and CountersDocument41 pagesSCE en 030-020 R1209 Timers and CountersYoga AdiNo ratings yet

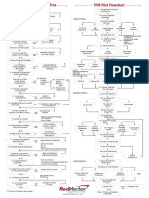

- TPM Chart PDFDocument1 pageTPM Chart PDFYoga AdiNo ratings yet

- SCE en 030-010 R1209 Block TypesDocument37 pagesSCE en 030-010 R1209 Block TypesYoga AdiNo ratings yet

- SCE en 030-010 R1209 Block TypesDocument37 pagesSCE en 030-010 R1209 Block TypesYoga AdiNo ratings yet

- SCE EN 020-011 R1404 Startup S7-1500 V13Document79 pagesSCE EN 020-011 R1404 Startup S7-1500 V13Yoga AdiNo ratings yet

74 Ls 390

74 Ls 390

Uploaded by

Yoga AdiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

74 Ls 390

74 Ls 390

Uploaded by

Yoga AdiCopyright:

Available Formats

DM74LS390 Dual 4-Bit Decade Counter

August 1986 Revised March 2000

DM74LS390 Dual 4-Bit Decade Counter

General Description

Each of these monolithic circuits contains eight masterslave flip-flops and additional gating to implement two individual four-bit counters in a single package. The DM74LS390 incorporates dual divide-by-two and divideby-five counters, which can be used to implement cycle lengths equal to any whole and/or cumulative multiples of 2 and/or 5 up to divide-by-100. When connected as a bi-quinary counter, the separate divide-by-two circuit can be used to provide symmetry (a square wave) at the final output stage. The DM74LS390 has parallel outputs from each counter stage so that any submultiple of the input count frequency is available for system-timing signals.

Features

s Dual version of the popular DM74LS90 s DM74LS390...individual clocks for A and B flip-flops provide dual 2 and 5 counters s Direct clear for each 4-bit counter s Dual 4-bit version can significantly improve system densities by reducing counter package count by 50% s Typical maximum count frequency...35 MHz s Buffered outputs reduce possibility of collector commutation

Ordering Code:

Order Number DM74LS390M DM74LS390N Package Number M16A N16E Package Description 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Connection Diagram

2000 Fairchild Semiconductor Corporation

DS006433

www.fairchildsemi.com

DM74LS390

Function Tables BCD Count Sequence

(Each Counter) (Note 1) Count 0 1 2 3 4 5 6 7 8 9

H = HIGH Level L = LOW Level Note 1: Output QA is connected to input B for BCD count. Note 2: Output QD is connected to input A for Bi-quinary count.

Bi-Quinary (5-2)

(Each Counter) (Note 2) Count 0 1 2 3 4 5 6 7 8 9 Outputs QA L L L L L H H H H H QD L L L L H L L L L H QC L L H H L L L H H L QB L H L H L L H L H L

Outputs QD L L L L L L L L H H QC L L L L H H H H L L QB L L H H L L H H L L QA L H L H L H L H L H

Logic Diagram

www.fairchildsemi.com

DM74LS390

Absolute Maximum Ratings(Note 3)

Supply Voltage Input Voltage Clear A or B Operating Free Air Temperature Range Storage Temperature Range 7V 5.5V 0C to +70C 65C to +150C 7V

Note 3: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions table will define the conditions for actual device operation.

Recommended Operating Conditions

Symbol VCC VIH VIL IOH IOL fCLK fCLK tW Supply Voltage HIGH Level Input Voltage LOW Level Input Voltage HIGH Level Output Current LOW Level Output Current Clock Frequency (Note 4) Clock Frequency (Note 5) Pulse Width (Note 4) A to QA B to QB A to QA B to QB A B Clear HIGH tREL TA Clear Release Time (Note 6)(Note 7) Free Air Operating Temperature 0 0 0 0 20 25 20 25 0 70 ns C ns Parameter Min 4.75 2 0.8 0.4 8 25 20 20 15 Nom 5 Max 5.25 Units V V V mA mA MHz MHz

Note 4: CL = 15 pF, RL = 2 k, TA = 25C and VCC = 5V. Note 5: CL = 50 pF, RL = 2 k, TA = 25C and VCC = 5V. Note 6: The symbol () indicates the falling edge of the clear pulse is used for reference. Note 7: TA = 25C and VCC = 5V.

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted) Symbol VI VOH VOL Parameter Input Clamp Voltage HIGH Level Output Voltage LOW Level Output Voltage II Input Current @ Max Input Voltage IIH HIGH Level Input Current IIL LOW Level Input Current IOS ICC Short Circuit Output Current Supply Current VCC = Max (Note 9) VCC = Max (Note 10) Conditions VCC = Min, II = 18 mA VCC = Min, IOH = Max VIL = Max, VIH = Min VCC = Min, IOL = Max VIL = Max, VIH = Min IOL = 4 mA, VCC = Min VCC = Max, VI = 7V VCC = Max VI = 5.5V VCC = Max VI = 2.7V VCC = Max, VI = 0.4V Clear A B Clear A B Clear A B 20 15 2.7 3.4 0.35 0.25 0.5 0.4 0.1 0.2 0.4 20 40 80 0.4 1.6 2.4 100 26 mA mA mA A mA Min Typ (Note 8) Max 1.5 Units V V

Note 8: All typicals are at VCC = 5V, TA = 25C. Note 9: Not more than one output should be shorted at a time, and the duration should not exceed one second. Note 10: ICC is measured with all outputs OPEN, both CLEAR inputs grounded following momentary connection to 4.5 and all other inputs grounded.

www.fairchildsemi.com

DM74LS390

Switching Characteristics

at VCC = 5V and TA = 25C RL = 2 k Symbol fMAX tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL tPLH tPHL tPHL Parameter Maximum Clock Frequency Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time LOW-to-HIGH Level Output Propagation Delay Time HIGH-to-LOW Level Output Propagation Delay Time HIGH-to-LOW Level Output From (Input) To (Output) A to QA B to QB A to QA A to QA A to QC A to QC B to QB B to QB B to QC B to QC B to QD B to QD Clear to Any Q CL = 15 pF Min 25 20 20 20 60 60 21 21 39 39 21 21 39 Max CL = 50 pF Min 20 15 24 30 81 81 27 33 51 54 27 33 45 Max MHz ns ns ns ns ns ns ns ns ns ns ns Units

www.fairchildsemi.com

DM74LS390

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow Package Number M16A

www.fairchildsemi.com

DM74LS390 Dual 4-Bit Decade Counter

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 6 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

www.fairchildsemi.com

You might also like

- 74LS393-Dual 4-Bit Binary CounterDocument6 pages74LS393-Dual 4-Bit Binary Counterkakashi116No ratings yet

- DM7490A Decade and Binary Counters: General Description FeaturesDocument6 pagesDM7490A Decade and Binary Counters: General Description FeaturesamrspNo ratings yet

- DM 74 Ls 90Document6 pagesDM 74 Ls 90Clesio MichaelNo ratings yet

- Datasheet 74LS83Document6 pagesDatasheet 74LS83Álvaro PinedaNo ratings yet

- DM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesDocument5 pagesDM74LS164 8-Bit Serial In/Parallel Out Shift Register: General Description FeaturesRoby Adi WibowoNo ratings yet

- 74LS73Document5 pages74LS73Cristin BarnesNo ratings yet

- DM74LS83A 4-Bit Binary Adder With Fast Carry: General Description FeaturesDocument6 pagesDM74LS83A 4-Bit Binary Adder With Fast Carry: General Description Featurescorpses88No ratings yet

- DM74LS393 Dual 4-Bit Binary Counter: General Description FeaturesDocument6 pagesDM74LS393 Dual 4-Bit Binary Counter: General Description Featuresjnax101No ratings yet

- MM74HC245A Octal 3-STATE Transceiver: General DescriptionDocument7 pagesMM74HC245A Octal 3-STATE Transceiver: General DescriptionMubarak CeNo ratings yet

- MC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738Document8 pagesMC74ACT564 Octal D Type Flip Flop With 3 State Outputs: PDIP 20 N Suffix CASE 738greentea601No ratings yet

- 74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionDocument9 pages74VHCT245A Octal Buffer/Line Driver With 3-STATE Outputs: Features General DescriptionMalik Mian Manzer MithaNo ratings yet

- DM74LS193 Synchronous 4-Bit Binary Counter With Dual Clock: General DescriptionDocument7 pagesDM74LS193 Synchronous 4-Bit Binary Counter With Dual Clock: General DescriptionsabarithasNo ratings yet

- Mid Semester 2012 TID203Document17 pagesMid Semester 2012 TID203peas002No ratings yet

- 74LS374Document8 pages74LS374Bechtel LanutanNo ratings yet

- 74ls193-Contador Binario de 4 BitsDocument8 pages74ls193-Contador Binario de 4 BitsEspartano HernándezNo ratings yet

- 74 Ls 175Document8 pages74 Ls 175AndrescronqueNo ratings yet

- 74LS574Document6 pages74LS574aminotepNo ratings yet

- DM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionDocument6 pagesDM74LS574 Octal D-Type Flip-Flop With 3-STATE Outputs: General DescriptionNicolas Yesenia VictorNo ratings yet

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument8 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeatureshuvillamilNo ratings yet

- sn74138 PDFDocument7 pagessn74138 PDFdujobozinovicNo ratings yet

- 74LS245Document7 pages74LS245Francisco Raúl DelgadoNo ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- MC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceiverDocument8 pagesMC74HC541A Octal 3-State Non-Inverting Buffer/Line Driver/ Line ReceivernandobnuNo ratings yet

- 74LCX16245 Low Voltage 16-Bit Bidirectional Transceiver With 5V Tolerant Inputs and OutputsDocument9 pages74LCX16245 Low Voltage 16-Bit Bidirectional Transceiver With 5V Tolerant Inputs and Outputsmichaelliu123456No ratings yet

- DatasheetDocument8 pagesDatasheetMaizatul Hanisah RoziNo ratings yet

- Adc 0808Document14 pagesAdc 0808Vikas PatelNo ratings yet

- TC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderDocument9 pagesTC74HC4028AP, TC74HC4028AF: BCD-to-Decimal DecoderAndrea DispoNo ratings yet

- 74LS47 PDFDocument6 pages74LS47 PDFJhill-Jhill Jimenez Dela PeñaNo ratings yet

- 74ACT244Document9 pages74ACT244ThanhNo ratings yet

- CD4553 Datasheet OKDocument13 pagesCD4553 Datasheet OKCong ThoNo ratings yet

- y 74158Document9 pagesy 74158Roberto Kaled Silva ValdiviaNo ratings yet

- 74VHC14 Hex Schmitt Inverter: Features General DescriptionDocument8 pages74VHC14 Hex Schmitt Inverter: Features General DescriptionAriel NavarreteNo ratings yet

- 74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BDocument7 pages74FST3251 8:1 Multiplexer/ Demultiplexer Bus Switch: SOIC 16 D Suffix CASE 751BRishabh PariharNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- ADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer OptionsDocument20 pagesADC0844/ADC0848 8-Bit P Compatible A/D Converters With Multiplexer Optionsrazali1982No ratings yet

- Datasheet - 74LS283 - Somador Binário Completo de 4 BitsDocument7 pagesDatasheet - 74LS283 - Somador Binário Completo de 4 BitsLucas CarvalhoNo ratings yet

- μP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerDocument16 pagesμP Compatible A/D Converters with 8-Channel: ADC0808/ADC0809 8-Bit MultiplexerKudo ShinichiNo ratings yet

- 74LS86P PDFDocument6 pages74LS86P PDFOsman KoçakNo ratings yet

- 74LS75 PDFDocument4 pages74LS75 PDFDeni KhanNo ratings yet

- 74ls245 (3-State Octal Bus Transceiver)Document7 pages74ls245 (3-State Octal Bus Transceiver)thanhdang8xNo ratings yet

- DM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesDocument6 pagesDM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesNegru P. PlantatieNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Radio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142From EverandRadio Shack TRS-80 Expansion Interface: Operator's Manual: Catalog Numbers: 26-1140, 26-1141, 26-1142No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- Digital Signal Processing Using the ARM Cortex M4From EverandDigital Signal Processing Using the ARM Cortex M4Rating: 1 out of 5 stars1/5 (1)

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Programmable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysFrom EverandProgrammable Logic Controllers: A Practical Approach to IEC 61131-3 using CoDeSysNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- 7 Types of AbnormalitiesDocument34 pages7 Types of AbnormalitiesYoga Adi100% (1)

- The New Standard To Analyse Risks Within The Automotive Supply ChainDocument8 pagesThe New Standard To Analyse Risks Within The Automotive Supply ChainYoga AdiNo ratings yet

- SCE en 030-020 R1209 Timers and CountersDocument41 pagesSCE en 030-020 R1209 Timers and CountersYoga AdiNo ratings yet

- TPM Chart PDFDocument1 pageTPM Chart PDFYoga AdiNo ratings yet

- SCE en 030-010 R1209 Block TypesDocument37 pagesSCE en 030-010 R1209 Block TypesYoga AdiNo ratings yet

- SCE en 030-010 R1209 Block TypesDocument37 pagesSCE en 030-010 R1209 Block TypesYoga AdiNo ratings yet

- SCE EN 020-011 R1404 Startup S7-1500 V13Document79 pagesSCE EN 020-011 R1404 Startup S7-1500 V13Yoga AdiNo ratings yet