Professional Documents

Culture Documents

Exam

Exam

Uploaded by

Hamed GhanbariOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Exam

Exam

Uploaded by

Hamed GhanbariCopyright:

Available Formats

EECS105

1 of 13

Fall 2000

Microelectronic Devices and Circuits- EECS105 Final Exam

Wednesday, December 13, 2000

Costas J. Spanos University of California at Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences

Your Name: ____________________________________________ (last) (first) Your Signature: __________________________________________ 1. Print and sign your name on this page before you start. 2. You are allowed three, 8.5x11 handwritten sheets. No books or notes! 3. Do everything on this exam, and make your methods as clear as possible. Problem 1 ________ / 24 Problem 2 ________ / 26 Problem 3 ________ / 26 Problem 4 ________ / 24 TOTAL _________ / 100 MOS Device Data (you may not have to use all of these...) n Cox = 50 A/V 2, pC ox = 25 A/V2, V Tn = -V Tp = 1V, Lmin = 2m. VBS = 0. n = p = 0.1V 1 when L = 1m, and it is otherwise proportional to 1/L Cox = 2.3fF/ m2 , Cjn = 0.1fF/m 2, C jp = 0.3fF/ m2 , Cjswn = 0.5fF/ m, Cjswp = 0.35fF/m, Covn = 0.5fF/m, Covp = 0.5fF/ m

EECS105

2 of 13

Fall 2000

Problem 1 of 4: Answer each question briefly and clearly. (4 points each, total 24)

Why are bipolar transistors capable of providing more drive current compared to MOS transistors that occupy similar area? (give a qualitative answer)

Comparing a Common Collector to a Common Drain voltage buffer amplifier, one sees some advantages and disadvantages. Place a mark below to indicate your choice, trying to get the largest DC voltage gain.

Aspect Rin Rout Av

CC

CD

In the IC industry layout designers can manipulate lateral device dimensions (L, W, area of baseemitter junction, etc.) while process designers manipulate vertical dimensions (Tox, base-width) and doping levels. List a parameter that each designer can change to affect the respective parameter, or write none if the designer cannot affect the value of the respective parameter: Parameter VTn ro (NMOS) gm (NMOS) ro (npn) gm (npn) Cgs Layout Designer Process Designer

EECS105

3 of 13

Fall 2000

What advantage(s) does a cascode configuration has over a cascade configuration?

Which conditions must be satisfied so that the open circuit time constant method leads to an exact solution?

In your own words, how does the dreaded Miller effect limit frequency response of a high voltage gain amplifier?

EECS105

4 of 13

Fall 2000

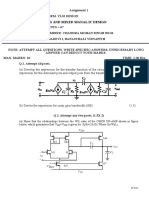

Problem 2 of 4 (26 points)

Consider the following cascode amplifier, driven by a perfect current source (r oc= ) For each of the following questions, make sure that you show the expressions before you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

a) Find (W/L)1 ratio so that the overall Gm of this amp is 1mS. (Do not specify values for W and for L here. That comes later). (5 points)

Expression for (W/L)1 (W/L) 1=

Value

EECS105

5 of 13

Fall 2000

b) Assume that gm2=gm1, and ro2 = ro1 . Find the value of L1 so that ro1 = 200k, and calculate the respective value of the overall Rout of this amplifier. (5 points)

Expression for L1 L1 =

Value

Expression for Rout Rout =

Value

EECS105

6 of 13

Fall 2000

c) Find the open circuit voltage gain of this two stage amplifier (roc= ). (5 points)

Expression for Voltage Gain vout/vin =

Value

in db

d) Calculate VBIAS (ignoring channel-length modulation). Assume that (W/L)1 = (W/L)2 = 16 (note that this is not the correct answer to question 2.a) (5 points)

Expression for VBIAS VBIAS =

Value

EECS105

7 of 13

Fall 2000

e) Assuming that (W/L) 2 = 16, find the value for VG2 that will give you the maximum voltage swing for this amp. Explain your thinking in one sentence (ignore channel length modulation). (6 points)

What limits Vout min?

Expression for VG2 VG2 =

Value

EECS105

8 of 13

Fall 2000

Problem 3/4 (26 points)

Consider the following pnp CE amplifier. Note that o = 50, IS= 10-17 A and VA = infinity. (Be very careful with signs in this problem!). For each of the following questions, make sure that you show the expressions before you plug in the specific values. A correct expression is worth 70% of the credit, even if the numerical calculation is incorrect!

a) Calculate VBIAS so that Vout = 2.5V. Ignore I B and Rs for this question. (Do NOT assume that VBE is exactly -0.7V). (5 points)

Expression for VBIAS VBIAS=

Value

EECS105

9 of 13

Fall 2000

b) Find Rout and the voltage gain, if R L = infinity. (8 points)

Expression for Rout Rout =

Value

Expression for Voltage Gain vout/vin =

Value

c) Calculate the value of R L that will cut the gain by a factor of two. (Assume that R L is connected through a small coupling capacitor, so that it does not disrupt the biasing of the transistor.) (5 points)

Expression for RL that cuts the gain by a factor of 2. RL =

Value

EECS105

10 of 13

Fall 2000

d) If you could increase o, how much would you have to increase it in order to increase the gain by 10%. (Hint: assume that the new, improved o = Xo, and write an expression that you can use to calculate the value of the factor X). (8 points)

Expression for X (multiplier for increasing o.) X=

Value

EECS105

11 of 13

Fall 2000

Problem 4/4 (24 points)

The following is a cascade of three 2-ports: a transconductance amplifier, a current buffer and a voltage buffer. The aim of this circuit is to produce lots of voltage gain over a wide bandwidth. .

a) Find the low frequency voltage gain vout/vin. (this means that you can ignore all the capacitors). Do this in stages as shown in the table below: (6 points)

Expression v2/vs = v3/v2 = vout/v3 = vout/vs =

Value

EECS105

12 of 13

Fall 2000

b) Replace all cross-over caps C1, C2 , C3, with their Miller equivalent CM1 , CM2 , CM3 . (6 points)

Expression CM1 = CM2 = CM3 = c) Calculate the Open Circuit Time Constant for the nodes 1, 2, 3 and 4. (6 points)

Value

Expression RT1 = RT2= RT3= RT4= Total

RC RC1 = RC2 = RC3 = RC4 =

Value

EECS105 d) Calculate the 3db of this amp (6 points)

13 of 13

Fall 2000

Expression for 3db. 3db =

Value

~ Thats All Folks! ~

You might also like

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliNo ratings yet

- Core Network Services-High Level Design TemplateDocument15 pagesCore Network Services-High Level Design TemplateBryan Gavigan100% (1)

- Two StageDocument6 pagesTwo StageSiphosethuSidloyiNo ratings yet

- PESTLE Analysis For Rolls RoyceDocument2 pagesPESTLE Analysis For Rolls Roycephi podcastNo ratings yet

- Midterm Exam Name: ID NumberDocument18 pagesMidterm Exam Name: ID NumberpskumarvlsipdNo ratings yet

- Cascode AmplifierDocument6 pagesCascode AmplifierRajesh NatarajanNo ratings yet

- Ee414 The4Document1 pageEe414 The4Asif SiddiqueNo ratings yet

- Aicd Exam SolutionDocument16 pagesAicd Exam SolutionTenzin ChoendenNo ratings yet

- HW 3Document5 pagesHW 3BrimwoodboyNo ratings yet

- 6.012 Electronic Devices and Circuits: Final ExaminationDocument13 pages6.012 Electronic Devices and Circuits: Final ExaminationhelpsatyaNo ratings yet

- Exam SolutionsDocument7 pagesExam SolutionsfaisalphyNo ratings yet

- 6002x FinalReview S2012 CleanDocument80 pages6002x FinalReview S2012 CleanGemini GntNo ratings yet

- Design & Testing of A RC Coupled Single Stage BJT AmplifierDocument6 pagesDesign & Testing of A RC Coupled Single Stage BJT AmplifierAaron GonsalvesNo ratings yet

- Problem Solving With MATLAB: CPET 190Document19 pagesProblem Solving With MATLAB: CPET 190Zan LayleNo ratings yet

- Birla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Document3 pagesBirla Institute of Technology and Science Pilani, Pilani Campus (Raj.)Arihant JainNo ratings yet

- E3-238: Analog VLSI Circuits Lab 2: InstructionsDocument4 pagesE3-238: Analog VLSI Circuits Lab 2: InstructionsR SHARMANo ratings yet

- AEC LabManualDocument30 pagesAEC LabManualPrateek PaliwalNo ratings yet

- AD 20flash 20converterDocument7 pagesAD 20flash 20converterChú Cá ConNo ratings yet

- Power System Analysis and Design 6th Edition Glover Test BankDocument14 pagesPower System Analysis and Design 6th Edition Glover Test BankMatthewGreenefgjtb100% (22)

- Midterm 2 Exam: Y-Parameters of The Amplifier With Feedback in (Ii) - You Must Show Your Work. (3 Points)Document9 pagesMidterm 2 Exam: Y-Parameters of The Amplifier With Feedback in (Ii) - You Must Show Your Work. (3 Points)Shubhresh Kumar JhaNo ratings yet

- Lab1 Ee140 s13 v1Document6 pagesLab1 Ee140 s13 v1Mohd YasirNo ratings yet

- Elec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2013 Final Exam - 4/22/13Document7 pagesElec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2013 Final Exam - 4/22/13SonDinhQuangNo ratings yet

- Eecs311 Lab06 PDFDocument28 pagesEecs311 Lab06 PDFGwenShepherdNo ratings yet

- University of Edinburgh College of Science and Engineering School of Engineering and ElectronicsDocument15 pagesUniversity of Edinburgh College of Science and Engineering School of Engineering and ElectronicsSyed Fasih Ur RehmanNo ratings yet

- Final Exam 2002Document12 pagesFinal Exam 2002Stephanie MurphyNo ratings yet

- EE3408E Project Design A Two-Stage Operational AmplifierDocument4 pagesEE3408E Project Design A Two-Stage Operational AmplifierLaSo ASNo ratings yet

- Design Opamp Summer CircuitDocument9 pagesDesign Opamp Summer CircuitA RNo ratings yet

- Digital Measurement Techniques-EIC703Document3 pagesDigital Measurement Techniques-EIC703sitaram_1No ratings yet

- Experiment 1Document5 pagesExperiment 1Abdul Basir SahebzadehNo ratings yet

- Experiment 3Document5 pagesExperiment 3Qurat AinniNo ratings yet

- Sample 1Document8 pagesSample 1nradhy2725No ratings yet

- Lecture13 BJT Transistor Circuit AnalysisDocument24 pagesLecture13 BJT Transistor Circuit Analysisazur33nNo ratings yet

- Adc Lab Manual PDFDocument74 pagesAdc Lab Manual PDFJega Deesan75% (4)

- Subject: Analog and Mixed Signal Ic DesignDocument2 pagesSubject: Analog and Mixed Signal Ic DesignchandravinitaNo ratings yet

- Final Exam 2020Document9 pagesFinal Exam 2020侯蕴书No ratings yet

- Sharmi ECE a-D-Circuits Lab ManualDocument74 pagesSharmi ECE a-D-Circuits Lab ManualSharmila83No ratings yet

- EE5310/EE3002: Analog Circuits Tutorial 1 Problems 6, 8, 10, 11 Are OptionalDocument10 pagesEE5310/EE3002: Analog Circuits Tutorial 1 Problems 6, 8, 10, 11 Are Optionaldummy1957jNo ratings yet

- LT SpiceDocument6 pagesLT SpiceVijay Preetham100% (1)

- Lab 2: Frequency and Time Response of Second Order Systems, Week of October 10, 2011Document9 pagesLab 2: Frequency and Time Response of Second Order Systems, Week of October 10, 2011Carlos ReyesNo ratings yet

- Function GeneratorDocument13 pagesFunction GeneratorDilJalaayNo ratings yet

- HomeworkDocument4 pagesHomework1dmsrufNo ratings yet

- A Be Midterm Spring KeyDocument11 pagesA Be Midterm Spring KeyRex ChemNo ratings yet

- Last Modified On September 3, 2004 by Stanley Wang and Henry JenDocument3 pagesLast Modified On September 3, 2004 by Stanley Wang and Henry JenThomas GeorgeNo ratings yet

- Design Project: (Due: Friday, December 8, 2006, 5pm PT)Document6 pagesDesign Project: (Due: Friday, December 8, 2006, 5pm PT)Ibrahim MuhammedNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- Ee141 HW5 2Document3 pagesEe141 HW5 2Vidhya DsNo ratings yet

- Name: - Student IDDocument10 pagesName: - Student IDMete SakallıNo ratings yet

- Midterm 07Document10 pagesMidterm 07ubertomeNo ratings yet

- EE477L HW1 Sp24Document4 pagesEE477L HW1 Sp24Archit SethiNo ratings yet

- Midterm1 SolutionDocument7 pagesMidterm1 SolutionSova ŽalosnaNo ratings yet

- Ee311 Homework4 2012 PDFDocument1 pageEe311 Homework4 2012 PDFtechaddicttNo ratings yet

- Introduction To Logic Design Experiments 1 Thru 10Document36 pagesIntroduction To Logic Design Experiments 1 Thru 10George Kokkinias100% (1)

- ME862VI-SampleMidSemQuestions 01Document4 pagesME862VI-SampleMidSemQuestions 01Manoj S KNo ratings yet

- Electric Circuit Exam INIESATDocument2 pagesElectric Circuit Exam INIESATMBIEDA NGOMEGNI FRANK GAETANNo ratings yet

- EE 330 Exam 2 Spring 2015 PDFDocument10 pagesEE 330 Exam 2 Spring 2015 PDFeng2011techNo ratings yet

- Lab#2 OpAmps 110420 V7Document4 pagesLab#2 OpAmps 110420 V7FrenkiNo ratings yet

- Lab 1: Multi-Stage Amplifiers: Philippine Institute For Integrated CircuitsDocument3 pagesLab 1: Multi-Stage Amplifiers: Philippine Institute For Integrated CircuitsIdk RebollosNo ratings yet

- ECD Lab 2 PDFDocument12 pagesECD Lab 2 PDFMaryam MahmoodNo ratings yet

- Power Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal AmplifiersDocument18 pagesPower Amplifiers Part 1 Class A: We Have Studied The Design of Small-Signal AmplifiersmalamigsajpanNo ratings yet

- Physics Investigatory Project Class 12Document22 pagesPhysics Investigatory Project Class 12Siddharth SinghNo ratings yet

- Review of The Relativistic MagnetronDocument20 pagesReview of The Relativistic MagnetronhaiquanNo ratings yet

- HR Governance As A Part of The Corporate Governance ConceptDocument24 pagesHR Governance As A Part of The Corporate Governance ConceptRudi HaryantoNo ratings yet

- Metodo Hach HierroDocument6 pagesMetodo Hach HierroJESSICA VANESSA ARISMENDI AVILEZNo ratings yet

- 8) Copper & Copper Alloy SpecificationsDocument3 pages8) Copper & Copper Alloy Specificationsnavas1972No ratings yet

- Rt7010 Lighting of Railway Premises PDFDocument17 pagesRt7010 Lighting of Railway Premises PDFCezary P.No ratings yet

- Employees Satisfaction in Indian Oil Corporation LimitedDocument14 pagesEmployees Satisfaction in Indian Oil Corporation LimitedBharat Makkar100% (1)

- Class - 12th Annual ReportDocument4 pagesClass - 12th Annual ReportPreksha SharmaNo ratings yet

- Petrol Skills - Seismic Interp EXTRADocument91 pagesPetrol Skills - Seismic Interp EXTRATroy Hewitt50% (2)

- 24 Solar TermsDocument98 pages24 Solar TermsWei Yu LowNo ratings yet

- SL-R930 (WIN) : Script Execution in Batch Mode: in This Lesson You Will Learn ToDocument2 pagesSL-R930 (WIN) : Script Execution in Batch Mode: in This Lesson You Will Learn Totruva_kissNo ratings yet

- EID Vol15No1Document151 pagesEID Vol15No1ImmortalYawnNo ratings yet

- Unit 1 Prog Logic DevelopmentDocument8 pagesUnit 1 Prog Logic DevelopmentAtharv KhadatareNo ratings yet

- Three Lever ClassesDocument5 pagesThree Lever ClassesSourabh SharafNo ratings yet

- Journal HFMDocument8 pagesJournal HFMVijayabhaskarareddy VemireddyNo ratings yet

- Solved ECE QP GATE PDFDocument112 pagesSolved ECE QP GATE PDFsmile4evr2100% (2)

- eDocument53 pageseHarik CNo ratings yet

- Reed Solomon CodesDocument6 pagesReed Solomon CodesMohammed MouftiNo ratings yet

- Aharen San - Mastering FPGA Embedded Systems A Case Study Approach To Designing and Implementing FPGA-Based Embedded Systems With TFT LCDs (Z-Library)Document263 pagesAharen San - Mastering FPGA Embedded Systems A Case Study Approach To Designing and Implementing FPGA-Based Embedded Systems With TFT LCDs (Z-Library)r.dmirandaNo ratings yet

- How Deep Is Your LoveDocument1 pageHow Deep Is Your LoveJanina JaworskiNo ratings yet

- Role of Design Department in Printing TextileDocument14 pagesRole of Design Department in Printing TextileAbdul RaphayNo ratings yet

- Science Lesson PlanDocument4 pagesScience Lesson PlanElyn LoRiNo ratings yet

- Finished Goods Inventories XX Work in Progress XX To Record The Completed JobDocument6 pagesFinished Goods Inventories XX Work in Progress XX To Record The Completed JobClarissa TeodoroNo ratings yet

- 2019-11-01 in The Moment PDFDocument154 pages2019-11-01 in The Moment PDFChantal ElieNo ratings yet

- Constitution Research PaperDocument9 pagesConstitution Research PaperSEJAL AGRAWAL BA LLBNo ratings yet

- Result Phase III - A, B - Lot (23!03!2024)Document15 pagesResult Phase III - A, B - Lot (23!03!2024)xxxlordimpalerxxxNo ratings yet

- 85.deep Seabed Mining (12-2013)Document4 pages85.deep Seabed Mining (12-2013)RSTNo ratings yet

- RFP Development of Central Green Park in Gift City09092021011413Document151 pagesRFP Development of Central Green Park in Gift City09092021011413akashNo ratings yet