Professional Documents

Culture Documents

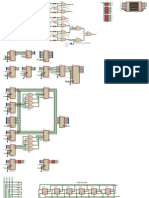

SAP-1 Simple As Possible Computer Schematic Diagram

SAP-1 Simple As Possible Computer Schematic Diagram

Uploaded by

pong74lsOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

SAP-1 Simple As Possible Computer Schematic Diagram

SAP-1 Simple As Possible Computer Schematic Diagram

Uploaded by

pong74lsCopyright:

Available Formats

OP7

OP6

OP5

OP4

OP3

OP2

OP1

OP0

Cp Ep Lm CE Li Ei La Ea Su Eu Lb Lo

T1 T2 T3 T4 T5 T6

U24:A

VCC 1 3 2 CLR ADR3 ADR2 ADR1 ADR0 D7 D6 D5 D4 D3 D2 D1 D0

VCC

SW5

Clear/Start

START

? ? ? ? ? ?

W7 W6 W5 W4 W3 W2 W1 W0

? ? ? ? ? ? ? ? ? ? ? ?

U24:B

CLEAR 4 6 VCC

? ? ? ? ? ? ? ?

5 7400

CLR

ADR3 ADR2 ADR1 ADR0

D7 D6 D5 D4 D3 D2 D1 D0

U24:C

VCC

SW1

OFF

SW3

ON

5 6 7 8

8 7 6 5 4 3 2 1

VCC

9 8 10

OFF

ON

Address Switch

OPCode / Data Switches

SW4

Write Memory

WEram Single Step

SW6

LOW

4 3 2 1

9 10 11 12 13 14 15 16

U24:D

HIGH 12 11 VCC 13 HLT 7400 1 2 13

U25:A

12

Note: The RAM has inverting outputs so this switch has also been inverted to enter the correct data. UP = Logic 0 input = Logic 1 Output from RAM DOWN = Logic 1 input = Logic 0 output from RAM (Observe W-Bus indicators for correct value)

U26:A

VCC 1 3 2 ENpc 13 11 12 1 2 3 4 CLK

U26:D

SW2

VCC ENmar Ep

SW8 SW7

Manual/Auto Manual Program/Run

U27:A

U27:B

CE ENram Program/Run Note: This extra switch was added to isolate the output of the Program Counter from the W-bus when entering data, otherwise a logic contention will occur. VCC

U26:B

Auto 4 6 5 HLT 3 4 5

U27:C U25:B

6 5 6 CLK

U25:B(C) INIT=LOW START=0 COUNT=-1 CLOCK=1

Note: The 555 timer circuit has been substituted with a virtual clock source to speed up the simulation.

W7 W6 W5 W4 W3 W2 W1 W0

Cp

U1:A

74LS107 3 Q J CLK R 2 Q K 1 12 5

U1:B

74LS107 Q J CLK R 6 Q K 8 9 3

U2:A

74LS107 Q J CLK R 2 Q K 1 12 5

U2:B

74LS107 Q J CLK R 6 Q K 8 9 11 CLK

11

13

10

13

10

CLR 12 2 5 9

U3:A

1

U3:B

4

U3:C

10

U3:D

13 7 1 2 9 10 15 14 13 12 11 CLK La CLK La

11

74LS126 ENpc

CLK OE1 OE2 E1 E2 MR

74LS173 Accumulator Q0 Q1 Q2 Q3

CLK OE1 OE2 E1 E2 MR

D0 D1 D2 D3

D0 D1 D2 D3

U11

7 1 2 9 10 15

14 13 12 11

U10

74LS173 Accumulator

3 4 5 6

Q0 Q1 Q2 Q3

CLK Lm 1 Ea 1 Ea

15 10 9 2 1 7

11 12 13 14

MR E2 E1 OE2 OE1 CLK

D3 D2 D1 D0

U4

74LS173 Memory Address Register 4 4

Q3 Q2 Q1 Q0

6 5 4 3

10

ENmar 11 15 1 13 14 10 11 6 5 3 2 12 11 12

13

E A/B

4B 4A 3B 3A 2B 2A 1B 1A

U5

74LS157 2-1 Multiplexer

U13:D

74LS126 Accumulator Output

U12:D

74LS126 Accumulator Output

4Y

3Y

2Y

ENram WEram 3 2 13 14 15 1 12 10 6 4

D7 D6 D5 D4

12

1Y

ENram WEram 3 2 13 14 15 1 12 10 6 4

D3 D2 D1 D0 10 12 13 1 2 4 5 9

13

ADR0 ADR1 ADR2 ADR3

10

Su 10 12

3 4 5 6

Su 13 1 2 4 5 9

WE ME A3 A2 A1 A0 D4 D3 D2 D1

WE ME A3 A2 A1 A0 D4 D3 D2 D1

U6

74LS89 16 X 4-bit RAM

U7

74LS89 16 X 4-bit RAM

U15:D

74LS86

U14:D

74LS86

Q4 Q3 Q2 Q1

11 9 7 5

11 9 7 5

Q4 Q3 Q2 Q1

11

Su 5 3 14 12 6 2 15 11 5 3 14 12 7 6 2 15 11 7

Carry

A0 A1 A2 A3

B0 B1 B2 B3

A0 A1 A2 A3

C0

B0 B1 B2 B3

74LS283 Full Adder (LSB) C4 C4 S0 S1 S2 S3 S0 S1 S2 S3

C0

U17

U16

74LS283 Full Adder (MSB)

4 1 13 10

4 1 13 10

CLK Li CLR

CLK Ei Li

Carry

15 10 9 2 1 7

15 10 9 2 1 7

11 12 13 14

11 12 13 14

U19:D

12 2 5 9 2 5

11

U18:D

12 10 8 11 1 3 6 4 9 74LS126 13

74LS126 13

MR E2 E1 OE2 OE1 CLK

MR E2 E1 OE2 OE1 CLK

D3 D2 D1 D0

D3 D2 D1 D0

U8

74LS173 Instruction Register (OPCode)

U9

74LS173 Instruction Register (Address) 3

1 6

4 8

10 11

Q3 Q2 Q1 Q0

Q3 Q2 Q1 Q0

Eu

6 5 4 3

I7 I6 I5 I4

6 5 4 3

CLK Lb

CLK Lb

14 13 12 11

7 1 2 9 10 15

14 13 12 11

D0 D1 D2 D3

CLK OE1 OE2 E1 E2 MR

D0 D1 D2 D3

74LS173 B Register (LSB) Q0 Q1 Q2 Q3

CLK OE1 OE2 E1 E2 MR

U21

7 1 2 9 10 15

U20

74LS173 B Register (MSB)

3 4 5 6

Q0 Q1 Q2 Q3

CLK Lo CLR

3 4 5 6

CLK Lo CLR

7 1 2 9 10 15

CLK OE1 OE2 E1 E2 MR

74LS173 Output Register Q0 Q1 Q2 Q3

CLK OE1 OE2 E1 E2 MR 8 9 11 10

D0 D1 D2 D3

D0 D1 D2 D3

U23

7 1 2 9 10 15

14 13 12 11

14 13 12 11

U22

74LS173 Output Register

3 4 5 6

Q0 Q1 Q2 Q3

VCC OP0 OP1 OP2 OP3 OP4 OP5 OP6 OP7 Note: These pull-up resistors are necessary because the outputs of the 74LS89 (substitute for the 74LS189) are open collector.

I7

I6

I5

I4

U31:A

2 1

Ring Counter

CLK

U31:B

4 3 3

U36:A

74LS107 Q J CLK 1 12 5

U36:B

74LS107 Q J CLK R 6 Q K 8 9 3

U37:A

74LS107 Q J CLK R 2 Q K 1 12 5

U37:B

74LS107 Q J CLK R 6 Q K 8 9 3

U38:A

74LS107 Q J CLK R 2 Q K 1 12 5

U38:B

74LS107 Q J CLK R 10 6 Q K

U31:C

6 5

13

11

11

10

13

10

13

3 4 5 6

U31:D

12 13 T6 T5 T4 T3 T2 T1 11 13

CLR

U35:E

U35:D

Instruction Decoder

1 2 4 5

Control Matrix

10

U32:A

6 1

U35:A

2 LDA ADD SUB

9 10 12 13

U32:B

8 3

U35:B

4

OUT

10

12 12

13

10

12

13

10

12

13

12

13

U39:D

1 2 4 5 3 6 8 3 6 8

U40:D

U41:D

U42:D

10

U43:C

U33:A

6 5

U35:C

6 3 6 8 3 6 8 3 6 11 11 11 11 8 Lo

9 10

12 13

1 2 13

9 10 12 13

U33:B

8 9

U35:F

1 2 4 5 3 4 5 1 2 4 8

U44:A U34:A

6 6 8

U44:B

U45:A

U45:B

U46:A

U46:B

1 2 4 5

12

11

13

U47:A

2 4

U47:B

6

U47:C

8

U47:F

10

U47:E U47:D

2 12

HLT

U48:B U48:A

4 Eu Lb

Cp Ep

Lm

CE

Li

Ei

La

Ea

Su

You might also like

- Assembly Language For Pic16f877a MicrocontrollerDocument65 pagesAssembly Language For Pic16f877a MicrocontrollerTarek Barhoum100% (2)

- Sap 2Document35 pagesSap 2Michael Vincent B. Nierva88% (8)

- Sap 1Document15 pagesSap 1Nahin Amin100% (1)

- Solution - Manual The 8051 Microcontroller Based Embedded SystemsDocument14 pagesSolution - Manual The 8051 Microcontroller Based Embedded Systemsmanishpatel_79No ratings yet

- 8051 LAB Assignment QuestionsDocument5 pages8051 LAB Assignment QuestionsMehul Patel0% (1)

- Digital Electronics Lab ManualDocument108 pagesDigital Electronics Lab Manualkunaraj88% (17)

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsNo ratings yet

- ASAP-2 Almost Simple As Possible Computer SchematicDocument1 pageASAP-2 Almost Simple As Possible Computer Schematicpong74lsNo ratings yet

- SAP-1 Simple As Possible Microprocessor - Original DesignDocument1 pageSAP-1 Simple As Possible Microprocessor - Original DesignFarhan S. Adul100% (1)

- SAP-3 Simple As Possible ComputerDocument18 pagesSAP-3 Simple As Possible ComputerAnthony K. Singleton100% (5)

- Sap 1 2Document21 pagesSap 1 2Brandon Maciel50% (2)

- Sap 1Document54 pagesSap 1ICANSAP0% (3)

- Sap 1 Manual NewDocument41 pagesSap 1 Manual NewAlexis John Rubio0% (1)

- Sap 3 ArchitectureDocument5 pagesSap 3 ArchitectureYzza Veah Esquivel100% (3)

- Simple As Possible Computer (SAP-1) : Lecture-3Document44 pagesSimple As Possible Computer (SAP-1) : Lecture-3Tawhid KhondakarNo ratings yet

- Review QuestionsDocument7 pagesReview QuestionsSyakila100% (1)

- SAP-2 Simple As Possible ComputerDocument22 pagesSAP-2 Simple As Possible ComputerAnthony K. Singleton91% (11)

- Computer Organization, Architecture and Machine Level ProgrammingDocument17 pagesComputer Organization, Architecture and Machine Level ProgrammingJaysen GeronimoNo ratings yet

- SAP-1 Simple As Possible Computer With Discrete Component RAMDocument1 pageSAP-1 Simple As Possible Computer With Discrete Component RAMpong74lsNo ratings yet

- Asm Lang Prog 68K FamilyDocument256 pagesAsm Lang Prog 68K FamilyPanos BriniasNo ratings yet

- Microprocessor Theory and Applications With 6800068020 and Pentium TQW - DarksidergDocument590 pagesMicroprocessor Theory and Applications With 6800068020 and Pentium TQW - DarksidergSuraj Kumar Gupta100% (4)

- The 8051 Microcontroller Based Embedded SystemsDocument45 pagesThe 8051 Microcontroller Based Embedded Systemsmanishpatel_7950% (8)

- 8051 Unit 1 NotesDocument19 pages8051 Unit 1 NotesSOMESH B S100% (13)

- SAP 1 Simple As Possible ComputerDocument51 pagesSAP 1 Simple As Possible ComputerShawon Nazrul Islam80% (5)

- 8051 Manual FinDocument39 pages8051 Manual Finnagaraj100% (2)

- Microprocessor Ppt1Document36 pagesMicroprocessor Ppt1alfred calaunan100% (1)

- 6502 User ManualDocument52 pages6502 User ManualOmar KhayyamNo ratings yet

- Digital Design Using Verilog HDLDocument108 pagesDigital Design Using Verilog HDLNihar PandaNo ratings yet

- Microprocessors and Interfacing Slides2Document28 pagesMicroprocessors and Interfacing Slides2Inception To Eminent MissionNo ratings yet

- Basic Computer Quiz Questions With AnswersDocument3 pagesBasic Computer Quiz Questions With AnswersDeev PokhrelNo ratings yet

- SAP (Simple-As-Possible) Computers: 10-1 ArchitectureDocument24 pagesSAP (Simple-As-Possible) Computers: 10-1 ArchitectureAfrahly Afable100% (1)

- Answers of Microprocessor (8085) & Electronics FAQDocument21 pagesAnswers of Microprocessor (8085) & Electronics FAQsoumyadev100% (23)

- 8086 Instruction SetDocument92 pages8086 Instruction SetAllanki Sanyasi Rao82% (28)

- Apple II Applesoft BASIC Programmer's Reference Manual - Volume 2Document134 pagesApple II Applesoft BASIC Programmer's Reference Manual - Volume 2remowNo ratings yet

- Assignment Microprocessor 8085Document2 pagesAssignment Microprocessor 8085Dhaval Shukla100% (1)

- Assembly Language: Arithmetic and Logic InstructionsDocument26 pagesAssembly Language: Arithmetic and Logic InstructionsRameen ChNo ratings yet

- Apple II Extended 80 Column Text Card SupplementDocument76 pagesApple II Extended 80 Column Text Card SupplementremowNo ratings yet

- Sap 2 ArchitectureDocument7 pagesSap 2 ArchitectureYzza Veah Esquivel75% (4)

- Digital Electronics & Computer Fundamentals Theory.Document137 pagesDigital Electronics & Computer Fundamentals Theory.Raju Ali Kawsar50% (2)

- 8051 Microcontroller NotesDocument40 pages8051 Microcontroller Notesilg1100% (1)

- Troubleshooting Maintaining Repairing Pcs Stephen J Bigelow PDFDocument3 pagesTroubleshooting Maintaining Repairing Pcs Stephen J Bigelow PDFRaj Gurjar Behind Wale75% (4)

- Basic Electronics Lab ManualDocument100 pagesBasic Electronics Lab ManualMitchell Cifuentes100% (4)

- SAP-1 Simple As Possible Computer With Microcoded ROMDocument1 pageSAP-1 Simple As Possible Computer With Microcoded ROMpong74lsNo ratings yet

- ID 4801 SchematicDocument1 pageID 4801 Schematicmjs6029100% (1)

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- Cpu Logic DiagramDocument0 pagesCpu Logic DiagramMauricio RaúlNo ratings yet

- SCH UnipolarDocument1 pageSCH UnipolarSerchu_29No ratings yet

- Driver StepDocument1 pageDriver StepTam Phuong NguyenNo ratings yet

- Bueno - DSN 06/05/2012 F:/bueno - DSN: File Name: DateDocument1 pageBueno - DSN 06/05/2012 F:/bueno - DSN: File Name: DateOswaldo LucioNo ratings yet

- Daewoo DVG 6000DDocument12 pagesDaewoo DVG 6000DOssian Valera PinedaNo ratings yet

- Schematic1 - Page1Document1 pageSchematic1 - Page1Phan Văn TúNo ratings yet

- Willem Eprom 4 and 3.5 SchematicDocument1 pageWillem Eprom 4 and 3.5 SchematicAislan SouzaNo ratings yet

- SCH CpuDocument1 pageSCH CpuWilliams Giorgio Sicsu100% (2)

- Ss 800 1200 Sinus Single PDFDocument1 pageSs 800 1200 Sinus Single PDFatomo33No ratings yet

- PR D Q: Control Input Pin 1 - Direction Pin 3 - Step Pulses Pin 5 - Motor On/Off (0 On)Document1 pagePR D Q: Control Input Pin 1 - Direction Pin 3 - Step Pulses Pin 5 - Motor On/Off (0 On)Serchu_29No ratings yet

- W375 L3 V1.2 SchemDocument3 pagesW375 L3 V1.2 SchemAdrian PeterNo ratings yet

- Placa 1Document1 pagePlaca 1Juan Galarza100% (1)

- Schematic DiagramDocument13 pagesSchematic DiagramSas WajiNo ratings yet

- PinOut Diagrams PDFDocument4 pagesPinOut Diagrams PDFDaryl ScottNo ratings yet

- SAP-1 Simple As Possible Computer With Discrete Component RAMDocument1 pageSAP-1 Simple As Possible Computer With Discrete Component RAMpong74lsNo ratings yet

- ASAP-2 Almost Simple As Possible Computer SchematicDocument1 pageASAP-2 Almost Simple As Possible Computer Schematicpong74lsNo ratings yet

- SAP-1 Simple As Possible Computer With Microcoded ROMDocument1 pageSAP-1 Simple As Possible Computer With Microcoded ROMpong74lsNo ratings yet

- SAP-1 Simple As Possible Computer Schematic Diagram - Updated DesignDocument1 pageSAP-1 Simple As Possible Computer Schematic Diagram - Updated Designpong74lsNo ratings yet

- ARM - Architecture Reference Manual - ARM DDI 0100BDocument322 pagesARM - Architecture Reference Manual - ARM DDI 0100BAkihito Hashimoto100% (1)

- Peripherai Interface Microprocessor 68000Document40 pagesPeripherai Interface Microprocessor 68000Alfi Muhammad Akbar BariaNo ratings yet

- 8085 AssignmentDocument2 pages8085 AssignmentnkNo ratings yet

- Supplemental Reading On Logic GatesDocument10 pagesSupplemental Reading On Logic GatesapelhenrytersooNo ratings yet

- Fundamentals of Computer Architecture: Unit - IDocument74 pagesFundamentals of Computer Architecture: Unit - IDhruv ChoudharyNo ratings yet

- Lab Report 4Document10 pagesLab Report 4abdulbabulNo ratings yet

- Basic Logic GatesDocument5 pagesBasic Logic GatesVasu ReddyNo ratings yet

- Sparc/Cpu-3Ce: Installation GuideDocument47 pagesSparc/Cpu-3Ce: Installation GuideTeguh RumiyartoNo ratings yet

- Logic FamiliesDocument14 pagesLogic FamiliesAjay ReddyNo ratings yet

- PCI-7432 Datasheet E3.3Document5 pagesPCI-7432 Datasheet E3.3ajma86No ratings yet

- 3-Sample Quiz FSM - SolutionDocument3 pages3-Sample Quiz FSM - SolutionSarah Nurfathiah Abdul RahmanNo ratings yet

- EE 319K Introduction To Embedded SystemsDocument24 pagesEE 319K Introduction To Embedded SystemsPablo LópezNo ratings yet

- Master Learning MapsDocument10 pagesMaster Learning Mapsuzairhasan09No ratings yet

- Er-Tftm070-4V2.1: Eastrising Technology Co., LimitedDocument26 pagesEr-Tftm070-4V2.1: Eastrising Technology Co., Limitedbeppino_andoNo ratings yet

- SMD ComponentsDocument131 pagesSMD ComponentsCvetkovic IgorNo ratings yet

- Integrated CircuitDocument21 pagesIntegrated CircuitahmedNo ratings yet

- What Is A Microprocessor and How Does It Work - PDFDocument9 pagesWhat Is A Microprocessor and How Does It Work - PDFTestuno TestunoNo ratings yet

- MC68HC908JL8Document212 pagesMC68HC908JL8kkkkkkkkkkkkNo ratings yet

- GC3355 Application NOTEDocument5 pagesGC3355 Application NOTEMarcianoValverdeNo ratings yet

- PD Flow I - FloorplanDocument25 pagesPD Flow I - FloorplansudhirNo ratings yet

- Q&ADocument89 pagesQ&AAjay Tomar100% (1)

- CBLM Output CSS FDocument39 pagesCBLM Output CSS FWALO100% (1)

- Project Report ON Metro Train PrototypeDocument38 pagesProject Report ON Metro Train PrototypeAnil TandonNo ratings yet

- Experiment No.1: AIM: Design The Following Combinational Circuits Using VHDL and Test The Circuits Using TestDocument83 pagesExperiment No.1: AIM: Design The Following Combinational Circuits Using VHDL and Test The Circuits Using Testdelinquent_abhishekNo ratings yet

- Logic Design DDocument48 pagesLogic Design DClint Marton Flores MarquezNo ratings yet

- Gate Level Modeling: Prof. A. K. Swain Asst. Prof., ECE Dept., NIT Rourkela EC6203: Reconfigurable System DesignDocument18 pagesGate Level Modeling: Prof. A. K. Swain Asst. Prof., ECE Dept., NIT Rourkela EC6203: Reconfigurable System DesignRashmi SinghNo ratings yet

- SST Base Memory Cross Reference Table Silicon Storage Technology, IncDocument39 pagesSST Base Memory Cross Reference Table Silicon Storage Technology, IncDenis DenisovNo ratings yet

- Eidc32 Spec SheetDocument2 pagesEidc32 Spec SheetKristopher OrtizNo ratings yet

- HP Elitebook 6930p PDFDocument58 pagesHP Elitebook 6930p PDFMarcos Alessandro Santana SantosNo ratings yet

- Debugger XtensaDocument68 pagesDebugger Xtensacarver_uaNo ratings yet