Professional Documents

Culture Documents

6C0065

6C0065

Uploaded by

Joshua prabu0 ratings0% found this document useful (0 votes)

69 views4 pagesThis document contains details about a digital logic theory and design exam for third semester BE EIE students at Sathyabama University, including:

- The exam has two parts (A and B) worth 20 and 60 marks respectively and lasts 3 hours

- Part A contains 10 short answer questions about topics like binary coding, Demorgan's theorem, tri-state gates, encoders/decoders, comparators, flip-flops and hazards

- Part B contains 5 long answer questions involving topics like K-map minimization, TTL parameters, logic gates, decoders, programmable logic arrays, counters and flip-flops

- Sample questions assess skills in binary coding, Boolean algebra, logic gate design

Original Description:

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains details about a digital logic theory and design exam for third semester BE EIE students at Sathyabama University, including:

- The exam has two parts (A and B) worth 20 and 60 marks respectively and lasts 3 hours

- Part A contains 10 short answer questions about topics like binary coding, Demorgan's theorem, tri-state gates, encoders/decoders, comparators, flip-flops and hazards

- Part B contains 5 long answer questions involving topics like K-map minimization, TTL parameters, logic gates, decoders, programmable logic arrays, counters and flip-flops

- Sample questions assess skills in binary coding, Boolean algebra, logic gate design

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

0 ratings0% found this document useful (0 votes)

69 views4 pages6C0065

6C0065

Uploaded by

Joshua prabuThis document contains details about a digital logic theory and design exam for third semester BE EIE students at Sathyabama University, including:

- The exam has two parts (A and B) worth 20 and 60 marks respectively and lasts 3 hours

- Part A contains 10 short answer questions about topics like binary coding, Demorgan's theorem, tri-state gates, encoders/decoders, comparators, flip-flops and hazards

- Part B contains 5 long answer questions involving topics like K-map minimization, TTL parameters, logic gates, decoders, programmable logic arrays, counters and flip-flops

- Sample questions assess skills in binary coding, Boolean algebra, logic gate design

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

You are on page 1of 4

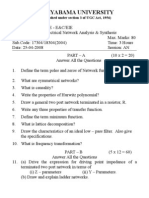

SATHYABAMA UNIVERSITY

(Established under section 3 of UGC Act, 1956)

Course & Branch: B.E - EIE

Title of the paper: Digital Logic Theory and Design

Semester: III Max. Marks: 80

Sub.Code: 6C0065 Time: 3 Hours

Date: 06-05-2008 Session: AN

PART – A (10 x 2 = 20)

Answer All the Questions

1. Express the following decimal numbers in 2421 and 5421 code (i)

1993

2. State Demorgan’s theorem.

3. Give two advantages and one disadvantages of the totem pole

arrangement.

4. What is a tri-state gate?

5. Compare Encoder and decoder.

6. What is meant by a magnitude comparator?

7. Draw the logic diagram of a master – slave D-flip flop using NAND

gate.

8. What do you mean by critical and Non-critical races? How can they

be avoided?

9. Why are shift registers considered to be basic memory devices?

10. How can essential hazards be eliminated?

PART – B (5 x 12 = 60)

Answer All the Questions

11. Using the K-map method, Simplify the following functions into

minimal sum of products

F(u,w,x,y,z)= ∑(0.2,5,7,9,11,13,15,16,18,21,23,25,27,29,31)

(or)

12. Find the minimal sum of products for the Boolean expression,

F(a,b,c,d) = ∑(1,2,3,7,8,9,10,11,14,15)

13. Discuss about the various parameters of TTL.

(or)

14. (a) Draw the basic BICMOS inverter, NAND and NOR gates and

explain its operation.

(b) Draw and explain the circuit diagram of a 3-input I2L NOR gate.

15. Explain briefly about the BCD – Seven Segment decoder.

(or)

16. Draw and explain the basic block diagram of PLA and what are the

steps used for implementing combinational circuit using PLA.

17. Design a synchronous counter with the following sequence counter

0000 0100 0100 0110 1000 1010 1100 1110 0000.

(or)

18. (a) Explain the working of serial in parallel out shift register with

logic diagram and waveforms.

(b) Explain about the various applications of flip-flops.

19. Obtain a static hazard free asynchronous circuit for the following

switching function.

F = ∑(0,2,4,5,8,10,14)

(or)

20. Design an asynchronous circuit that will output only the first pulse

received whatever a control input is asserted from LOW to HIGH

state. Any future pulses will be ignored.

(ii) Timing Diagram

You might also like

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- Sathyabama University: Semester: IV Max - Marks: 80Document5 pagesSathyabama University: Semester: IV Max - Marks: 80GAURAVKINHANo ratings yet

- Deld QB EndsemDocument4 pagesDeld QB EndsemUV New MoviesNo ratings yet

- Question Bank: Ec6302 Digital ElectronicsDocument14 pagesQuestion Bank: Ec6302 Digital ElectronicsBarry SmithNo ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- Digital Electronics QBDocument7 pagesDigital Electronics QBvinaytmkNo ratings yet

- EE6301 DLC Question Bank Rejinpaul 2Document8 pagesEE6301 DLC Question Bank Rejinpaul 2aruljothiNo ratings yet

- DF_QUESTION BANKDocument6 pagesDF_QUESTION BANKjignasha.patelNo ratings yet

- Digital Electronics QuestionsDocument8 pagesDigital Electronics QuestionsShivamahendar SunkaNo ratings yet

- Question Bank For DLCDocument8 pagesQuestion Bank For DLCAvina AshNo ratings yet

- EC2203 U Q BankDocument12 pagesEC2203 U Q Bankvlsi_satheeshNo ratings yet

- EE6301 QB FinalDocument21 pagesEE6301 QB FinallithijanarNo ratings yet

- MODEL-dlc Eeee RmkcetDocument2 pagesMODEL-dlc Eeee RmkcetreporterrajiniNo ratings yet

- Sathyabama: Register NumberDocument3 pagesSathyabama: Register NumberBoopalanElumalaiNo ratings yet

- Digital System Design: Provided by Humayra JahanDocument5 pagesDigital System Design: Provided by Humayra JahanZabirNo ratings yet

- EE6301-Digital Logic Circuits QBDocument7 pagesEE6301-Digital Logic Circuits QBariv2009No ratings yet

- Ec2203 Digital ElectronicsDocument8 pagesEc2203 Digital ElectronicspappujayaNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- MODULE_wise Question_2022-ddcoDocument4 pagesMODULE_wise Question_2022-ddcojeevanashree2004No ratings yet

- EC 6302 2-Marks and 16 Marks QuestionsDocument12 pagesEC 6302 2-Marks and 16 Marks QuestionsskaruppaiaheceNo ratings yet

- Sample Question Paper - Principles of Digital Techniques-12069Document4 pagesSample Question Paper - Principles of Digital Techniques-12069Jackson AnthonyNo ratings yet

- Subject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeeDocument16 pagesSubject Code/ Title: Ee6301 Digital Logic Circuits Year/ Sem/Branch: Ii/ Iii/ EeePavithra ManiNo ratings yet

- Digital Principles and System DesignDocument24 pagesDigital Principles and System Designhelloworld1000% (3)

- DLCDocument1 pageDLCrjvenkiNo ratings yet

- Ei2353:Digital System Design: Question BankDocument3 pagesEi2353:Digital System Design: Question BanknithyadeceNo ratings yet

- Question Paper Code:: Y Abcababc + + +Document3 pagesQuestion Paper Code:: Y Abcababc + + +karthick VijayanNo ratings yet

- A.R. Engineering College, Villupuram Ece Department: Ec2203/Digital ElectronicsDocument8 pagesA.R. Engineering College, Villupuram Ece Department: Ec2203/Digital ElectronicsNitu VlsiNo ratings yet

- Question Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-ADocument3 pagesQuestion Bank Subject Code: Ec6302 Subject: Digital Electronics Sem / Year: Iii / Ii-Ece Unit-I Minimization Techniques and Logic Gates Part-AmohanaNo ratings yet

- Question Paper Code:: (10×2 20 Marks)Document2 pagesQuestion Paper Code:: (10×2 20 Marks)kenny kannaNo ratings yet

- Ap9212 AdsdDocument12 pagesAp9212 AdsdKartheeswaran Arumugam33% (3)

- @vtucode.in-question bank-DD&CO-2022-schemeDocument4 pages@vtucode.in-question bank-DD&CO-2022-schememurageshadahalli8No ratings yet

- Digital Fundamentals BE SEM 3Document2 pagesDigital Fundamentals BE SEM 3Dhwanil BhattNo ratings yet

- DD&CO QBANK (Vtu23)Document3 pagesDD&CO QBANK (Vtu23)manjufk456No ratings yet

- Sample Question Paper Digital Techniques PDFDocument5 pagesSample Question Paper Digital Techniques PDFAshutosh PatilNo ratings yet

- 9a04306-Digital Logic DesignDocument1 page9a04306-Digital Logic DesignSheikh Noor MohammadNo ratings yet

- DellDocument6 pagesDellamu_manuNo ratings yet

- Nov 2019Document6 pagesNov 2019ponniNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- Principles of Digital Techniques On Web PDFDocument5 pagesPrinciples of Digital Techniques On Web PDFmdwalunjkar3095No ratings yet

- EC6302 Digital ElectronicsDocument12 pagesEC6302 Digital ElectronicsJabeen BanuNo ratings yet

- MODULE - Wise Question - 2022-ADE-CODocument4 pagesMODULE - Wise Question - 2022-ADE-COvinayvinayakars313No ratings yet

- Question Paper Code:: Reg. No.Document2 pagesQuestion Paper Code:: Reg. No.Monica NareshNo ratings yet

- EC6302-Digital ElectronicsDocument14 pagesEC6302-Digital Electronicsmagy1989No ratings yet

- Ec1312 QBDocument7 pagesEc1312 QBGopinathan MuthusamyNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- Sample-Question-Paper - Digital Electronics and Microcontroller ApplicationsDocument5 pagesSample-Question-Paper - Digital Electronics and Microcontroller ApplicationsAbhishek ManeNo ratings yet

- 2EC6302-Digital Electronics QBDocument12 pages2EC6302-Digital Electronics QBSurendar PNo ratings yet

- Digital ElectronicsDocument2 pagesDigital ElectronicsVaso RanaNo ratings yet

- 3409Document5 pages3409Sohail AhmadNo ratings yet

- Question Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodeDocument2 pagesQuestion Paper Code:: Part - A 1. Convert (643) Into Its Excess 3-CodePrabu KumarNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- R5 210504 Digital Logic DesignDocument1 pageR5 210504 Digital Logic DesignsivabharathamurthyNo ratings yet

- WWW - Universityquestions.in: Unit 1 Number Systems and Digital Logic Families Part ADocument7 pagesWWW - Universityquestions.in: Unit 1 Number Systems and Digital Logic Families Part Abunny_589318117No ratings yet

- Digital Electronics Question BankDocument6 pagesDigital Electronics Question BankReshna ShowkathNo ratings yet

- Ee2255 Digital Logic CircuitsDocument3 pagesEe2255 Digital Logic CircuitsecessecNo ratings yet

- Dem QB Ut-1 110120Document2 pagesDem QB Ut-1 110120ABHI THORATNo ratings yet

- DSP Integrated Circuits 3Document3 pagesDSP Integrated Circuits 3brindkowsiNo ratings yet

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionFrom EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document4 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- 6C0034Document5 pages6C0034Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document4 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document2 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Sathyabama University: (Established Under Section 3 of UGC Act, 1956)Document3 pagesSathyabama University: (Established Under Section 3 of UGC Act, 1956)Joshua prabuNo ratings yet

- Install Ulang RT1904Document10 pagesInstall Ulang RT1904ChandraNo ratings yet

- 89c Vs 89sDocument0 pages89c Vs 89sraunaq25No ratings yet

- CG - Module 1Document28 pagesCG - Module 1Swaroop Surendra100% (1)

- Digital Design and Computer Architecture: Lab 1: Full AdderDocument10 pagesDigital Design and Computer Architecture: Lab 1: Full AdderГруппа СМ5-41No ratings yet

- The Need For Harmonic Modeling and Mitigation of Generator ApplicationsDocument8 pagesThe Need For Harmonic Modeling and Mitigation of Generator ApplicationssnfulNo ratings yet

- Fc-100 Service Notes: SpecificationsDocument8 pagesFc-100 Service Notes: SpecificationsNina FernandezNo ratings yet

- A Brief History of ... SemiconductorsDocument11 pagesA Brief History of ... SemiconductorsLucas Chagas FazoloNo ratings yet

- FSM Melay Using 1011Document3 pagesFSM Melay Using 1011dineshvhavalNo ratings yet

- RB2011 Series-160118111327 PDFDocument1 pageRB2011 Series-160118111327 PDFJuanpa ReinhardNo ratings yet

- Step by Step Procedure HFSSDocument23 pagesStep by Step Procedure HFSSNilabja SahaNo ratings yet

- Spreadtrum SC6820 Guia Mantenimiento Reparacion Maintain Guide 0624Document45 pagesSpreadtrum SC6820 Guia Mantenimiento Reparacion Maintain Guide 0624olger huancara gaspara100% (1)

- 18EE33 - Module 1Document81 pages18EE33 - Module 1Rajendra VirajendraNo ratings yet

- Cobra ODE Installation Manual (English)Document46 pagesCobra ODE Installation Manual (English)ChipytoNo ratings yet

- Ads 1256Document43 pagesAds 1256yaser2005100% (2)

- DCI Format 1ADocument4 pagesDCI Format 1AFerdinandus RurukNo ratings yet

- Small SignalModellingoftheCukConverterDocument11 pagesSmall SignalModellingoftheCukConverterSamuel JuradoNo ratings yet

- AC To AC ConversionDocument6 pagesAC To AC ConversionTaniyaNo ratings yet

- EU1091-HR Application Guide DynaVar Surge ArresterDocument12 pagesEU1091-HR Application Guide DynaVar Surge ArresterHarold NaiborhuNo ratings yet

- Research PaperDocument11 pagesResearch Paperapi-466416222No ratings yet

- Siri MsDocument40 pagesSiri Msapi-3864016No ratings yet

- HD-D10 D20 D30 C10 C30 A30 Simple Operating Manual V1.2Document15 pagesHD-D10 D20 D30 C10 C30 A30 Simple Operating Manual V1.2Prashant SharmaNo ratings yet

- CMOS Inverter-Switching, Time DelayDocument14 pagesCMOS Inverter-Switching, Time DelayAlisha AnjumNo ratings yet

- Chemical Dosing I/o ListDocument3 pagesChemical Dosing I/o Listpriyo_a_sNo ratings yet

- Foto Ups 100 Kva Dak 2021Document5 pagesFoto Ups 100 Kva Dak 2021myrnaganiNo ratings yet

- P19 ArduinoDocument1 pageP19 ArduinoSanto MulyonoNo ratings yet

- Mec Question Bank 17-18Document2 pagesMec Question Bank 17-18nobita PlusNo ratings yet

- Sky 77528Document2 pagesSky 77528Anton Andi SetyawanNo ratings yet

- Gilas PC MaintenanceDocument97 pagesGilas PC MaintenanceEmmanuel Jimenez-Bacud, CSE-Professional,BA-MA Pol SciNo ratings yet

- Roc306/Roc312 Remote Operations Controller: Instruction ManualDocument160 pagesRoc306/Roc312 Remote Operations Controller: Instruction ManualtenithomasNo ratings yet

- MHL3000 AmplifierDocument16 pagesMHL3000 AmplifierThiem NguyenNo ratings yet