Professional Documents

Culture Documents

Angus Electronics Company Limited: PT2323 Description

Angus Electronics Company Limited: PT2323 Description

Uploaded by

vetchboyCopyright:

Available Formats

You might also like

- Diagrama cfd-rg880cpDocument14 pagesDiagrama cfd-rg880cpMarvin Leon Alegria100% (1)

- Av36d303 SchematicDocument30 pagesAv36d303 SchematicLuis MorenoNo ratings yet

- Data Pin FBT TV CinaDocument7 pagesData Pin FBT TV CinaKristen JuarezNo ratings yet

- Aiwa Av-D58-U SMDocument34 pagesAiwa Av-D58-U SMmiguel angel jaramilloNo ratings yet

- AbrilDocument11 pagesAbrilWilfrido Escobar ZuñigaNo ratings yet

- DVD Receiver System: Service ManualDocument73 pagesDVD Receiver System: Service ManualgondifNo ratings yet

- FBTDocument22 pagesFBTsalmanNo ratings yet

- Data FlybackDocument4 pagesData FlybackBanaNiBebang100% (1)

- (Codientu - Org) - 29Q317B, CHASSIS CW4Document14 pages(Codientu - Org) - 29Q317B, CHASSIS CW4GioVoTam100% (1)

- Data Pin Plyback Dan PersamaannyaDocument8 pagesData Pin Plyback Dan PersamaannyaMoch RofiiiqNo ratings yet

- Persamaan FBTDocument4 pagesPersamaan FBTAnam Elektronik HpaiNo ratings yet

- Eht CTVDocument34 pagesEht CTVPKPNo ratings yet

- Philips - Chassis L01.1A AC PDFDocument26 pagesPhilips - Chassis L01.1A AC PDFOsvaldo Dutto100% (1)

- Data Pin FlybackDocument4 pagesData Pin FlybackRene100% (3)

- Circuit Diagram 12-1-6Document1 pageCircuit Diagram 12-1-6stolllle67% (3)

- Sanyo ct21ks2 Chassis Fc8-A PDFDocument37 pagesSanyo ct21ks2 Chassis Fc8-A PDFKaray TehnikNo ratings yet

- Samsung EHTDocument8 pagesSamsung EHTshafiuddin7326No ratings yet

- Flybacks HR ReplacementDocument17 pagesFlybacks HR Replacementlastfriendsv100% (7)

- Data Pin FBT 2Document6 pagesData Pin FBT 2Rene100% (2)

- Fly BackDocument1 pageFly BackJose Gregorio Sanchez AraujoNo ratings yet

- Data Pin FlybackDocument5 pagesData Pin FlybackWahyu Ilhami100% (1)

- WB Gram Panchayat Previous Year Question Papers PDFDocument48 pagesWB Gram Panchayat Previous Year Question Papers PDFRitam AichNo ratings yet

- LTN140AT07Document30 pagesLTN140AT07JhonSalchichonNo ratings yet

- Tmpa 8859 Service Manual: ContentDocument14 pagesTmpa 8859 Service Manual: ContentNeto Garcia100% (1)

- Pin Flyback Dilihat / Dihitung Dari Bawah Searah Jarum JamDocument52 pagesPin Flyback Dilihat / Dihitung Dari Bawah Searah Jarum JamJuan Carlos RangelNo ratings yet

- Ic Osc FuenteDocument6 pagesIc Osc FuenteLeonardo Flei100% (1)

- Aoc Le32a1330-61 Le40a1330-61 LCD TV PDFDocument87 pagesAoc Le32a1330-61 Le40a1330-61 LCD TV PDFtrietNo ratings yet

- Okok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFDocument13 pagesOkok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFAloui Zakaria100% (1)

- Persamaan Flyback TVDocument10 pagesPersamaan Flyback TVAndika100% (1)

- TC 21gx20m MalaysiaDocument29 pagesTC 21gx20m MalaysiaChandan Tripathi100% (4)

- Data Pin Flyback LengkapDocument49 pagesData Pin Flyback LengkapAhmad Humaidi67% (3)

- Service Manual Samsung CS 29M40MH S16A Sdiag 10 A3Document4 pagesService Manual Samsung CS 29M40MH S16A Sdiag 10 A3Edgar AdonisNo ratings yet

- DATA PIN KAKI PLAYBEAKTV POLYTRON - FacebookDocument22 pagesDATA PIN KAKI PLAYBEAKTV POLYTRON - FacebookÁngel TapiaNo ratings yet

- Service Manual: Model: HT-2199 (Europe)Document48 pagesService Manual: Model: HT-2199 (Europe)Eze KielNo ratings yet

- TDA8375ADocument73 pagesTDA8375Asontuyet82No ratings yet

- TV Servicing Remote CodeDocument4 pagesTV Servicing Remote CodeVenkatesh Subramanya100% (1)

- Sharp Part ChassisDocument2 pagesSharp Part Chassiswatcharen100% (1)

- Flyback Monitor 3Document17 pagesFlyback Monitor 3Skumar Soni100% (1)

- Int 26 32 A-Z Magmeet MLT-688 SchematicDocument4 pagesInt 26 32 A-Z Magmeet MLT-688 SchematicMukesh Thakkar100% (5)

- Data Flyback TVDocument12 pagesData Flyback TVAntok DoankNo ratings yet

- TV Service ModeDocument26 pagesTV Service Modevideoson100% (5)

- JVC CA DX t9, DX t7, DX t5Document31 pagesJVC CA DX t9, DX t7, DX t5Roosevelt Vega SanchezNo ratings yet

- Persamaan Flyback TVDocument12 pagesPersamaan Flyback TVAzka TronikNo ratings yet

- Sanyo CM29FS2 FB1B PDFDocument41 pagesSanyo CM29FS2 FB1B PDFJerald D'costaNo ratings yet

- TV Flyback Transformer Datasheet List - Belajar SEODocument5 pagesTV Flyback Transformer Datasheet List - Belajar SEOempeeno10% (1)

- Remove Inverter Protection MethodDocument1 pageRemove Inverter Protection MethodmontepincioNo ratings yet

- Transistores SMD Codes Beginning With 'C'Document3 pagesTransistores SMD Codes Beginning With 'C'carlosNo ratings yet

- Toshiba TV 29AS42 Service ManualDocument38 pagesToshiba TV 29AS42 Service ManualLuthvi SanjayaNo ratings yet

- MC 84A ChassisDocument19 pagesMC 84A ChassisKapila Gunawardena100% (1)

- Description: 6-Ch Audio Selector PT2323Document17 pagesDescription: 6-Ch Audio Selector PT2323panjoelsNo ratings yet

- Parts Reference List: Brother Laser MFCDocument41 pagesParts Reference List: Brother Laser MFCNebi aktaşNo ratings yet

- Casio AP-60R Service ManualDocument34 pagesCasio AP-60R Service ManualMario Gabriel MoralliNo ratings yet

- PL Eclfb e Ver7Document42 pagesPL Eclfb e Ver7AgostinoNo ratings yet

- Schematic Diagrams: KD-G455, KD-G405Document5 pagesSchematic Diagrams: KD-G455, KD-G405heyjuNo ratings yet

- DCP 9030CDNL3510CDWL3517CDW - DCP L3550CDWL3551CDW - HL L3290CDW - MFC 9150CDN9350CDW - MFC L3710CWL3730CDNL3735CDN - MFC L3745CDWL3750CDWL3770CDW PDFDocument39 pagesDCP 9030CDNL3510CDWL3517CDW - DCP L3550CDWL3551CDW - HL L3290CDW - MFC 9150CDN9350CDW - MFC L3710CWL3730CDNL3735CDN - MFC L3745CDWL3750CDWL3770CDW PDFStefanGarnetNo ratings yet

- Ax5505 r1.1 AxeliteDocument12 pagesAx5505 r1.1 AxeliteSaul UribeNo ratings yet

- pt2388 (v1Document18 pagespt2388 (v1vetchboy0% (1)

- PTP6005 LP-BK-F (5000T) - 1P-KB-WO/COV LG: 3 Way Toggle Switch 101-1D CRP Knob:BkDocument1 pagePTP6005 LP-BK-F (5000T) - 1P-KB-WO/COV LG: 3 Way Toggle Switch 101-1D CRP Knob:BkmisterNo ratings yet

- CR50 PDFDocument1 pageCR50 PDFmisterNo ratings yet

- IO - LIST - 7K6S0607 - Rev06 - TSQ-B RPIO (CT)Document8 pagesIO - LIST - 7K6S0607 - Rev06 - TSQ-B RPIO (CT)Akun TestNo ratings yet

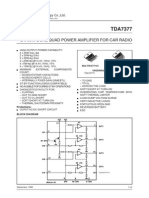

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocument10 pages2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNo ratings yet

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Document16 pagesCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNo ratings yet

- Tda7294 PDFDocument16 pagesTda7294 PDFRoger NunesNo ratings yet

- Audio Tda8510j Spec enDocument16 pagesAudio Tda8510j Spec envetchboyNo ratings yet

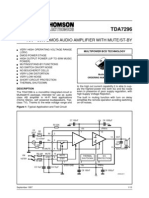

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocument10 pages4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 pagesTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNo ratings yet

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocument14 pagesDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNo ratings yet

- Tda 7296Document14 pagesTda 7296Mayra GonzálezNo ratings yet

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocument14 pagesDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNo ratings yet

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pages120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNo ratings yet

- 30W Bridge Car Radio Amplifier: DescriptionDocument10 pages30W Bridge Car Radio Amplifier: DescriptionvetchboyNo ratings yet

- TDA 2822M CircuitoDocument11 pagesTDA 2822M CircuitoDATA24No ratings yet

- Tda 7265 2 x25 WDocument12 pagesTda 7265 2 x25 WJavier CanaviriNo ratings yet

- Features: Stereo 330mW Audio Power Amp With ShutdownDocument9 pagesFeatures: Stereo 330mW Audio Power Amp With ShutdownvetchboyNo ratings yet

- 10W Car Radio Audio Amplifier: DescriptionDocument11 pages10W Car Radio Audio Amplifier: DescriptionvetchboyNo ratings yet

- pt2388 (v1Document18 pagespt2388 (v1vetchboy0% (1)

- LM124/224/324/324A/ SA534/LM2902: Low Power Quad Op AmpsDocument12 pagesLM124/224/324/324A/ SA534/LM2902: Low Power Quad Op AmpsvetchboyNo ratings yet

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 pagesTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument13 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Angus Electronics Company Limited: PT2323 DescriptionDocument18 pagesAngus Electronics Company Limited: PT2323 DescriptionvetchboyNo ratings yet

- Audio Tas5100a Spec enDocument15 pagesAudio Tas5100a Spec envetchboyNo ratings yet

- Angus Electronics Company Limited: PreliminaryDocument18 pagesAngus Electronics Company Limited: PreliminaryvetchboyNo ratings yet

- 2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesDocument7 pages2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesvetchboyNo ratings yet

- 2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesDocument7 pages2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesvetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument9 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Dual Operational Amplifiers: Technical DataDocument4 pagesDual Operational Amplifiers: Technical DatavetchboyNo ratings yet

Angus Electronics Company Limited: PT2323 Description

Angus Electronics Company Limited: PT2323 Description

Uploaded by

vetchboyOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Angus Electronics Company Limited: PT2323 Description

Angus Electronics Company Limited: PT2323 Description

Uploaded by

vetchboyCopyright:

Available Formats

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Description

PT2323 is a 6-Channel Audio Selector utilizing CMOS Technology specially designed for Home Theater System.

It provides a built-in 2-Channel to 6-Channel Translator, which can directly mix traditional stereo channel to

simulate a 6-Channel audio output. Single power supply (9V), I2C Bus Interface as well as very low Total

Harmonic Distortion (THD < 0.005%) and other features are incorporated into a single chip thereby providing

very high performance. Pin assignments and application circuit are optimized for easy PCB layout and cost saving

advantages.

Features

§ Supply Voltage: 9V

§ 4 Stereo Inputs

§ One 6-Channel Input

§ Maximum Input Voltage: 3.75Vrms (1kHz, THD<1%)

§ Low Total Harmonic Distortion, THD<0.005% (1kHz, 0.2Vrms)

§ Low Noise: No<6 uVrms

§ I2C Bus Interface

§ Available in 28 Pins, DIP or SOP Package

Applications

§ AV System

§ Mini Compo

§ Car Stereo

§ Multi-Media Audio Systems

PT2323 pre 1.0 Page 1 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Block Diagram

6-CH IN

FL FR CT SUB SL SR

L1 MUTE FL

L2

L3 MUTE FR

L4 FL

FR

MUTE CT

2-CH CT

to 6-CH 6-CH

6-CH SUB SWITCH OUT

CONVERTER SL

MUTE SUB

SR

R1

R2 MUTE SL

R3

MUTE SR

R4

CONTROL SDA I2C BUS

REF UNIT SCL

MIXO LPFI LPFO

+

VCC GND

PT2323 pre 1.0 Page 2 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Pin Configuration

L1 R1

L2 R2

L3 R3

L4 R4

FLI LPF_I

FRI LPF_O

CTI FLO

SUBI FRO

SLI CTO

SRI SUBO

MIXO SLO

VCC SRO

REF SCL

GND SDA

PT2323

PT2323 pre 1.0 Page 3 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Pin Description

Pin Name I/O Description Pin No.

L1 I Left Channel Input Pin No. 1 1

L2 I Left Channel Input Pin No. 2 2

L3 I Left Channel Input Pin No. 3 3

L4 I Left Channel Input Pin No. 4 4

FLI I 6-Ch Front Left Channel Input Pin 5

FRI I 6-Ch Front Right Channel Input Pin 6

CTI I 6-Ch Center Channel Input Pin 7

SUBI I 6-Ch Subwoofer Channel Input Pin 8

SLI I 6-Ch Rear Left Channel Input Pin 9

SRI I 6-Ch Rear Right Channel Output Pin 10

MIXO O L+R Mixed Input Pins 11

VCC - Positive Power Supply 12

REF O Reference Voltage (1/2 Vcc) 13

GND - Ground Pin 14

2

SDA I I C Control Data Input Pin 15

SCL I I2C Control Bus Clock Input Pin 16

SRO O 6-Ch Rear Right Channel Output Pin 17

SLO O 6-Ch Rear Left Channel Output Pin 18

SUBO O 6-Ch Subwoofer Channel Output Pin

CTO O 6-Ch Center Channel Output Pin 20

FRO O 6-Ch Front Right Channel Output Pin 21

FLO O 6-Ch Front Left Channel Output Pin 22

LPF_O O Low Pass Filter Output Pin 23

LPF_I I Low Pass Filter Input Pin 24

R4 I Right Channel Input Pin No. 4 25

R3 I Right Channel Input Pin No. 3 26

R2 I Right Channel Input Pin No. 2 27

R1 I Right Channel Input Pin No. 1 28

PT2323 pre 1.0 Page 4 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Functional Description

Bus Interface

Data are transmitted to and from the microprocessor to the PT2323 via the SDA and SCL. The SDA and SCL

make up the BUS Interface. It should be noted that the pull-up resistors must be connected to the positive supply

voltage.

Data Validity

A data on the SDA Line is considered valid and stable only when the SCL Signal is in HIGH State. The HIGH

and LOW States of the SDA Line can only change when the SCL signal is LOW. Please refer to the figure below.

Start and Stop Conditions

A Start Condition is activated when 1) the SCL is set to HIGH and 2) SDA shifts from HIGH to LOW State.

The Stop Condition is activated when 1) SCL is set to HIGH and 2) SDA shifts from LOW to HIGH State.

Please refer to the timing diagram below.

PT2323 pre 1.0 Page 5 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Byte Format

Every byte transmitted to the SDA Line consists of 8 bits. Each byte must be followed by an Acknowledge Bit.

The MSB is transmitted first.

Acknowledge

During the Acknowledge Clock Pulse, the master (µP) puts a resistive HIGH level on the SDA Line. The

peripheral (audio processor) that acknowledges has to pull-down (LOW) the SDA line during the Acknowledge

Clock Pulse so that the SDA Line is in a Stable Low State during this Clock Pulse. Please refer to the diagram

below.

The audio processor that has been addressed has to generate an Acknowledge after receiving each byte,

otherwise, the SDA Line will remain at the High Level during the ninth (9th) Clock Pulse. In this case, the master

transmitter can generate the STOP Information in order to abort the transfer.

Transmission without Acknowledge

If you want to avoid the acknowledge detection of the audio processor, a simpler µP transmission may be used.

Wait one clock and do not check the slave acknowledge of this same clock then send the new data. If you use this

approach, there are greater chances of faulty operation as well as decrease in noise immunity.

PT2323 pre 1.0 Page 6 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Interface Protocol

The interface protocol consists of the following:

· A Start Condition

· A Chip Address Byte = 10010100

· ACK = Acknowledge Bit

· A Sub-Address

· A Data Byte

· A Stop Condition

Please refer to the diagram below:

PT2323 Address

MSB FIRST BYTE LSB MSB LSB MSB LSB

AC AC AC

START 1 0 0 1 0 1 0 0 DATA DATA STOP

K K K

DATA TRANSMITTED (N-BYTES+ACKNOWLEDGE)

Note: ACK = Acknowledge Bit

Maximum Clock Speed = 100k bits / second

Software Specification

PT2323 ADDRESS

PT2323 Address is shown below.

1 0 0 1 0 1 0 0

MSB LSB

PT2323 pre 1.0 Page 7 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

I2C Bus Start-up timing

After Power is turned ON, PT2323 needs to wait for a short time in order to insure stability. This waiting period

is relative to the value of Cref. As the Cref value becomes bigger, the waiting time period for PT2323 to be able

to send I2 C Bus Signal effectively becomes longer.

For example, if Cref = 10µF, after power is turned ON, the waiting time period for PT2322 to send I 2 C Bus Signal

is at least 300 ms. If the waiting time period is less than 300 ms, I2 C Control may fail. Please refer to the diagram

below.

V

Power ON

VDD

at least 300 ms

SDA/SCL

Data Bytes

MSB LSB Function

1 1 0 0 C3 C2 C1 C0 Input Switch

1 1 1 1 0 0 0 M FL Mute

1 1 1 1 0 0 1 M FR Mute

1 1 1 1 0 1 0 M CT Mute

1 1 1 1 0 1 1 M SUB Mute

1 1 1 1 1 0 0 M SL Mute

1 1 1 1 1 0 1 M SR Mute

1 1 1 1 1 1 1 M All CH Mute

Notes: M = 1 (Mute Function Enabled)

M=0 (Mute Function Disabled)

PT2323 pre 1.0 Page 8 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

C3 C2 C1 C0 Function

1 0 0 0 Input Stereo Group 4

1 0 0 1 Input Stereo Group 3

1 0 1 0 Input Stereo Group 2

1 0 1 1 Input Stereo Group 1

0 1 1 1 6-Ch Input

Notes: 1. Stereo Group 1 consists of L1 and R1.

2. Stereo Group 2 consist of L2, R2.

3. Stereo Group 3 consists of L3, R3.

4. Stereo Group 4 consists of L4, R4.

Add-On Feature

MSB LSB Function

1 1 0 1 0 0 0 0 Enhanced Surround Function Active

1 1 0 1 0 0 0 1 Enhanced Surround Function Disabled

1 0 0 1 0 0 0 0 Mixed Channel (-6dB) ON

2-Ch to 6-Ch Translation

PT2323 has a built-in 2-Ch to 6-Ch Translator. Any one of the stereo inputs -- L1/R1, L2/R2, L3/R3, L4/R4

may be selected and converted to a 6-channel output. If the 6-Channel Input is selected, the audio signal just

directly flows through the 6-channel output, it is not internally processed by PT2323.

During a 2-Ch to 6-Ch translation processes, the original Left and Right signals are also directly outputted. and

only the Center (CT), Subwoofer (SUB), Rear Right (SR) and the Rear Left (SL) signals are processed by the

PT2323.

PT2323 provides individual mute functions which prevent output signals from unused stereo input sources from

being heard.

PT2323 pre 1.0 Page 9 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Surround Enhance Function

When the 2-Ch to 6-Ch Translation is enabled, and the Enhanced Surround Function is turned ON, then the

Surround Function is enhanced. However, it is suggested that the enhanced surround function be turned OFF

when using a stereo input / output channel in order to ensure better crosstalk or stereo separation.

Under the 6-Ch Input, this function is not active. The signals from the 6-Ch input just directly flows through.

Mixed Channel

The Mixed channels consists of the CT and the SUB channels. These 2 channels (CT and SUB) are mixed via the

L and R signals. The Mixed Channel is set to -6dB gain since the original L and R channel signals directly flow

though output and still includes the CT and the SUB signals. The I2C may be used to turn On the mixed channel.

Subwoofer

PT2323 provides an internal OP AMP for the Subwoofer Crossover. An external RC Sallen Key Type Low

Pass Filter may be added. Please refer to the diagram below.

From MIXO C1

R R (Pin24) (Pin25)

C2 LPF_I LPF_O

PT2323 +

- To SUB

PT2323 pre 1.0 Page 10 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Subwoofer Crossover Frequency Response Curve

+5

+0

-5

-10

-15

d -20

B

V -25

-30

-35

-40

-45

-50

20 50 100 200 500 1k 2k 5k 10k 20k

Hz

Notes: 1. R=24KΩ (where R is the resistor in the Subwoofer Cross-Over Circuit)

2. : Cross-Over Frequency = 280Hz,C1=0.047uf,C2=0.018uf.

3 : Cross-Over Frequency = 200Hz,C1=0.068uf,C2=0.027uf.

4 : Cross-Over Frequency = 120Hz,C1=0.1uf,C2=0.047uf.

5. C1, C2=Low Pass Filter Capacitor

Absolute Maximum Rating

PT2323 pre 1.0 Page 11 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Symbol Parameter Rating Unit

Vs Operating Voltage 12 V

Tamb Ambient Temperature -40 ~ 85 ℃

Tstg Storage Temperature -55 ~ +150 ℃

Electrical Parameters

Unless otherwise stated:Tamb=25℃, Vcc=9V, RL=100KΩ, f=1kHz)

Symbol Parameter Condition Min. Typ. Max. Unit

VCC Supply Voltage 4.5 9 - V

IS Supply Current - 4 - mA

Input=0.2Vrms

THD Total Harmonic Distortion 0.001 0.005 - %

A-Weighting

RIS =600Ω

NO Output Noise - 6 - μV

A-Weighting

0dB=1Vrms

SN Signal to Noise Ratio - 100 104 dB

A-Weighting

RL=50KΩ, 1KHz

VIMAX Maximum Input Voltage - 3.75 - Vrms

THD=1%

GN Voltage Gain F=1KHz -1 0 +1 dB

RON Internal Switch Impedance - 200 - Ω

CT Cross Talk Vin=1Vrms - 90 - dB

CS Channel Separation Vin=1Vrms - 80 - dB

Vin=1Vrms

MUTE Mute Function - 95 - dB

A-Weighting

VIH I2C Bus High Level Input Voltage 0.7 VDD - - V

2

VIL I C Bus Low Level Input Voltage - - 0.3 VDD V

TINIT I2C Bus Initial Time CREF=10μf - 300 - ms

Application Circuit

PT2323 pre 1.0 Page 12 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

10uF

+ R-CH1

10uF 100K

L-CH1

100K

L1 R1 10uF+

R-CH2

10uF 100K

L-CH2

100K

L2 R2 10uF +

R-CH3

10uF 100K

L-CH3 L3 R3 10uF

+ R-CH4

100K

10uF 100K

L-CH4

100K

L4 R4

10uF From MIXO

100K

FLI LPF_I C2

<<

10uF

C1

100K

FRI LPF_O

10uF 270Ω∗ 10uF

+

6CH

100K

CTI FLO 100K

IN 10uF 270Ω∗

+ 10uF

100K SUBI FRO 100K

10uF 270Ω∗

+ 10uF

100K

SLI CTO 100K 6-CH

10uF 270Ω∗ OUT

+ 10uF

SRI SUBO 100K

100K

270Ω∗ 10uF

<< MIXO SLO +

100K

9V

270Ω∗

VCC + 10uF

SRO 100K

REF SCL

10uF

47uF

0.1

GND SDA

I2C BUS

Note: * = An external resistor (R=270Ω) must be connected in series to each of the output pins (FLO, FRO,

CTO, SUBO, SLO, SRO) and must be as close as possible to the PT2323 chip.

PT2323 pre 1.0 Page 13 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Package Information

28 Pins, DIP Package (600 mil)

Symbol Min. Nom. Max.

A - 0.250

A1 0.015 -

A2 0.125 0.195

B 0.014 0.022

B1 0.030 0.070

C 0.008 0.015

D1 0.005 -

E 0.600 0.625

E1 0.485 0.580

e 0.100 BSC.

PT2323 pre 1.0 Page 14 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

eA 0.600 BSC.

eB - 0.700

L 0.115 0.200

D 1.380 1.565

Notes:

1. Controlling dimension:INCH

2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

3. Dimensions A, A1 and L are measured with the package seated in JEDEC Seating Plane Gauge GS-3.

4. “D” & “E1” dimensions, for ceramic packages, include allowance for glass overrun and meniscus and lid to

base mismatch.

5. “D” & “E1” dimensions for plastic package, do not includes mold flash or protrusion. Mold flash or

protrusions shall not exceed 0.01 inch. (0.25mm).

6. “E” and “eA” measured with the leads constrained to be perpendicular to plane T.

7. “eB” and “eC” are measured at the lead tips with the loads un-constrained. “eC” must be zero or greater.

8. “N” is the maximum quantity of lead positions. (N=28)

9. Corner leads (1, N, N/2, and N/2+1) may be configured as shown in Figure 2.

10. Pointed our rounded leads tips are preferred to ease insertion.

11. For automatic insertion, any rained irregularity on the top surface (step, mess, etc.) shall b symmetrical about

the lateral and longitudinal package centerlines.

12. Refer JEDEC MS-011 Variation AB.

JEDEC is the trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2323 pre 1.0 Page 15 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

28 Pins, SOP Package (300 mil)

Symbol Min. Nom. Max.

A 0.0926 0.1043

A1 0.0040 0.0118

B 0.013 0.20

C 0.0091 0.0125

E 0.2914 0.2992

e 0.050 BSC

H 0.394 0.419

h 0.010 0.029

L 0.016 0.050

D 0.6969 0.7125

α 0° 8°

PT2323 pre 1.0 Page 16 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Notes:

1. Refer to applicable symbol list.

2. Dimensioning and tolerancing per ANSI Y 14.5M-1982.

3. Dimension “D” does not include mold flash, protrusions or gate burrs. Mold flash, protrusions and gate burrs

shall not exceed 0.15mm (0.06 in) per side.

4. Dimension “E” does not include inter-lead flash or protrusions. Inter-lead flash and protrusions shall not

exceed 0.25mm (0.10 in) per side.

5. The chamfer on the body is optional. If it is not present, a visual index feature must be located within the

crosshatched area.

6. “L” is the length of terminal for soldering to a substrate.

7. “N” is the number of terminal positions. (N=28)

8. Terminal numbers are shown for reference only.

9. The lead width “B” as measured 0.36mm (0.14 in) or greater above the seating plane, shall not exceed a

maximum value of 0.61mm (0.24 in).

10. Controlling dimension: INCHES.

11. Refer to JEDEC MS-013 Variation AE.

JEDEC is the trademark of JEDEC SOLID STATE TECHNOLOGY ASSOCIATION.

PT2323 pre 1.0 Page 17 Updated Oct. 2001

ANGUS ELECTRONICS COMPANY LIMITED

Princeton Technology Corp. Tel: (852) 2345 0540 Fax: (852) 2345 9948 Web Site: www.angus.com.hk

6-Ch Audio Selector Preliminary PT2323

Revision History

Date Revision Document No. Remarks

Oct. 11, 2001 01 PT2323 pre 1.0 Approval No. 011003

PT2323 pre 1.0 Page 18 Updated Oct. 2001

You might also like

- Diagrama cfd-rg880cpDocument14 pagesDiagrama cfd-rg880cpMarvin Leon Alegria100% (1)

- Av36d303 SchematicDocument30 pagesAv36d303 SchematicLuis MorenoNo ratings yet

- Data Pin FBT TV CinaDocument7 pagesData Pin FBT TV CinaKristen JuarezNo ratings yet

- Aiwa Av-D58-U SMDocument34 pagesAiwa Av-D58-U SMmiguel angel jaramilloNo ratings yet

- AbrilDocument11 pagesAbrilWilfrido Escobar ZuñigaNo ratings yet

- DVD Receiver System: Service ManualDocument73 pagesDVD Receiver System: Service ManualgondifNo ratings yet

- FBTDocument22 pagesFBTsalmanNo ratings yet

- Data FlybackDocument4 pagesData FlybackBanaNiBebang100% (1)

- (Codientu - Org) - 29Q317B, CHASSIS CW4Document14 pages(Codientu - Org) - 29Q317B, CHASSIS CW4GioVoTam100% (1)

- Data Pin Plyback Dan PersamaannyaDocument8 pagesData Pin Plyback Dan PersamaannyaMoch RofiiiqNo ratings yet

- Persamaan FBTDocument4 pagesPersamaan FBTAnam Elektronik HpaiNo ratings yet

- Eht CTVDocument34 pagesEht CTVPKPNo ratings yet

- Philips - Chassis L01.1A AC PDFDocument26 pagesPhilips - Chassis L01.1A AC PDFOsvaldo Dutto100% (1)

- Data Pin FlybackDocument4 pagesData Pin FlybackRene100% (3)

- Circuit Diagram 12-1-6Document1 pageCircuit Diagram 12-1-6stolllle67% (3)

- Sanyo ct21ks2 Chassis Fc8-A PDFDocument37 pagesSanyo ct21ks2 Chassis Fc8-A PDFKaray TehnikNo ratings yet

- Samsung EHTDocument8 pagesSamsung EHTshafiuddin7326No ratings yet

- Flybacks HR ReplacementDocument17 pagesFlybacks HR Replacementlastfriendsv100% (7)

- Data Pin FBT 2Document6 pagesData Pin FBT 2Rene100% (2)

- Fly BackDocument1 pageFly BackJose Gregorio Sanchez AraujoNo ratings yet

- Data Pin FlybackDocument5 pagesData Pin FlybackWahyu Ilhami100% (1)

- WB Gram Panchayat Previous Year Question Papers PDFDocument48 pagesWB Gram Panchayat Previous Year Question Papers PDFRitam AichNo ratings yet

- LTN140AT07Document30 pagesLTN140AT07JhonSalchichonNo ratings yet

- Tmpa 8859 Service Manual: ContentDocument14 pagesTmpa 8859 Service Manual: ContentNeto Garcia100% (1)

- Pin Flyback Dilihat / Dihitung Dari Bawah Searah Jarum JamDocument52 pagesPin Flyback Dilihat / Dihitung Dari Bawah Searah Jarum JamJuan Carlos RangelNo ratings yet

- Ic Osc FuenteDocument6 pagesIc Osc FuenteLeonardo Flei100% (1)

- Aoc Le32a1330-61 Le40a1330-61 LCD TV PDFDocument87 pagesAoc Le32a1330-61 Le40a1330-61 LCD TV PDFtrietNo ratings yet

- Okok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFDocument13 pagesOkok Sony - kv-2197m3 - Cxp85220a - Tda8375 - str-6707 - La7830 - Ta8248k PDFAloui Zakaria100% (1)

- Persamaan Flyback TVDocument10 pagesPersamaan Flyback TVAndika100% (1)

- TC 21gx20m MalaysiaDocument29 pagesTC 21gx20m MalaysiaChandan Tripathi100% (4)

- Data Pin Flyback LengkapDocument49 pagesData Pin Flyback LengkapAhmad Humaidi67% (3)

- Service Manual Samsung CS 29M40MH S16A Sdiag 10 A3Document4 pagesService Manual Samsung CS 29M40MH S16A Sdiag 10 A3Edgar AdonisNo ratings yet

- DATA PIN KAKI PLAYBEAKTV POLYTRON - FacebookDocument22 pagesDATA PIN KAKI PLAYBEAKTV POLYTRON - FacebookÁngel TapiaNo ratings yet

- Service Manual: Model: HT-2199 (Europe)Document48 pagesService Manual: Model: HT-2199 (Europe)Eze KielNo ratings yet

- TDA8375ADocument73 pagesTDA8375Asontuyet82No ratings yet

- TV Servicing Remote CodeDocument4 pagesTV Servicing Remote CodeVenkatesh Subramanya100% (1)

- Sharp Part ChassisDocument2 pagesSharp Part Chassiswatcharen100% (1)

- Flyback Monitor 3Document17 pagesFlyback Monitor 3Skumar Soni100% (1)

- Int 26 32 A-Z Magmeet MLT-688 SchematicDocument4 pagesInt 26 32 A-Z Magmeet MLT-688 SchematicMukesh Thakkar100% (5)

- Data Flyback TVDocument12 pagesData Flyback TVAntok DoankNo ratings yet

- TV Service ModeDocument26 pagesTV Service Modevideoson100% (5)

- JVC CA DX t9, DX t7, DX t5Document31 pagesJVC CA DX t9, DX t7, DX t5Roosevelt Vega SanchezNo ratings yet

- Persamaan Flyback TVDocument12 pagesPersamaan Flyback TVAzka TronikNo ratings yet

- Sanyo CM29FS2 FB1B PDFDocument41 pagesSanyo CM29FS2 FB1B PDFJerald D'costaNo ratings yet

- TV Flyback Transformer Datasheet List - Belajar SEODocument5 pagesTV Flyback Transformer Datasheet List - Belajar SEOempeeno10% (1)

- Remove Inverter Protection MethodDocument1 pageRemove Inverter Protection MethodmontepincioNo ratings yet

- Transistores SMD Codes Beginning With 'C'Document3 pagesTransistores SMD Codes Beginning With 'C'carlosNo ratings yet

- Toshiba TV 29AS42 Service ManualDocument38 pagesToshiba TV 29AS42 Service ManualLuthvi SanjayaNo ratings yet

- MC 84A ChassisDocument19 pagesMC 84A ChassisKapila Gunawardena100% (1)

- Description: 6-Ch Audio Selector PT2323Document17 pagesDescription: 6-Ch Audio Selector PT2323panjoelsNo ratings yet

- Parts Reference List: Brother Laser MFCDocument41 pagesParts Reference List: Brother Laser MFCNebi aktaşNo ratings yet

- Casio AP-60R Service ManualDocument34 pagesCasio AP-60R Service ManualMario Gabriel MoralliNo ratings yet

- PL Eclfb e Ver7Document42 pagesPL Eclfb e Ver7AgostinoNo ratings yet

- Schematic Diagrams: KD-G455, KD-G405Document5 pagesSchematic Diagrams: KD-G455, KD-G405heyjuNo ratings yet

- DCP 9030CDNL3510CDWL3517CDW - DCP L3550CDWL3551CDW - HL L3290CDW - MFC 9150CDN9350CDW - MFC L3710CWL3730CDNL3735CDN - MFC L3745CDWL3750CDWL3770CDW PDFDocument39 pagesDCP 9030CDNL3510CDWL3517CDW - DCP L3550CDWL3551CDW - HL L3290CDW - MFC 9150CDN9350CDW - MFC L3710CWL3730CDNL3735CDN - MFC L3745CDWL3750CDWL3770CDW PDFStefanGarnetNo ratings yet

- Ax5505 r1.1 AxeliteDocument12 pagesAx5505 r1.1 AxeliteSaul UribeNo ratings yet

- pt2388 (v1Document18 pagespt2388 (v1vetchboy0% (1)

- PTP6005 LP-BK-F (5000T) - 1P-KB-WO/COV LG: 3 Way Toggle Switch 101-1D CRP Knob:BkDocument1 pagePTP6005 LP-BK-F (5000T) - 1P-KB-WO/COV LG: 3 Way Toggle Switch 101-1D CRP Knob:BkmisterNo ratings yet

- CR50 PDFDocument1 pageCR50 PDFmisterNo ratings yet

- IO - LIST - 7K6S0607 - Rev06 - TSQ-B RPIO (CT)Document8 pagesIO - LIST - 7K6S0607 - Rev06 - TSQ-B RPIO (CT)Akun TestNo ratings yet

- 2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsDocument10 pages2 X 3 W Dual/Quad Power Amplifier For Car Radio: ProtectionsJosé VidalNo ratings yet

- CD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)Document16 pagesCD-R/RW Playback Shock Proof CDP Chipset Specification: (Full Digit LCD Model)vetchboyNo ratings yet

- Tda7294 PDFDocument16 pagesTda7294 PDFRoger NunesNo ratings yet

- Audio Tda8510j Spec enDocument16 pagesAudio Tda8510j Spec envetchboyNo ratings yet

- 4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionDocument10 pages4 X 18W Bridge Car Radio Amplifier: Protections: DescriptionvetchboyNo ratings yet

- TDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierDocument9 pagesTDA7384A: 4 X 35W Quad Bridge Car Radio AmplifierGerardo Moreno RenteriaNo ratings yet

- Digital Controlled Stereo Audio Processor With Loudness: DescriptionDocument14 pagesDigital Controlled Stereo Audio Processor With Loudness: DescriptionvetchboyNo ratings yet

- Tda 7296Document14 pagesTda 7296Mayra GonzálezNo ratings yet

- Dual Btl/Quad Power Amplifier For Car Radio: ProtectionsDocument14 pagesDual Btl/Quad Power Amplifier For Car Radio: ProtectionsvetchboyNo ratings yet

- 120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyDocument13 pages120V - 100W Dmos Audio Amplifier With Mute/St-By: Multipower BCD TechnologyvetchboyNo ratings yet

- 30W Bridge Car Radio Amplifier: DescriptionDocument10 pages30W Bridge Car Radio Amplifier: DescriptionvetchboyNo ratings yet

- TDA 2822M CircuitoDocument11 pagesTDA 2822M CircuitoDATA24No ratings yet

- Tda 7265 2 x25 WDocument12 pagesTda 7265 2 x25 WJavier CanaviriNo ratings yet

- Features: Stereo 330mW Audio Power Amp With ShutdownDocument9 pagesFeatures: Stereo 330mW Audio Power Amp With ShutdownvetchboyNo ratings yet

- 10W Car Radio Audio Amplifier: DescriptionDocument11 pages10W Car Radio Audio Amplifier: DescriptionvetchboyNo ratings yet

- pt2388 (v1Document18 pagespt2388 (v1vetchboy0% (1)

- LM124/224/324/324A/ SA534/LM2902: Low Power Quad Op AmpsDocument12 pagesLM124/224/324/324A/ SA534/LM2902: Low Power Quad Op AmpsvetchboyNo ratings yet

- TA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyDocument18 pagesTA2041 Four Channel Class-T Digital Audio Amplifier Using Digital Power Processing (DPP) TechnologyvetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument13 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Angus Electronics Company Limited: PT2323 DescriptionDocument18 pagesAngus Electronics Company Limited: PT2323 DescriptionvetchboyNo ratings yet

- Audio Tas5100a Spec enDocument15 pagesAudio Tas5100a Spec envetchboyNo ratings yet

- Angus Electronics Company Limited: PreliminaryDocument18 pagesAngus Electronics Company Limited: PreliminaryvetchboyNo ratings yet

- 2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesDocument7 pages2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesvetchboyNo ratings yet

- 2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesDocument7 pages2-Channel Preamplifier For Car Stereo: Package Dimensions FeaturesvetchboyNo ratings yet

- Description: Angus Electronics Company LimitedDocument9 pagesDescription: Angus Electronics Company LimitedvetchboyNo ratings yet

- Dual Operational Amplifiers: Technical DataDocument4 pagesDual Operational Amplifiers: Technical DatavetchboyNo ratings yet