Professional Documents

Culture Documents

Parameters

Parameters

Uploaded by

Milo LatinoCopyright:

Available Formats

You might also like

- ADE Cycle-IDocument18 pagesADE Cycle-InadeemNo ratings yet

- Design An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KDocument21 pagesDesign An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KMangaiyarkarasi VengatachalamNo ratings yet

- Introduction To Logic Design Lab: And, Or, Not Nand and Nor GatesDocument5 pagesIntroduction To Logic Design Lab: And, Or, Not Nand and Nor GatesErnest Omorose OsemwegieNo ratings yet

- Exp 03Document3 pagesExp 03Captain Jack SparrowNo ratings yet

- Lab 2Document7 pagesLab 2楊明倫No ratings yet

- IntroductionDocument13 pagesIntroductionnokia58No ratings yet

- Basic Electronics LAB ManualDocument32 pagesBasic Electronics LAB ManualHasith VankadaruNo ratings yet

- I / I (V Constant) : PNP Transistor Aim: To Determine The Collector and Transfer CharacteristicsDocument3 pagesI / I (V Constant) : PNP Transistor Aim: To Determine The Collector and Transfer CharacteristicsSukhwinder Singh GillNo ratings yet

- Study OF Transistor Characteristics: 8-Shrikant Kunj, M.N. Patankar Marg, Kurla (W) MUMBAI, 400070. PH-09869112159Document11 pagesStudy OF Transistor Characteristics: 8-Shrikant Kunj, M.N. Patankar Marg, Kurla (W) MUMBAI, 400070. PH-09869112159Yogesh KumarNo ratings yet

- EE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 4: Current Source, Current Mirror, and Differential PairDocument4 pagesEE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 4: Current Source, Current Mirror, and Differential PairSruthiNo ratings yet

- PE & S Lab Manual (Student Copy)Document67 pagesPE & S Lab Manual (Student Copy)Chunduri Rambabu100% (4)

- An Ultra-Low Power Voltage Reference For Passive UHF RFID TagDocument5 pagesAn Ultra-Low Power Voltage Reference For Passive UHF RFID TagChennamsetyNo ratings yet

- Emitter Coupled LogicDocument3 pagesEmitter Coupled LogicfoggybluueNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- 07 - Experiment Dac J09Document11 pages07 - Experiment Dac J09Beatrice ShokryNo ratings yet

- Charoli 26Document7 pagesCharoli 26Hakimuddin BohariNo ratings yet

- Review 1 ManuvalDocument25 pagesReview 1 ManuvalvikasNo ratings yet

- Astable Multivibrator ExperimentDocument5 pagesAstable Multivibrator ExperimentShivakumar goud100% (1)

- Manipal Institute of Technology: Reg. NoDocument2 pagesManipal Institute of Technology: Reg. Nodreamivory29No ratings yet

- Compter ModellingDocument7 pagesCompter Modellingahmadgafarov1No ratings yet

- Connecting The Circuit On Bread Board As Per The Circuit DiagramDocument3 pagesConnecting The Circuit On Bread Board As Per The Circuit Diagramhmpudur1968No ratings yet

- PDC Assignment IDocument4 pagesPDC Assignment IathomeNo ratings yet

- Experiment 2 BJT SwitchDocument6 pagesExperiment 2 BJT Switchprop_kcp50% (2)

- Worksheet For EEE and ECE 3rd-1 PDFDocument3 pagesWorksheet For EEE and ECE 3rd-1 PDFnigus hailuNo ratings yet

- Astable CircuitsDocument9 pagesAstable CircuitsRavindranath ShrivastavaNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Atul SainiNo ratings yet

- Lab 1-Bjt AmplifierDocument8 pagesLab 1-Bjt Amplifierhasnain3257100% (1)

- Ae Exp 9 To Design Monostable Multivibrators Using 555 IcDocument6 pagesAe Exp 9 To Design Monostable Multivibrators Using 555 IcPriyanshu KumawatNo ratings yet

- Ece Ade Manual 500 CopiesDocument79 pagesEce Ade Manual 500 CopiesRajkumarNo ratings yet

- CO#1 Describe, Analyze, and Design of Basic BJT & NMOS Differential AmplifierDocument6 pagesCO#1 Describe, Analyze, and Design of Basic BJT & NMOS Differential AmplifierCJ CHNo ratings yet

- Electronic OscillatorsDocument2 pagesElectronic OscillatorsAlessio CapitanelliNo ratings yet

- EC - Lab Manul With Viva Questions and AnswersDocument83 pagesEC - Lab Manul With Viva Questions and AnswerssunandaalurNo ratings yet

- Electronic Instrumentation (EI 333) Unit - IDocument17 pagesElectronic Instrumentation (EI 333) Unit - IGanesh SeetharamanNo ratings yet

- Lab FinalDocument21 pagesLab FinalG ManNo ratings yet

- Circuit Diagram: Monostable Multivibrator:: +VCC 5VDocument25 pagesCircuit Diagram: Monostable Multivibrator:: +VCC 5VKAVIKRISHNAVEL TNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- Ieai Lab File: Name: Yuvan Saroya ROLL NO.: 2K18/PSY/16 M.Tech Psy 1St SemDocument26 pagesIeai Lab File: Name: Yuvan Saroya ROLL NO.: 2K18/PSY/16 M.Tech Psy 1St SemNitin SharmaNo ratings yet

- Timing Circuits Using Timer Ic 555 ProblemDocument7 pagesTiming Circuits Using Timer Ic 555 ProblemDevi Sree JeevanandhamNo ratings yet

- List of Experiments: Ic Applications Lab Minimum Twelve Experiments To Be ConductedDocument6 pagesList of Experiments: Ic Applications Lab Minimum Twelve Experiments To Be ConductedAmy OliverNo ratings yet

- Lab #1 Logic Gates: ObjectiveDocument6 pagesLab #1 Logic Gates: ObjectiveZbiggNo ratings yet

- AEC Lab ManualDocument70 pagesAEC Lab ManualRohan BoseNo ratings yet

- Electronic Circuits Question PaperDocument3 pagesElectronic Circuits Question PaperRaja SekharNo ratings yet

- Ade Lab ManualDocument79 pagesAde Lab ManualVinod KannaNo ratings yet

- Introduction To Logic Gates Exp2Document11 pagesIntroduction To Logic Gates Exp2Tamim ANo ratings yet

- EC1 Lab Exp3 PDFDocument2 pagesEC1 Lab Exp3 PDFRitu RoyNo ratings yet

- V, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyDocument2 pagesV, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyraghavbhatiaNo ratings yet

- (Ce) Transistor Characteristics in Common Emitter ConfigurationDocument7 pages(Ce) Transistor Characteristics in Common Emitter Configurationjassisc100% (1)

- MOSFET Experiment GuideDocument3 pagesMOSFET Experiment GuidemangyanNo ratings yet

- E.G. Per Set/group of StudentDocument4 pagesE.G. Per Set/group of StudentKiritoNo ratings yet

- ECE 2201 Experiment 1 - 4Document13 pagesECE 2201 Experiment 1 - 4Deepak SharmaNo ratings yet

- Lab Repot 5 - TransistorDocument8 pagesLab Repot 5 - TransistorUmmu Umar Wa Aisyah100% (2)

- Laboratory Manual Course Code Ece254 Course Title: Unified Electronics Laboratory-IDocument67 pagesLaboratory Manual Course Code Ece254 Course Title: Unified Electronics Laboratory-IKaran SainiNo ratings yet

- NEP2020 ISEM ManualElectricallabDocument28 pagesNEP2020 ISEM ManualElectricallabrangooNo ratings yet

- 3-Transistor Characteristics and Amplifier CircuitsDocument11 pages3-Transistor Characteristics and Amplifier CircuitsJudah SnehanNo ratings yet

- 2630-Prathmesh KakadeDocument46 pages2630-Prathmesh KakadeTanmay MhatreNo ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Small, Low Power, 3-Axis 3 G Accelerometer ADXL335: Features General DescriptionDocument16 pagesSmall, Low Power, 3-Axis 3 G Accelerometer ADXL335: Features General DescriptionMilo LatinoNo ratings yet

- C Function AtofDocument1 pageC Function AtofMilo LatinoNo ratings yet

- ProjectDocument1 pageProjectMilo LatinoNo ratings yet

- EjercicioDocument1 pageEjercicioMilo LatinoNo ratings yet

- Design and Simulate A Chronometer As FollowsDocument1 pageDesign and Simulate A Chronometer As FollowsMilo LatinoNo ratings yet

- Data Sheet: ADJD-S311-CR999Document20 pagesData Sheet: ADJD-S311-CR999Milo LatinoNo ratings yet

Parameters

Parameters

Uploaded by

Milo LatinoOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Parameters

Parameters

Uploaded by

Milo LatinoCopyright:

Available Formats

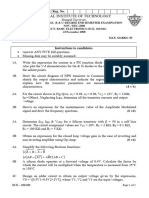

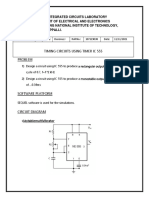

UNIVERSIDAD TECNICA DEL NORTE FACULTAD DE INGENIERIA EN CIENCIAS APLICADAS LABORATORY 1

BASIC PARAMETERS OF LOGICAL GATES

Ic

1. With Q1(transistor 2N3707 or similar) working in the cutoff and saturation regions, design an inverter as in the figure. Apply inV1 a variable voltage from -0,2V. to 5 V. in suitable steps (0,2 V), measure Ic,Ib,V2,Vbe for each value. Repeat the procedure from 5V. to -0,2V.

Sketch: V1 vs Ib Ib Vbe vs Ib V2 vs V1

2. Now using a quad 2-input TTL NAND gate (7400). Implement one inverter in two different ways. As was made above, take suitable measurements to sketch the transfer characteristic of this gate. 3. With the NAND gate as inverter, and using a square wave signal of 5 V. peak, 100 kHz as input, find for this gate: propagation delay times (tpHL, tpLH), rise time ( tR) and fall time (tF). Plot the input and output waves in a common scale.

You might also like

- ADE Cycle-IDocument18 pagesADE Cycle-InadeemNo ratings yet

- Design An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KDocument21 pagesDesign An Amplifier With A Gain of - 10 and Input Resistance of 10k . Ri 10k Av - Rf/Ri - 10 - Rf/10k RF 10 X 10 K 100 KMangaiyarkarasi VengatachalamNo ratings yet

- Introduction To Logic Design Lab: And, Or, Not Nand and Nor GatesDocument5 pagesIntroduction To Logic Design Lab: And, Or, Not Nand and Nor GatesErnest Omorose OsemwegieNo ratings yet

- Exp 03Document3 pagesExp 03Captain Jack SparrowNo ratings yet

- Lab 2Document7 pagesLab 2楊明倫No ratings yet

- IntroductionDocument13 pagesIntroductionnokia58No ratings yet

- Basic Electronics LAB ManualDocument32 pagesBasic Electronics LAB ManualHasith VankadaruNo ratings yet

- I / I (V Constant) : PNP Transistor Aim: To Determine The Collector and Transfer CharacteristicsDocument3 pagesI / I (V Constant) : PNP Transistor Aim: To Determine The Collector and Transfer CharacteristicsSukhwinder Singh GillNo ratings yet

- Study OF Transistor Characteristics: 8-Shrikant Kunj, M.N. Patankar Marg, Kurla (W) MUMBAI, 400070. PH-09869112159Document11 pagesStudy OF Transistor Characteristics: 8-Shrikant Kunj, M.N. Patankar Marg, Kurla (W) MUMBAI, 400070. PH-09869112159Yogesh KumarNo ratings yet

- EE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 4: Current Source, Current Mirror, and Differential PairDocument4 pagesEE 230 - Analog Lab - 2021-22/I (Autumn) Experiment 4: Current Source, Current Mirror, and Differential PairSruthiNo ratings yet

- PE & S Lab Manual (Student Copy)Document67 pagesPE & S Lab Manual (Student Copy)Chunduri Rambabu100% (4)

- An Ultra-Low Power Voltage Reference For Passive UHF RFID TagDocument5 pagesAn Ultra-Low Power Voltage Reference For Passive UHF RFID TagChennamsetyNo ratings yet

- Emitter Coupled LogicDocument3 pagesEmitter Coupled LogicfoggybluueNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- 07 - Experiment Dac J09Document11 pages07 - Experiment Dac J09Beatrice ShokryNo ratings yet

- Charoli 26Document7 pagesCharoli 26Hakimuddin BohariNo ratings yet

- Review 1 ManuvalDocument25 pagesReview 1 ManuvalvikasNo ratings yet

- Astable Multivibrator ExperimentDocument5 pagesAstable Multivibrator ExperimentShivakumar goud100% (1)

- Manipal Institute of Technology: Reg. NoDocument2 pagesManipal Institute of Technology: Reg. Nodreamivory29No ratings yet

- Compter ModellingDocument7 pagesCompter Modellingahmadgafarov1No ratings yet

- Connecting The Circuit On Bread Board As Per The Circuit DiagramDocument3 pagesConnecting The Circuit On Bread Board As Per The Circuit Diagramhmpudur1968No ratings yet

- PDC Assignment IDocument4 pagesPDC Assignment IathomeNo ratings yet

- Experiment 2 BJT SwitchDocument6 pagesExperiment 2 BJT Switchprop_kcp50% (2)

- Worksheet For EEE and ECE 3rd-1 PDFDocument3 pagesWorksheet For EEE and ECE 3rd-1 PDFnigus hailuNo ratings yet

- Astable CircuitsDocument9 pagesAstable CircuitsRavindranath ShrivastavaNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Atul SainiNo ratings yet

- Lab 1-Bjt AmplifierDocument8 pagesLab 1-Bjt Amplifierhasnain3257100% (1)

- Ae Exp 9 To Design Monostable Multivibrators Using 555 IcDocument6 pagesAe Exp 9 To Design Monostable Multivibrators Using 555 IcPriyanshu KumawatNo ratings yet

- Ece Ade Manual 500 CopiesDocument79 pagesEce Ade Manual 500 CopiesRajkumarNo ratings yet

- CO#1 Describe, Analyze, and Design of Basic BJT & NMOS Differential AmplifierDocument6 pagesCO#1 Describe, Analyze, and Design of Basic BJT & NMOS Differential AmplifierCJ CHNo ratings yet

- Electronic OscillatorsDocument2 pagesElectronic OscillatorsAlessio CapitanelliNo ratings yet

- EC - Lab Manul With Viva Questions and AnswersDocument83 pagesEC - Lab Manul With Viva Questions and AnswerssunandaalurNo ratings yet

- Electronic Instrumentation (EI 333) Unit - IDocument17 pagesElectronic Instrumentation (EI 333) Unit - IGanesh SeetharamanNo ratings yet

- Lab FinalDocument21 pagesLab FinalG ManNo ratings yet

- Circuit Diagram: Monostable Multivibrator:: +VCC 5VDocument25 pagesCircuit Diagram: Monostable Multivibrator:: +VCC 5VKAVIKRISHNAVEL TNo ratings yet

- Laboratory Manual Course Code:Ece 201Document41 pagesLaboratory Manual Course Code:Ece 201Er Sacchu SrivastavaNo ratings yet

- Ieai Lab File: Name: Yuvan Saroya ROLL NO.: 2K18/PSY/16 M.Tech Psy 1St SemDocument26 pagesIeai Lab File: Name: Yuvan Saroya ROLL NO.: 2K18/PSY/16 M.Tech Psy 1St SemNitin SharmaNo ratings yet

- Timing Circuits Using Timer Ic 555 ProblemDocument7 pagesTiming Circuits Using Timer Ic 555 ProblemDevi Sree JeevanandhamNo ratings yet

- List of Experiments: Ic Applications Lab Minimum Twelve Experiments To Be ConductedDocument6 pagesList of Experiments: Ic Applications Lab Minimum Twelve Experiments To Be ConductedAmy OliverNo ratings yet

- Lab #1 Logic Gates: ObjectiveDocument6 pagesLab #1 Logic Gates: ObjectiveZbiggNo ratings yet

- AEC Lab ManualDocument70 pagesAEC Lab ManualRohan BoseNo ratings yet

- Electronic Circuits Question PaperDocument3 pagesElectronic Circuits Question PaperRaja SekharNo ratings yet

- Ade Lab ManualDocument79 pagesAde Lab ManualVinod KannaNo ratings yet

- Introduction To Logic Gates Exp2Document11 pagesIntroduction To Logic Gates Exp2Tamim ANo ratings yet

- EC1 Lab Exp3 PDFDocument2 pagesEC1 Lab Exp3 PDFRitu RoyNo ratings yet

- V, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyDocument2 pagesV, V, K U C W/L, V I, I, G, R: Unless Given SpecificallyraghavbhatiaNo ratings yet

- (Ce) Transistor Characteristics in Common Emitter ConfigurationDocument7 pages(Ce) Transistor Characteristics in Common Emitter Configurationjassisc100% (1)

- MOSFET Experiment GuideDocument3 pagesMOSFET Experiment GuidemangyanNo ratings yet

- E.G. Per Set/group of StudentDocument4 pagesE.G. Per Set/group of StudentKiritoNo ratings yet

- ECE 2201 Experiment 1 - 4Document13 pagesECE 2201 Experiment 1 - 4Deepak SharmaNo ratings yet

- Lab Repot 5 - TransistorDocument8 pagesLab Repot 5 - TransistorUmmu Umar Wa Aisyah100% (2)

- Laboratory Manual Course Code Ece254 Course Title: Unified Electronics Laboratory-IDocument67 pagesLaboratory Manual Course Code Ece254 Course Title: Unified Electronics Laboratory-IKaran SainiNo ratings yet

- NEP2020 ISEM ManualElectricallabDocument28 pagesNEP2020 ISEM ManualElectricallabrangooNo ratings yet

- 3-Transistor Characteristics and Amplifier CircuitsDocument11 pages3-Transistor Characteristics and Amplifier CircuitsJudah SnehanNo ratings yet

- 2630-Prathmesh KakadeDocument46 pages2630-Prathmesh KakadeTanmay MhatreNo ratings yet

- Exercises in Electronics: Operational Amplifier CircuitsFrom EverandExercises in Electronics: Operational Amplifier CircuitsRating: 3 out of 5 stars3/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Small, Low Power, 3-Axis 3 G Accelerometer ADXL335: Features General DescriptionDocument16 pagesSmall, Low Power, 3-Axis 3 G Accelerometer ADXL335: Features General DescriptionMilo LatinoNo ratings yet

- C Function AtofDocument1 pageC Function AtofMilo LatinoNo ratings yet

- ProjectDocument1 pageProjectMilo LatinoNo ratings yet

- EjercicioDocument1 pageEjercicioMilo LatinoNo ratings yet

- Design and Simulate A Chronometer As FollowsDocument1 pageDesign and Simulate A Chronometer As FollowsMilo LatinoNo ratings yet

- Data Sheet: ADJD-S311-CR999Document20 pagesData Sheet: ADJD-S311-CR999Milo LatinoNo ratings yet