Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

107 viewsVerilog Tutorial: 1-Bit Full Adder

Verilog Tutorial: 1-Bit Full Adder

Uploaded by

Le HieuCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

You might also like

- VERILOG HDL - Tutorial, PPT FormatDocument30 pagesVERILOG HDL - Tutorial, PPT FormatArslan Kiani100% (2)

- Full Adder Design Using Verilog HDL in Three Modeling StylesDocument8 pagesFull Adder Design Using Verilog HDL in Three Modeling Stylesvijayseshu100% (1)

- Verilog Updated ProgramsDocument47 pagesVerilog Updated Programsanand_duraiswamy100% (1)

- Lab 02 Submitted ToDocument5 pagesLab 02 Submitted ToBilal AhmadNo ratings yet

- Vlsi 1Document17 pagesVlsi 1Sudeep KrishnappaNo ratings yet

- Lab 01 Submitted ToDocument4 pagesLab 01 Submitted ToBilal AhmadNo ratings yet

- Lab Assignment 1:: Design IssuesDocument6 pagesLab Assignment 1:: Design IssuesAbdul Wasay JawaidNo ratings yet

- Eda LabrecordDocument71 pagesEda Labrecordteja roopNo ratings yet

- Dataflow Modelling. // // Behavioural Modelling.Document2 pagesDataflow Modelling. // // Behavioural Modelling.ReyPanchalNo ratings yet

- What Is A Full Adder?: Block DiagramDocument5 pagesWhat Is A Full Adder?: Block DiagramAbcdNo ratings yet

- Lab Report SubmissionDocument26 pagesLab Report SubmissionTharshninipriya RajasekarNo ratings yet

- Lab 3 DSDDocument8 pagesLab 3 DSDRohaidNo ratings yet

- Dataflow ModellingDocument30 pagesDataflow ModellingMayur NayakaNo ratings yet

- Ver I Log ExamplesDocument22 pagesVer I Log ExamplesDayanand Gowda KrNo ratings yet

- Combinational Logic Design - Ripple Carry Adder, Carry Look Ahead AdderDocument25 pagesCombinational Logic Design - Ripple Carry Adder, Carry Look Ahead Adderdarlachantisaideepthi450No ratings yet

- Verilog Tutorial: Chin-Lung SuDocument42 pagesVerilog Tutorial: Chin-Lung Suajay_kr931No ratings yet

- Verilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindDocument36 pagesVerilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindVIJAYPUTRANo ratings yet

- VLSI Lab Report 8Document24 pagesVLSI Lab Report 8Umar AyubNo ratings yet

- Carry Save AdderDocument5 pagesCarry Save AdderMohan Babu ANo ratings yet

- Verilog - Combinational CircuitDocument47 pagesVerilog - Combinational CircuitSharan ChaitanyaNo ratings yet

- I. Half Adder: Block DiagramDocument4 pagesI. Half Adder: Block DiagramSam XingxnNo ratings yet

- DLD (Assignment 2)Document12 pagesDLD (Assignment 2)Hamna SajjadNo ratings yet

- New Text DocumentDocument1 pageNew Text Documentnguyen hungNo ratings yet

- Part 3: Verilog Tutorial: ECE232: Hardware Organization and DesignDocument18 pagesPart 3: Verilog Tutorial: ECE232: Hardware Organization and DesignAbhishek MishraNo ratings yet

- Experiment No. 6Document5 pagesExperiment No. 6Hrishikesh UgleNo ratings yet

- DSDV Lab Manual PDFDocument15 pagesDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- Logic Design Lab Verilog 101Document49 pagesLogic Design Lab Verilog 101杜岳No ratings yet

- Verilog ReviewDocument78 pagesVerilog ReviewsubbuNo ratings yet

- Digital Circuit Verification Hardware Descriptive Language VerilogDocument17 pagesDigital Circuit Verification Hardware Descriptive Language VerilogFreyja SigurgisladottirNo ratings yet

- Module:4 Design of Data Path Circuits 6 HoursDocument44 pagesModule:4 Design of Data Path Circuits 6 HoursSahana MecheriNo ratings yet

- Vlsi Comple Lab TaskDocument37 pagesVlsi Comple Lab TaskTausique SheikhNo ratings yet

- 9.four Bit Multiplier: AIM:To Design and Simulate Four Bit Multiplier Using Modelsim. TOOL:Modelsim. Logic DiagramDocument4 pages9.four Bit Multiplier: AIM:To Design and Simulate Four Bit Multiplier Using Modelsim. TOOL:Modelsim. Logic DiagramJhansiJhanuNo ratings yet

- Intro To VerilogDocument68 pagesIntro To VerilogNicolas AmezquitaNo ratings yet

- Verilog Tutorial For Beginner'sDocument65 pagesVerilog Tutorial For Beginner'sSachin SreelalNo ratings yet

- All VerilogLabsDocument74 pagesAll VerilogLabssamruthNo ratings yet

- EE-307 Fpga Based System Design: Lecture # 03Document19 pagesEE-307 Fpga Based System Design: Lecture # 03Muhammad AnasNo ratings yet

- Digital Circuits (2) - Ch6Document9 pagesDigital Circuits (2) - Ch6jameg20458No ratings yet

- Ec6612 Vlsi Design Lab - Exact Record DetailsDocument54 pagesEc6612 Vlsi Design Lab - Exact Record DetailsBharat RohanNo ratings yet

- 3 &4 Full Adder and DEMUX StrucDocument6 pages3 &4 Full Adder and DEMUX StrucSubhash Chandra SahuNo ratings yet

- Synthesis IDocument99 pagesSynthesis IsenthilNo ratings yet

- VLSI Lab Record 2023Document47 pagesVLSI Lab Record 2023HARISABARISH J 21ECNo ratings yet

- HDL Lab Manual VTUDocument63 pagesHDL Lab Manual VTUSyed MisbahNo ratings yet

- EECS 270 Verilog Reference: Combinational Logic: Figure 1a: Half Adder Figure 1b: Full AdderDocument6 pagesEECS 270 Verilog Reference: Combinational Logic: Figure 1a: Half Adder Figure 1b: Full AdderTampolenNo ratings yet

- Lab Results VlsiDocument18 pagesLab Results Vlsipankaj rangareeNo ratings yet

- Experiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor GateDocument7 pagesExperiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor Gatepadmavasavi1973No ratings yet

- 6 HDLDocument12 pages6 HDLlakshmiNo ratings yet

- Verilog Behavioral Program For Counters: Up Counter (4 Bit)Document17 pagesVerilog Behavioral Program For Counters: Up Counter (4 Bit)Sainadh YerrapragadaNo ratings yet

- 3.ECE301 - Levels of AbstractionDocument22 pages3.ECE301 - Levels of AbstractionenzuekNo ratings yet

- Objective: To Implement and Simulate 4-Bit Binary Ripple Carry Adder Using Verilog BackgroundDocument2 pagesObjective: To Implement and Simulate 4-Bit Binary Ripple Carry Adder Using Verilog BackgroundMohamed NiyasNo ratings yet

- EXP4Document6 pagesEXP4Dhruv GuptaNo ratings yet

- Chapter 7 Parameters Task and Function in VerilogDocument34 pagesChapter 7 Parameters Task and Function in Veriloghieu27718No ratings yet

- Verlog IntroDocument16 pagesVerlog IntroGuruNo ratings yet

- Lab 1Document23 pagesLab 1Santosh KumarNo ratings yet

- Combinational - Circuits-Verilog CodesDocument6 pagesCombinational - Circuits-Verilog CodesTheVerseNo ratings yet

- HDL Model Combinational CircuitDocument24 pagesHDL Model Combinational CircuitsaidaraoNo ratings yet

- Digital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkDocument63 pagesDigital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkBhaskar KNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- CS202 Lab2submission LeTrungHieu 10ESDocument27 pagesCS202 Lab2submission LeTrungHieu 10ESLe HieuNo ratings yet

- ECE371 Lab1Report Group2Document9 pagesECE371 Lab1Report Group2Le HieuNo ratings yet

- TOEFL iBT Speaking Sample 2Document7 pagesTOEFL iBT Speaking Sample 2Le HieuNo ratings yet

- EE 471 Group12 Lab3 ReportDocument24 pagesEE 471 Group12 Lab3 ReportLe HieuNo ratings yet

- Student Shop Exercise ECE 271 Name: Lê Trung Hiếu Class: 10ES Instructor: Mr Nguyen The NghiaDocument9 pagesStudent Shop Exercise ECE 271 Name: Lê Trung Hiếu Class: 10ES Instructor: Mr Nguyen The NghiaLe HieuNo ratings yet

Verilog Tutorial: 1-Bit Full Adder

Verilog Tutorial: 1-Bit Full Adder

Uploaded by

Le Hieu0 ratings0% found this document useful (0 votes)

107 views8 pagesOriginal Title

verilog_tutorial1

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

107 views8 pagesVerilog Tutorial: 1-Bit Full Adder

Verilog Tutorial: 1-Bit Full Adder

Uploaded by

Le HieuCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 8

Verilog Tutorial: 1-Bit Full Adder

B A

Cin

1-bit full adder

Sum

Cout

A B

S1 Sum

C2 Cout C1 Cin

2012 Chang Choo

Verilog Tutorial: 1-Bit Full Adder

module fulladd (sum, cout, a, b, cin); input a, b, cin; // comments output sum, cout; wire s1, c1, c2; xor (s1, a, b); and (c1, a, b); xor (sum, s1, cin); and (c2, s1, cin); or (cout, c1, c2); endmodule

2012 Chang Choo

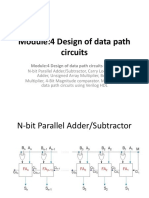

Verilog Tutorial: 4-Bit Full Adder

B[3] C4 3 A[3] C3 2 B[2] A[2] C2 1 B[1] A[1] C1 0 B[0] A[0] Cin full adder full adder full adder full adder

S4

S[3]

S[2]

S[1]

S[0]

module fulladd4 (sum, cout, a, b, cin); output [3:0] sum; output cout; input [3:0] a, b; input cin; wire c3, c2, c1; fulladd fa0 (sum[0], c1, a[0], b[0], cin); fulladd fa1 (sum[1], c2, a[1], b[1], c1); fulladd fa2 (sum[2], c3, a[2], b[2], c2); fulladd fa3 (sum[3], cout, a[3], b[3], c3); endmodule

2012 Chang Choo

Verilog Tutorial: 4-Bit Full Adder

// Data Flow Model module adder (sum, a, b); input [3:0] a, b; output [4:0] sum; wire [4:0] sum; assign sum = a + b; // assign p=a*b; endmodule

2012 Chang Choo

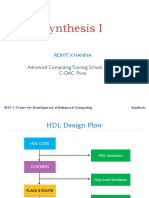

HDL Design Flow Behavior. Simulation

VHDL Library VHDL Model

VHDL Testbench

Optional

Simulation Compiler

Simulation Model

Test Vectors

Waveform

VHDL Simulation

Text Output

2012 Chang Choo

Some Verilog Examples

// 4-bit comparator module four_bit_comp (gt, A, B); output gt; input [3:0] A, B; assign gt = (A > B); endmodule // 4-bit max another way module four_bit_max (max, A, B); output [3:0] max; input [3:0] A, B; assign max = (A > B) ? A : B; endmodule

2012 Chang Choo

Some Verilog Examples

// 4-bit ALU module alu4 (A, B, S, Y); input [3:0] A, B; input [1:0] S; // selection inputs output [3:0] Y; reg [3:0] Y; always @ (A or B or S) case (S) 2'b00: Y = A+B; // A*B for multiplication 2'b01: Y = A-B; 2'b10: Y = A&B; 2'b11: Y = A|B; endcase endmodule

2012 Chang Choo

Some Verilog Examples

// 4-bit 2-to-1 MUX module mux4 (y, a, b, sel); input [3:0] a, b; input sel; output [3:0] y; reg [3:0] y; always @(a or b or sel) begin if (sel==0) y = a; else y = b; end endmodule

2012 Chang Choo

You might also like

- VERILOG HDL - Tutorial, PPT FormatDocument30 pagesVERILOG HDL - Tutorial, PPT FormatArslan Kiani100% (2)

- Full Adder Design Using Verilog HDL in Three Modeling StylesDocument8 pagesFull Adder Design Using Verilog HDL in Three Modeling Stylesvijayseshu100% (1)

- Verilog Updated ProgramsDocument47 pagesVerilog Updated Programsanand_duraiswamy100% (1)

- Lab 02 Submitted ToDocument5 pagesLab 02 Submitted ToBilal AhmadNo ratings yet

- Vlsi 1Document17 pagesVlsi 1Sudeep KrishnappaNo ratings yet

- Lab 01 Submitted ToDocument4 pagesLab 01 Submitted ToBilal AhmadNo ratings yet

- Lab Assignment 1:: Design IssuesDocument6 pagesLab Assignment 1:: Design IssuesAbdul Wasay JawaidNo ratings yet

- Eda LabrecordDocument71 pagesEda Labrecordteja roopNo ratings yet

- Dataflow Modelling. // // Behavioural Modelling.Document2 pagesDataflow Modelling. // // Behavioural Modelling.ReyPanchalNo ratings yet

- What Is A Full Adder?: Block DiagramDocument5 pagesWhat Is A Full Adder?: Block DiagramAbcdNo ratings yet

- Lab Report SubmissionDocument26 pagesLab Report SubmissionTharshninipriya RajasekarNo ratings yet

- Lab 3 DSDDocument8 pagesLab 3 DSDRohaidNo ratings yet

- Dataflow ModellingDocument30 pagesDataflow ModellingMayur NayakaNo ratings yet

- Ver I Log ExamplesDocument22 pagesVer I Log ExamplesDayanand Gowda KrNo ratings yet

- Combinational Logic Design - Ripple Carry Adder, Carry Look Ahead AdderDocument25 pagesCombinational Logic Design - Ripple Carry Adder, Carry Look Ahead Adderdarlachantisaideepthi450No ratings yet

- Verilog Tutorial: Chin-Lung SuDocument42 pagesVerilog Tutorial: Chin-Lung Suajay_kr931No ratings yet

- Verilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindDocument36 pagesVerilog 1 - Fundamentals: 6.375 Complex Digital Systems ArvindVIJAYPUTRANo ratings yet

- VLSI Lab Report 8Document24 pagesVLSI Lab Report 8Umar AyubNo ratings yet

- Carry Save AdderDocument5 pagesCarry Save AdderMohan Babu ANo ratings yet

- Verilog - Combinational CircuitDocument47 pagesVerilog - Combinational CircuitSharan ChaitanyaNo ratings yet

- I. Half Adder: Block DiagramDocument4 pagesI. Half Adder: Block DiagramSam XingxnNo ratings yet

- DLD (Assignment 2)Document12 pagesDLD (Assignment 2)Hamna SajjadNo ratings yet

- New Text DocumentDocument1 pageNew Text Documentnguyen hungNo ratings yet

- Part 3: Verilog Tutorial: ECE232: Hardware Organization and DesignDocument18 pagesPart 3: Verilog Tutorial: ECE232: Hardware Organization and DesignAbhishek MishraNo ratings yet

- Experiment No. 6Document5 pagesExperiment No. 6Hrishikesh UgleNo ratings yet

- DSDV Lab Manual PDFDocument15 pagesDSDV Lab Manual PDFÅᴅᴀʀsʜ Rᴀᴍ100% (3)

- VLSI Lab Manual Exercise ProblemsDocument38 pagesVLSI Lab Manual Exercise ProblemsPrakhar Kumar100% (1)

- Logic Design Lab Verilog 101Document49 pagesLogic Design Lab Verilog 101杜岳No ratings yet

- Verilog ReviewDocument78 pagesVerilog ReviewsubbuNo ratings yet

- Digital Circuit Verification Hardware Descriptive Language VerilogDocument17 pagesDigital Circuit Verification Hardware Descriptive Language VerilogFreyja SigurgisladottirNo ratings yet

- Module:4 Design of Data Path Circuits 6 HoursDocument44 pagesModule:4 Design of Data Path Circuits 6 HoursSahana MecheriNo ratings yet

- Vlsi Comple Lab TaskDocument37 pagesVlsi Comple Lab TaskTausique SheikhNo ratings yet

- 9.four Bit Multiplier: AIM:To Design and Simulate Four Bit Multiplier Using Modelsim. TOOL:Modelsim. Logic DiagramDocument4 pages9.four Bit Multiplier: AIM:To Design and Simulate Four Bit Multiplier Using Modelsim. TOOL:Modelsim. Logic DiagramJhansiJhanuNo ratings yet

- Intro To VerilogDocument68 pagesIntro To VerilogNicolas AmezquitaNo ratings yet

- Verilog Tutorial For Beginner'sDocument65 pagesVerilog Tutorial For Beginner'sSachin SreelalNo ratings yet

- All VerilogLabsDocument74 pagesAll VerilogLabssamruthNo ratings yet

- EE-307 Fpga Based System Design: Lecture # 03Document19 pagesEE-307 Fpga Based System Design: Lecture # 03Muhammad AnasNo ratings yet

- Digital Circuits (2) - Ch6Document9 pagesDigital Circuits (2) - Ch6jameg20458No ratings yet

- Ec6612 Vlsi Design Lab - Exact Record DetailsDocument54 pagesEc6612 Vlsi Design Lab - Exact Record DetailsBharat RohanNo ratings yet

- 3 &4 Full Adder and DEMUX StrucDocument6 pages3 &4 Full Adder and DEMUX StrucSubhash Chandra SahuNo ratings yet

- Synthesis IDocument99 pagesSynthesis IsenthilNo ratings yet

- VLSI Lab Record 2023Document47 pagesVLSI Lab Record 2023HARISABARISH J 21ECNo ratings yet

- HDL Lab Manual VTUDocument63 pagesHDL Lab Manual VTUSyed MisbahNo ratings yet

- EECS 270 Verilog Reference: Combinational Logic: Figure 1a: Half Adder Figure 1b: Full AdderDocument6 pagesEECS 270 Verilog Reference: Combinational Logic: Figure 1a: Half Adder Figure 1b: Full AdderTampolenNo ratings yet

- Lab Results VlsiDocument18 pagesLab Results Vlsipankaj rangareeNo ratings yet

- Experiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor GateDocument7 pagesExperiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor Gatepadmavasavi1973No ratings yet

- 6 HDLDocument12 pages6 HDLlakshmiNo ratings yet

- Verilog Behavioral Program For Counters: Up Counter (4 Bit)Document17 pagesVerilog Behavioral Program For Counters: Up Counter (4 Bit)Sainadh YerrapragadaNo ratings yet

- 3.ECE301 - Levels of AbstractionDocument22 pages3.ECE301 - Levels of AbstractionenzuekNo ratings yet

- Objective: To Implement and Simulate 4-Bit Binary Ripple Carry Adder Using Verilog BackgroundDocument2 pagesObjective: To Implement and Simulate 4-Bit Binary Ripple Carry Adder Using Verilog BackgroundMohamed NiyasNo ratings yet

- EXP4Document6 pagesEXP4Dhruv GuptaNo ratings yet

- Chapter 7 Parameters Task and Function in VerilogDocument34 pagesChapter 7 Parameters Task and Function in Veriloghieu27718No ratings yet

- Verlog IntroDocument16 pagesVerlog IntroGuruNo ratings yet

- Lab 1Document23 pagesLab 1Santosh KumarNo ratings yet

- Combinational - Circuits-Verilog CodesDocument6 pagesCombinational - Circuits-Verilog CodesTheVerseNo ratings yet

- HDL Model Combinational CircuitDocument24 pagesHDL Model Combinational CircuitsaidaraoNo ratings yet

- Digital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkDocument63 pagesDigital Design Lab (Ec661) Experiment N0.:1: Brief Description of WorkBhaskar KNo ratings yet

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (2)

- CS202 Lab2submission LeTrungHieu 10ESDocument27 pagesCS202 Lab2submission LeTrungHieu 10ESLe HieuNo ratings yet

- ECE371 Lab1Report Group2Document9 pagesECE371 Lab1Report Group2Le HieuNo ratings yet

- TOEFL iBT Speaking Sample 2Document7 pagesTOEFL iBT Speaking Sample 2Le HieuNo ratings yet

- EE 471 Group12 Lab3 ReportDocument24 pagesEE 471 Group12 Lab3 ReportLe HieuNo ratings yet

- Student Shop Exercise ECE 271 Name: Lê Trung Hiếu Class: 10ES Instructor: Mr Nguyen The NghiaDocument9 pagesStudent Shop Exercise ECE 271 Name: Lê Trung Hiếu Class: 10ES Instructor: Mr Nguyen The NghiaLe HieuNo ratings yet