Professional Documents

Culture Documents

Pseudo Random Sequence Generator

Pseudo Random Sequence Generator

Uploaded by

nakamo_idOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Pseudo Random Sequence Generator

Pseudo Random Sequence Generator

Uploaded by

nakamo_idCopyright:

Available Formats

Switching and Logic

Spring 2008

jeg

Pseudo-Random Sequence Generator

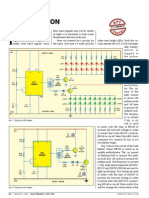

The use of a shift-register with XNOR feedback will yield a pseudo random sequence of numbers. If an n-bit shift register is used, the sequence is 2n-1 where the state of all ones is excluded. The schematic for this pseudo random sequence generator is shown in Figure 1. This diagram shows the most common configuration with two taps. To reach a maximal length sequence sometimes 3, 4 or 5 taps are required. See Table 1 for the taps that give maximal length pseudo random sequences. Note when the shift register is powered up the content is all zeros. By using the exclusive-NOR the sequence is self starting.

=1

clk

Figure 1 Pseudo Random Sequence Generator

The code given below for the 7-bit shift register will work as a template for shift registers of other sizes.

ENTITY PRSG7 IS PORT( CLK : IN BIT; Q : BUFFER BIT_VECTOR (7 DOWNTO 1) ); END ENTITY PRSG7; ARCHITECTURE BEHAVIORAL OF PRSG7 IS BEGIN PROCESS(Q,CLK) BEGIN IF CLK'EVENT AND CLK = '1' THEN Q <= Q(6 DOWNTO 1) & (Q(7) XNOR Q(6)); ELSE Q <= Q; END IF; END PROCESS; END ARCHITECTURE BEHAVIORAL;

The PLDT-2 boards come with a 4 MHz clock oscillator as the standard global clock. Table 1 list the time it will take the sequence to repeat for the 4 MHz clock oscillator. It is assumed that one would allow the pseudo random sequence generator to run continuously, and then pick different taps to generate the smaller bit patterns to cause random events to take place in the design.

Switching and Logic

Table 1 Primitive Polynomial Modula 2 n 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 Taps Repetition Time for 4 MHz Clock 1.75 3.75 7.75 15.75 31.75 63.75 127.75 255.75 511.75 1.02 2.05 4.10 8.19 16.38 32.77 65.54 131.07 262.14 524.29 1.05 2.10 4.19 8.39 16.78 33.55 1.12 2.24 4.47 8.95 17.90

Spring 2008

jeg

Units us ns ns us us us us us us ms ms ms ms ms ms ms ms ms ms s s s s s s m m m m m

3,2 4,3 5,3 6,5 7,6 8,6,5,4 9,5 10,7 11,9 12,6,4,1 13,4,3,1 14,5,3,1 15,14 16,15,13,4 17,14 18,11 19,6,2,1 20,17 21,19 22,21, 23,18 24,23,22,17 25,22 26,6,2,1 27,5,2,1 28,25 29,27 30,6,4,1 31,28 32,22,2,1

You might also like

- Mech 375 Lab 1Document13 pagesMech 375 Lab 1Patrick Mroczek100% (1)

- Experiment 1 - Leds and 7-Segment Display (Part 1) : A. Learning OutcomesDocument10 pagesExperiment 1 - Leds and 7-Segment Display (Part 1) : A. Learning OutcomesBianca ReyNo ratings yet

- A Student's Guide to Python for Physical Modeling: Second EditionFrom EverandA Student's Guide to Python for Physical Modeling: Second EditionNo ratings yet

- Lab #8Document9 pagesLab #8Grant HeilemanNo ratings yet

- Lab 1Document8 pagesLab 1Mulugeta AbebawNo ratings yet

- DGD 8Document2 pagesDGD 8Dolores MakaruinaNo ratings yet

- On A Method of Pseudo-Random Numbers: GenerationDocument11 pagesOn A Method of Pseudo-Random Numbers: GenerationgalacticfridgeNo ratings yet

- Design of An 8 Bit Barrel Shifter: Gene Vea, Perry Hung, Ricardo Rosas, Kevin YooDocument15 pagesDesign of An 8 Bit Barrel Shifter: Gene Vea, Perry Hung, Ricardo Rosas, Kevin YoodivyeddNo ratings yet

- DGD 8 SolDocument6 pagesDGD 8 SolDolores MakaruinaNo ratings yet

- FlexCAN Bit Timing ParametersDocument8 pagesFlexCAN Bit Timing Parametersravillakiran56No ratings yet

- Clock PowerDocument8 pagesClock PowerSathish BalaNo ratings yet

- SN1-2223-Lab3 1-2 EngDocument4 pagesSN1-2223-Lab3 1-2 EngBoualem MestafaNo ratings yet

- Digital Wavelet Decomposition GroupDocument10 pagesDigital Wavelet Decomposition GroupkjnanduNo ratings yet

- Reference of LFSR AesDocument21 pagesReference of LFSR AesK.KALAISELVI HICET STAFF ECENo ratings yet

- Clocking and Latches: Notes For EEC180B Spring 1999 University of California DavisDocument18 pagesClocking and Latches: Notes For EEC180B Spring 1999 University of California Davisrvs_093No ratings yet

- EE 367 - Logic Design: AgendaDocument6 pagesEE 367 - Logic Design: Agendadivya1587No ratings yet

- DSP Implementation of Cholesky DecompositionDocument4 pagesDSP Implementation of Cholesky DecompositionNayim MohammadNo ratings yet

- Chapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)Document6 pagesChapter 4: One-Shots, Counters, and Clocks: I. The Monostable Multivibrator (One-Shot)amitpatel1991No ratings yet

- ECNG 3016 Advanced Digital Electronics: Eneral NformationDocument10 pagesECNG 3016 Advanced Digital Electronics: Eneral NformationMarlon BoucaudNo ratings yet

- Digital Electronics Module 05Document44 pagesDigital Electronics Module 05Yadana1No ratings yet

- Computer Organization July 2005 OldDocument2 pagesComputer Organization July 2005 OldPrasad C MNo ratings yet

- 2019 Holiday NotificationDocument2 pages2019 Holiday NotificationAmbika KrNo ratings yet

- Frequency Dividers: Device Modelling Mini-ProjectDocument24 pagesFrequency Dividers: Device Modelling Mini-Projectjoshuacool4No ratings yet

- Real-Time Operating Systems and Scheduling: 2add. Timing Anomalies in ProcessorsDocument6 pagesReal-Time Operating Systems and Scheduling: 2add. Timing Anomalies in ProcessorsNA KarthikNo ratings yet

- Configuring A Transient Analysis in Multisim: TutorialDocument4 pagesConfiguring A Transient Analysis in Multisim: TutorialariasnomercyNo ratings yet

- A Cmos: Zero-Overhead Self-Timed 16011s DividerDocument3 pagesA Cmos: Zero-Overhead Self-Timed 16011s DividerIndrasena Reddy GadeNo ratings yet

- FPGA-based Direct Conversion Receiver With Continuous Acquisition To A PCDocument25 pagesFPGA-based Direct Conversion Receiver With Continuous Acquisition To A PCJeong-geun KimNo ratings yet

- BER MeterDocument8 pagesBER Metersakti prasad nandaNo ratings yet

- Mod 5Document83 pagesMod 5Jane BillonesNo ratings yet

- 4-Bit Counter Using Modified Master - Slave Edge Triggered RegisterDocument20 pages4-Bit Counter Using Modified Master - Slave Edge Triggered Registermilanjauhari0% (1)

- TE 2019 MechatronicsDocument6 pagesTE 2019 MechatronicsVishalNo ratings yet

- Laboratory Exercise 5: BackgroundDocument3 pagesLaboratory Exercise 5: BackgroundMB Fazli NisarNo ratings yet

- Design A Combinatorial Circuit 863832727868Document5 pagesDesign A Combinatorial Circuit 863832727868Siva Guru0% (1)

- Homework Set 6 SolutionDocument10 pagesHomework Set 6 SolutionLamar Griffiths100% (1)

- C&i Lab-2019Document67 pagesC&i Lab-2019aniruthNo ratings yet

- Physical Unclonable Function (PUF) Based Random Number GeneratorDocument7 pagesPhysical Unclonable Function (PUF) Based Random Number GeneratorAnonymous IlrQK9HuNo ratings yet

- RC Servo Controller: Free IPDocument6 pagesRC Servo Controller: Free IPrainrrNo ratings yet

- Lab 8Document8 pagesLab 8Anonymous yG7oj20% (1)

- PTI Section 8 Digital CircuitsDocument32 pagesPTI Section 8 Digital Circuitschrist9088No ratings yet

- Psuedo Sequence SignalDocument14 pagesPsuedo Sequence Signalzfa91No ratings yet

- An Integer Square Root Algorithm: Example 24Document10 pagesAn Integer Square Root Algorithm: Example 24psomasalNo ratings yet

- Lab11 CountersDocument6 pagesLab11 Countersjocansino4496100% (1)

- Control Engineering Lab Manual Part 2Document11 pagesControl Engineering Lab Manual Part 2UmerShahzadQurashi100% (1)

- Interface Clavier PicDocument27 pagesInterface Clavier Picblaiso2020No ratings yet

- BaitapVerilog LabDocument6 pagesBaitapVerilog LabHai LúaNo ratings yet

- Exp - 08 Flight86Document6 pagesExp - 08 Flight86Muhammad SaqibNo ratings yet

- M.tech Lab Manual JNTUHDocument80 pagesM.tech Lab Manual JNTUHSivarama Prasad PamarthyNo ratings yet

- Demo 4 - 4 X 4 Matrix Keyboard Using Timer InterruptDocument17 pagesDemo 4 - 4 X 4 Matrix Keyboard Using Timer Interruptchuku7No ratings yet

- Lab ManualDocument88 pagesLab ManualKirubha Shankar EceNo ratings yet

- Systolic Arrays & Their ApplicationsDocument35 pagesSystolic Arrays & Their ApplicationsSp SinghNo ratings yet

- PRBS GenerationDocument10 pagesPRBS GenerationFaye YturraldeNo ratings yet

- Lab Report 1 EE32200 - Ronny VintimillaDocument16 pagesLab Report 1 EE32200 - Ronny VintimillaRonny VintimillaNo ratings yet

- Welcome To International Journal of Engineering Research and Development (IJERD)Document8 pagesWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Flancter App NoteDocument11 pagesFlancter App NotebigdogguruNo ratings yet

- Application Note AN047: CC1100/CC2500 - Wake-On-RadioDocument17 pagesApplication Note AN047: CC1100/CC2500 - Wake-On-Radiolucas_amclNo ratings yet

- Economic and Financial Modelling with EViews: A Guide for Students and ProfessionalsFrom EverandEconomic and Financial Modelling with EViews: A Guide for Students and ProfessionalsNo ratings yet

- Numerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityFrom EverandNumerical Methods for Simulation and Optimization of Piecewise Deterministic Markov Processes: Application to ReliabilityNo ratings yet

- GARCH Models: Structure, Statistical Inference and Financial ApplicationsFrom EverandGARCH Models: Structure, Statistical Inference and Financial ApplicationsRating: 5 out of 5 stars5/5 (1)

- Jpeg Ls LocoDocument16 pagesJpeg Ls Loconakamo_idNo ratings yet

- Practical Amplifier: To Analyse The CircuitDocument15 pagesPractical Amplifier: To Analyse The Circuitnakamo_idNo ratings yet

- Traffic Baton PDFDocument2 pagesTraffic Baton PDFbits_who_am_iNo ratings yet

- 2007 Anna University PaperDocument2 pages2007 Anna University Papernakamo_idNo ratings yet

- Virtual Keyboard: P-IsmDocument40 pagesVirtual Keyboard: P-Ismnakamo_idNo ratings yet

- Piezoelectric TransducerDocument10 pagesPiezoelectric Transducernakamo_idNo ratings yet