Professional Documents

Culture Documents

Ee311 Homework4 2012 PDF

Ee311 Homework4 2012 PDF

Uploaded by

techaddicttCopyright:

Available Formats

You might also like

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliNo ratings yet

- Solns 29Document102 pagesSolns 29ramprakash_rampelliNo ratings yet

- EE 330 Lab - 7 Spring 2013Document6 pagesEE 330 Lab - 7 Spring 2013Tuan VoNo ratings yet

- Elec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2011 Final Exam - April 25, 2011Document4 pagesElec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2011 Final Exam - April 25, 2011Filip ZubacNo ratings yet

- A Guide to Electronic Maintenance and RepairsFrom EverandA Guide to Electronic Maintenance and RepairsRating: 4.5 out of 5 stars4.5/5 (7)

- EXAM #1 - Solution Problem 1 - (43 Points) : Vo I oDocument14 pagesEXAM #1 - Solution Problem 1 - (43 Points) : Vo I okbkkrNo ratings yet

- Objective:: Study of The Multistage (Cascaded) AmplifierDocument6 pagesObjective:: Study of The Multistage (Cascaded) Amplifierعلي حسنNo ratings yet

- Homework SolutionsDocument46 pagesHomework SolutionsKashif AmjadNo ratings yet

- ExamDocument13 pagesExamHamed GhanbariNo ratings yet

- 9 Multistage Amplifiers and Logarithmic Scales: 9.1 ObjectivesDocument4 pages9 Multistage Amplifiers and Logarithmic Scales: 9.1 ObjectivesdjelbouNo ratings yet

- Midterm 2013 SolutionDocument5 pagesMidterm 2013 SolutionArunabh BhattacharyaNo ratings yet

- Chapter - 5 SolutionsDocument102 pagesChapter - 5 SolutionsForrest LingNo ratings yet

- Ec Manual NewDocument59 pagesEc Manual NewWasz MujthabaNo ratings yet

- Multisimm Report 301 Final ProjectDocument3 pagesMultisimm Report 301 Final Projectapi-296881750No ratings yet

- Department of Electrical and Computer Engineering: American University of BeirutDocument10 pagesDepartment of Electrical and Computer Engineering: American University of BeirutadgjkinghackNo ratings yet

- ELE350 Section 2 Midterm Exam - Attempt Review - 2Document4 pagesELE350 Section 2 Midterm Exam - Attempt Review - 2toqaele2020No ratings yet

- Notes 221021 191613Document18 pagesNotes 221021 191613Gustavo CircelliNo ratings yet

- Lab 8 ReportDocument6 pagesLab 8 Reportapi-491291595No ratings yet

- EEC110A Win 2010 Final Exam: Name: ID #Document35 pagesEEC110A Win 2010 Final Exam: Name: ID #Zoro ZhaoNo ratings yet

- ) For The Given NMOS. Given: V 1 V, .: ESC201A: Assignment VIII Date: 17 March, 2015Document4 pages) For The Given NMOS. Given: V 1 V, .: ESC201A: Assignment VIII Date: 17 March, 2015Deepak TholiaNo ratings yet

- RC Coupled Amplifier - DC Operation - EXERCISE 7Document15 pagesRC Coupled Amplifier - DC Operation - EXERCISE 7Debbie ComissionNo ratings yet

- Aicd Exam SolutionDocument16 pagesAicd Exam SolutionTenzin ChoendenNo ratings yet

- Ece3110 HW 3Document7 pagesEce3110 HW 3Apricot BlueberryNo ratings yet

- Tutorial DiodeDocument15 pagesTutorial DiodeAravind KumarNo ratings yet

- Analog Electronic Circuits Lab-Module1: Gowra P SDocument5 pagesAnalog Electronic Circuits Lab-Module1: Gowra P SReddyvari VenugopalNo ratings yet

- Tutorial 2 AnsDocument9 pagesTutorial 2 AnsKemproof100% (3)

- Electronic 2 Solved ProblemDocument8 pagesElectronic 2 Solved ProblemAbdullah S OthmanNo ratings yet

- Biasing: Diodes, Transistors, Fets Practical Perspective. Prof K.Appa RaoDocument44 pagesBiasing: Diodes, Transistors, Fets Practical Perspective. Prof K.Appa RaoSuresh ThallapelliNo ratings yet

- Diodes, Home Work Solutions: 3.1 Problem 3.11Document13 pagesDiodes, Home Work Solutions: 3.1 Problem 3.11Sherweet A. AlsaadanyNo ratings yet

- Opamp Applications: Session 10: Prakash Biswagar Asst. Professor E&C Engg. Dept RV College of Engineering, BangaloreDocument35 pagesOpamp Applications: Session 10: Prakash Biswagar Asst. Professor E&C Engg. Dept RV College of Engineering, BangaloreSatya Prasad AkkinaNo ratings yet

- Lecture21 Multistage AmplifiersDocument10 pagesLecture21 Multistage AmplifierscitraumariNo ratings yet

- Design Problem: 1-Design of First StageDocument4 pagesDesign Problem: 1-Design of First StageIbrahim SaadNo ratings yet

- EE 735: Microelectronics Simulations Lab: 1. Input-Output Characteristics of The InverterDocument13 pagesEE 735: Microelectronics Simulations Lab: 1. Input-Output Characteristics of The InverterRonik JadhavNo ratings yet

- Problem Based Learning: Roll Number: 19ES31Document8 pagesProblem Based Learning: Roll Number: 19ES31Qurban AliNo ratings yet

- Quiz 1Document1 pageQuiz 1Kishor KunalNo ratings yet

- Lecture 050 - Followers: (READING: GHLM - 344-362, AH - 221-226) ObjectiveDocument7 pagesLecture 050 - Followers: (READING: GHLM - 344-362, AH - 221-226) ObjectiveArchana RkNo ratings yet

- Homework Assignment 8 SolutionDocument8 pagesHomework Assignment 8 SolutionKL Chiang100% (1)

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- Analog CircuitsDocument18 pagesAnalog CircuitsSAMIT KARMAKARNo ratings yet

- 2310 Lab06Document4 pages2310 Lab06tarottaurus54No ratings yet

- EE31594 Quiz 4 Dec 14, 2019Document8 pagesEE31594 Quiz 4 Dec 14, 2019Hyunsog ChoiNo ratings yet

- Home Assignment - 8: 30 September, 2013Document2 pagesHome Assignment - 8: 30 September, 2013egupta1No ratings yet

- College of Engineering Midterm Test Answer: Subject Code: Course Title: Date: Time AllowedDocument8 pagesCollege of Engineering Midterm Test Answer: Subject Code: Course Title: Date: Time AllowedMohd RashdanNo ratings yet

- Transistor: Penguat Daya Dan Perancangan Penguat Klas A (Amplifier Design)Document66 pagesTransistor: Penguat Daya Dan Perancangan Penguat Klas A (Amplifier Design)Adri Muhaimin AfifNo ratings yet

- Analog Electronics Lab ManualDocument9 pagesAnalog Electronics Lab ManualRohan KatkamNo ratings yet

- Electronic Circuit Analysis Lab: Sumathi Reddy Institute of Technology Science For WomenDocument59 pagesElectronic Circuit Analysis Lab: Sumathi Reddy Institute of Technology Science For WomenSrinivasu RajuNo ratings yet

- Pspice Simulation of Mosfet Amplifier Configurations: 2.1 ObjectiveDocument8 pagesPspice Simulation of Mosfet Amplifier Configurations: 2.1 ObjectivePreet PatelNo ratings yet

- Bistable Multivibrator Design PDFDocument20 pagesBistable Multivibrator Design PDFOmkar Thakur100% (1)

- Stable Pulse Generator Uses Matched Transistors in A Current MirrorDocument6 pagesStable Pulse Generator Uses Matched Transistors in A Current MirrorDerek RamosNo ratings yet

- Frequency Response of A Single Stage RC Coupled AmplifierDocument26 pagesFrequency Response of A Single Stage RC Coupled AmplifierkanchankonwarNo ratings yet

- Final Exam ECE 1312 Question Sem-1 2013-2014Document9 pagesFinal Exam ECE 1312 Question Sem-1 2013-2014Fatihah AinaNo ratings yet

- BJTDocument18 pagesBJTMohd Nasrul Shafiq MnsNo ratings yet

- Elec I Lab 5Document3 pagesElec I Lab 5niguisisiNo ratings yet

- EE 735: Microelectronics Simulations Lab: Circuits Assignment-1 (Due On 17th October)Document2 pagesEE 735: Microelectronics Simulations Lab: Circuits Assignment-1 (Due On 17th October)Indranil ChakrabortyNo ratings yet

- Homework #4: I I V VDocument7 pagesHomework #4: I I V Vtay ChantsNo ratings yet

- Exercise - SAMPLE BJT PROBLEMSDocument8 pagesExercise - SAMPLE BJT PROBLEMSALi AlawiehNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- EE 436 HW2 - Spring2014Document2 pagesEE 436 HW2 - Spring2014techaddicttNo ratings yet

- EE436 HW1 Spring2014Document2 pagesEE436 HW1 Spring2014techaddicttNo ratings yet

- EE 311 Analog Electronics: Take Home Exam #2 Due: October 17, 2012 (In Class)Document1 pageEE 311 Analog Electronics: Take Home Exam #2 Due: October 17, 2012 (In Class)techaddicttNo ratings yet

- Ee311 2012HW3 PDFDocument1 pageEe311 2012HW3 PDFtechaddicttNo ratings yet

Ee311 Homework4 2012 PDF

Ee311 Homework4 2012 PDF

Uploaded by

techaddicttOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ee311 Homework4 2012 PDF

Ee311 Homework4 2012 PDF

Uploaded by

techaddicttCopyright:

Available Formats

EE 311 Analog Electronics

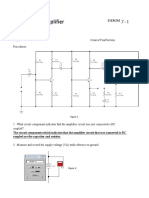

Take Home Exam Part IV Due: November 16, 2012 (Submit to D-112, by 17:00) Multi-Stage Amplifiers Q1. This problem deals with the amplifier design shown on the next figure.

1 k

500

Stage 1

+10 R1 200 k +10 RD 5 k vo vi RS 4 k MN R2 200 k

Stage 2

+10 +10

Stage 3

+10 +10

R1

RD vo

R1

vi

MN

vi

QN vo

CS

R2

RS1

R2

RE

-10 KN = 20 VTN = 1 V ro = mA/V2

-10 KN = 20 VTN = 1 V ro = mA/V2

-10

RS2

CS

-10

= 100 VBE(ON) = 0.7 V VTN = 25 mV ro =

-10

-10

Note that some of the resistor values are not provided so that you find proper values for them for your design. You can make assumptions and approximations as long as you indicate and justify them clearly. a) Design Stage 2 and Stage 3 to have, GV_TOTAL (overall gain, vo/vsignal) > 1000 V/V, GV3 (3rd stage gain when RL=500, vo/vi) > 0.8 V/V. b) Find the input and output resistances (RIN and ROUT) for the overall amplifier. c) Simulate this circuit in Spice and compare the results with previous parts. Q2. For the circuit given in the following figure, find RIN and the midband gain (Amid), assuming that =100, VA=100 V, RI=50 k (internal resistance of the current sources).

+5 +5

100 A

Q2

RS Q1 10 k vS RE 1 k RIN -5 -5 -5 100 A CL 1 pF vout

You might also like

- Solns 2cmosDocument18 pagesSolns 2cmosramprakash_rampelliNo ratings yet

- Solns 29Document102 pagesSolns 29ramprakash_rampelliNo ratings yet

- EE 330 Lab - 7 Spring 2013Document6 pagesEE 330 Lab - 7 Spring 2013Tuan VoNo ratings yet

- Elec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2011 Final Exam - April 25, 2011Document4 pagesElec Eng 2ei5 Microelectronic Devices and Circuits I Winter 2011 Final Exam - April 25, 2011Filip ZubacNo ratings yet

- A Guide to Electronic Maintenance and RepairsFrom EverandA Guide to Electronic Maintenance and RepairsRating: 4.5 out of 5 stars4.5/5 (7)

- EXAM #1 - Solution Problem 1 - (43 Points) : Vo I oDocument14 pagesEXAM #1 - Solution Problem 1 - (43 Points) : Vo I okbkkrNo ratings yet

- Objective:: Study of The Multistage (Cascaded) AmplifierDocument6 pagesObjective:: Study of The Multistage (Cascaded) Amplifierعلي حسنNo ratings yet

- Homework SolutionsDocument46 pagesHomework SolutionsKashif AmjadNo ratings yet

- ExamDocument13 pagesExamHamed GhanbariNo ratings yet

- 9 Multistage Amplifiers and Logarithmic Scales: 9.1 ObjectivesDocument4 pages9 Multistage Amplifiers and Logarithmic Scales: 9.1 ObjectivesdjelbouNo ratings yet

- Midterm 2013 SolutionDocument5 pagesMidterm 2013 SolutionArunabh BhattacharyaNo ratings yet

- Chapter - 5 SolutionsDocument102 pagesChapter - 5 SolutionsForrest LingNo ratings yet

- Ec Manual NewDocument59 pagesEc Manual NewWasz MujthabaNo ratings yet

- Multisimm Report 301 Final ProjectDocument3 pagesMultisimm Report 301 Final Projectapi-296881750No ratings yet

- Department of Electrical and Computer Engineering: American University of BeirutDocument10 pagesDepartment of Electrical and Computer Engineering: American University of BeirutadgjkinghackNo ratings yet

- ELE350 Section 2 Midterm Exam - Attempt Review - 2Document4 pagesELE350 Section 2 Midterm Exam - Attempt Review - 2toqaele2020No ratings yet

- Notes 221021 191613Document18 pagesNotes 221021 191613Gustavo CircelliNo ratings yet

- Lab 8 ReportDocument6 pagesLab 8 Reportapi-491291595No ratings yet

- EEC110A Win 2010 Final Exam: Name: ID #Document35 pagesEEC110A Win 2010 Final Exam: Name: ID #Zoro ZhaoNo ratings yet

- ) For The Given NMOS. Given: V 1 V, .: ESC201A: Assignment VIII Date: 17 March, 2015Document4 pages) For The Given NMOS. Given: V 1 V, .: ESC201A: Assignment VIII Date: 17 March, 2015Deepak TholiaNo ratings yet

- RC Coupled Amplifier - DC Operation - EXERCISE 7Document15 pagesRC Coupled Amplifier - DC Operation - EXERCISE 7Debbie ComissionNo ratings yet

- Aicd Exam SolutionDocument16 pagesAicd Exam SolutionTenzin ChoendenNo ratings yet

- Ece3110 HW 3Document7 pagesEce3110 HW 3Apricot BlueberryNo ratings yet

- Tutorial DiodeDocument15 pagesTutorial DiodeAravind KumarNo ratings yet

- Analog Electronic Circuits Lab-Module1: Gowra P SDocument5 pagesAnalog Electronic Circuits Lab-Module1: Gowra P SReddyvari VenugopalNo ratings yet

- Tutorial 2 AnsDocument9 pagesTutorial 2 AnsKemproof100% (3)

- Electronic 2 Solved ProblemDocument8 pagesElectronic 2 Solved ProblemAbdullah S OthmanNo ratings yet

- Biasing: Diodes, Transistors, Fets Practical Perspective. Prof K.Appa RaoDocument44 pagesBiasing: Diodes, Transistors, Fets Practical Perspective. Prof K.Appa RaoSuresh ThallapelliNo ratings yet

- Diodes, Home Work Solutions: 3.1 Problem 3.11Document13 pagesDiodes, Home Work Solutions: 3.1 Problem 3.11Sherweet A. AlsaadanyNo ratings yet

- Opamp Applications: Session 10: Prakash Biswagar Asst. Professor E&C Engg. Dept RV College of Engineering, BangaloreDocument35 pagesOpamp Applications: Session 10: Prakash Biswagar Asst. Professor E&C Engg. Dept RV College of Engineering, BangaloreSatya Prasad AkkinaNo ratings yet

- Lecture21 Multistage AmplifiersDocument10 pagesLecture21 Multistage AmplifierscitraumariNo ratings yet

- Design Problem: 1-Design of First StageDocument4 pagesDesign Problem: 1-Design of First StageIbrahim SaadNo ratings yet

- EE 735: Microelectronics Simulations Lab: 1. Input-Output Characteristics of The InverterDocument13 pagesEE 735: Microelectronics Simulations Lab: 1. Input-Output Characteristics of The InverterRonik JadhavNo ratings yet

- Problem Based Learning: Roll Number: 19ES31Document8 pagesProblem Based Learning: Roll Number: 19ES31Qurban AliNo ratings yet

- Quiz 1Document1 pageQuiz 1Kishor KunalNo ratings yet

- Lecture 050 - Followers: (READING: GHLM - 344-362, AH - 221-226) ObjectiveDocument7 pagesLecture 050 - Followers: (READING: GHLM - 344-362, AH - 221-226) ObjectiveArchana RkNo ratings yet

- Homework Assignment 8 SolutionDocument8 pagesHomework Assignment 8 SolutionKL Chiang100% (1)

- Electronics Design MOSFETDocument14 pagesElectronics Design MOSFETbhanuNo ratings yet

- Analog CircuitsDocument18 pagesAnalog CircuitsSAMIT KARMAKARNo ratings yet

- 2310 Lab06Document4 pages2310 Lab06tarottaurus54No ratings yet

- EE31594 Quiz 4 Dec 14, 2019Document8 pagesEE31594 Quiz 4 Dec 14, 2019Hyunsog ChoiNo ratings yet

- Home Assignment - 8: 30 September, 2013Document2 pagesHome Assignment - 8: 30 September, 2013egupta1No ratings yet

- College of Engineering Midterm Test Answer: Subject Code: Course Title: Date: Time AllowedDocument8 pagesCollege of Engineering Midterm Test Answer: Subject Code: Course Title: Date: Time AllowedMohd RashdanNo ratings yet

- Transistor: Penguat Daya Dan Perancangan Penguat Klas A (Amplifier Design)Document66 pagesTransistor: Penguat Daya Dan Perancangan Penguat Klas A (Amplifier Design)Adri Muhaimin AfifNo ratings yet

- Analog Electronics Lab ManualDocument9 pagesAnalog Electronics Lab ManualRohan KatkamNo ratings yet

- Electronic Circuit Analysis Lab: Sumathi Reddy Institute of Technology Science For WomenDocument59 pagesElectronic Circuit Analysis Lab: Sumathi Reddy Institute of Technology Science For WomenSrinivasu RajuNo ratings yet

- Pspice Simulation of Mosfet Amplifier Configurations: 2.1 ObjectiveDocument8 pagesPspice Simulation of Mosfet Amplifier Configurations: 2.1 ObjectivePreet PatelNo ratings yet

- Bistable Multivibrator Design PDFDocument20 pagesBistable Multivibrator Design PDFOmkar Thakur100% (1)

- Stable Pulse Generator Uses Matched Transistors in A Current MirrorDocument6 pagesStable Pulse Generator Uses Matched Transistors in A Current MirrorDerek RamosNo ratings yet

- Frequency Response of A Single Stage RC Coupled AmplifierDocument26 pagesFrequency Response of A Single Stage RC Coupled AmplifierkanchankonwarNo ratings yet

- Final Exam ECE 1312 Question Sem-1 2013-2014Document9 pagesFinal Exam ECE 1312 Question Sem-1 2013-2014Fatihah AinaNo ratings yet

- BJTDocument18 pagesBJTMohd Nasrul Shafiq MnsNo ratings yet

- Elec I Lab 5Document3 pagesElec I Lab 5niguisisiNo ratings yet

- EE 735: Microelectronics Simulations Lab: Circuits Assignment-1 (Due On 17th October)Document2 pagesEE 735: Microelectronics Simulations Lab: Circuits Assignment-1 (Due On 17th October)Indranil ChakrabortyNo ratings yet

- Homework #4: I I V VDocument7 pagesHomework #4: I I V Vtay ChantsNo ratings yet

- Exercise - SAMPLE BJT PROBLEMSDocument8 pagesExercise - SAMPLE BJT PROBLEMSALi AlawiehNo ratings yet

- Easy(er) Electrical Principles for General Class Ham License (2015-2019)From EverandEasy(er) Electrical Principles for General Class Ham License (2015-2019)Rating: 5 out of 5 stars5/5 (1)

- EE 436 HW2 - Spring2014Document2 pagesEE 436 HW2 - Spring2014techaddicttNo ratings yet

- EE436 HW1 Spring2014Document2 pagesEE436 HW1 Spring2014techaddicttNo ratings yet

- EE 311 Analog Electronics: Take Home Exam #2 Due: October 17, 2012 (In Class)Document1 pageEE 311 Analog Electronics: Take Home Exam #2 Due: October 17, 2012 (In Class)techaddicttNo ratings yet

- Ee311 2012HW3 PDFDocument1 pageEe311 2012HW3 PDFtechaddicttNo ratings yet