Professional Documents

Culture Documents

Questions Consolidated 11

Questions Consolidated 11

Uploaded by

Harold WilsonOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

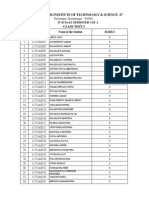

Questions Consolidated 11

Questions Consolidated 11

Uploaded by

Harold WilsonCopyright:

Available Formats

Questions for self assessment

Module 11--Lecture 1

1. What does BIST stand for? 2. Why do we require BIST even after all circuits are tested before deployment? 3. Draw and explain the basic architecture of BIST. 4. We know that in BIST, hardware pattern generator is required. Ideally speaking, the pattern generator should be able to generate the exhaustive set (i.e., generate all patterns from 0 to 2n , if there are n flip-flops in the register). A simple counter can do it. But in BIST, counters are not used as pattern generators, why? 5. Suggest circuits which can be used as pattern generators in BIST. 6. Outputs of the circuit under test in case of BIST need to be compressed, why? 7. Discuss some output compression techniques used in BIST. 8. What are the issues with output compression in terms of test coverage?

Module 11--Lecture 2,3

1. Why we consider testing of memory chips different compared to other digital (combinational/sequential) circuits? 2. What are the popular memory fault models? Among the memory fault models which are the ones that are different for the ones considered in other digital (combinational/sequential) circuits? 3. What are the different types of neighborhood considered for memory fault models? 4. What is March test? 5. Which memory faults cannot be detected by March test? How can those faults be detected? 6. Why is BIST of memory important? 7. What is the basic difference between pattern generators used in memory BIST compared to BIST of ordinary (combinational/sequential) circuits?

You might also like

- Digital System Designs and Practices: Using Verilog HDL and FpgasDocument14 pagesDigital System Designs and Practices: Using Verilog HDL and FpgasHarold WilsonNo ratings yet

- SMS MethodologyDocument33 pagesSMS MethodologySivaSubramanian100% (2)

- Xbox Architecture: Architecture of Consoles: A Practical Analysis, #13From EverandXbox Architecture: Architecture of Consoles: A Practical Analysis, #13No ratings yet

- PlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6From EverandPlayStation Architecture: Architecture of Consoles: A Practical Analysis, #6No ratings yet

- Laboratory Manual: Ho Chi Minh City University of Technology Faculty of Computer Science & EngineeringDocument8 pagesLaboratory Manual: Ho Chi Minh City University of Technology Faculty of Computer Science & EngineeringHuy Minh HoàngNo ratings yet

- Digital Registers: Serial Input Serial OutputDocument6 pagesDigital Registers: Serial Input Serial OutputHarold WilsonNo ratings yet

- Questions Consolidated 11Document1 pageQuestions Consolidated 11dycsteiznNo ratings yet

- Chapter 1Document13 pagesChapter 1jahnavi ratnamNo ratings yet

- ET5152 - Design of Embedded SystemsDocument12 pagesET5152 - Design of Embedded Systemsantoabi100% (1)

- Electronic Engineer Interview QuestionsDocument4 pagesElectronic Engineer Interview QuestionsAbhilashPadmanabhanNo ratings yet

- Cse-Viii-Advanced Computer Architectures (06CS81) - Question PaperDocument5 pagesCse-Viii-Advanced Computer Architectures (06CS81) - Question PaperDeepak Ravi ShankarNo ratings yet

- Question Bank-1913104-Design of Embedded SystemsDocument12 pagesQuestion Bank-1913104-Design of Embedded SystemsHasib Al-ariki100% (1)

- Cce521: Programming and Languages: (Lecture Notes 1)Document20 pagesCce521: Programming and Languages: (Lecture Notes 1)Lawal Ahmed ShehuNo ratings yet

- CCE521 L1 IntroductionDocument20 pagesCCE521 L1 IntroductionLawal Ahmed ShehuNo ratings yet

- CSE-MECS Super-Imp-Tie-22Document2 pagesCSE-MECS Super-Imp-Tie-22Shan MpNo ratings yet

- An Efficient Ic On Chip Test Framework To Embed TSV Testing in Memory Bist Using Dynamic TechniqueDocument5 pagesAn Efficient Ic On Chip Test Framework To Embed TSV Testing in Memory Bist Using Dynamic TechniqueijcnesNo ratings yet

- Tutorial 1: Chapter 1:general Introduction ECP4166-Advanced MicroprocessorsDocument1 pageTutorial 1: Chapter 1:general Introduction ECP4166-Advanced MicroprocessorsNiessuh IlaNo ratings yet

- LBIST Designs and Test ChallengesDocument7 pagesLBIST Designs and Test ChallengesSaransh ChoudharyNo ratings yet

- CA Part B QuestionsDocument4 pagesCA Part B QuestionsShanmathy KpNo ratings yet

- EE6602 EmbeddedDocument9 pagesEE6602 EmbeddedPraveen Kumar ReddyNo ratings yet

- What Is A MicrocontrollerDocument8 pagesWhat Is A Microcontroller123kailashNo ratings yet

- Question BankDocument2 pagesQuestion BankGeetuNo ratings yet

- Exam Questions 2018Document3 pagesExam Questions 2018naveen g cNo ratings yet

- Cse-Vii-Advanced Computer Architectures (10CS74) - Assignment PDFDocument6 pagesCse-Vii-Advanced Computer Architectures (10CS74) - Assignment PDFGovindaRajuGowdaNo ratings yet

- 1904304-Operating SystemsDocument13 pages1904304-Operating SystemsnathanselNo ratings yet

- Computer ArchitectureDocument18 pagesComputer ArchitecturepungarajanNo ratings yet

- CS8493-Operating Systems PDFDocument13 pagesCS8493-Operating Systems PDFBuvana MurugaNo ratings yet

- DFT QnsDocument6 pagesDFT QnsRajishaNo ratings yet

- VLSI Project DescriptionDocument4 pagesVLSI Project DescriptionKishoreNo ratings yet

- 8 ES QB - FiNALDocument5 pages8 ES QB - FiNALmanoj kumar reddy busireddysNo ratings yet

- Practice QuestionsDocument1 pagePractice QuestionsSwastik swarup meherNo ratings yet

- Esd 1Document40 pagesEsd 1154Soyal LonareNo ratings yet

- Vlsi Questions Unit WiseDocument3 pagesVlsi Questions Unit WisenaactitexcellenceNo ratings yet

- Camp Que BankDocument36 pagesCamp Que BankDiya ShahNo ratings yet

- Basic Comparison of PowerPC and Pentium Processor FamiliesDocument14 pagesBasic Comparison of PowerPC and Pentium Processor FamilieslokendrakashyapNo ratings yet

- 1908402-Operating System ConceptsDocument12 pages1908402-Operating System ConceptsVarshu LNo ratings yet

- Embedded Real Time SystemDocument12 pagesEmbedded Real Time SystemKottai eswariNo ratings yet

- VTU ACA 6,7,8 Important QuestionsDocument2 pagesVTU ACA 6,7,8 Important QuestionsReshma BJNo ratings yet

- 1-Definition of Microprocessor, 8 Bit - 16 Bit Processors-05-01-2024Document19 pages1-Definition of Microprocessor, 8 Bit - 16 Bit Processors-05-01-2024someshwaranmNo ratings yet

- 2-Intel I Series Processors, Distinguish Between Microprocessor and Microcontroller-14-12-2022Document19 pages2-Intel I Series Processors, Distinguish Between Microprocessor and Microcontroller-14-12-2022BRO CUBIESNo ratings yet

- A Tool For Soc Test Network Design Automation: Aram, KhzarjyanDocument4 pagesA Tool For Soc Test Network Design Automation: Aram, KhzarjyanLusine MartirosyanNo ratings yet

- Coss MidSemester RegularDocument3 pagesCoss MidSemester RegularUdayChanderAmbatiNo ratings yet

- Sheet 1Document2 pagesSheet 1Draghici Viorel PetrutNo ratings yet

- Embedded SystemDocument13 pagesEmbedded Systemjigar16789100% (1)

- Training 2Document44 pagesTraining 2Baluvu Jagadish100% (1)

- Module 1 (Part 1)Document103 pagesModule 1 (Part 1)SAATHVIK SHEKARNo ratings yet

- Avinash Eswar Intrv QuesDocument13 pagesAvinash Eswar Intrv QuesVeeresh TangadgiNo ratings yet

- Computer Organization & Architecture Questions and AnswersDocument8 pagesComputer Organization & Architecture Questions and AnswersEm PeeNo ratings yet

- Computer Organization & Architecture Questions and AnswersDocument8 pagesComputer Organization & Architecture Questions and AnswersEm PeeNo ratings yet

- db2 Cert9183 PDFDocument37 pagesdb2 Cert9183 PDFSergio LitumaNo ratings yet

- CA Classes-161-165Document5 pagesCA Classes-161-165SrinivasaRaoNo ratings yet

- Ece 309 BDocument2 pagesEce 309 BMahakNo ratings yet

- Hardware Interview QuestionsDocument5 pagesHardware Interview Questionssneha587No ratings yet

- Exec SODocument9 pagesExec SOMohamedAlyNo ratings yet

- Lecture-16-17 Design For Testability-Built-in-self-testDocument46 pagesLecture-16-17 Design For Testability-Built-in-self-testDeepika KumariNo ratings yet

- 54208-mt - Design For TestabilityDocument2 pages54208-mt - Design For TestabilitySRINIVASA RAO GANTA100% (1)

- Edk 8.1 Microblaze Tutorial in Spartan 3: ObjectivesDocument32 pagesEdk 8.1 Microblaze Tutorial in Spartan 3: ObjectivesRoshan RajuNo ratings yet

- WWW - Indiastudents.in: Question Paper CodeDocument2 pagesWWW - Indiastudents.in: Question Paper CodeBehin SamNo ratings yet

- IoT - Simp QB (1) PDFDocument2 pagesIoT - Simp QB (1) PDFRisulNo ratings yet

- FALL 2009 Computer Sciences Department University of Wisconsin-Madison Ph.D. Qualifying ExaminationDocument4 pagesFALL 2009 Computer Sciences Department University of Wisconsin-Madison Ph.D. Qualifying ExaminationAli ZahidNo ratings yet

- Question Bank of Embedded SystemDocument7 pagesQuestion Bank of Embedded Systemneelam sanjeev kumar100% (1)

- EEL4742-Lab-Manual-Embedded SystemsDocument101 pagesEEL4742-Lab-Manual-Embedded SystemsSusie KNo ratings yet

- ECAD and VLSI Lab ManualDocument107 pagesECAD and VLSI Lab ManualHarold WilsonNo ratings yet

- FGDFGFDocument5 pagesFGDFGFHarold WilsonNo ratings yet

- Question Bank Iii Semester BtechDocument18 pagesQuestion Bank Iii Semester BtechHarold WilsonNo ratings yet

- ECE 4514 Digital Design II Spring 2008 Functions and Tasks: A Language LectureDocument27 pagesECE 4514 Digital Design II Spring 2008 Functions and Tasks: A Language LectureHarold WilsonNo ratings yet

- STLD Question Bank Unit I 1: (RR, R05, Nov 08SET II, III)Document16 pagesSTLD Question Bank Unit I 1: (RR, R05, Nov 08SET II, III)Harold WilsonNo ratings yet

- ELE2120 Digital Circuits and Systems: Tutorial Note 7Document19 pagesELE2120 Digital Circuits and Systems: Tutorial Note 7Harold Wilson100% (1)

- Veltech PG Vlsi RegCDocument43 pagesVeltech PG Vlsi RegCtiitumaNo ratings yet

- ECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationDocument49 pagesECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationHarold WilsonNo ratings yet

- Nominal Rolls Cse A & B 3 Class TestDocument4 pagesNominal Rolls Cse A & B 3 Class TestHarold WilsonNo ratings yet

- Frequently Asked Questions On PGEC/PGECET AdmissionsDocument1 pageFrequently Asked Questions On PGEC/PGECET AdmissionsHarold WilsonNo ratings yet

- List of Helpline Centers: S.No Name of The Help Line CentreDocument1 pageList of Helpline Centers: S.No Name of The Help Line CentreHarold WilsonNo ratings yet

- Batch-3 First Contact PGMDocument58 pagesBatch-3 First Contact PGMHarold WilsonNo ratings yet

- Certificates SubmittedDocument1 pageCertificates SubmittedHarold WilsonNo ratings yet

- Jntu Kak 2 2 Eee STLD Set 1 2Document18 pagesJntu Kak 2 2 Eee STLD Set 1 2Harold WilsonNo ratings yet

- Phase-I Admissions: Admission Schedule PGECET-2014Document1 pagePhase-I Admissions: Admission Schedule PGECET-2014Harold WilsonNo ratings yet

- EE-2171 Digital Logic: Course SpecificationDocument2 pagesEE-2171 Digital Logic: Course SpecificationHarold WilsonNo ratings yet