Professional Documents

Culture Documents

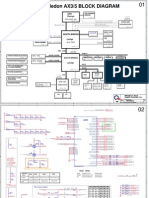

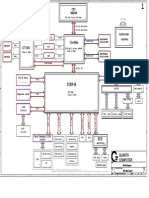

Packard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCH

Packard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCH

Uploaded by

Aloui ZakariaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Packard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCH

Packard-Bell Easynote Ml65 Vesurio Pb5 Pb6 Quanta Pb5 Pb6 Rev 1a SCH

Uploaded by

Aloui ZakariaCopyright:

Available Formats

1

01

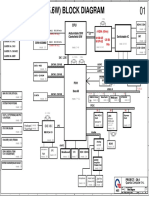

PB5/6 Block Diagram

VCC_CORE

CLOCK GENERATOR

+1.5V

+1.05V

Intel

PENRYN

uFCPGA

CRT

CK505

ICS9LPR363

Page 2

A

Page 20

Page 3,4

+1.25V

INT MIC

Page 19

Page 19

HDMI

VGA CONNECTOR

+1.8VSUS

+1.8V

CRT

FSB(667/800MHZ)

LCD PANEL

LCD/LED

CRT

+3VPCU

+3V_S5

+3VSUS

+3V

+5VPCU

+5V_S5

+5V

+SMDDR_VTERM

+SMDDR_VREF

LVDS

533/ 667 MHZ DDR II

SATA

SATA - HDD

Page 18

PCI-E 16X Lan

NB

CANTIGA

DDRII-SODIMM1

DDRII-SODIMM2

Page 5,7,8,9,10,11

Page 16, 17

Page 22

SATA

SATA - ODD

DMI(x2/x4)

MINI CARD-4

ROBSON

Page 22

(FTB)

Page 25

SATA

eSATA

PCI-Express

Page 22

USB-5

WLAN

SB

ICH9M

USB 2.0

Page 25

Camera

PCIE-4

PCIE-6

PCIE-3

PCIE-1

MINI CARD-1

WLAN

MINI CARD-2

UMA TV/ROBSON

NEW CARD

Page 25

USB-3

Page 25

PCIE-5

LAN

RTL8102

Page 27

Page 26

PCI Bus

Page 19

Bluetooth

USB-2

Azalia

Page 12, 13, 14, 15

OZ129

Page 26

New Card

Page 24

USB-9

LPC

32.768KHz

Page 27

C

M/B USB2

4 IN 1

USB-7

Page 24

1394

C

Page 24

Page 27

M/B USB

ITE8512

USB-6

VGA

Board

Page 27

TV/ROBSON

Page 28

USB-8

Page 25

USB

Board

Port-A

HP

Page 30

Port-B

MIC JACK

AUDIO CODEC

ALC268/ALC272

FAN

T/P

Board

Key

Board

FLASH

ROM

CIR

Page 3

Page 26

Page 26

Page 28

Page 28

Touch Pad

Board

Daughter

Board

Function

Board

Page 29

Page 30

D

INT SPK

Page 29

SPK AMP

Page 29

PROJECT : PB5/6

Quanta Computer Inc.

http://mycomp.su/x/

1

Size

Document Number

Date:

Friday, March 21, 2008

Rev

1A

Block Diagram

3

Sheet

1

8

of

35

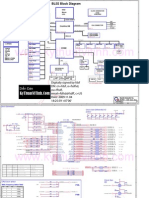

Clock Generator

PBY160808T-301Y-N_6

L41

VCC3

02

VCCP_VDD

PBY160808T-301Y-N_6

C507

0.1u/10V_4

C553

C544

C540

C543

C528

C532

C537

C545

*10u/10V_6

10u/10V_6

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

L50

VCCP

C535

C88

0.1u/10V_4

C521

10u/10V_6

10u/10V_6

C84

0.1u/10V_4

C542

0.1u/10V_4

C515

0.1u/10V_4

C93

T36

PCLK_OZ129

25 PCLK_OZ129

CG_XIN

33p/50V_4

2

C101

Y2

33p/50V_4

14.318MHZ

C100

PCLK_EC

28 PCLK_EC

CL=20p

13

PCLK_ICH

PCLK_ICH

R118

56

R86

CLK_BSEL0 R91

VDD_PCI

VDD_48

VDD_PLL3

VDD_REF

VDD_CK_VDD_PCI

VDD_CK_VDD_CPU

39

55

VDD_SRC

VDD_CPU

12

20

26

45

36

49

VDD_96_IO

VDD_PLL3_IO

VDD_SRC_IO_1

VDD_SRC_IO_3

VDD_SRC_IO_2

VDD_CPU_IO

R114

33_4

R110

PCLK_DEBUG_R

PCI0/CR#_A

PCLK_PCM_R

PCI1/CR#_B

33_4

PCLK_OZ129_R

PCI2/TME

R109

10K_4

PCI_CLK_SIO_R

PCI3

R107

33_4

PCLK_EC_R

PCI4/SRC5_EN

R101

33_4

CG_XOUT

14 CLKUSB_48

2

9

16

61

VCCP_VDD

0.1u/10V_4

PCLK_DEBUG

24 PCLK_DEBUG

PCLK_ICH_R

7

60

XTAL_IN

CG_XOUT

59

XTAL_OUT

FSA

33_4

2.2K_4

10

14

14M_ICH

R108

USB_48/FSA

FSB

57

FSB/TEST/MODE

FSC

62

REF0/FSC/TESTSEL

8

11

15

19

52

23

29

42

58

10K_4

33_4

IO_VOUT

48

SCLK

SDA

64

63

CGCLK_SMB

CGDAT_SMB

SRC5/PCI_STOP#

SRC5#/CPU_STOP#

38

37

PM_STPPCI#

PM_STPCPU#

CPU0

CPU0#

54

53

CLK_CPU_BCLK_R

CLK_CPU_BCLK#_R

RP14

CPU1

CPU1#

51

50

CLK_MCH_BCLK_R

CLK_MCH_BCLK#_R

RP12

SRC8/ITP

SRC8#/ITP#

47

46

CLK_PCIE_MINI3_R

CLK_PCIE_MINI3#_R

SRC10#

SRC10

35

34

CLK_PCIE_3GPLL#_R

CLK_PCIE_3GPLL_R

SRC11/CR#_H

SRC11#/CR#_G

33

32

CLK_MCH_OE#_R

NEW_CLKREQ#_R

R74

R73

SRC9

SRC9#

30

31

CLK_PCIE_NEW_R

CLK_PCIE_NEW_R#

RP2

3

1

4 0X2

2

SRC7/CR#_F

SRC7#/CR#_E

44

43

CLK_PCIE_MINI2_R

CLK_PCIE_MINI2#_R

RP8

1

3

2 0X2

4

SRC6

SRC6#

41

40

CLK_PCIE_MINI_R

CLK_PCIE_MINI#_R

RP6

1

3

2 0X2

4

CLK_PCIE_MINI 24

CLK_PCIE_MINI# 24

To WLAN

SRC4

SRC4#

27

28

CLK_PCIE_LAN_R

CLK_PCIE_LAN#_R

RP4

3

1

4 0X2

2

CLK_PCIE_LAN 23

CLK_PCIE_LAN# 23

To LAN

CK505

PCIF5/ITP_EN

CG_XIN

CLK_BSEL1

CLK_BSEL2 R111

U8

VDD_CK_VDD_PCI

VDD_CK_VDD_48

VDD_CK_VDD_PCI

VDD_CK_VDD_REF

VSS_PCI

VSS_48

VSS_IO

VSS_PLL3

VSS_CPU

VSS_SRC1

VSS_SRC2

VSS_SRC3

VSS_REF

BOM Option Table

PM_STPPCI# 14

PM_STPCPU# 14

To SB

1

3

2 0X2

4

CLK_CPU_BCLK 3

CLK_CPU_BCLK# 3

To CPU

1

3

2 0X2

4

CLK_MCH_BCLK 5

CLK_MCH_BCLK# 5

To NB

RP10

1

3

2 IV@0X2

4

RP3

1

3

2 0X2

4

CLK_PCIE_MINI3 24

CLK_PCIE_MINI3# 24

INT VGA

EXT VGA

To NB

CLK_MCH_OE# 6

NEW_CLKREQ# 24

CLK_PCIE_NEW 24

CLK_PCIE_NEW# 24

To New Card

CLK_PCIE_MINI2 24

CLK_PCIE_MINI2# 24

VCC3

To TV

PM_STPPCI#

R76

PM_STPCPU#

R75

2.2K_4

NEW_CLKREQ#_R

R560

10K_4

2.2K_4

SRC3/CR#_C

SRC3#/CR#_D

24

25

CLK_PCIE_ICH_R

CLK_PCIE_ICH#_R

RP5

3

1

4 0X2

2

CLK_PCIE_ICH 13

CLK_PCIE_ICH# 13

To SB

SRC2/SATA

SRC2#/SATA#

21

22

CLK_PCIE_SATA_R

CLK_PCIE_SATA#_R

RP7

3

1

4 0X2

2

CLK_PCIE_SATA 12

CLK_PCIE_SATA# 12

To SB

SRC1/SE1

SRC1#/SE2

17

18

DREFSSCLK_R

DREFSSCLK#_R

SRC0/DOT96

SRC0#/DOT96#

13

14

DREFCLK_R

DREFCLK#_R

3

1

4 0

2

DREFCLK 6

DREFCLK# 6

To NB

CKPWRGD/PWRDWN#

56

RP13

Description

IV@

EV@

To ROBSON

CLK_PCIE_3GPLL# 6

CLK_PCIE_3GPLL 6

475/F_4

475/F_4

Reference

CK_PWRGD 14

ICS9LPRS365BGLFT

ICS9LPRS365

RTM875T-606

(ALPRS365K13) (AL000875K06)

Pin 4

PCI2/TME

PCI2/TME

internal PD

Pin 5

PCI-3

PCI-3/SRC5_EN

internal PD

Pin 6

PCI-4/27M_SEL

PCI-4/27M_SEL internal PD

Pin 7

PCIF-5/ITP_EN

PCIF-5/ITP_EN internal PD

PULL HIGH

VCC3

PULL DOWN

NO OVERCLOCKING

PIN37/38 IS SRC5

PIN37/38 IS

PCI_STOP/CPU_STOP

(default)

PIN 17/18 IS 27MHz

PIN 17/18

IS SRC/DOT

(default)

(default)

PIN 46/47 IS CPUITP

R520

10K_4

R113

*10K_4

R521

*10K_4

R106

10K_4

PCLK_OZ129

<MAIN>:ICS9LPRS365BGLFT QCI:ALPRS365K13

<SECOND>:SLG8SP512TTR: QCI:AL8SP512K05

NORMAL RUN

PIN 46/47 IS SRC8

VCC3

(default)

VCC3

R526

*10K_4

R100

10K_4

PCLK_EC

HIGH 27MHz

LOW SRC

DREFSSCLK_R

DREFSSCLK#_R

RP9

RP11

PCLK_ICH

1

3

2 IV@0X2

4

DREFSSCLK 6

DREFSSCLK# 6

To NB

3

1

4

2

CLK_MXM 20

CLK_MXM# 20

To VGA Card

EV@0X2

VCC3

FREQ. SEL TABLE

Clock Gen I2C

VCCP

BSEL Frequency Select Table

FSC

FSB

FSA

Frequency

266Mhz

133Mhz

166Mhz

VCCP

200Mhz

400Mhz

Reserved

100Mhz

333Mhz

R88

*56_4

3 CPU_BSEL2

VCCP

R95

CLK_BSEL0

Q7

2

0_4

R89

3 CPU_BSEL1

R87

MCH_BSEL0 6

14,24

SDATA

1K_4

*0_4

R94

1K_4

R112

0_4

R116

*0_4

R117

1K_4

10K_4

CGDAT_SMB

CGDAT_SMB 17

CLK_BSEL1

MCH_BSEL1 6

14,24

CLK_BSEL2

SCLK

Q8

R134

RHU002N06

10K_4

CGCLK_SMB

10p

C508

10p

CLKUSB_48

C87

10p

14M_ICH

C95

10p

PCLK_ICH

C512

10p

PCLK_DEBUG C505

22p

MCH_BSEL2 6

PROJECT : PB5/6

Quanta Computer Inc.

Document Number

Rev

1A

CLK GEN

Date:

http://mycomp.su/x/

C506

PCLK_EC

CGCLK_SMB 17

Size

PCLK_OZ129

VCC3

0_4

R93

R127

RHU002N06

3 CPU_BSEL0

Sheet

Friday, May 30, 2008

1

of

35

H_A#[3..16]

12

12

12

12

R578

H_INTR

H_NMI

H_SMI#

H_STPCLK#

H_INTR

H_NMI

H_SMI#

A6

A5

C4

0_4

T19

T18

T15

T13

T158

T159

T26

T160

T20

A20M#

FERR#

IGNNE#

D5

C6

B4

A3

STPCLK#

LINT0

LINT1

SMI#

M4

N5

T2

V3

B2

D2

D22

D3

F6

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

RSVD[08]

RSVD[09]

F1

H_BREQ#

D20

B3

H_IERR#

H_INIT#

LOCK#

H4

H_LOCK#

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

C1

F3

F4

G3

G2

H_CPURST#

H_RS#0

H_RS#1

H_RS#2

H_TRDY#

HIT#

HITM#

G6

E4

H_HIT#

H_HITM#

CONTROL

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TCK

TDI

TDO

TMS

TRST#

DBR#

PROCHOT#

THERMDA

THERMDC

THERMTRIP#

ZS2 Default no use this function

H_BREQ# 5

R67

H_INIT#

56_4

VCCP

12

H_LOCK# 5

H_CPURST# 5

H_RS#0 5

H_RS#1 5

H_RS#2 5

H_TRDY# 5

H_HIT#

H_HITM#

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

XDP_BPM#3

XDP_BPM#4

XDP_BPM#5

XDP_TCK

XDP_TDI

XDP_TDO

XDP_TMS

XDP_TRST#

XDP_DBRESET#

D21

A24

B25

H_PROCHOT#_D

H_THERMDA

H_THERMDC

T11

T7

T6

T9

T10

T5

5

5

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_D#[16..31]

Connect it to CPU DBR# is for ITP debug port

or CPU interposer (like ICE) to reset the system

0_4 SYS_RST#

R68

5

5

5

VCCP

SYS_RST# 14

R40

1K/F_4

5

5

5

H_DSTBN#1

H_DSTBP#1

H_DINV#1

CPU_PM_THRMTRIP#

T25

T23

T22

T12

T8

T24

T21

R39

2K/F_4

H CLK

BCLK[0]

BCLK[1]

A22

A21

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_DSTBN#0

H_DSTBP#0

H_DINV#0

H_DEFER# 5

H_DRDY# 5

H_DBSY# 5

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

C7

H_D#[0..15]

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_CPU_BCLK 2

CLK_CPU_BCLK# 2

2

2

2

Layout note:

H_GTLREF: Zo=55 ohm,L<0.5"

2/3*VCCP+-2%

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

E22

F24

E26

G22

F23

G25

E25

E23

K24

G24

J24

J23

H22

F26

K22

H23

J26

H26

H25

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_DSTBN#1

H_DSTBP#1

H_DINV#1

N22

K25

P26

R23

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

T25

N25

L26

M26

N24

H_GTLREF

CPU_TEST1

CPU_TEST2

CPU_TEST3

CPU_TEST4

CPU_TEST5

CPU_TEST6

CPU_TEST7

CPU_BSEL0

CPU_BSEL1

CPU_BSEL2

AD26

C23

D25

C24

AF26

AF1

A26

C3

B22

B23

C21

D[0]#

D[1]#

D[2]#

D[3]#

D[4]#

D[5]#

D[6]#

D[7]#

D[8]#

D[9]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

DSTBN[0]#

DSTBP[0]#

DINV[0]#

D[16]#

D[17]#

D[18]#

D[19]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[30]#

D[31]#

DSTBN[1]#

DSTBP[1]#

DINV[1]#

GTLREF

TEST1

TEST2

TEST3

TEST4

TEST5

TEST6

TEST7

BSEL[0]

BSEL[1]

BSEL[2]

BOM Option Table

H_DSTBN#2 5

H_DSTBP#2 5

H_DINV#2 5

H_D#[48..63]

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_DSTBN#3

H_DSTBP#3

H_DINV#3

COMP[0]

COMP[1]

COMP[2]

COMP[3]

R26

U26

AA1

Y1

COMP0

COMP1

COMP2

COMP3

DPRSTP#

DPSLP#

DPWR#

PWRGOOD

SLP#

PSI#

E5

B5

D24

D6

D7

AE6

ICH_DPRSTP#

H_DPSLP#

H_DPWR#

H_PWRGD

H_CPUSLP#

PSI#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DSTBN[3]#

DSTBP[3]#

DINV[3]#

MISC

H_D#[32..47]

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_DSTBN#2

H_DSTBP#2

H_DINV#2

Y22

AB24

V24

V26

V23

T22

U25

U23

Y25

W22

Y23

W24

W25

AA23

AA24

AB25

Y26

AA26

U22

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DSTBN[2]#

DSTBP[2]#

DINV[2]#

DATA GRP 2

H_DEFER#

H_DRDY#

H_DBSY#

U29B

5

5

5

DATA GRP 3

H5

F21

E1

H_ADS#

H_BNR#

H_BPRI#

THERMAL

ICH

H_A20M#

H_FERR#

H_IGNNE#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

H_ADS#

H_BNR#

H_BPRI#

IERR#

INIT#

BR0#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

H1

E2

G5

DATA GRP 1

H_ADSTB#1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

U2

V4

W3

AA4

AB2

AA3

V1

DEFER#

DRDY#

DBSY#

ADDR GROUP_1

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADSTB#1

12 H_A20M#

12 H_FERR#

12 H_IGNNE#

C

K3

H2

K2

J3

L1

ADS#

BNR#

BPRI#

XDP/ITP SIGNALS

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_A#[17..35]

03

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

DATA GRP 0

H_ADSTB#0

H_REQ#[0..4]

J4

L5

L4

K5

M3

N2

J1

N3

P5

P2

L2

P4

P1

R1

M1

ADDR GROUP_0

U29A

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_ADSTB#0

5

5

Reference

Description

N/A

N/A

H_DSTBN#3 5

H_DSTBP#3 5

H_DINV#3 5

R48

R47

R43

R44

27.4/F_6

54.9/F_4

27.4/F_6

54.9/F_4

Layout note:

comp0,2: Zo=27.4ohm, L<0.5"

comp1,3: Zo=55ohm, L<0.5"

C

ICH_DPRSTP# 6,12,31

H_DPSLP# 12

H_DPWR# 5

H_PWRGD 12

H_CPUSLP# 5

PSI#

31

Penryn_1p0

RESERVED

Layout note:

ICH_DPRSTP# , Daisy Chain

(SB>PowerIC>NB>CPU)

Penryn_1p0

Thermal Trip

XDP

VCCP

CPU Thermal monitor

VCCP

VCCP

VCC3

D31

R581

FDV301N

*10K_4

*BAS316

*51/F_4

2

H_CPURST#

VCCP

R32

R33

R34

*51/F_4

56_4

54.9/F_4

XDP_TCK

XDP_TRST#

R36

R35

56_4

56_4

Q22

3

20,28,35 MBCLK

2

1

SYS_SHDN#

R568

10K_4

10K_4

U27

2

3

Q24

2ND_MBCLK#

7

8

SDAT

SCLK

2ND_MBDATA#

VCC

RHU002N06

5

SYS_SHDN#

30

*0_4 PM_THRMTRIP#

R563

*10K_4

R565

0_4

VCC3

R566

10K_4

VCC3

R569

330_4

VCC3

PM_THRMTRIP# 6,12

14,29 THERM_ALERT#

No use Thermal trip CPU side still PU 56ohm.

Use Thermal trip can share PU at SB side

4

6

DXP

C555

DXN

2200p/50V_4

H_THERMDA

H_THERMDC

ADDRESS: 98H

THERM_ALERT#_R

Processor hot

GND

OVT

ALERT

G780

NS LM95245 PU this pin

R571

0.1u/10V_4

20,28,35 MBDATA

Q26

MMBT3904

3

R562

RHU002N06

C562

*1u/16V_6

56.2/F_4

200_6 LM86VCC C554

R561

XDP_TDO

XDP_TDI

XDP_TMS

R572

CPU_PM_THRMTRIP#

VCC3

VCCP

Reserve 1K for XDP function

6,14,31 DELAY_VR_PWRGOOD

R580

VCC3

Q29

30

SYS_SHDN#

VCCP

Q23

THER_SHD#

MMBT3904

No use PROCHOT CPU side still PU 56ohm.

Use PROCHOT to optional receiver CPU side PU

68ohm and through isolat 2.2K ohm to receiver

side

R71

A

56_4

H_PROCHOT#_D

R70

*0_4

H_PROCHOT# 31

PROJECT : PB5/6

Quanta Computer Inc.

Size

Document Number

Rev

1A

CPU(1/2) HOST BUS

Date:

5

http://mycomp.su/x/

Sheet

Friday, May 30, 2008

1

of

35

04

BOM Option Table

Reference

Description

N/A

N/A

Need NC 20PCS 10u before A1 BOM released(A0 all stuff)

Place these parts reference

to Intel demo board.

U29D

A4

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C11

C14

C16

C19

C2

C22

C25

D1

D4

D8

D11

D13

D16

D19

D23

D26

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G23

G26

H3

H6

H21

H24

J2

J5

J22

J25

K1

K4

K23

K26

L3

L6

L21

L24

M2

M5

M22

M25

N1

N4

N23

N26

P3

VSS[001]

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

VSS[009]

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

VSS[017]

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

VSS[023]

VSS[024]

VSS[025]

VSS[026]

VSS[027]

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

VSS[035]

VSS[036]

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

VSS[044]

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

VSS[050]

VSS[051]

VSS[052]

VSS[053]

VSS[054]

VSS[055]

VSS[056]

VSS[057]

VSS[058]

VSS[059]

VSS[060]

VSS[061]

VSS[062]

VSS[063]

VSS[064]

VSS[065]

VSS[066]

VSS[067]

VSS[068]

VSS[069]

VSS[070]

VSS[071]

VSS[072]

VSS[073]

VSS[074]

VSS[075]

VSS[076]

VSS[077]

VSS[078]

VSS[079]

VSS[080]

VSS[081]

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

VSS[082]

VSS[083]

VSS[084]

VSS[085]

VSS[086]

VSS[087]

VSS[088]

VSS[089]

VSS[090]

VSS[091]

VSS[092]

VSS[093]

VSS[094]

VSS[095]

VSS[096]

VSS[097]

VSS[098]

VSS[099]

VSS[100]

VSS[101]

VSS[102]

VSS[103]

VSS[104]

VSS[105]

VSS[106]

VSS[107]

VSS[108]

VSS[109]

VSS[110]

VSS[111]

VSS[112]

VSS[113]

VSS[114]

VSS[115]

VSS[116]

VSS[117]

VSS[118]

VSS[119]

VSS[120]

VSS[121]

VSS[122]

VSS[123]

VSS[124]

VSS[125]

VSS[126]

VSS[127]

VSS[128]

VSS[129]

VSS[130]

VSS[131]

VSS[132]

VSS[133]

VSS[134]

VSS[135]

VSS[136]

VSS[137]

VSS[138]

VSS[139]

VSS[140]

VSS[141]

VSS[142]

VSS[143]

VSS[144]

VSS[145]

VSS[146]

VSS[147]

VSS[148]

VSS[149]

VSS[150]

VSS[151]

VSS[152]

VSS[153]

VSS[154]

VSS[155]

VSS[156]

VSS[157]

VSS[158]

VSS[159]

VSS[160]

VSS[161]

VSS[162]

VSS[163]

Layout Note:

Inside CPU center cavity in 2 rows

VCC_CORE

VCC_CORE

U29C

C586

C588

C35

C591

C27

C573

C599

C38

C59

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C10

C12

C13

C15

C17

C18

D9

D10

D12

D14

D15

D17

D18

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AB9

AC10

AB10

AB12

AB14

AB15

AB17

AB18

VCC_CORE

C593

C46

C54

C39

C594

C597

C45

C31

C26

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

VCC_CORE

C658

C589

C598

C32

C29

C574

C61

C28

C37

C595

0.1u

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

VCC_CORE

C659

C587

C592

C585

C583

C584

C596

C572

C590

C571

0.1u

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

10u/10V_8

Penryn_1p0

.

VCC_CORE

C44

VCC_CORE Bulk CAPs place

to BOT of CPU centeral

C58

+

330u/2.5V_7343

330u/2.5V_7343

VCC_CORE

VCC[001]

VCC[002]

VCC[003]

VCC[004]

VCC[005]

VCC[006]

VCC[007]

VCC[008]

VCC[009]

VCC[010]

VCC[011]

VCC[012]

VCC[013]

VCC[014]

VCC[015]

VCC[016]

VCC[017]

VCC[018]

VCC[019]

VCC[020]

VCC[021]

VCC[022]

VCC[023]

VCC[024]

VCC[025]

VCC[026]

VCC[027]

VCC[028]

VCC[029]

VCC[030]

VCC[031]

VCC[032]

VCC[033]

VCC[034]

VCC[035]

VCC[036]

VCC[037]

VCC[038]

VCC[039]

VCC[040]

VCC[041]

VCC[042]

VCC[043]

VCC[044]

VCC[045]

VCC[046]

VCC[047]

VCC[048]

VCC[049]

VCC[050]

VCC[051]

VCC[052]

VCC[053]

VCC[054]

VCC[055]

VCC[056]

VCC[057]

VCC[058]

VCC[059]

VCC[060]

VCC[061]

VCC[062]

VCC[063]

VCC[064]

VCC[065]

VCC[066]

VCC[067]

VCCP_CPU

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

VCCP[01]

VCCP[02]

VCCP[03]

VCCP[04]

VCCP[05]

VCCP[06]

VCCP[07]

VCCP[08]

VCCP[09]

VCCP[10]

VCCP[11]

VCCP[12]

VCCP[13]

VCCP[14]

VCCP[15]

VCCP[16]

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

CPU_G21

VCCA[01]

VCCA[02]

B26

C26

+VCCA_PROC

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

AD6

AF5

AE5

AF4

AE3

AF3

AE2

VCCSENSE

AF7

VSSSENSE

AE7

C52

C41

C48

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

VCCP_CPU

C34

C57

C36

0.1u/10V_4

0.1u/10V_4

0.1u/10V_4

VCCP_CPU

R51

0_4

VCCP

R564

+

0_1206

C556

VCCP Bulk CAP

close to Pin

270u/2V_7343

VCC1.5

R69

H_VID0

H_VID1

H_VID2

H_VID3

H_VID4

H_VID5

H_VID6

31

31

31

31

31

31

31

C78

C72

0.01u/16V_4

10u/10V_8

0_6

Place 0.01u

near pin-B26

VCC_CORE

Penryn_1p0

.

R586

Penryn CPU Power Status and max current table

POWER PLANE S0

S3

S4/S5

Voltage

I(max)

100/F_6

Note

VCC_CORE

VID

47A

Standard Voltage CPU

VCC_CORE

VID

50A

SV Design Target

VCC_CORE

VID

TBD

Extreme Edition CPU

VCC_CORE

VID

67A

EE Design Target

VCCA

+1.5V

130mA

VCCP

+1.05V

4.5A

Before VCC Stable

VCCP

+1.05V

2.5A

After VCC Stable

VCCSENSE 31

VSSSENSE 31

R587

100/F_6

Layout Note:

Route VCCSENSE and VSSSENSE traces at

27.4 Ohms with 50 mil spacing.

Place PU and PD within 1 inch of CPU.

(See Penryn EMTS Rev:1.0 Table7,8 for voltage and current)

(See Penryn EMTS Rev:1.0 Table-3 for VID table)

PROJECT : PB5/6

Quanta Computer Inc.

Size

Document Number

Rev

1A

CPU(2/2) POWER

Date:

5

http://mycomp.su/x/

Sheet

Friday, May 30, 2008

1

of

35

05

H_A#[3..16] 3

H_D#[0..15]

VCCP

H_D#[16..31]

H_D#[32..47]

0.3125*VCCP

W:10,S:20 , L<0.5"

R538

221/F_4

H_SWING

C

R530

C509

100/F_4

0.1u/10V_4

W:10,S:20 , L<0.5"

H_RCOMP

H_D#[48..63]

R128

24.9/F_4

B

VCCP

2/3*VCCP

W:10,S:20 , L<0.5"

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

R539

F2

G8

F8

E6

G2

H6

H2

F6

D4

H3

M9

M11

J1

J2

N12

J6

P2

L2

R2

N9

L6

M5

J3

N2

R1

N5

N6

P13

N8

L7

N10

M3

Y3

AD14

Y6

Y10

Y12

Y14

Y7

W2

AA8

Y9

AA13

AA9

AA11

AD11

AD10

AD13

AE12

AE9

AA2

AD8

AA3

AD3

AD7

AE14

AF3

AC1

AE3

AC3

AE11

AE8

AG2

AD6

C5

E3

H_D#_0

H_D#_1

H_D#_2

H_D#_3

H_D#_4

H_D#_5

H_D#_6

H_D#_7

H_D#_8

H_D#_9

H_D#_10

H_D#_11

H_D#_12

H_D#_13

H_D#_14

H_D#_15

H_D#_16

H_D#_17

H_D#_18

H_D#_19

H_D#_20

H_D#_21

H_D#_22

H_D#_23

H_D#_24

H_D#_25

H_D#_26

H_D#_27

H_D#_28

H_D#_29

H_D#_30

H_D#_31

H_D#_32

H_D#_33

H_D#_34

H_D#_35

H_D#_36

H_D#_37

H_D#_38

H_D#_39

H_D#_40

H_D#_41

H_D#_42

H_D#_43

H_D#_44

H_D#_45

H_D#_46

H_D#_47

H_D#_48

H_D#_49

H_D#_50

H_D#_51

H_D#_52

H_D#_53

H_D#_54

H_D#_55

H_D#_56

H_D#_57

H_D#_58

H_D#_59

H_D#_60

H_D#_61

H_D#_62

H_D#_63

HOST

U26A

3

H_SWING

H_RCOMP

1K/F_4

H_AVREF

R534

R522

0_4

3

3

H_CPURST#

H_CPUSLP#

H_CPURST#

H_CPUSLP#

C12

E11

H_CPURST#

H_CPUSLP#

H_DVREF

H_AVREF

H_DVREF

2K/F_4

A11

B11

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

H_ADS#

H_ADSTB#0

H_ADSTB#1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

CLK_MCH_BCLK

CLK_MCH_BCLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

J8

L3

Y13

Y1

H_DINV#0

H_DINV#1

H_DINV#2

H_DINV#3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

L10

M7

AA5

AE6

H_DSTBN#0

H_DSTBN#1

H_DSTBN#2

H_DSTBN#3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

L9

M8

AA6

AE5

H_DSTBP#0

H_DSTBP#1

H_DSTBP#2

H_DSTBP#3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

B15

K13

F13

B13

B14

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#_0

H_RS#_1

H_RS#_2

B6

F12

C8

H_RS#0

H_RS#1

H_RS#2

BOM Option Table

Reference

Description

N/A

N/A

H_A#[17..35] 3

H_ADS# 3

H_ADSTB#0 3

H_ADSTB#1 3

H_BNR# 3

H_BPRI# 3

H_BREQ# 3

H_DEFER# 3

H_DBSY# 3

CLK_MCH_BCLK 2

CLK_MCH_BCLK# 2

H_DPWR# 3

H_DRDY# 3

H_HIT# 3

H_HITM# 3

H_LOCK# 3

H_TRDY# 3

H_DINV#[3..0]

3

B

H_DSTBN#[3..0] 3

H_DSTBP#[3..0] 3

H_REQ#[0..4] 3

H_RS#[2..0] 3

H_AVREF

H_DVREF

CANTIGA_1p2

PROJECT : PB5/6

Quanta Computer Inc.

Size

Document Number

Rev

1A

NB (1/7) HOST

Date:

5

http://mycomp.su/x/

Friday, May 30, 2008

Sheet

1

of

35

BOM Option Table

Reference

U26B

RSVD14

B31

RSVD15

MCH_RSVD17

T51

T72

T38

T74

T76

T156

T75

M1

RSVD17

MCH_RSVD20

AY21

RSVD20

MCH_RSVD21

MCH_RSVD22

MCH_RSVD23

MCH_RSVD24

MCH_RSVD25

B2

BG23

BF23

BH18

BF18

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

M_CLK_DDR0

M_CLK_DDR1

M_CLK_DDR3

M_CLK_DDR4

SA_CK#_0

SA_CK#_1

SB_CK#_0

SB_CK#_1

AR24

AR21

AU24

AV20

M_CLK_DDR#0

M_CLK_DDR#1

M_CLK_DDR#3

M_CLK_DDR#4

SA_CKE_0

SA_CKE_1

SB_CKE_0

SB_CKE_1

BC28

AY28

AY36

BB36

M_CKE0

M_CKE1

M_CKE3

M_CKE4

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

BA17

AY16

AV16

AR13

M_CS#0

M_CS#1

M_CS#2

M_CS#3

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

BD17

AY17

BF15

AY13

M_ODT0

M_ODT1

M_ODT2

M_ODT3

SM_RCOMP

SM_RCOMP#

BG22

BH21

M_RCOMP

M_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

BF28

BH28

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_VREF

SM_PWROK

SM_REXT

SM_DRAMRST#

AV42

AR36

BF17

BC36

SM_VREF

SM_PWROK

SM_REXT

MCH_SM_DRAMRST#

B38

A38

E41

F41

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

F43

E43

CLK_PCIE_3GPLL

CLK_PCIE_3GPLL#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

AE41

AE37

AE47

AH39

DMI_TXN0

DMI_TXN1

DMI_TXN2

DMI_TXN3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

AE40

AE38

AE48

AH40

DMI_TXP0

DMI_TXP1

DMI_TXP2

DMI_TXP3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

AE35

AE43

AE46

AH42

DMI_RXN0

DMI_RXN1

DMI_RXN2

DMI_RXN3

R99

R528

R147

R143

R203

R186

R141

R104

0_4

0_4

0_4

0_4

0_4

100_4

*0_4

0_4

PM_DPRSTP#

The Daisy chain topology should

be routed from ICH9M to IMVP ,

then to (G)MCH and CPU, in that

order.

B

RST_IN#_MCH

THRMTRIP#_R

DPRSLPVR_R

AT11

T20

R32

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

TP_MCH_NC1

TP_MCH_NC2

TP_MCH_NC3

TP_MCH_NC4

TP_MCH_NC5

TP_MCH_NC6

TP_MCH_NC7

TP_MCH_NC8

TP_MCH_NC9

TP_MCH_NC10

TP_MCH_NC11

TP_MCH_NC12

TP_MCH_NC13

TP_MCH_NC14

TP_MCH_NC15

TP_MCH_NC16

TP_MCH_NC17

TP_MCH_NC18

TP_MCH_NC19

TP_MCH_NC20

TP_MCH_NC21

TP_MCH_NC22

TP_MCH_NC23

TP_MCH_NC24

TP_MCH_NC25

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

CLK

DMI

NC

T153

T146

T143

T139

T152

T80

T154

T145

T78

T151

T144

T150

T149

T142

T138

T148

T73

T155

T77

T157

T141

T137

T147

T140

T44

NB Thermal trip pin

No use Thermal trip NB side can

NC.(NB has ODT)

PM_SYNC#_R

R29

ICH_DPRSTP#_R

B7

PM_EXTTS#0_1_EC_R N33

TS#DIMM0_1_R

P32

AT40

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

AD35

AE44

AF46

AH43

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

B33

B32

G33

F33

E33

GFX_VR_EN

EV_IV@

EV&IV diff. value

M_CLK_DDR#0 17

M_CLK_DDR#1 17

M_CLK_DDR#3 17

M_CLK_DDR#4 17

M_CKE0

M_CKE1

M_CKE3

M_CKE4

16,17

16,17

16,17

16,17

U26C

L<0.5" , If PCIE not support

still connect to +VCC_PEG

LVDS I/F

M_CS#0 16,17

M_CS#1 16,17

M_CS#2 16,17

M_CS#3 16,17

M_ODT0 16,17

M_ODT1 16,17

M_ODT2 16,17

M_ODT3 16,17

19 INT_LVDS_EDIDCLK

11,19 INT_LVDS_EDIDDATA

19 INT_LVDS_DIGON

T31

T71

19 INT_TXLCLKOUT19 INT_TXLCLKOUT+

19 INT_TXUCLKOUT19 INT_TXUCLKOUT+

SM_DRAMRST# only for

DDR3.(DDR2 NC).

19 INT_TXLOUT019 INT_TXLOUT119 INT_TXLOUT2-

DREFCLK 2

DREFCLK# 2

DREFSSCLK 2

DREFSSCLK# 2

T35

19 INT_TXLOUT0+

19 INT_TXLOUT1+

19 INT_TXLOUT2+

CLK_PCIE_3GPLL 2

CLK_PCIE_3GPLL# 2

T33

19 INT_TXUOUT019 INT_TXUOUT119 INT_TXUOUT2-

DMI_TXN[3:0] 13

T52

19 INT_TXUOUT0+

19 INT_TXUOUT1+

19 INT_TXUOUT2+

DMI_TXP[3:0] 13

T54

DMI_RXN[3:0] 13

TV IF (Disable)

DMI_RXP[3:0] 13

DMI_RXP0

DMI_RXP1

DMI_RXP2

DMI_RXP3

CRT I/F

T32

T34

T47

T42

1

C34

18 INT_CRT_DDCCLK

18 INT_CRT_DDCDAT

18 INT_HSYNC

T39

INT_HSYNCR140

INT_VSYNCR148

AH37

AH36

AN36

AJ35

AH34

CL_CLK0

CL_DATA0

MPWROK

CL_RST#0

MCH_CLVREF_R

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLKREQ#

ICH_SYNC#

N28

M28

G36

E36

K36

H36

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

CLK_MCH_OE#

MCH_ICH_SYNC#

TSATN#

B12

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

B28

B30

B29

C29

A28

CL_CLK0 14

CL_DATA0 14

MPWROK 14

CL_RST#0 14

HSYNC/VSYNC serial R place close to NB

+1.05V_VCC_PEG

D

19 INT_LVDS_PWM

19 INT_LVDS_BLON

18 INT_VSYNC

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

INT HDMI

INT_LVDS_PWM

INT_LVDS_BLON

L_CTRL_CLK

L32

G32

M32

L_BKLT_CTRL

L_BKLT_EN

L_CTRL_CLK

L_CTRL_DATA

INT_LVDS_EDIDCLK

INT_LVDS_EDIDDATA

M33

K33

J33

L_CTRL_DATA

L_DDC_CLK

L_DDC_DATA

INT_LVDS_DIGON

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

INT_TXLCLKOUTINT_TXLCLKOUT+

INT_TXUCLKOUTINT_TXUCLKOUT+

M29

C44

B43

E37

E38

C41

C40

B37

A37

L_VDD_EN

LVDS_IBG

LVDS_VBG

LVDS_VREFH

LVDS_VREFL

LVDSA_CLK#

LVDSA_CLK

LVDSB_CLK#

LVDSB_CLK

INT_TXLOUT0INT_TXLOUT1INT_TXLOUT2INT_TXLOUT3-

H47

E46

G40

A40

LVDSA_DATA#_0

LVDSA_DATA#_1

LVDSA_DATA#_2

LVDSA_DATA#_3

INT_TXLOUT0+

INT_TXLOUT1+

INT_TXLOUT2+

INT_TXLOUT3+

H48

D45

F40

B40

LVDSA_DATA_0

LVDSA_DATA_1

LVDSA_DATA_2

LVDSA_DATA_3

INT_TXUOUT0INT_TXUOUT1INT_TXUOUT2INT_TXUOUT3-

A41

H38

G37

J37

LVDSB_DATA#_0

LVDSB_DATA#_1

LVDSB_DATA#_2

LVDSB_DATA#_3

INT_TXUOUT0+

INT_TXUOUT1+

INT_TXUOUT2+

INT_TXUOUT3+

B42

G38

F37

K37

LVDSB_DATA_0

LVDSB_DATA_1

LVDSB_DATA_2

LVDSB_DATA_3

INT_TV_COMP

INT_TV_Y/G

INT_TV_C/R

F25

H25

K25

TVA_DAC

TVB_DAC

TVC_DAC

INT_TV_RNT

H24

TV_RTN

TV_DCONSEL_0

TV_DCONSEL_1

C31

E32

TV_DCONSEL_0

TV_DCONSEL_1

INTB

E28

CRT_BLUE

INTG

G28

CRT_GREEN

INTR

J28

CRT_RED

CRT_IRTN

G29

CRT_IRTN

H32

J32

J29

E29

L29

CRT_DDC_CLK

CRT_DDC_DATA

CRT_HSYNC

CRT_TVO_IREF

CRT_VSYNC

INT_CRT_DDCCLK

INT_CRT_DDCDAT

IV@30.1/F_4HSYNC_G

CRTIREF

IV@30.1/F_4VSYNC_G

PEG_COMPI

PEG_COMPO

T37

T36

EXP_A_COMPX

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

H44

J46

L44

L40

N41

P48

N44

T43

U43

Y43

Y48

Y36

AA43

AD37

AC47

AD39

PEG_RXN0

PEG_RXN1

PEG_RXN2

PEG_RXN3

PEG_RXN4

PEG_RXN5

PEG_RXN6

PEG_RXN7

PEG_RXN8

PEG_RXN9

PEG_RXN10

PEG_RXN11

PEG_RXN12

PEG_RXN13

PEG_RXN14

PEG_RXN15

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

H43

J44

L43

L41

N40

P47

N43

T42

U42

Y42

W47

Y37

AA42

AD36

AC48

AD40

PEG_RXP0

PEG_RXP1

PEG_RXP2

PEG_RXP3

PEG_RXP4

PEG_RXP5

PEG_RXP6

PEG_RXP7

PEG_RXP8

PEG_RXP9

PEG_RXP10

PEG_RXP11

PEG_RXP12

PEG_RXP13

PEG_RXP14

PEG_RXP15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

J41

M46

M47

M40

M42

R48

N38

T40

U37

U40

Y40

AA46

AA37

AA40

AD43

AC46

C_PEG_TXN0

C_PEG_TXN1

C_PEG_TXN2

C_PEG_TXN3

C_PEG_TXN4

C_PEG_TXN5

C_PEG_TXN6

C_PEG_TXN7

C_PEG_TXN8

C_PEG_TXN9

C_PEG_TXN10

C_PEG_TXN11

C_PEG_TXN12

C_PEG_TXN13

C_PEG_TXN14

C_PEG_TXN15

C497

C121

C495

C137

C490

C148

C487

C158

C484

C164

C481

C170

C476

C174

C468

C179

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

PEG_TXN0

PEG_TXN1

PEG_TXN2

PEG_TXN3

PEG_TXN4

PEG_TXN5

PEG_TXN6

PEG_TXN7

PEG_TXN8

PEG_TXN9

PEG_TXN10

PEG_TXN11

PEG_TXN12

PEG_TXN13

PEG_TXN14

PEG_TXN15

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

J42

L46

M48

M39

M43

R47

N37

T39

U36

U39

Y39

Y46

AA36

AA39

AD42

AD46

C_PEG_TXP0

C_PEG_TXP1

C_PEG_TXP2

C_PEG_TXP3

C_PEG_TXP4

C_PEG_TXP5

C_PEG_TXP6

C_PEG_TXP7

C_PEG_TXP8

C_PEG_TXP9

C_PEG_TXP10

C_PEG_TXP11

C_PEG_TXP12

C_PEG_TXP13

C_PEG_TXP14

C_PEG_TXP15

C498

C120

C493

C132

C491

C145

C489

C153

C485

C161

C483

C168

C480

C173

C469

C177

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

EV@0.1u/10V_4

PEG_TXP0

PEG_TXP1

PEG_TXP2

PEG_TXP3

PEG_TXP4

PEG_TXP5

PEG_TXP6

PEG_TXP7

PEG_TXP8

PEG_TXP9

PEG_TXP10

PEG_TXP11

PEG_TXP12

PEG_TXP13

PEG_TXP14

PEG_TXP15

VGA

PM_EXTTS#0

PM_EXTTS#1

PM

14 PM_SYNC#

3,12,31 ICH_DPRSTP#

17 PM_EXTTS#0

17 PM_EXTTS#1

3,14,31 DELAY_VR_PWRGOOD

13 PLT_RST#_NB

3,12 PM_THRMTRIP#

14,31 PM_DPRSLPVR

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

ME

T41

T56

11 MCH_CFG_19

11 MCH_CFG_20

T25

R25

P25

P20

P24

C25

N24

M24

E21

C23

C24

N21

P21

T21

R20

M20

L21

H21

P29

R28

T28

ME_JTAG_TMS

MISC

T59

T43

11 MCH_CFG_16

AM35

EXT VGA

IHM@

TV

T46

11 MCH_CFG_12

11 MCH_CFG_13

ME_JTAG_TDO

CFG

T40

11 MCH_CFG_9

11 MCH_CFG_10

AN35

PEG_CLK

PEG_CLK#

HDA

T48

T55

11 MCH_CFG_5

11 MCH_CFG_6

11 MCH_CFG_7

ME_JTAG_TDI

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

MCH_CFG_3

MCH_CFG_4

MCH_CFG_5

MCH_CFG_6

MCH_CFG_7

MCH_CFG_8

MCH_CFG_9

MCH_CFG_10

MCH_CFG_11

MCH_CFG_12

MCH_CFG_13

MCH_CFG_14

MCH_CFG_15

MCH_CFG_16

MCH_CFG_17

MCH_CFG_18

MCH_CFG_19

MCH_CFG_20

2 MCH_BSEL0

2 MCH_BSEL1

2 MCH_BSEL2

C

ME_JTAG_TCK

GRAPHICS VID

JTAG_TMS

T67

AL34

AK34

ME JTAG

JTAG_TDI

T65

INT VGA

EV@

LVDS

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

M_CLK_DDR0 17

M_CLK_DDR1 17

M_CLK_DDR3 17

M_CLK_DDR4 17

GRAPHICS

T24

MCH_RSVD15

RSVD

T37

MCH_RSVD14

SA_CK_0

SA_CK_1

SB_CK_0

SB_CK_1

AP24

AT21

AV24

AU20

06

Description

IV@

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

PCI-EXPRESS

T57

D

M36

N36

R33

T33

AH9

AH10

AH12

AH13

K12

DDR CLK/ CONTROL/COMPENSATION

MCH_RSVD1

MCH_RSVD2

MCH_RSVD3

MCH_RSVD4

MCH_RSVD5

MCH_RSVD6

MCH_RSVD7

MCH_RSVD8

MCH_RSVD9

T50

T53

T30

T58

T64

T62

T60

T61

T49

For IV @ Connect to 30.1ohm

For EV@ NC

R153

49.9/F_4

PEG_RXN[15:0] 20

PEG_RXP[15:0] 20

PEG_TXN[15:0] 20

PEG_TXP[15:0] 20

CANTIGA_1p2

DDPC_CTRL for HDMI port C

SDVO_CTRL for HDMI port B

T29

DDPC_CTRLDATA 11

T45

SDVO_CTRLDATA 11

CLK_MCH_OE# 2

MCH_ICH_SYNC# 14

Close U3030

NOTE:

If (G)MCH's HD Audio signals are connected to ICH9M for

iHDMI, VCCHDA and VCCSUSHDA on ICH9M should be

only on 1.5V. These power pins on ICH9M can be supplied

with 3.3V if and only if (G)MCH's HDA is not connected to

ICH9M. Consequently, only 1.5V audio/modem codecs can

be used on the platform.

T162

T163

T164

T165

T166

INTR

L48

0@IV

INT_CRT_RED 18

INTG

L49

0@IV

INT_CRT_GRN 18

INTB

L47

0@IV

INT_CRT_BLU 18

C549 C550 C551

C552 C548 C547

*5.6P *5.6P *5.6P

*5.6P *5.6P *5.6P

CANTIGA_1p2

Check list note : CL_REF=0.35V

SM_VREF.Default use voltage divider for poor layout cause +SMDDR_VREF not

meet spec.And Intel circuit PU/PD is 1K,But Check list PU/PD is 10K.

VCCP

<Checklist ver0.8>

If TSATN# is not used, then it must be terminated

with a 56- pull-up resistor to VCCP.

VCCP

TSATN#

R166

R202

0_6

SMDDR_VREF

R189

*10K/F_4

+1.8VSUS_GMCH

56_4

R529

CLK_MCH_OE# 10K_4

R102

VCC3

1K/F_4

MCH_CLVREF_R

SM_VREF

C136

PM_EXTTS#0

10K_4

R152

PM_EXTTS#1

10K_4

R149

R170

0.1u/10V_4

IV&EV Dis/Enable LVDS setting(See DG 1.0 P190 Table 103)

R195

*10K/F_4

511/F_6

VCC3

R122

IV@0_4

LVDS_VREFH

LVDS_VREFL

For IV @ 0ohm

For EV@ NC

R120

For IV @ 2.37K/F

For EV@ NC

IV@2.37K/F_4

LVDS_IBG

R79

IV@10K_4

L_CTRL_CLK

R80

IV@10K_4

L_CTRL_DATA

For IV @ 2.37K 10K

For EV@ NC

IV&EV Dis/Enable CRT setting(See DG 1.0 P190 Table 103)

SM_REXT

R199

R130

R136

*EV@0_4

*EV@0_4

INT_CRT_DDCCLK

INT_CRT_DDCDAT

For IV @ NC

For EV@ 0ohm to GND or NC

R137

R145

*EV@0_4

*EV@0_4

HSYNC_G

VSYNC_G

For IV @ NC

For EV@ 0ohm to GND or NC

SM_PWROK only for DDR3.(DDR2 PD only)

+1.8VSUS_GMCH

+1.8VSUS_GMCH

+1.8VSUS_GMCH

R495

SM_RCOMP_VOH

1K/F_4

C465

C464

0.01u/16V_4

2.2u/6.3V_6

HWPG_1.8V 28,33

R500

R492

R491

R185

*12K/F_4

3.01K/F_4

80.6/F_4

*20/F_4

SM_PWROK

M_RCOMP

M_RCOMP#

Dis TV/En CRT( See DG1.0 P208 Table 118)

499/F_4

R129

R131

R135

EV_IV@150/F_4

EV_IV@150/F_4

EV_IV@150/F_4

INTB

INTG

INTR

R496

*20/F_4

80.6/F_4

http://mycomp.su/x/

5

R488

1K/F_4

C461

0.01u/16V_4

R124

R121

EV_IV@75_4 INT_TV_COMP

EV_IV@75_4 INT_TV_Y/G

EV_IV@75_4 INT_TV_C/R

0_4

0_4

TV_DCONSEL_0

TV_DCONSEL_1

For IV @ 75ohm to GND

For EV@ 0ohm to GND

For IV @ 0ohm to GND

For EV@ 0ohm to GND

For IV @ Connect to 150ohm/F

For EV@ Connect to 0ohm GND

SM_RCOMP_VOL

R497

R125

R132

R139

IV&EV Dis/Enable PLL setting(See DG 1.0 P190 Table 103)

R184

10K/F_6

C458

R119

2.2u/6.3V_6

EV_IV@1K/F_4

CRTIREF

For IV @ Connect to 1.02K/F

For EV@ Connect to 0ohm GND

DREFCLK

DREFCLK#

DREFSSCLK

DREFSSCLK#

R535

R523

R126

R133

EV@0_4

EV@0_4

EV@0_4

EV@0_4

For IV @ NC

For EV@ 0ohm to GND

PROJECT : PB5/6

Quanta Computer Inc.

Size

Document Number

Date:

Wednesday, June 04, 2008

Layout Note :See DG1.0 P180

Rev

1A

NB(2/7)

2

Sheet

of

35

07

BOM Option Table

Reference

Description

N/A

N/A

17 M_A_DQ[32..39]

17 M_A_DQ[40..47]

17 M_A_DQ[48..55]

B

17 M_A_DQ[56..63]

SA_RAS#

SA_CAS#

SA_WE#

BB20

BD20

AY20

M_A_RAS#

M_A_CAS#

M_A_WE#

17 M_B_DQ[0..7]

M_A_BS#0 16,17

M_A_BS#1 16,17

M_A_BS#2 16,17

M_A_RAS# 16,17

M_A_CAS# 16,17

M_A_WE# 16,17

SA_DM_0

SA_DM_1

SA_DM_2

SA_DM_3

SA_DM_4

SA_DM_5

SA_DM_6

SA_DM_7

AM37

AT41

AY41

AU39

BB12

AY6

AT7

AJ5

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

SA_DQS_0

SA_DQS_1

SA_DQS_2

SA_DQS_3

SA_DQS_4

SA_DQS_5

SA_DQS_6

SA_DQS_7

SA_DQS#_0

SA_DQS#_1

SA_DQS#_2

SA_DQS#_3

SA_DQS#_4

SA_DQS#_5

SA_DQS#_6

SA_DQS#_7

AJ44

AT44

BA43

BC37

AW12

BC8

AU8

AM7

AJ43

AT43

BA44

BD37

AY12

BD8

AU9

AM8

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

BA21

BC24

BG24

BH24

BG25

BA24

BD24

BG27

BF25

AW24

BC21

BG26

BH26

BH17

AY25

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_DM[0..7] 17

17 M_B_DQ[16..23]

M_A_DQS[0..7] 17

17 M_B_DQ[24..31]

M_A_DQS#[0..7] 17

17 M_B_DQ[32..39]

M_A_A[0..14] 16,17

17 M_B_DQ[40..47]

17 M_B_DQ[48..55]

17 M_B_DQ[56..63]

CANTIGA_1p2

U26E

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

AK47

AH46

AP47

AP46

AJ46

AJ48

AM48

AP48

AU47

AU46

BA48

AY48

AT47

AR47

BA47

BC47

BC46

BC44

BG43

BF43

BE45

BC41

BF40

BF41

BG38

BF38

BH35

BG35

BH40

BG39

BG34

BH34

BH14

BG12

BH11

BG8

BH12

BF11

BF8

BG7

BC5

BC6

AY3

AY1

BF6

BF5

BA1

BD3

AV2

AU3

AR3

AN2

AY2

AV1

AP3

AR1

AL1

AL2

AJ1

AH1

AM2

AM3

AH3

AJ3

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

M_A_BS#0

M_A_BS#1

M_A_BS#2

MEMORY

17 M_A_DQ[24..31]

BD21

BG18

AT25

SYSTEM

SA_BS_0

SA_BS_1

SA_BS_2

17 M_B_DQ[8..15]

MEMORY

17 M_A_DQ[16..23]

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SYSTEM

17 M_A_DQ[8..15]

AJ38

AJ41

AN38

AM38

AJ36

AJ40

AM44

AM42

AN43

AN44

AU40

AT38

AN41

AN39

AU44

AU42

AV39

AY44

BA40

BD43

AV41

AY43

BB41

BC40

AY37

BD38

AV37

AT36

AY38

BB38

AV36

AW36

BD13

AU11

BC11

BA12

AU13

AV13

BD12

BC12

BB9

BA9

AU10

AV9

BA11

BD9

AY8

BA6

AV5

AV7

AT9

AN8

AU5

AU6

AT5

AN10

AM11

AM5

AJ9

AJ8

AN12

AM13

AJ11

AJ12

DDR

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR

U26D

17 M_A_DQ[0..7]

SB_BS_0

SB_BS_1

SB_BS_2

BC16

BB17

BB33

M_B_BS#0

M_B_BS#1

M_B_BS#2

SB_RAS#

SB_CAS#

SB_WE#

AU17

BG16

BF14

M_B_RAS#

M_B_CAS#

M_B_WE#

SB_DM_0

SB_DM_1

SB_DM_2

SB_DM_3

SB_DM_4

SB_DM_5

SB_DM_6

SB_DM_7

AM47

AY47

BD40

BF35

BG11

BA3

AP1

AK2

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

SB_DQS_0

SB_DQS_1

SB_DQS_2

SB_DQS_3

SB_DQS_4

SB_DQS_5

SB_DQS_6

SB_DQS_7

SB_DQS#_0

SB_DQS#_1

SB_DQS#_2

SB_DQS#_3

SB_DQS#_4

SB_DQS#_5

SB_DQS#_6

SB_DQS#_7

AL47

AV48

BG41

BG37

BH9

BB2

AU1

AN6

AL46

AV47

BH41

BH37

BG9

BC2

AT2

AN5

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

AV17

BA25

BC25

AU25

AW25

BB28

AU28

AW28

AT33

BD33

BB16

AW33

AY33

BH15

AU33

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_BS#0 16,17

M_B_BS#1 16,17

M_B_BS#2 16,17

M_B_RAS# 16,17

M_B_CAS# 16,17

M_B_WE# 16,17

M_B_DM[0..7] 17

M_B_DQS[0..7] 17

M_B_DQS#[0..7] 17

M_B_A[0..14] 16,17

CANTIGA_1p2

PROJECT : PB5/6

Quanta Computer Inc.

Size

Document Number

Date:

Friday, May 30, 2008

Rev

1A

DDRII

5

http://mycomp.su/x/

Sheet

1

of

35

BOM Option Table

+1.8VSUS_GMCH

+1.8VSUS_GMCH

AM32

AL32

AK32

AJ32

AH32

AG32

AE32

AC32

AA32

Y32

W32

U32

AM30

AL30

AK30

AH30

AG30

AF30

AE30

AC30

AB30

AA30

Y30

W30

V30

U30

AL29

AK29

AJ29

AH29

AG29

AE29

AC29

AA29

Y29

W29

V29

AL28

AK28

AL26

AK26

AK25

AK24

AK23

BA36

BB24

BD16

BB21

AW16

AW13

AT13

VCC_SM_36/NC

VCC_SM_37/NC

VCC_SM_38/NC

VCC_SM_39/NC

VCC_SM_40/NC

VCC_SM_41/NC

VCC_SM_42/NC

+VGFX_CORE_INT

CANTIGA_1p2

Y26

AE25

AB25

AA25

AE24

AC24

AA24

Y24

AE23

AC23

AB23

AA23

AJ21

AG21

AE21

AC21

AA21

Y21

AH20

AF20

AE20

AC20

AB20

AA20

T17

T16

AM15

AL15

AE15

AJ15

AH15

AG15

AF15

AB15

AA15

Y15

V15

U15

AN14

AM14

U14

T14

VCC_AXG_1

VCC_AXG_2

VCC_AXG_3

VCC_AXG_4

VCC_AXG_5

VCC_AXG_6

VCC_AXG_7

VCC_AXG_8

VCC_AXG_9

VCC_AXG_10

VCC_AXG_11

VCC_AXG_12

VCC_AXG_13

VCC_AXG_14

VCC_AXG_15

VCC_AXG_16

VCC_AXG_17

VCC_AXG_18

VCC_AXG_19

VCC_AXG_20

VCC_AXG_21

VCC_AXG_22

VCC_AXG_23

VCC_AXG_24

VCC_AXG_25

VCC_AXG_26

VCC_AXG_27

VCC_AXG_28

VCC_AXG_29

VCC_AXG_30

VCC_AXG_31

VCC_AXG_32

VCC_AXG_33

VCC_AXG_34

VCC_AXG_35

VCC_AXG_36

VCC_AXG_37

VCC_AXG_38

VCC_AXG_39

VCC_AXG_40

VCC_AXG_41

VCC_AXG_42

AJ14

AH14

VCC_AXG_SENSE

VSS_AXG_SENSE

+VGFX_CORE_INT

R174

R173

IV@10/F_6

IV@10/F_6

VCC_AXG_NCTF_1

VCC_AXG_NCTF_2

VCC_AXG_NCTF_3

VCC_AXG_NCTF_4

VCC_AXG_NCTF_5

VCC_AXG_NCTF_6

VCC_AXG_NCTF_7

VCC_AXG_NCTF_8

VCC_AXG_NCTF_9

VCC_AXG_NCTF_10

VCC_AXG_NCTF_11

VCC_AXG_NCTF_12

VCC_AXG_NCTF_13

VCC_AXG_NCTF_14

VCC_AXG_NCTF_15

VCC_AXG_NCTF_16

VCC_AXG_NCTF_17

VCC_AXG_NCTF_18

VCC_AXG_NCTF_19

VCC_AXG_NCTF_20

VCC_AXG_NCTF_21

VCC_AXG_NCTF_22

VCC_AXG_NCTF_23

VCC_AXG_NCTF_24

VCC_AXG_NCTF_25

VCC_AXG_NCTF_26

VCC_AXG_NCTF_27

VCC_AXG_NCTF_28

VCC_AXG_NCTF_29

VCC_AXG_NCTF_30

VCC_AXG_NCTF_31

VCC_AXG_NCTF_32

VCC_AXG_NCTF_33

VCC_AXG_NCTF_34

VCC_AXG_NCTF_35

VCC_AXG_NCTF_36

VCC_AXG_NCTF_37

VCC_AXG_NCTF_38

VCC_AXG_NCTF_39

VCC_AXG_NCTF_40

VCC_AXG_NCTF_41

VCC_AXG_NCTF_42

VCC_AXG_NCTF_43

VCC_AXG_NCTF_44

VCC_AXG_NCTF_45

VCC_AXG_NCTF_46

VCC_AXG_NCTF_47

VCC_AXG_NCTF_48

VCC_AXG_NCTF_49

VCC_AXG_NCTF_50

VCC_AXG_NCTF_51

VCC_AXG_NCTF_52

VCC_AXG_NCTF_53

VCC_AXG_NCTF_54

VCC_AXG_NCTF_55

VCC_AXG_NCTF_56

VCC_AXG_NCTF_57

VCC_AXG_NCTF_58

VCC_AXG_NCTF_59

VCC_AXG_NCTF_60

EXT VGA

08

1.8VSUS

0_1206

W28

V28

W26

V26

W25

V25

W24

V24

W23

V23

AM21

AL21

AK21

W21

V21

U21

AM20

AK20

W20

U20

AM19

AL19

AK19

AJ19

AH19

AG19

AF19

AE19

AB19

AA19

Y19

W19

V19

U19

AM17

AK17

AH17

AG17

AF17

AE17

AC17

AB17

Y17

W17

V17

AM16

AL16

AK16

AJ16

AH16

AG16

AF16

AE16

AC16

AB16

AA16

Y16

W16

V16

U16

C463

C462

C163

10u/6.3V_8

10u/6.3V_8

0.1u/10V_4

C156

330u/2.5V_7343

C122

C135

C131

C127

0.1u/10V_4

0.22u/6.3V_4

0.22u/6.3V_4

22u/6.3V_8

Close to GMCH

VCCP

C91

VCCP

270u/2V_7343

Close to GMCH

+VGFX_CORE_INT

See Page 9 EV&IV table

C128

IV@0.47u/6.3V_4

C112

C124

C143

C111

C133

IV@1u/16V_6

IV@10u/10V_8

IV@10u/6.3V_8

IV@0.1u/10V_4

IV@0.1u/10V_4

R172

IV@0_0402

R154

IV@0_0402

R164

IV@0_0402

R169

IV@0_0402

R155

IV@0_1206

R519

IV@0_1206

R163

R167

R165

EV@0_6

EV@0_6

EV@0_6

DR8

DR9

Place close to the GMCH

and different location

+VGFX_CORE_INT

+ C92

+ C85

IV@330u/2.5V_7343

IV@330u/2.5V_7343

Close to GMCH

NB Power Status and max current table(1/3)

POWER PLANE

S0

S3

Voltage

I(max)

VCC(EXT_VGA)

S4/S5

X

+1.05V

2178mA

Note

VCC(INT_VGA)

+1.05V

2899mA

VCC_AXG

+1.05V

8700mA

VCC_SM(800)

+1.8VSUS

3A

(DDRII-667) 2.6A

VCC_SM(Standby)

+1.8VSUS

1mA

Self Refresh during S3

Graphics Core

B

(See NB EDS Rev:1.0 Section 10.1 for max current)

(See NB EDS Rev:1.0 Section 12.2 for DC voltage)

Close to each pins

1.8V Internal connect to power

VCC SM LF

VCC NCTF

R156

0_4

VCC_NCTF_1

VCC_NCTF_2

VCC_NCTF_3

VCC_NCTF_4

VCC_NCTF_5

VCC_NCTF_6

VCC_NCTF_7

VCC_NCTF_8

VCC_NCTF_9

VCC_NCTF_10

VCC_NCTF_11

VCC_NCTF_12

VCC_NCTF_13

VCC_NCTF_14

VCC_NCTF_15

VCC_NCTF_16

VCC_NCTF_17

VCC_NCTF_18

VCC_NCTF_19

VCC_NCTF_20

VCC_NCTF_21

VCC_NCTF_22

VCC_NCTF_23

VCC_NCTF_24

VCC_NCTF_25

VCC_NCTF_26

VCC_NCTF_27

VCC_NCTF_28

VCC_NCTF_29

VCC_NCTF_30

VCC_NCTF_31

VCC_NCTF_32

VCC_NCTF_33

VCC_NCTF_34

VCC_NCTF_35

VCC_NCTF_36

VCC_NCTF_37

VCC_NCTF_38

VCC_NCTF_39

VCC_NCTF_40

VCC_NCTF_41

VCC_NCTF_42

VCC_NCTF_43

VCC_NCTF_44

POWER

VCC_35

VCC GFX NCTF

T32

VCCP

VCC_SM_1

VCC_SM_2

VCC_SM_3

VCC_SM_4

VCC_SM_5

VCC_SM_6

VCC_SM_7

VCC_SM_8

VCC_SM_9

VCC_SM_10

VCC_SM_11