Professional Documents

Culture Documents

Clo Format1 LD

Clo Format1 LD

Uploaded by

Sunil BegumpurCopyright:

Available Formats

You might also like

- Computer Applications CoursehandoutDocument2 pagesComputer Applications CoursehandoutMrinal GourNo ratings yet

- Network Simulation Lab ManualDocument85 pagesNetwork Simulation Lab Manualdipshi92No ratings yet

- Btech Mae All Syllabus For Amity University RajasthanDocument173 pagesBtech Mae All Syllabus For Amity University RajasthanVishnu Gupta0% (1)

- ME Computer Engineering Syllabus - 5!8!13Document37 pagesME Computer Engineering Syllabus - 5!8!13virusisb4uNo ratings yet

- Nivetha M.: Masters in Electronics & Communication EngineeringDocument3 pagesNivetha M.: Masters in Electronics & Communication EngineeringArulNo ratings yet

- CourseoutlineDocument4 pagesCourseoutlineapi-249059012No ratings yet

- BE Electronic & Comunication 2016 RCOEM SyllabusDocument63 pagesBE Electronic & Comunication 2016 RCOEM SyllabusKaranNo ratings yet

- Muffakham Jah College of Engineering and Technology Course Handout - Academic Year 2014-15Document3 pagesMuffakham Jah College of Engineering and Technology Course Handout - Academic Year 2014-15Sobhan DasariNo ratings yet

- Course Outcome With PO COADocument2 pagesCourse Outcome With PO COAbalasha_937617969No ratings yet

- Dhanapathi.J: ObjectiveDocument3 pagesDhanapathi.J: ObjectiveGanesh KumarNo ratings yet

- ABET PTU Syllabus Digital Control (JAFAR JALLAD)Document3 pagesABET PTU Syllabus Digital Control (JAFAR JALLAD)Green HeartNo ratings yet

- Laboratory. MATLAB Has Evolved Over A Period ofDocument2 pagesLaboratory. MATLAB Has Evolved Over A Period ofMrityunjayChauhanNo ratings yet

- Vinu ResumeDocument2 pagesVinu Resumeமனிதம்No ratings yet

- Synopsis Point M.tech III SemDocument7 pagesSynopsis Point M.tech III Sempiyushji125No ratings yet

- Tsu Obtl Plan - Ece333Document9 pagesTsu Obtl Plan - Ece333ferdie marcosNo ratings yet

- Course Outline MCDocument5 pagesCourse Outline MCWajeeha_Khan1No ratings yet

- CEG 3320-01 - Digital System DesignDocument3 pagesCEG 3320-01 - Digital System DesignTetteh SamuelNo ratings yet

- Syllabus - CEN 3024 Software Development IDocument5 pagesSyllabus - CEN 3024 Software Development Ijkough840No ratings yet

- De Course File 2013-14Document75 pagesDe Course File 2013-14ragvshahNo ratings yet

- Developing Power Cycles Simulations For An Applied Thermodynamics CourseDocument12 pagesDeveloping Power Cycles Simulations For An Applied Thermodynamics Coursebakisahin2No ratings yet

- LabDocument11 pagesLabravi855885No ratings yet

- Syllabus M.tech Extc-1Document59 pagesSyllabus M.tech Extc-1swapnilNo ratings yet

- ME 310 Fall 2023 Course PolicyDocument2 pagesME 310 Fall 2023 Course PolicyNecati Eray UçarNo ratings yet

- Ue Obe-Syllabus Ncp515Document13 pagesUe Obe-Syllabus Ncp515Alexis John RubioNo ratings yet

- MPMC Lab ManualDocument127 pagesMPMC Lab ManualMeghashyam Sarma0% (1)

- Neural Networks BrochureDocument2 pagesNeural Networks BrochureAnonymous xaeuoo4No ratings yet

- tdj3m Todd Crossley April 2014Document11 pagestdj3m Todd Crossley April 2014api-201489392No ratings yet

- Resource Practicefeedback Learining Content Presentation: Bago City CollegeDocument2 pagesResource Practicefeedback Learining Content Presentation: Bago City Collegeᒛᓏᕨᖻ ᗫᕧ ᒷᕠ ᑖᖆᘴᙑNo ratings yet

- SS 0slab 15csl67Document63 pagesSS 0slab 15csl67TalibNo ratings yet

- ECE - 3rd To 8th SemDocument147 pagesECE - 3rd To 8th SemSonaal GuptaNo ratings yet

- CN Lab Manual HighlitedDocument72 pagesCN Lab Manual Highliteddarshangondkar15No ratings yet

- FEM Course HandoutDocument3 pagesFEM Course HandoutSyed Sirajul HaqNo ratings yet

- Wa0013 PDFDocument70 pagesWa0013 PDFRahulPatilNo ratings yet

- Department of Information Technology Faculty of CS&IT: Course TitleDocument5 pagesDepartment of Information Technology Faculty of CS&IT: Course TitleNabeel SalmanNo ratings yet

- Outline Syllabi Field of Electronic Telecommunication EngineeringDocument64 pagesOutline Syllabi Field of Electronic Telecommunication EngineeringsukirajNo ratings yet

- ELEC5402 Digital Integrated Circuit Design 2010Document4 pagesELEC5402 Digital Integrated Circuit Design 2010tssandeepkumarchoudhary@scribd0% (1)

- Beginners Guide To Digital ElectronicsDocument3 pagesBeginners Guide To Digital ElectronicsSuperusNovusNo ratings yet

- BE Syllabus Chandigarh UniversityDocument114 pagesBE Syllabus Chandigarh Universitykashishbhatia50% (2)

- ECE NITRR SyllabusDocument78 pagesECE NITRR SyllabusDeepak Kumar RaiNo ratings yet

- Eee Peo-PoDocument1 pageEee Peo-PoAyyar KandasamyNo ratings yet

- Session 13c6Document5 pagesSession 13c6viratNo ratings yet

- Subject For Software Engineering Course MalaysiaDocument10 pagesSubject For Software Engineering Course Malaysiaafiqzaqwan001No ratings yet

- TeachingPlan BTKR1313 SEM1 20122013Document10 pagesTeachingPlan BTKR1313 SEM1 20122013Sabikan SulaimanNo ratings yet

- Final Hand Book 2-2 2013-14Document66 pagesFinal Hand Book 2-2 2013-14sunilkumareceNo ratings yet

- CSE Syllabus Draft 28aug19Document132 pagesCSE Syllabus Draft 28aug19240 Sadman ShafiNo ratings yet

- Rajat Sood: Male, 23 YearsDocument3 pagesRajat Sood: Male, 23 Yearspramesh1010No ratings yet

- Course Outcome (Co) : Name of Course/Subject: Digital Communication (Theory)Document3 pagesCourse Outcome (Co) : Name of Course/Subject: Digital Communication (Theory)Praveen Khatkale PatilNo ratings yet

- 4 - E&TC SY Syllabus W.E.F. 23-24 Autonomous WIT - FY - 22-23Document42 pages4 - E&TC SY Syllabus W.E.F. 23-24 Autonomous WIT - FY - 22-23SarinNo ratings yet

- MS in Electronics and Telecommunications Engineering (MS-ETE)Document3 pagesMS in Electronics and Telecommunications Engineering (MS-ETE)Sharif SarwarNo ratings yet

- GGS College of Modern Technology, Kharar: Department of Electrical EngineeringDocument6 pagesGGS College of Modern Technology, Kharar: Department of Electrical EngineeringHarsh BatthNo ratings yet

- Resume: Ability To Work Alone and in Team Dedication and Perfectness On Work Zeal To Learn New ThingsDocument3 pagesResume: Ability To Work Alone and in Team Dedication and Perfectness On Work Zeal To Learn New ThingsNasir AhmedNo ratings yet

- Course File CPDocument70 pagesCourse File CPkaps_er_3No ratings yet

- Model of Department Information - EceDocument5 pagesModel of Department Information - EcegdeepthiNo ratings yet

- Emt & TL Course FileDocument42 pagesEmt & TL Course FileSuraj KumarNo ratings yet

- Lowres Engcoursecg 0214 PDFDocument24 pagesLowres Engcoursecg 0214 PDFIrakshayNo ratings yet

- MEC 4627 Vehicle Electronic and Instrumental SystemDocument5 pagesMEC 4627 Vehicle Electronic and Instrumental SystemFarith AhmadNo ratings yet

- NITRR SyllabusDocument77 pagesNITRR SyllabusDeepak Kumar RaiNo ratings yet

- Mechatronics Curriculum White PaperDocument4 pagesMechatronics Curriculum White PaperSolGriffinNo ratings yet

- Teaching and Learning in STEM With Computation, Modeling, and Simulation Practices: A Guide for Practitioners and ResearchersFrom EverandTeaching and Learning in STEM With Computation, Modeling, and Simulation Practices: A Guide for Practitioners and ResearchersNo ratings yet

Clo Format1 LD

Clo Format1 LD

Uploaded by

Sunil BegumpurOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Clo Format1 LD

Clo Format1 LD

Uploaded by

Sunil BegumpurCopyright:

Available Formats

Smt. Kamala and Sri Venkappa. M. Agadi College of Engineering and Technology., Laxmesh ar!

"#$%%& 'Appro(ed )y A*CTE +elhi and Affiliated to VT, -elga.m/ +epartment of Electronics and Comm.nication Comm.nication

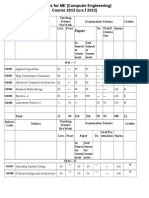

Course Plan Semester : III Year: 2013

Program: Electronics and Communication Engineering Course Title: Logic Design Total Content Hours: 52 E"am $ar%s: 100 Lesson Plan &ut#or: Santos# 'u(ari C#ec%ed ',: Course Code: 10ES33 Duration o !inal E"am: 3 #rs Internal $ar%s: 25 Date: 0)*0+*2013 Date:

Course Learning Objectives-CLO &t t#e end o t#e course student s#ould -e a-le to: 1. State /#at is Logic Design and /#, it is re0uired and to descri-e com-inational logic1 to generate s/itc#ing e0uations rom trut# ta-les1 to sim2li , ma"term and minterm e0uations using 3*ma2s. 2. Practice t#e 4uine*$cClus%, minimi5ation tec#ni0ue1 reduced 2rime im2licant ta-les1 $a2 entered 6aria-les. 3. &nal,5e and design decoders and encoders. 7. &nal,5e and design digital multi2le"ers1 adders1 su-tractors. 5. &nal,5e and design t#e -asic -ista-le element1 latc#es and li2* lo2s. ). Practice c#aracteristic e0uations and design registers and counters. 8. 9ecall $ela, and $oore $odels and design s,nc#ronous se0uential +. Construct State diagrams and design counters.

SKSVMACET!L01

+E2T 34 ECE

Smt. Kamala and Sri Venkappa. M. Agadi College of Engineering and Technology., Laxmesh ar!"#$%%& 'Appro(ed )y A*CTE +elhi and Affiliated to VT, -elga.m/ +epartment of Electronics and Comm.nication Comm.nication

Course Learning Outcomes-CLO &t t#e end o t#e course student s#ould -e a-le to: 1. Students /ill demonstrate %no/ledge o Logic Design and s#o/ /#at com-inational logic is and sim2li , t#e e0uations using 3*ma2s. 2. Students /ill demonstrate s%ills to use 4uine*$cClus%, minimi5ation tec#ni0ue1 9educed 2rime im2licant ta-les and ma2 entered 6aria-les. 3. Students /ill demonstrate s%ills to design decoders1 encoders1 digital multi2le"ers1 adders1 su-tractors. 7. Students /ill demonstrate to use Latc#es1 li2* lo2s. 5. Students /ill demonstrate a-ilit, to design registers and counters. ). Students /ill s#o/ /#, $eal, and $oore $odels and /ill demonstrate t#e s%ills to design S,nc#ronous Se0uential Circuit. 8. Students /ill demonstrate an a-ilit, to construct state diagrams. +. Students /ill demonstrate an a-ilit, to anal,5e s,nt#esis in ormation rom entit, and module and to ma2 2rocess and al/a,s in t#e #ard/are domain.

SKSVMACET!L01

+E2T 34 ECE

You might also like

- Computer Applications CoursehandoutDocument2 pagesComputer Applications CoursehandoutMrinal GourNo ratings yet

- Network Simulation Lab ManualDocument85 pagesNetwork Simulation Lab Manualdipshi92No ratings yet

- Btech Mae All Syllabus For Amity University RajasthanDocument173 pagesBtech Mae All Syllabus For Amity University RajasthanVishnu Gupta0% (1)

- ME Computer Engineering Syllabus - 5!8!13Document37 pagesME Computer Engineering Syllabus - 5!8!13virusisb4uNo ratings yet

- Nivetha M.: Masters in Electronics & Communication EngineeringDocument3 pagesNivetha M.: Masters in Electronics & Communication EngineeringArulNo ratings yet

- CourseoutlineDocument4 pagesCourseoutlineapi-249059012No ratings yet

- BE Electronic & Comunication 2016 RCOEM SyllabusDocument63 pagesBE Electronic & Comunication 2016 RCOEM SyllabusKaranNo ratings yet

- Muffakham Jah College of Engineering and Technology Course Handout - Academic Year 2014-15Document3 pagesMuffakham Jah College of Engineering and Technology Course Handout - Academic Year 2014-15Sobhan DasariNo ratings yet

- Course Outcome With PO COADocument2 pagesCourse Outcome With PO COAbalasha_937617969No ratings yet

- Dhanapathi.J: ObjectiveDocument3 pagesDhanapathi.J: ObjectiveGanesh KumarNo ratings yet

- ABET PTU Syllabus Digital Control (JAFAR JALLAD)Document3 pagesABET PTU Syllabus Digital Control (JAFAR JALLAD)Green HeartNo ratings yet

- Laboratory. MATLAB Has Evolved Over A Period ofDocument2 pagesLaboratory. MATLAB Has Evolved Over A Period ofMrityunjayChauhanNo ratings yet

- Vinu ResumeDocument2 pagesVinu Resumeமனிதம்No ratings yet

- Synopsis Point M.tech III SemDocument7 pagesSynopsis Point M.tech III Sempiyushji125No ratings yet

- Tsu Obtl Plan - Ece333Document9 pagesTsu Obtl Plan - Ece333ferdie marcosNo ratings yet

- Course Outline MCDocument5 pagesCourse Outline MCWajeeha_Khan1No ratings yet

- CEG 3320-01 - Digital System DesignDocument3 pagesCEG 3320-01 - Digital System DesignTetteh SamuelNo ratings yet

- Syllabus - CEN 3024 Software Development IDocument5 pagesSyllabus - CEN 3024 Software Development Ijkough840No ratings yet

- De Course File 2013-14Document75 pagesDe Course File 2013-14ragvshahNo ratings yet

- Developing Power Cycles Simulations For An Applied Thermodynamics CourseDocument12 pagesDeveloping Power Cycles Simulations For An Applied Thermodynamics Coursebakisahin2No ratings yet

- LabDocument11 pagesLabravi855885No ratings yet

- Syllabus M.tech Extc-1Document59 pagesSyllabus M.tech Extc-1swapnilNo ratings yet

- ME 310 Fall 2023 Course PolicyDocument2 pagesME 310 Fall 2023 Course PolicyNecati Eray UçarNo ratings yet

- Ue Obe-Syllabus Ncp515Document13 pagesUe Obe-Syllabus Ncp515Alexis John RubioNo ratings yet

- MPMC Lab ManualDocument127 pagesMPMC Lab ManualMeghashyam Sarma0% (1)

- Neural Networks BrochureDocument2 pagesNeural Networks BrochureAnonymous xaeuoo4No ratings yet

- tdj3m Todd Crossley April 2014Document11 pagestdj3m Todd Crossley April 2014api-201489392No ratings yet

- Resource Practicefeedback Learining Content Presentation: Bago City CollegeDocument2 pagesResource Practicefeedback Learining Content Presentation: Bago City Collegeᒛᓏᕨᖻ ᗫᕧ ᒷᕠ ᑖᖆᘴᙑNo ratings yet

- SS 0slab 15csl67Document63 pagesSS 0slab 15csl67TalibNo ratings yet

- ECE - 3rd To 8th SemDocument147 pagesECE - 3rd To 8th SemSonaal GuptaNo ratings yet

- CN Lab Manual HighlitedDocument72 pagesCN Lab Manual Highliteddarshangondkar15No ratings yet

- FEM Course HandoutDocument3 pagesFEM Course HandoutSyed Sirajul HaqNo ratings yet

- Wa0013 PDFDocument70 pagesWa0013 PDFRahulPatilNo ratings yet

- Department of Information Technology Faculty of CS&IT: Course TitleDocument5 pagesDepartment of Information Technology Faculty of CS&IT: Course TitleNabeel SalmanNo ratings yet

- Outline Syllabi Field of Electronic Telecommunication EngineeringDocument64 pagesOutline Syllabi Field of Electronic Telecommunication EngineeringsukirajNo ratings yet

- ELEC5402 Digital Integrated Circuit Design 2010Document4 pagesELEC5402 Digital Integrated Circuit Design 2010tssandeepkumarchoudhary@scribd0% (1)

- Beginners Guide To Digital ElectronicsDocument3 pagesBeginners Guide To Digital ElectronicsSuperusNovusNo ratings yet

- BE Syllabus Chandigarh UniversityDocument114 pagesBE Syllabus Chandigarh Universitykashishbhatia50% (2)

- ECE NITRR SyllabusDocument78 pagesECE NITRR SyllabusDeepak Kumar RaiNo ratings yet

- Eee Peo-PoDocument1 pageEee Peo-PoAyyar KandasamyNo ratings yet

- Session 13c6Document5 pagesSession 13c6viratNo ratings yet

- Subject For Software Engineering Course MalaysiaDocument10 pagesSubject For Software Engineering Course Malaysiaafiqzaqwan001No ratings yet

- TeachingPlan BTKR1313 SEM1 20122013Document10 pagesTeachingPlan BTKR1313 SEM1 20122013Sabikan SulaimanNo ratings yet

- Final Hand Book 2-2 2013-14Document66 pagesFinal Hand Book 2-2 2013-14sunilkumareceNo ratings yet

- CSE Syllabus Draft 28aug19Document132 pagesCSE Syllabus Draft 28aug19240 Sadman ShafiNo ratings yet

- Rajat Sood: Male, 23 YearsDocument3 pagesRajat Sood: Male, 23 Yearspramesh1010No ratings yet

- Course Outcome (Co) : Name of Course/Subject: Digital Communication (Theory)Document3 pagesCourse Outcome (Co) : Name of Course/Subject: Digital Communication (Theory)Praveen Khatkale PatilNo ratings yet

- 4 - E&TC SY Syllabus W.E.F. 23-24 Autonomous WIT - FY - 22-23Document42 pages4 - E&TC SY Syllabus W.E.F. 23-24 Autonomous WIT - FY - 22-23SarinNo ratings yet

- MS in Electronics and Telecommunications Engineering (MS-ETE)Document3 pagesMS in Electronics and Telecommunications Engineering (MS-ETE)Sharif SarwarNo ratings yet

- GGS College of Modern Technology, Kharar: Department of Electrical EngineeringDocument6 pagesGGS College of Modern Technology, Kharar: Department of Electrical EngineeringHarsh BatthNo ratings yet

- Resume: Ability To Work Alone and in Team Dedication and Perfectness On Work Zeal To Learn New ThingsDocument3 pagesResume: Ability To Work Alone and in Team Dedication and Perfectness On Work Zeal To Learn New ThingsNasir AhmedNo ratings yet

- Course File CPDocument70 pagesCourse File CPkaps_er_3No ratings yet

- Model of Department Information - EceDocument5 pagesModel of Department Information - EcegdeepthiNo ratings yet

- Emt & TL Course FileDocument42 pagesEmt & TL Course FileSuraj KumarNo ratings yet

- Lowres Engcoursecg 0214 PDFDocument24 pagesLowres Engcoursecg 0214 PDFIrakshayNo ratings yet

- MEC 4627 Vehicle Electronic and Instrumental SystemDocument5 pagesMEC 4627 Vehicle Electronic and Instrumental SystemFarith AhmadNo ratings yet

- NITRR SyllabusDocument77 pagesNITRR SyllabusDeepak Kumar RaiNo ratings yet

- Mechatronics Curriculum White PaperDocument4 pagesMechatronics Curriculum White PaperSolGriffinNo ratings yet

- Teaching and Learning in STEM With Computation, Modeling, and Simulation Practices: A Guide for Practitioners and ResearchersFrom EverandTeaching and Learning in STEM With Computation, Modeling, and Simulation Practices: A Guide for Practitioners and ResearchersNo ratings yet