Professional Documents

Culture Documents

Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-I

Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-I

Uploaded by

shankarCopyright:

Available Formats

You might also like

- Assignment 2021-22Document2 pagesAssignment 2021-22Dan Ojwang67% (3)

- Homework 1 (DLC)Document3 pagesHomework 1 (DLC)Aamir KhanNo ratings yet

- DE Question BankDocument5 pagesDE Question BankKaree MullahNo ratings yet

- DE Assignment-3Document2 pagesDE Assignment-3shivajisingh12345678123456No ratings yet

- DCEPFDocument11 pagesDCEPFkanishkhatanaNo ratings yet

- What Is Meant by Register TransferDocument4 pagesWhat Is Meant by Register TransferSiva GuruNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- Question Bank Unit 4-1Document3 pagesQuestion Bank Unit 4-1birajkushwaha1996No ratings yet

- CMOS Two Input NAND Gate and NOR GateDocument4 pagesCMOS Two Input NAND Gate and NOR GateSiva GuruNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- 19EC303 QP RepositoryDocument4 pages19EC303 QP RepositoryssfjvhsffsNo ratings yet

- College of Engineering, Nashik - 4Document2 pagesCollege of Engineering, Nashik - 4Klein Morallos BianesNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- 210 - EC8392, EC6302 Digital Electronics - Important QuestionsDocument2 pages210 - EC8392, EC6302 Digital Electronics - Important QuestionsMuhammad NawazNo ratings yet

- Epc Questions - Cs8351 Digital Principles and System DesignDocument2 pagesEpc Questions - Cs8351 Digital Principles and System DesignaltaNo ratings yet

- Template Assignment 3Document3 pagesTemplate Assignment 3Sador YonasNo ratings yet

- Da2 271222Document4 pagesDa2 271222rh457707No ratings yet

- D11se3 Extc DLDDocument1 pageD11se3 Extc DLDRahul KadamNo ratings yet

- TP 1 Computer Systems II - Yonder ArellanoDocument9 pagesTP 1 Computer Systems II - Yonder ArellanoScribdTranslationsNo ratings yet

- DIGITAL CIRCUIT AND SYSTEM End TermDocument2 pagesDIGITAL CIRCUIT AND SYSTEM End TermRavindra KumarNo ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- Digital Logic Circuits PDFDocument8 pagesDigital Logic Circuits PDFnaina10691No ratings yet

- Digital 4Document38 pagesDigital 4usaravanakumarNo ratings yet

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- Original PDFDocument3 pagesOriginal PDFMaxamedNo ratings yet

- TKHTS Cuoiky 20192 Thuy - CTTTDocument1 pageTKHTS Cuoiky 20192 Thuy - CTTTLinh Nguyen TienNo ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- Sample FinalDocument8 pagesSample FinalJonathan JufenoNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- EE& EIC de Assingement - IIDocument1 pageEE& EIC de Assingement - IIAkshay GuptaNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- EESB423 Sem1 1314 Assignment2Document3 pagesEESB423 Sem1 1314 Assignment2Shamraj KunnasagarNo ratings yet

- Digital System Design QuestionsDocument5 pagesDigital System Design Questionsvijay4u4allNo ratings yet

- Digital Circuit Design-ECE 2026 Digital AssignmentDocument1 pageDigital Circuit Design-ECE 2026 Digital AssignmentDesta Yakob Doda 18BML0121No ratings yet

- Practice Sheet CDA-1Document6 pagesPractice Sheet CDA-1brijesh.gec21No ratings yet

- EE2001 Tutorial 5Document9 pagesEE2001 Tutorial 5RetheshNo ratings yet

- Question Bank DSDDocument6 pagesQuestion Bank DSDJithinmvijayan VijayanNo ratings yet

- Chapter 4 Combinational LogicDocument54 pagesChapter 4 Combinational LogicAkrur NeupaneNo ratings yet

- Digital System Deisgn (ELE 2152) RCS (Makeup) Dec 19Document2 pagesDigital System Deisgn (ELE 2152) RCS (Makeup) Dec 19Abhinav KumarNo ratings yet

- BE EC5303 DSD Nov2021 QP2Document2 pagesBE EC5303 DSD Nov2021 QP2hello worldNo ratings yet

- CompoundDocument4 pagesCompounduscrNo ratings yet

- Ejercicios Unidad VIIDocument2 pagesEjercicios Unidad VIIdiego4545No ratings yet

- 2001 Paper E2.1/ISE2.2: Digital Electronics IIDocument12 pages2001 Paper E2.1/ISE2.2: Digital Electronics IIkolkassNo ratings yet

- Digital Electronic Circuits (ELE 2102) RCS (MAKE UP) Dec 17Document2 pagesDigital Electronic Circuits (ELE 2102) RCS (MAKE UP) Dec 17Abhinav KumarNo ratings yet

- VL2019205005389 Da PDFDocument44 pagesVL2019205005389 Da PDFsimon jordan1005No ratings yet

- Advanced Digital Systems DesignDocument12 pagesAdvanced Digital Systems DesignlawrencerajasekaranNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- Model QPDocument6 pagesModel QPvlsisivaNo ratings yet

- Synchronous Sequential Circuit Problems: Problem # 1Document6 pagesSynchronous Sequential Circuit Problems: Problem # 1Anonymous AFFiZnNo ratings yet

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiNo ratings yet

- Computer System Architecture Assignment 1Document1 pageComputer System Architecture Assignment 1Mohini Mohit BatraNo ratings yet

- Design A Pulse Mode Circuit Having Two InputDocument4 pagesDesign A Pulse Mode Circuit Having Two InputSiva GuruNo ratings yet

- Line Drawing Algorithm: Mastering Techniques for Precision Image RenderingFrom EverandLine Drawing Algorithm: Mastering Techniques for Precision Image RenderingNo ratings yet

- Adsd TT 2018Document1 pageAdsd TT 2018shankarNo ratings yet

- Ex05 - Question Paper Ada Te-1Document2 pagesEx05 - Question Paper Ada Te-1shankarNo ratings yet

- MATLAB BasicsDocument24 pagesMATLAB BasicsshankarNo ratings yet

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsDocument11 pagesDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarNo ratings yet

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyDocument5 pagesZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarNo ratings yet

- Kongunadu College of Engineering and TechnologyDocument2 pagesKongunadu College of Engineering and TechnologyshankarNo ratings yet

- NBA Modified RF&MW LPDocument4 pagesNBA Modified RF&MW LPshankarNo ratings yet

- Adaic TT 2016Document2 pagesAdaic TT 2016shankarNo ratings yet

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Document17 pagesEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarNo ratings yet

- Digital Signal Processing Introduction PartDocument13 pagesDigital Signal Processing Introduction Partshankar100% (1)

- Kongunadu College of Engineering and Technology, ThourpattiDocument1 pageKongunadu College of Engineering and Technology, ThourpattishankarNo ratings yet

- CH 3 - FeedbackDocument54 pagesCH 3 - FeedbackshankarNo ratings yet

- DSP Question Paper Unit 1Document10 pagesDSP Question Paper Unit 1shankarNo ratings yet

- Unit V: Time Varying Fields and Maxwell'S EquationsDocument12 pagesUnit V: Time Varying Fields and Maxwell'S EquationsshankarNo ratings yet

- Ap7102 Adsd SyllabiDocument6 pagesAp7102 Adsd SyllabishankarNo ratings yet

- Ex05b - PDSP Question Paper - Te - 1Document4 pagesEx05b - PDSP Question Paper - Te - 1shankarNo ratings yet

- DSP Question Paper Unit 4Document2 pagesDSP Question Paper Unit 4shankarNo ratings yet

- PDSP - T1 - 1 - Shaju QPDocument2 pagesPDSP - T1 - 1 - Shaju QPshankarNo ratings yet

- EC6403 Lesson Plan EMF 2014Document4 pagesEC6403 Lesson Plan EMF 2014shankarNo ratings yet

- DSP Objective QuestionsDocument4 pagesDSP Objective QuestionsshankarNo ratings yet

Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-I

Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-I

Uploaded by

shankarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-I

Kongunadu College of Engineering and Technology M.E-Applied Electronics Advanced Digital System Design-Assignment-I

Uploaded by

shankarCopyright:

Available Formats

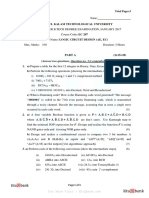

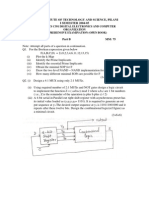

Kongunadu College of Engineering and Technology

M.E-Applied Electronics

Advanced Digital System Design-Assignment-I

1.Design a serial adder using mealy model and Moore model. Also

draw the ASM chart for both the models.

2. Write down the design steps involved in designing Traditional

synchronous sequential circuits.

3. With an example explain the state assignment rules.

4. Determine the minimal state equivalent of the state table given

5. Design a sequential circuit to convert BCD to excess 3 codes

6. Design an asynchronous sequential circuit that has two inputs X2 and

X1 and one output Z. When X1 = 0, the output Z is 0. The first change in

X2 that occurs while X1 is 1 will cause output Z to be 1. The output Z

remains at 1 until X1 returns to 0.

7. Explain the design steps involved in the realization of ASM.

8. Design a Fundamental mode asynchronous sequential network

meeting the following requirements :

(i) There are 2 inputs xl and x2 and single output z.

(ii) The inputs xl and x2 never change simultaneously

(iii) An output z = 1 is to occur only during the input state xlx2 = 01

and if input state xlx2 = 01 is preceded by input sequence x1x2 =

01,00,10,00,10,00.

9. Determine the minimal state equivalent of the state table given using

Implication chart.

10. Design a gated latch circuit with two inputs, G (gate) and D (data),

and one output Q. The gated latch is a memory element that accepts the

value of D when G = 1 and retains this value after G goes to 0. Once G

= 0, a change in D does not change the value of the output Q.

You might also like

- Assignment 2021-22Document2 pagesAssignment 2021-22Dan Ojwang67% (3)

- Homework 1 (DLC)Document3 pagesHomework 1 (DLC)Aamir KhanNo ratings yet

- DE Question BankDocument5 pagesDE Question BankKaree MullahNo ratings yet

- DE Assignment-3Document2 pagesDE Assignment-3shivajisingh12345678123456No ratings yet

- DCEPFDocument11 pagesDCEPFkanishkhatanaNo ratings yet

- What Is Meant by Register TransferDocument4 pagesWhat Is Meant by Register TransferSiva GuruNo ratings yet

- Digital 16 Marks.Document4 pagesDigital 16 Marks.Saranya PrabhuNo ratings yet

- Question Bank Unit 4-1Document3 pagesQuestion Bank Unit 4-1birajkushwaha1996No ratings yet

- CMOS Two Input NAND Gate and NOR GateDocument4 pagesCMOS Two Input NAND Gate and NOR GateSiva GuruNo ratings yet

- Apr - May 2023Document3 pagesApr - May 2023Pandyselvi BalasubramanianNo ratings yet

- EE8351 Iq 16 Marks PDFDocument7 pagesEE8351 Iq 16 Marks PDFdeepika senthilNo ratings yet

- DLD Ques1Document2 pagesDLD Ques1mahbub mitulNo ratings yet

- 19EC303 QP RepositoryDocument4 pages19EC303 QP RepositoryssfjvhsffsNo ratings yet

- College of Engineering, Nashik - 4Document2 pagesCollege of Engineering, Nashik - 4Klein Morallos BianesNo ratings yet

- Important 16 Mark Questions-19!1!2024Document5 pagesImportant 16 Mark Questions-19!1!2024FLOWERNo ratings yet

- 210 - EC8392, EC6302 Digital Electronics - Important QuestionsDocument2 pages210 - EC8392, EC6302 Digital Electronics - Important QuestionsMuhammad NawazNo ratings yet

- Epc Questions - Cs8351 Digital Principles and System DesignDocument2 pagesEpc Questions - Cs8351 Digital Principles and System DesignaltaNo ratings yet

- Template Assignment 3Document3 pagesTemplate Assignment 3Sador YonasNo ratings yet

- Da2 271222Document4 pagesDa2 271222rh457707No ratings yet

- D11se3 Extc DLDDocument1 pageD11se3 Extc DLDRahul KadamNo ratings yet

- TP 1 Computer Systems II - Yonder ArellanoDocument9 pagesTP 1 Computer Systems II - Yonder ArellanoScribdTranslationsNo ratings yet

- DIGITAL CIRCUIT AND SYSTEM End TermDocument2 pagesDIGITAL CIRCUIT AND SYSTEM End TermRavindra KumarNo ratings yet

- DLD Question BankDocument5 pagesDLD Question BankHarshad ThiteNo ratings yet

- Digital Logic Circuits PDFDocument8 pagesDigital Logic Circuits PDFnaina10691No ratings yet

- Digital 4Document38 pagesDigital 4usaravanakumarNo ratings yet

- Answer Two Questions, Question No. 3 Is CompulsoryDocument3 pagesAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KNo ratings yet

- Original PDFDocument3 pagesOriginal PDFMaxamedNo ratings yet

- TKHTS Cuoiky 20192 Thuy - CTTTDocument1 pageTKHTS Cuoiky 20192 Thuy - CTTTLinh Nguyen TienNo ratings yet

- Cs PaperDocument37 pagesCs PaperAshish BokilNo ratings yet

- Sample FinalDocument8 pagesSample FinalJonathan JufenoNo ratings yet

- Birla Institute of Technology and Science, Pilani I SEMESTER 2004-05Document6 pagesBirla Institute of Technology and Science, Pilani I SEMESTER 2004-05navaneeth_kumarNo ratings yet

- EE& EIC de Assingement - IIDocument1 pageEE& EIC de Assingement - IIAkshay GuptaNo ratings yet

- Digital Logic CircuitsDocument7 pagesDigital Logic CircuitsMATHANKUMAR.SNo ratings yet

- 9A04401 Switching Theory & Logic DesignDocument4 pages9A04401 Switching Theory & Logic DesignsivabharathamurthyNo ratings yet

- EESB423 Sem1 1314 Assignment2Document3 pagesEESB423 Sem1 1314 Assignment2Shamraj KunnasagarNo ratings yet

- Digital System Design QuestionsDocument5 pagesDigital System Design Questionsvijay4u4allNo ratings yet

- Digital Circuit Design-ECE 2026 Digital AssignmentDocument1 pageDigital Circuit Design-ECE 2026 Digital AssignmentDesta Yakob Doda 18BML0121No ratings yet

- Practice Sheet CDA-1Document6 pagesPractice Sheet CDA-1brijesh.gec21No ratings yet

- EE2001 Tutorial 5Document9 pagesEE2001 Tutorial 5RetheshNo ratings yet

- Question Bank DSDDocument6 pagesQuestion Bank DSDJithinmvijayan VijayanNo ratings yet

- Chapter 4 Combinational LogicDocument54 pagesChapter 4 Combinational LogicAkrur NeupaneNo ratings yet

- Digital System Deisgn (ELE 2152) RCS (Makeup) Dec 19Document2 pagesDigital System Deisgn (ELE 2152) RCS (Makeup) Dec 19Abhinav KumarNo ratings yet

- BE EC5303 DSD Nov2021 QP2Document2 pagesBE EC5303 DSD Nov2021 QP2hello worldNo ratings yet

- CompoundDocument4 pagesCompounduscrNo ratings yet

- Ejercicios Unidad VIIDocument2 pagesEjercicios Unidad VIIdiego4545No ratings yet

- 2001 Paper E2.1/ISE2.2: Digital Electronics IIDocument12 pages2001 Paper E2.1/ISE2.2: Digital Electronics IIkolkassNo ratings yet

- Digital Electronic Circuits (ELE 2102) RCS (MAKE UP) Dec 17Document2 pagesDigital Electronic Circuits (ELE 2102) RCS (MAKE UP) Dec 17Abhinav KumarNo ratings yet

- VL2019205005389 Da PDFDocument44 pagesVL2019205005389 Da PDFsimon jordan1005No ratings yet

- Advanced Digital Systems DesignDocument12 pagesAdvanced Digital Systems DesignlawrencerajasekaranNo ratings yet

- 9A04401 Switching Theory and Logic DesignDocument4 pages9A04401 Switching Theory and Logic DesignsivabharathamurthyNo ratings yet

- EC8392-Digital EletronicsDocument2 pagesEC8392-Digital Eletronicssyed1188No ratings yet

- Assignment EDES232CDocument3 pagesAssignment EDES232CPrakash DasNo ratings yet

- Model QPDocument6 pagesModel QPvlsisivaNo ratings yet

- Synchronous Sequential Circuit Problems: Problem # 1Document6 pagesSynchronous Sequential Circuit Problems: Problem # 1Anonymous AFFiZnNo ratings yet

- 21 - 2011 - Dec - R09 - STLDDocument8 pages21 - 2011 - Dec - R09 - STLDvasuvlsiNo ratings yet

- Computer System Architecture Assignment 1Document1 pageComputer System Architecture Assignment 1Mohini Mohit BatraNo ratings yet

- Design A Pulse Mode Circuit Having Two InputDocument4 pagesDesign A Pulse Mode Circuit Having Two InputSiva GuruNo ratings yet

- Line Drawing Algorithm: Mastering Techniques for Precision Image RenderingFrom EverandLine Drawing Algorithm: Mastering Techniques for Precision Image RenderingNo ratings yet

- Adsd TT 2018Document1 pageAdsd TT 2018shankarNo ratings yet

- Ex05 - Question Paper Ada Te-1Document2 pagesEx05 - Question Paper Ada Te-1shankarNo ratings yet

- MATLAB BasicsDocument24 pagesMATLAB BasicsshankarNo ratings yet

- Design of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsDocument11 pagesDesign of Efficient Class-E Power Amplifiers For Short-Distance CommunicationsshankarNo ratings yet

- Zero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyDocument5 pagesZero Diagonal Property Symmetry Property Unitary Property Phase Shift PropertyshankarNo ratings yet

- Kongunadu College of Engineering and TechnologyDocument2 pagesKongunadu College of Engineering and TechnologyshankarNo ratings yet

- NBA Modified RF&MW LPDocument4 pagesNBA Modified RF&MW LPshankarNo ratings yet

- Adaic TT 2016Document2 pagesAdaic TT 2016shankarNo ratings yet

- Ec 6502 Principles of Digital Signal Processing - Question Bank - 2018Document17 pagesEc 6502 Principles of Digital Signal Processing - Question Bank - 2018shankarNo ratings yet

- Digital Signal Processing Introduction PartDocument13 pagesDigital Signal Processing Introduction Partshankar100% (1)

- Kongunadu College of Engineering and Technology, ThourpattiDocument1 pageKongunadu College of Engineering and Technology, ThourpattishankarNo ratings yet

- CH 3 - FeedbackDocument54 pagesCH 3 - FeedbackshankarNo ratings yet

- DSP Question Paper Unit 1Document10 pagesDSP Question Paper Unit 1shankarNo ratings yet

- Unit V: Time Varying Fields and Maxwell'S EquationsDocument12 pagesUnit V: Time Varying Fields and Maxwell'S EquationsshankarNo ratings yet

- Ap7102 Adsd SyllabiDocument6 pagesAp7102 Adsd SyllabishankarNo ratings yet

- Ex05b - PDSP Question Paper - Te - 1Document4 pagesEx05b - PDSP Question Paper - Te - 1shankarNo ratings yet

- DSP Question Paper Unit 4Document2 pagesDSP Question Paper Unit 4shankarNo ratings yet

- PDSP - T1 - 1 - Shaju QPDocument2 pagesPDSP - T1 - 1 - Shaju QPshankarNo ratings yet

- EC6403 Lesson Plan EMF 2014Document4 pagesEC6403 Lesson Plan EMF 2014shankarNo ratings yet

- DSP Objective QuestionsDocument4 pagesDSP Objective QuestionsshankarNo ratings yet