Professional Documents

Culture Documents

FJKCP

FJKCP

Uploaded by

Wahyu Septriandi SaktiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

FJKCP

FJKCP

Uploaded by

Wahyu Septriandi SaktiCopyright:

Available Formats

Libraries Guide www.xilinx.

com 493

ISE 6.3i 1-800-255-7778

FJKCP

R

FJKCP

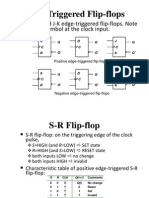

J-K Flip-Flop with Asynchronous Clear and Preset

FJKCP is a single J-K-type flip-flop with J, K, asynchronous clear (CLR), and

asynchronous preset (PRE) inputs and data output (Q). When the asynchronous clear

(CLR) is High, all other inputs are ignored and Q is reset 0. The asynchronous preset

(PRE), when High, and CLR set to Low overrides all other inputs and sets the Q

output High. When CLR and PRE are Low, Q responds to the state of the J and K

inputs during the Low-to-High clock transition, as shown in the following truth table.

The flip-flop is asynchronously cleared, output Low, when power is applied. The

power-on condition can be simulated by applying a High-level pulse on the PRLD

global net.

FJKCP Implementation XC9500/XV/XL, CoolRunner XPLA3, CoolRunner-II

Architectures Supported

FJKCP

Spartan-II, Spartan-IIE No

Spartan-3 No

Virtex, Virtex-E No

Virtex-II, Virtex-II Pro, Virtex-II Pro X No

XC9500, XC9500XV, XC9500XL Macro

CoolRunner XPLA3 Macro

CoolRunner-II Macro

Inputs Outputs

CLR PRE J K C Q

1 X X X X 0

0 1 X X X 1

0 0 0 0 X No Chg

0 0 0 1 0

0 0 1 0 1

0 0 1 1 Toggle

Q

J

C

FJKCP

K

PRE

CLR

X4390

Q

X8124

C

AND2B1

FDCP

D

C

Q

PRE

OR2

K

AND2B1

PRE

CLR

Q

J

CLR

FJKCP

R

494 www.xilinx.com Libraries Guide

1-800-255-7778 ISE 6.3i

Usage

For HDL, this design element is inferred rather than instantiated.

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- J-K Flip FlopDocument5 pagesJ-K Flip FlopNagham Hikmat AzizNo ratings yet

- Project ReportDocument11 pagesProject Reportamiethurgat100% (2)

- Expt 12Document5 pagesExpt 12Dhrrishith VikalNo ratings yet

- Flip Flop Counters PDFDocument15 pagesFlip Flop Counters PDFAdarsh SinghNo ratings yet

- Unit 4Document11 pagesUnit 4anithar2No ratings yet

- UntitledDocument8 pagesUntitledlalita chauhanNo ratings yet

- Search For DocumentsDocument9 pagesSearch For DocumentsdineshvhavalNo ratings yet

- Flip FlopDocument6 pagesFlip FlopMuzakki SathorNo ratings yet

- Unit 4 D-JK Flip FlopsDocument17 pagesUnit 4 D-JK Flip FlopsRongeet SodhiNo ratings yet

- Basic Flip-Flop CircuitDocument2 pagesBasic Flip-Flop CircuitSyieda ZamryNo ratings yet

- Module 4Document26 pagesModule 4OKNo ratings yet

- Elc2242 - VHDL - 15Document2 pagesElc2242 - VHDL - 15Ahmed AdilNo ratings yet

- Flip Flops in Sequential CircuitsDocument9 pagesFlip Flops in Sequential Circuitsarpanrin2No ratings yet

- Mod 5 - FLIPFLOPS and Its TypesDocument28 pagesMod 5 - FLIPFLOPS and Its TypesRavi CharanNo ratings yet

- Experiment 3Document4 pagesExperiment 3Ishan Satya PrakashNo ratings yet

- JK Flip Flop July4Document4 pagesJK Flip Flop July4devpratap110305No ratings yet

- Flipflops: Technical Seminar ReportDocument16 pagesFlipflops: Technical Seminar ReportrachitNo ratings yet

- Flip-Flop and Memory (12328)Document14 pagesFlip-Flop and Memory (12328)red100% (1)

- Title ObjectiveDocument4 pagesTitle ObjectiveShekhar ShuklaNo ratings yet

- CSE 1203 Introduction To Sequential Circuits and FFDocument27 pagesCSE 1203 Introduction To Sequential Circuits and FFgbikornoNo ratings yet

- M7 Sequentials Circuits-1Document67 pagesM7 Sequentials Circuits-1joelNo ratings yet

- The Clocked RS Flip-FlopDocument4 pagesThe Clocked RS Flip-Flopabhisheksikka17No ratings yet

- Objective Questions MCQ On LatchesDocument32 pagesObjective Questions MCQ On LatchesNaman KumarNo ratings yet

- T Flip Flop With Synch Ron Us ClearDocument4 pagesT Flip Flop With Synch Ron Us ClearKhalid JavedNo ratings yet

- Latch and Flip-FlopDocument58 pagesLatch and Flip-FlopDalila Nadia RazaliNo ratings yet

- DL CH 4Document50 pagesDL CH 4Praches AcharyaNo ratings yet

- Topic 5 - Flip Flops Sequential CircuitsDocument16 pagesTopic 5 - Flip Flops Sequential CircuitsShivneet KumarNo ratings yet

- Flip FlopDocument5 pagesFlip Flopwala alabedNo ratings yet

- EXPT:-Study of J K Flip Flop Using IC 7476 Apparatus:-IC 7476, Breadboard, Single Stand WiresDocument4 pagesEXPT:-Study of J K Flip Flop Using IC 7476 Apparatus:-IC 7476, Breadboard, Single Stand WiresPoonam GholapNo ratings yet

- JK FlilflopDocument6 pagesJK FlilflopImran AliNo ratings yet

- Asynchronous Flip Flop InputsDocument3 pagesAsynchronous Flip Flop InputsCarolina CastanedaNo ratings yet

- Practical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Document5 pagesPractical: 14 To Study J - K Flip Flop: Sohil Vohra (Lecturer - Shri K.J. Polytechnic College, Bharuch (C.E. Deptt) )Sohil VohraNo ratings yet

- Flip FlopsDocument3 pagesFlip FlopsnikomuzNo ratings yet

- Cream and Brown Minimalist Let's Learn PresentationDocument25 pagesCream and Brown Minimalist Let's Learn PresentationReychille AbianNo ratings yet

- Chap 8Document8 pagesChap 8mailusman9835No ratings yet

- Chapter 2.2Document15 pagesChapter 2.2OzzyNo ratings yet

- DSD Module 5Document81 pagesDSD Module 5Abinesh RNo ratings yet

- MD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5Document17 pagesMD. Shybur Rahaman - 1811099 - EEE232L - Lab - Report - 5shyburrahaman120No ratings yet

- FlipssDocument8 pagesFlipssOrion Starbwoy BlackstockNo ratings yet

- The J K Flip FlopDocument3 pagesThe J K Flip FlopSaanguNo ratings yet

- 2 FlipflopDocument19 pages2 FlipfloplidhisijuNo ratings yet

- EE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Document19 pagesEE331L Experiment #4: Written By: Shehab Alaa Ramadan Group: C University ID Number: 022180589Shehab RamadanNo ratings yet

- Module 5 - Counter Design Problems and Flip-Flops - Oct 8thDocument65 pagesModule 5 - Counter Design Problems and Flip-Flops - Oct 8thRavi CharanNo ratings yet

- Flip FlopsDocument11 pagesFlip FlopsZakaria JubarnNo ratings yet

- JK Flip Flop Experiment 9Document5 pagesJK Flip Flop Experiment 9Nev Callejo50% (2)

- Simulation of Se Qu Ntial CK TDocument10 pagesSimulation of Se Qu Ntial CK TSivaprakasam KarthikeyanNo ratings yet

- Jkflip FlopDocument27 pagesJkflip FlopUsama NaveedNo ratings yet

- The Basic JK Flip-FlopDocument4 pagesThe Basic JK Flip-Flopom1444100% (1)

- JK Flip Flop Is The Most Widely Used of All The Flip-Flop Designs and Is ConsideredDocument1 pageJK Flip Flop Is The Most Widely Used of All The Flip-Flop Designs and Is ConsidereddbircsNo ratings yet

- Date: 06-10-2020, 8AM-9 AM Branch: CS/2 Year Topic: Flip FlopsDocument14 pagesDate: 06-10-2020, 8AM-9 AM Branch: CS/2 Year Topic: Flip FlopsTech guru MaheshwariNo ratings yet

- D Flip-FlopDocument35 pagesD Flip-FlopSwati Kasht100% (1)

- Unit 5 Sequential CircuitDocument21 pagesUnit 5 Sequential CircuitAnurag GoelNo ratings yet

- ET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)Document19 pagesET398 LAB 6 "Flip-Flops in VHDL" (PDFDrive)kaesarsabahNo ratings yet

- Lec 3 Asynchronous Flip-Flop InputsDocument9 pagesLec 3 Asynchronous Flip-Flop Inputsshivam007No ratings yet

- Experiment 9 (Flip Flops)Document7 pagesExperiment 9 (Flip Flops)groupidb3100% (3)

- Sequential CircuitsDocument22 pagesSequential CircuitsBaeNo ratings yet

- Flip FlopsDocument40 pagesFlip Flopszohaiba338No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Met A RouterDocument26 pagesMet A RouterWahyu Septriandi SaktiNo ratings yet

- 11.Fisika1-Kalor KinetikDocument47 pages11.Fisika1-Kalor KinetikWahyu Septriandi SaktiNo ratings yet

- Kata Kerja Tak BeraturanDocument10 pagesKata Kerja Tak BeraturanWahyu Septriandi SaktiNo ratings yet

- Kunci Unas Mat SMK 2012 Tipe CDocument8 pagesKunci Unas Mat SMK 2012 Tipe CWahyu Septriandi SaktiNo ratings yet

- R Outsos'Slu N) : 90066I 'TNVCL DTSV)Document1 pageR Outsos'Slu N) : 90066I 'TNVCL DTSV)Wahyu Septriandi SaktiNo ratings yet