Professional Documents

Culture Documents

Combi Seuqential Circuit

Combi Seuqential Circuit

Uploaded by

Cuong LaidangCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Combi Seuqential Circuit

Combi Seuqential Circuit

Uploaded by

Cuong LaidangCopyright:

Available Formats

1

CHAPTER 7:

SEQUENTIAL CIRCUITS -

FLIP-FLOPS REGISTERS FLIP FLOPS, REGISTERS,

AND COUNTERS

What will we learn? What will we learn?

2

Logic circuits that can store information

Latches, which store a single bit

Flip-Flops, which store a single bit

Registers, which store multiple bits

Shift i t Shift registers

Counters

Design Examples

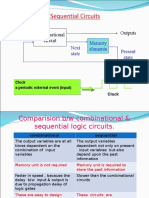

Sequential Circuits Sequential Circuits

3

Combinational Circuits

circuits without feedback

( ) output = f (current inputs)

Sequential Circuits

circuits with feedback

output = f (current inputs, past inputs, past outputs)

how can we feed the past inputs and outputs into the circuits?

b i f b ildi i l i i i basis for building memory into logic circuits

Circuits with feedback Circuits with feedback

4

How to control feedback?

h t t l f li d dl l what stops values from cycling around endlessly

x

1

x

2

y

1

y

2

Sequential

Circuit

2

x

3

y

2

y

3

.

.

.

.

x

n

y

m

. .

Control of an alarm system Control of an alarm system

5

S t

Memory

element

Alarm

Sensor

Reset

Set

On Off

the simplest case of a sequential circuit

Reset

p q

Alarm is on when the sensor generates the Set signal in

response to some undesirable events

O h l i i l b d ff ll h h Once the alarm is on, it can only be turned off manually through

a reset button

Memory is needed to remember that the alarm Memory is needed to remember that the alarm

has to be active until the reset signal arrives

A simple memory element A simple memory element

6

Th di l The most rudimentary memory element

Two inverters form a static memory cell

Assume A=0 and B=1 then the below circuit will maintain these Assume A=0 and B=1, then the below circuit will maintain these

values indefinitely (as long as it has power applied)

The state is defined by the value of the memory cell

Two states

A B

Two states

How to get a new value into the memory cell? How to get a new value into the memory cell?

selectively break feedback path

load new value into cell

A controlled memory element A controlled memory element

7

Load

A B

Output Data

TG1

TG2

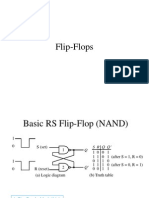

A memory element with NOR gates A memory element with NOR gates

8

C t t ll i di l i t Construct a memory cell using ordinary logic gates

Two NOR gates are connected in cross-coupled style

Basic Latch

Two inputs

Reset

Set

Reset

Set Q

A basic latch built with NOR gates A basic latch built with NOR gates

9

S R Q

a

Q

b

0 0

0 1

1 0

0/1 1/0

0 1

1 0

Q

a

R

(no change)

1 1 0 0

(a) Circuit (b) Truth table or characteristic table

Q

b

S

1

0

1

R

t

1

t

2

t

3

t

4

t

5

t

6

t

7

t

8

t

9

t

10

1

0

1

S

Q

a ?

There will

be an

oscillation

0

1

0

Q

b ?

Time

(c) Timing diagram

Timing Waveform Timing Waveform

10

R

S

R

S

Q

Timing Waveform

Reset Hold Set Reset

Set

Race

S

\Q

100

R

Reset Hold Set Reset

Set

Race

S

Q

\ Q

Forbidden State

Forbidden State

State Behavior of R-S Latch State Behavior of R S Latch

11

Q

hold

S

0

R

0

Q Q Q Q

0 1

1 0

0

1

unstable

0

1

1

1

0

1

Truth Table Summary

unstable 1 1

Q Q

0 0

of R-S Latch Behavior

Q Q

1 1 1 1

Theoretical R-S Latch State Diagram Theoretical R S Latch State Diagram

12

Q Q Q Q

1 0

SR = 1 0

SR = 00, 01

SR = 00, 10

State Diagram

state: possible values

0 1

1 0

SR = 0 1

SR = 0 1 SR = 1 0

transitions: changes

based on inputs

Q Q

0 0

SR = 1 1

SR = 1 1

SR = 11

0 0

SR = 0 0

SR = 1 0 SR = 0 1

Q Q

1 1

SR = 0 0, 11

1 1

Observed R-S Latch Behavior

SR = 00 01

SR = 00, 10

Observed R S Latch Behavior

13

Q Q Q Q

1 0

SR = 1 0

SR = 00, 01

SR 00, 10

0 1

1 0

SR = 0 1

SR = 0 1 SR = 1 0

SR = 1 1

SR = 1 1

SR = 11

Q Q

0 0

SR = 0 0

SR = 0 0

Very difficult to observe R-S Latch in the 1-1 state

Ambiguously returns to state 0-1 or 1-0 Ambiguously returns to state 0 1 or 1 0

A so-called " race condition"

R-S Latch Analysis

T th T bl

Derived K-Map:

R S Latch Analysis

14

R-S Latch Revisited

Truth Table:

Next State = F(S, R, Current State)

Derived K-Map:

SR

00 01 11 10

Q ( t )

S

R S Latch Revisited

0 0 X 1

1 0 X 1

0

1

S R Q

t

0 0 0

0 0 1

Q+

0

1

hold

Characteristic Equation:

R

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

0

1

0

0

1

1

reset

set

S

Characteristic Equation:

Q+ = S + R Q

t

1 0 1

1 1 0

1 1 1

1

x

x not allowed

S

R

Q

R-S

Latch

Q+

Problems of R-S Latch Problems of R S Latch

15

The slightest glitch on R or S could cause

change in value stored

R-S Latch has transparent outputs

Transparent outputs : when the memory elements outputs

immediately change in response to input changes immediately change in response to input changes

Want to control when R and S inputs have Want to control when R and S inputs have

effect on value stored

E bl Si l ( l k i l) Enable Signal (or clock signal)

R and S inputs are active only when Enable = 1

Gated Latches or Level sensitive latches Gated Latches or Level sensitive latches

Gated SR latch Gated SR latch

C t l h R d S i t

16

\ S

Control when R and S inputs

matters

the latch can be modified to respond to

th i t i l S d R l h

\ S

\ Q

the input signal S and R only when

Enable =1 \ R

Q

\enb

output is

Set Reset

output is

changing

output is

stable

Gated SR Latch Gated SR Latch

17

Gated SR latch with NAND gates Gated SR latch with NAND gates

18

S

Q

Clk

R

Q

Problems of the Gated S/R Latches Problems of the Gated S/R Latches

19

1. Forbidden State and Race condition

How to eliminate the forbidden state and race condition

When S=R=1, (forbidden state)

Oscillation (Race condition)

D-type Latch

0 = = Q Q

D-type Latch

JK-Latch (toggling)

The output toggles forever when J=K=1

2. When cascading level-sensitive Latches

Master/Slave F/Fs

Edge-triggered F/Fs

1 How to eliminate the forbidden state? 1. How to eliminate the forbidden state?

20

G t d D l t h Gated D-latch

eliminate the

troublesome situation troublesome situation

where S=R=1

How to eliminate the forbidden state?

contd

21

Idea: use output feedback to

guarantee that R and S are

never both one

K R \ Q

\ Q

J-K Latch

J, K both one yields toggle

R-S

latch

K

J S

R

Q

\ Q

Q

J K Latch

J (t) K(t) Q(t)

0 0 0

Q+

0

1

hold

Q

Characteristic Equation:

Q+ = Q K + Q J

0 0 1

0 1 0

0 1 1

1 0 0

0

1

1

0

0

1

hold

reset

set

1 0 1

1 1 0

1 1 1

1

1

1

0 toggle

set

J-K Latch: Toggles forever in the

Set Reset Toggle

toggle mode

22

100

gg

J

K

QQ

\ Q

Oscillation

Toggle Correctness: Single State change per clocking event Toggle Correctness: Single State change per clocking event

Solution: Master/Slave Flipflop

Master/Slave J-K Flipflop

Master Stage Slave Stage

Master/Slave J K Flipflop

23

R-S

Latch

R-S

Latch

K

R

S

\Q

Q

\P

R

S

\Q

Q

\Q

Delay

(d)

J

S

Clk

Q

P

S Q

Q

Sample inputs while clock high

Sample inputs while clock low

Uses time to break feedback path from outputs to inputs!

1's

Set Reset T oggle Catch 100

J

K

Delay

(d)

Correct Toggle

Operation

Master

outputs

Clk

P

\ P

(d)

Slave

outputs

Q

\ Q

2 When cascading Latches 2. When cascading Latches

24

R

Q

R

R

Q

Qa

Qb

S

Q

S

S

Q

clock

How to stop changes from racing through

h i ? chain?

need to be able to control flow of data from one latch to the

next

move one latch per clock period

have to worry about logic between latches that is too fast

Master/Slave D Flip-Flop Master/Slave D Flip Flop

25

Master Slave

D Q

Q

D Q

Q

Master Slave

D

Clock

Q

Q

D Q

Q

Q

m

Q

s

Clk Clk

(a) Circuit

(c) Graphical symbol

D

Clock

Q

m

Q Q

s

=

(b) Timing diagram (b) Timing diagram

D Q D Q

D

Qa

Qb

Q Q

Clock

Positive-edge-triggered D flip-flop Positive edge triggered D flip flop

26

1

P3

1

Clock = 0

Output of gate 2 and 3 are high -> P1,P2 high

Output is maintained

Clock = 1

D

1

hold

1 D

P1

5

2

Q

P3 and P4 are transmitted through gate 2 and

3 to cause P1 = D and P2 = D.

This sets Q = D and Q = D

P3 and P4 must be stable when the clock goes from

1

hold state

D

D

D

0

Clock

6

0 to 1.

After that, the changes in D have no effect.

=0

1

D

D

D

0

P2

6

3

D Q

Q

1

=1

D

D

0

D

P4

Q Clock

4

D

D

1

1

D

(a) Circuit (b) Graphical symbol

Comparison of level-sensitive and

edge-triggered D storage elements

27

D Q D Q

Clock

D Q

Q

D

Clock

Q a

Q

a

Clk

D

Clock

Q

a

D Q

Q Q b

Q

b

Q

b

Q

c

D Q

Q Q c

Q

c

(b) Timing diagram

(a) Circuit

Master-slave D flip-flop with Clear

and Preset

28

Preset

Q

D

Clock

0

0 1

1

Q

1

1

1

1

1

0

1

0

D Q

Preset

Clear

1 1

Q

Clear

(a) Circuit

(b) Graphical symbol

Clear

Positive-edge-triggered D flip-flop

with Clear and Preset

29

Preset

Preset

Q

Preset

D Q

Clock

Clear

Q

Q

(b) Graphical symbol

D

Clear

(a) Circuit

Synchronous reset for a D flip-flop Synchronous reset for a D flip flop

30

D

Clock

Q

Q

Clear

D Q

Q

Clock

Q Q

T Flip-Flop T Flip Flop

31

T Q

T Q t 1 + ( )

D Q

Q

Q

Q

T

Q

0

1

Q t ( )

Q t ( )

(b) Truthtable (c) Graphical symbol

Clock

(a) Circuit

(b) Truth table (c) Graphical symbol

Clock

T

Q

(d) Timing diagram

Realizing JK flip-flop with D flip-flop Realizing JK flip flop with D flip flop

32

D Q

Q

J

D Q

Q

Q

Q

K

Clock

(a) Circuit

J Q

K

0

Q t 1 +

( )

Q t

( )

J

0

Q

Q

1 0 0

0 1 1

1 Q t

( )

1

K

(b) Truth table (c) Graphical symbol

Q

( )

Last time Last time

33

M C ll Memory Cell

SR Latch

Problems of SR Latches Problems of SR Latches

Glitch problems

Transparent output - the memory elements outputs immediately

change in response to input changes change in response to input changes

Gated SR Latches (Enable signal or clock)

Another problems

Forbidden state and racing problem D-latches, JK-latches g p ,

When cascading latches

How to stop changes from racing through chain?

Mater slave F/Fs and Edge triggered F/Fs (clock signal)

Memory elements change their states in response to a clock signal

We call these Synchronous systems

Today Today

34

Timing Methodologies

To guarantee the correct operation when cascading the

M bl k Memory blocks

Comparison of Latches and F/Fs

Registers store multiple bits

Storage registers

Shift registers

Counters count events

Asynchronous counters

Synchronous counters

Timing Methodologies Timing Methodologies

35

Set of rules for interconnecting components and clocks

When followed, guarantee proper operation of system

Proper operation:

(1) The correct inputs, with respect to time, are provided to the FFs

(2) no FF changes more than once per clocking event

Approach depends on building blocks used for memory elements Approach depends on building blocks used for memory elements

For systems with latches:

Narrow Width Clocking

Multiphase Clocking (e.g., Two Phase Non-Overlapping)

For systems with edge-triggered flip-flops:

Single Phase Clocking Single Phase Clocking

Definition of Terms

Clock:

Definition of Terms

36

Input

T

su

T

h

Periodic Event, causes state of memory

element to change

rising edge falling edge high level low level

Clock

Setup Time (Tsu)

rising edge, falling edge, high level, low level

Minimum time before the clocking event by

Clock

There is a timing

" window" around the

g y

which the input must be stable

Hold Time (Th)

clocking event

during which the input

must remain stable

and unchanged

Hold Time (Th)

Minimum time after the clocking event during

which the input must remain stable

and unchanged

in order

to be recognized

Setup and Hold times for Latches Setup and Hold times for Latches

37

t

su

t

h

Clk

D

Q

t

plh

t

phl

Comparison of latch and F/F Comparison of latch and F/F

38

Edge triggered device sample inputs on the event

7474

Edge triggered device sample inputs on the event

edge

Transparent latches sample inputs as long as the

l k i t d

D Q

Timing Diagram:

clock is asserted

Positive edge-triggered

flip-flop

Clk

7476

p p

D Q

D

Clk D Q

C

Clk

Clk

Q

7474

Bubble here

for negative

Level-sensitive

latch Q

7476

for negative

edge triggered

device

Behavior the same unless input changes

while the clock is high

Comparison of latches and F/Fs Comparison of latches and F/Fs

39

Input/Output Behavior of Latches and Flipflops Input/Output Behavior of Latches and Flipflops

Type When Inputs are Sampled When Outputs are Valid

unclocked always propagation delay from

latch input change latch input change

level clock high propagation delay from

sensitive (Tsu, Th around input change

latch falling clock edge)

positive edge clock lo-to-hi transition propagation delay from

flipflop (Tsu, Th around rising edge of clock flipflop (Tsu, Th around rising edge of clock

rising clock edge)

negative edge clock hi-to-lo transition propagation delay from

flipflop (Tsu Th around falling edge of clock flipflop (Tsu, Th around falling edge of clock

falling clock edge)

master/slave clock hi-to-lo transition propagation delay from

flipflop (Tsu, Th around falling edge of clock

falling clock edge)

Typical Timing Specifications:

Flipflops vs. Latches

40

74LS74 Positive

Edge Triggered

D Flipflop

T

su

20

T

h

5

T

su

20

T

h

5

Setup time

Hold time

D

ns ns

T

w

25

ns ns

Hold time

Minimum clock width

Propagation delays

(low to high, high to low,

d t i l)

Clk

ns

T

plh

25 ns

13 ns

T

phl

40 ns

25 ns

max and typical)

Q

13 ns 25 ns

All measurements are made from the clocking event

that is, the rising edge of the clock that is, the rising edge of the clock

Typical Timing Specifications:

Flipflops vs. Latches

41

74LS76 74LS76

Transparent

Latch

T

su

20

ns

T

h

5

ns

T

su

20

ns

T

h

5

ns

D

Setup time

Hold time

Minimum Clock Width

ns ns ns ns

T

w

20

ns

D

Clk

Propagation Delays:

high to low, low to high,

maximum, typical

data to output

ns

T

plh

C Q

27 ns

15

T

phl

C Q

25 ns

14

Clk

Q

data to output

clock to output

15 ns 14 ns

T

plh

D Q

27

T

phl

D Q

16

Measurements from falling clock edge

27 ns

15 ns

16 ns

7 ns

Measurements from falling clock edge

or rising or falling data edge

Timing Methodologies Timing Methodologies

42

IN Q0

Q1

Two F/Fs are cascaded

New value to first stage

IN Q0

Q1

D

C

Q

Q

D

C

Q

Q

New value to first stage

while second stage

obtains current value

of first stage Shift Register

CLK

100

Cascaded Flipflops and Setup/Hold/Propagation Delays

In

Q

0

100

Correct Operation,

i i i

0

Q

1

Clk

assuming positive

edge triggered FF

Cascaded Flipflops and

/ / Setup/Hold/Propagation Delays

43

Why this works: Why this works:

Propagation delays far exceed hold times;

Clock width constraint exceeds setup time

This guarantees following stage will latch current value

before it is replaced by new value

Assumes infinitely fast distribution of the clock Assumes infinitely fast distribution of the clock

Ti i t i t T

In

Timing constraints

guarantee proper

operation of

cascaded components

T

su

20 ns

T

T

su

20 ns

T

Q

0

p

T

plh

13 ns

T

plh

13 ns

Q

1

T

h

5 ns

T

h

5 ns

Clk

The Problem of Clock Skew The Problem of Clock Skew

44

Correct behavior assumes next state of all storage elements g

determined by all storage elements at the same time

Not possible in real systems!

logical clock driven from more than one physical circuit with logical clock driven from more than one physical circuit with

timing behavior

different wire delay to different points in the circuit

Effect of Skew on Cascaded Flipflops:

FF0 samples IN

FF1 samples Q

0

100

Effect of Skew on Cascaded Flipflops:

In

Q

0

Q

1

CLK2 is a delayed

version of CLK1

Q

1

Clk1

Clk2

Original State: Q0 = 1, Q1 = 1, In = 0

Because of skew, next state becomes: Q0 = 0, Q1 = 0, not Q0 = 0, Q1 = 1

Design Strategies for Minimizing

Clock Skew

45

Typical propagation delays for LS FFs: 13 ns

Need substantial clock delay (on the order of 13 ns) for skew to y ( )

be a problem in this relatively slow technology

Nevertheless, the following are good design practices:

distribute clock signals in general direction of data flows

wire carrying the clock between two communicating components wire carrying the clock between two communicating components

should be as short as possible

for multiphase clocked systems, distribute all clocks in similar

i th thi i i i th ibilit f l wire paths; this minimizes the possibility of overlap

for the non-overlap clock generate, use the phase feedback

signals from the furthest point in the circuit to which the clock g p

is distributed; this guarantees that the phase is seen as low

everywhere before it allows the next phase to go high

Choosing a Flipflop Choosing a Flipflop

46

R S Clocked Latch: R-S Clocked Latch:

used as storage element in narrow width clocked systems

its use is not recommended!

however, fundamental building block of other flipflop types

J-K Flipflop: (historically popular, but now not used)

versatile building block

can be used to implement D and T FFs

usually requires least amount of logic to implement usually requires least amount of logic to implement

but has two inputs with increased wiring complexity

because of 1's catching, never use master/slave J-K FFs

edge-triggered varieties exist

D Flipflop:

minimizes wires, much preferred in VLSI technologies

simplest design technique

best choice for storage registers best choice for storage registers

T Flipflops:

don't really exist, constructed from J-K FFs

usually best choice for implementing counters usually best choice for implementing counters

Preset and Clear inputs highly desirable!!

Registers Registers

47

Collection of Flip-Flops with similar controls

and logic

stored values somehow related

share clocks, reset, and set lines

i il l i t h t similar logic at each stage

Ex l Examples

storage registers

shift registers shift registers

counters

Storage Register Storage Register

48

Group of storage elements read/written as a unit

4-bit register constructed from 4 D FFs

Shared clock and clear lines

+

\clr

Q3 Shared clock and clear lines

Schematic Shape

D3

Q3

D

R

S

CLR

171

CLK

Q3

Q3

10

9

7

13

12

D2

Q2

D

R

S

Q1

CLR

D3

D2

Q1

Q2

Q2

11

5

6

7

4

3

2

1

D1

Q1

D

R

S

TTL 74171 Quad D type FF with Clear

D1

D0

Q0

Q0

4

14 15

1

D1

D0

Q0

D

R

S

TTL 74171 Quad D-type FF with Clear

(Small numbers represent pin #s on package)

clk

D

R

Kinds of Registers Kinds of Registers

49

Input/Output Variations Input/Output Variations

Selective Load Capability

Tri-state or Open Collector Outputs

True and Complementary Outputs

377

EN

CLK

1

11

H QH

374

11

18

19

CLK

D6

Q5

EN

Q6

Q7

D5

D7

1

14

17

18

12

15

16

19

G

F

E

D

QG

QF

QE

QD

8

13

14

17

9

12

15

16

D3

Q2

Q1

Q3

Q4

D2

D1

D4

4

7

8

13

5

6

9

12

C

B

A

Q

QC

QB

QA

OE

3

4

7

2

5

6

74377 Octal D-type FFs

with input enable

74374 Octal D-type FFs

with output enable

Q

Q0 D0

3 2

OE

1

p

EN enabled low and lo-to-hi

clock transition to load new

data into register

OE asserted low presents FF

state to output pins;

otherwise high impedence

A simple shift register A simple shift register

50

Q Q Q Q Out = In

t

0

t

1

1

0

0

1

0

0

0

0

0

0

Q

1

Q

2

Q

3

Q

4

Out = In

D Q D Q D Q D Q In Out

Q

1

Q

2

Q

3

Q

4

t

2

t

3

t

4

1

1

1

0

1

1

1

0

1

0

1

0

0

0

1

Q

Clock

Q Q Q

4

t

5

t

6

0

0

1

0

1

1

1

1

0

1

(a) Circuit

t

7

0 0 0 1 1

(b) A sample sequence

Parallel-access shift register

Parallel output

Parallel access shift register

51

Q

3

Q

2

Q

1

Q

0

Parallel output

D Q

Q

D Q

Q

D Q

Q

D Q

Q

Clock

Parallel input

Shift/Load

Serial

input

Shift Register I/O

S i l P ll l I t

Shift Register I/O

52

Serial vs. Parallel Inputs

Serial vs. Parallel Outputs

Shift Direction: Left vs. Right

Serial Inputs: LSI, RSI

Parallel Inputs: D, C, B, A

Parallel Outputs: QD, QC, QB, QA

Clear Signal Clear Signal

Positive Edge Triggered Devices

S1,S0 determine the shift function

S1 = 1 S0 = 1: Load on rising clk edge

10

9

7

6

12

S1

S0

LSI

S1 = 1, S0 = 1: Load on rising clk edge

synchronous load

S1 = 1, S0 = 0: shift left on rising clk edge

LSI replaces element D

6

5

4

3

2

12

15

14

13

194

D

C

B

A

RSI

S1 = 0, S0 = 1: shift right on rising clk edge

RSI replaces element A

S1 = 0, S0 = 0: hold state

2

11

1

RSI

CLK

CLR

74194 4-bit Universal

Shift Register

Multiplexing logic on input to each FF!

Shift ll it d f i l t ll l i Shifters well suited for serial-to-parallel conversions,

such as terminal to computer communications

Shift Register Application: Parallel to

Serial Conversion

53

D7

Sender

Receiver

D7

10

9

7

6

12

S1

S0

LSI

D

10

9

7

6

12

S1

S0

LSI

D7

D6

D5

D4

D7

D6

D5

D4

Clock

6

5

4

3

2

11

12

15

14

13

194

D

C

B

A

RSI

CLK

6

5

4

3

2

11

12

15

14

13

194

D

C

B

A

RSI

CLK

Parallel

Inputs

Parallel

Outputs

10

9

7

S1

S0

1

CLK

CLR

1

CLK

CLR

10

9

7

S1

S0

D3

D2

D1

D0

D3

D2

D1

D0

7

6

5

4

3

2

12

15

14

13

194

S0

LSI

D

C

B

A

RSI

7

6

5

4

3

2

12

15

14

13

194

S0

LSI

D

C

B

A

RSI

2

11

1

RSI

CLK

CLR

2

11

1

RSI

CLK

CLR

Serial

transmission

Counters Counters

54

Counters

Proceed through a well-defined sequence of states in response to

count signal count signal

3 Bit Up-counter: 000, 001, 010, 011, 100, 101, 110, 111, 000, ...

3 Bit Down-counter: 111, 110, 101, 100, 011, 010, 001, 000, 111, ...

Binary vs. BCD vs. Gray Code Counters

A counter is a " degenerate" finite state machine/sequential circuit

where the state is the only output

Types of counters

Asynchronous vs. Synchronous Counters Asynchronous vs. Synchronous Counters

Asynchronous counters Asynchronous counters

55

T Q T Q T Q 1

Ripple counter

Q

Clock

Q Q

Q

0

Q

1

Q

2

State transitions are not sharp!

Q

0

Q

1

Q

2

(a) Circuit

Can lead to "spiked outputs" from

combinational logic

decoding the counter's state

Clock

Q

0

Q

1

Q

2

Count 0 1 2 3 4 5 6 7 0

(b) Timing diagram

A three-bit up-counter

Asynchronous counters contd Asynchronous counters, cont d

56

T Q

Q

Cl k

T Q

Q

T Q

Q

1

Q

Clock

Q Q

Q

0

Q

1

Q

2

A three-bit down-counter

(a) Circuit

Clock Clock

Q

0

Q

1

Q

2

Count 0 7 6 5 4 3 2 1 0

(b) Timing diagram

Synchronous counter Synchronous counter

57

A h Asynchronous counters

simple, but not very fast

can build faster counters by clocking all FFs at the same

Clock cycle Q

2

Q

1

Q

0

can build faster counters by clocking all FFs at the same

time synchronous counter

0

0

1

0

1

0

0

1

2

0

0

0

Q

1

changes

Q

2

changes

Synchronous counters

with T F/ F

1

1

0

1

2

3

0

0

0

1

4

5

0

0

1

1

T

0

=1

T

1

=Q

0

T =Q Q

0

1

1

0

5

6

1 1 7

1

1

1

T

2

=Q

0

Q

1

0 0 8 0

A four-bit synchronous up-counter A four bit synchronous up counter

58

T Q

Q

Clock

T Q

Q

T Q

Q

1

Q

0

Q

1

Q

2

T Q

Q

Q

3

(a) Circuit

Clock

Q

0

Q

1

Q

2

Q

3

Count 0 1 2 3 5 9 12 14 0

(b) Timing diagram

4 6 8 7 10 11 13 15 1

Enable and Clear capability Enable and Clear capability

59

T Q

Q Clock

T Q

Q

Enable T Q

Q

T Q

Q

Clear

A four-bit counter with D FFs A four bit counter with D FFs

60

Enable

D Q

Q

Q

0

D Q

Q

1

Q

D Q

Q

Q

2

D Q

Q

Q

3

Clock

Q

Output

carry

A counter with parallel-load

capability

61

Enable

D Q

Q

Q

0

D

0

0

1

D Q Q

1

D

1

0

1

Q

D Q

Q

Q

2

D

2

0

1

D Q

Q

Q

3

D

3

0

1

Q

Load

Clock

Output

carry

Catalog Counter Catalog Counter

62

Synchronous Load and Clear Inputs

Positive Edge Triggered FFs

163

RCO

P

T

CLK

2

7

10

15

Parallel Load Data from D, C, B, A

P, T Enable Inputs: both must be asserted to

QA

QB

QC

QD

A

B

C

D

3

4

5

6

14

12

11

13

p

enable counting

RCO: asserted when counter enters its highest

state 1111 used for cascading counters

QA A

LOAD

CLR

9

1

3 14

74163 Synchronous

4-Bit Upcounter

state 1111, used for cascading counters

" Ripple Carry Output"

74161: similar in function, asynchronous load and reset

74163 Detailed Timing Diagram 74163 Detailed Timing Diagram

63

CLR

A

LOAD

CLR

B

C

D

CLK

D

P

T

Q

A

QQ

B

Q

C

Q

D

RCO

12 13 14 15 0 1 2

Clear Load Count Inhibit

A modulo-6 counter with

synchronous reset

64

Enable

Q

0

D

0

1

0

0

Q

1

Q

2

0

D

1

D

2

Load

Clock

0

0

Clock

Clock

(a) Circuit

Clock

Q

00

Q

1

Q

2

0 1 2 3 4 5 0 1 Count

2

(b) Timing diagram

A modulo-6 counter with

asynchronous reset

65

T Q T Q T Q 1

Q

0

Q

1

Q

2

Q

Clock

Q Q

(a) Circuit

Clock

Q

0

Q

1

Q

22

Count

(b) Timing diagram

0 1 2 3 4 5 0 1 2

Other types of counters Other types of counters

66

Two-digit BCD counters

Two modulo-10 counters, one for each digit

Reset when the counter reaches 9

Ring counters

One bit is one while other bits are 0

one hot encoding

J h t Johnson counter

1000, 1100, 1110, 1111, 0111, 0011, 0001, 0000,

A two-digit BCD counter

E bl

1

A two digit BCD counter

67

Enable

Q

0

Q

1

Q

2

D

0

D

1

D

2

1

0

0

0

BCD

0

Q

2 2

Load

Clock

Q

3

0 D

3

Clock

Clock

Enable Clear Enable

Q

0

Q

1

Q

2

D

0

D

1

D

2

0

0

0

BCD

1

Clear

Load

Clock

Q

3

0 D

3

Ring Counter Ring Counter

68

Q

0

Q

1

Q

1 ?

D Q D Q D Q

Start

Q

0

Q

1

Q

n 1 ?

Q

Clock

Q Q

Q

0

Q

1

Q

2

Q

3

(a) An n -bit ring counter

Q

0

w

0

En

y

0

w

1

y

1

y

2

y

3

Q

1

Q

2

Q

3

2-to-4 decoder

Clock

1

Q

1

Q

0

Clock

Start

Two-bit up-counter

Clear

(b) A four-bit ring counter

Johnson counter Johnson counter

69

Q

0

Q

1

Q

n 1

D Q D Q D Q D Q

Q

D Q

Q

D Q

Q

Clock

Reset

You might also like

- BS EN 50365 - 2002 Insulating HelmetsDocument18 pagesBS EN 50365 - 2002 Insulating HelmetsmetropodikasNo ratings yet

- Adm4001 - UnderWorld - An Adventure Game of Subterranean Fantasy (Oef)Document158 pagesAdm4001 - UnderWorld - An Adventure Game of Subterranean Fantasy (Oef)Mike Kovacs100% (2)

- TTTTT Eeee AsDocument20 pagesTTTTT Eeee AsEric GongNo ratings yet

- Role of AI in RetailDocument46 pagesRole of AI in RetailpavanNo ratings yet

- Sequential Circuits: Presented By: Group 3Document30 pagesSequential Circuits: Presented By: Group 3Jalaj SrivastavaNo ratings yet

- 05 SeqDocument46 pages05 SeqRenju TjNo ratings yet

- cs1104 11Document32 pagescs1104 11N Sandeep KumarNo ratings yet

- FlipflopsDocument80 pagesFlipflopsvikramkolanuNo ratings yet

- Flip Flop Mealy and Moore ModelDocument25 pagesFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- CS1104 - Computer Organization: Aaron Tan Tuck ChoyDocument30 pagesCS1104 - Computer Organization: Aaron Tan Tuck ChoyTaye ToluNo ratings yet

- Sequential Logic - Flip-Flops: 6.1 SR LatchDocument5 pagesSequential Logic - Flip-Flops: 6.1 SR Latchanon020202No ratings yet

- Unit 5 DLDDocument189 pagesUnit 5 DLDGuru VelmathiNo ratings yet

- ELE2120 Digital Circuits and Systems: Tutorial Note 7Document19 pagesELE2120 Digital Circuits and Systems: Tutorial Note 7Harold Wilson100% (1)

- FF and LDocument30 pagesFF and LRaja BenitaNo ratings yet

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDocument6 pagesChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011No ratings yet

- Digital Design On Digital Works.Document25 pagesDigital Design On Digital Works.nileshchaurasiaNo ratings yet

- COE211 CH5 Part1Document30 pagesCOE211 CH5 Part1hm100hm100hm100No ratings yet

- Flip-Flop LabDocument7 pagesFlip-Flop Labjose mirandaNo ratings yet

- Chapter3-Sequential Circuits PDFDocument10 pagesChapter3-Sequential Circuits PDFAshu1803No ratings yet

- Sequential Circuits: Digital ElectronicsDocument10 pagesSequential Circuits: Digital ElectronicsAshu1803No ratings yet

- Chp1 - Latches and Flip-FlopsDocument44 pagesChp1 - Latches and Flip-FlopsAbnen OngNo ratings yet

- CounterDocument22 pagesCounterMahesh MahiNo ratings yet

- Synchronous Sequential Ckts by Lakshmi NarayanaDocument30 pagesSynchronous Sequential Ckts by Lakshmi NarayanaMurali Krishna100% (1)

- UntitledDocument8 pagesUntitledlalita chauhanNo ratings yet

- Sequential Circuit: Shreyas Patel M.Tech VLSI Design (VIT, Vellore) SVNIT, SuratDocument21 pagesSequential Circuit: Shreyas Patel M.Tech VLSI Design (VIT, Vellore) SVNIT, SuratMudit SandNo ratings yet

- Topic 2 - Subtopic 2.3Document31 pagesTopic 2 - Subtopic 2.3Navinaash Chanthra SegaranNo ratings yet

- Sequential LogicDocument139 pagesSequential Logicmdhuq1100% (1)

- Flip FlopsDocument25 pagesFlip FlopsNagul MeeraNo ratings yet

- Latch and Flip-FlopDocument58 pagesLatch and Flip-FlopDalila Nadia RazaliNo ratings yet

- Flip FlopsDocument60 pagesFlip FlopsA10-14Rajat KumarNo ratings yet

- Notes 326 Set8Document16 pagesNotes 326 Set8Bakshi AmitNo ratings yet

- Chapter 6 - Introduction To Sequential DevicesDocument62 pagesChapter 6 - Introduction To Sequential DevicesSarath Chandra SNo ratings yet

- Synchronous: Sequential LogicDocument67 pagesSynchronous: Sequential LogickenNo ratings yet

- Enel3de IntrosequentialcircuitsDocument49 pagesEnel3de IntrosequentialcircuitsZamani MhlongoNo ratings yet

- Sequential CircuitsDocument8 pagesSequential Circuits망토No ratings yet

- Combinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)Document16 pagesCombinational Circuits: ALU: AND OR ADD SUB SLT Zero (A B)anbaneNo ratings yet

- 6 111 l4 Seqntl BlocksDocument24 pages6 111 l4 Seqntl BlocksysakeunNo ratings yet

- 06 - DFC10093 (Subchapter 2.3)Document23 pages06 - DFC10093 (Subchapter 2.3)Navinaash Chanthra SegaranNo ratings yet

- 6 RegistersDocument24 pages6 RegistersPiyooshTripathiNo ratings yet

- 10 - Sequential CircuitDocument32 pages10 - Sequential CircuitJose Mari Emmanuel MedinaNo ratings yet

- Flip FlopsDocument22 pagesFlip FlopsSrinika ReddyNo ratings yet

- Flip FlopsDocument28 pagesFlip FlopssreekarscribdNo ratings yet

- Synchronous Sequential LogicDocument69 pagesSynchronous Sequential Logic魏延任No ratings yet

- Flip Flops in Sequential CircuitsDocument9 pagesFlip Flops in Sequential Circuitsarpanrin2No ratings yet

- DTE Question Bank SolutionDocument15 pagesDTE Question Bank SolutionkhantaukirhasanNo ratings yet

- Types of Flip-Flops: Electronics Computing Digital Circuit Bit Memory Input Clock Output ComplementDocument4 pagesTypes of Flip-Flops: Electronics Computing Digital Circuit Bit Memory Input Clock Output ComplementVikas KumarNo ratings yet

- Flip-Flops: Revision of Lecture Notes Written by Dr. Timothy DrysdaleDocument35 pagesFlip-Flops: Revision of Lecture Notes Written by Dr. Timothy DrysdaleKaustav MitraNo ratings yet

- Flip FlopsDocument29 pagesFlip FlopsShweta RoyNo ratings yet

- Flip-Flops & Latches: Digital ElectronicsDocument20 pagesFlip-Flops & Latches: Digital ElectronicsGowtham PalanirajanNo ratings yet

- Computer Architecture 1Document39 pagesComputer Architecture 1ARAFAT GaamanNo ratings yet

- Module 4 - Seq Circuits 1Document55 pagesModule 4 - Seq Circuits 1Nithish KannaaNo ratings yet

- ELE2120 Digital Circuits and Systems: Tutorial Note 8Document28 pagesELE2120 Digital Circuits and Systems: Tutorial Note 8SidhanNo ratings yet

- Siddhi - E23cseu2200 - Assignment 8Document7 pagesSiddhi - E23cseu2200 - Assignment 8chipichipichapachapa2121No ratings yet

- Digital Design ExamplesDocument29 pagesDigital Design ExampleshumnaharoonNo ratings yet

- GATE+ISRO DIGITAL LOGIC AND COMPUTER ORGANIZATION 2015 - Sequential CircuitsDocument35 pagesGATE+ISRO DIGITAL LOGIC AND COMPUTER ORGANIZATION 2015 - Sequential CircuitsRejinRajanNo ratings yet

- L4: Sequential Building Blocks (Flip - Flops, Latches and Registers)Document24 pagesL4: Sequential Building Blocks (Flip - Flops, Latches and Registers)ggk87No ratings yet

- Flipflops: Technical Seminar ReportDocument16 pagesFlipflops: Technical Seminar ReportrachitNo ratings yet

- Chapter-6: Sequential Logic Circuit (Latches, Flip-Flop and Counter)Document56 pagesChapter-6: Sequential Logic Circuit (Latches, Flip-Flop and Counter)Bonsa100% (1)

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Fundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsFrom EverandFundamentals of Electronics 3: Discrete-time Signals and Systems, and Quantized Level SystemsNo ratings yet

- Implementation Implementation Technology: (PART 2)Document45 pagesImplementation Implementation Technology: (PART 2)katral-jamerson-9379No ratings yet

- Chapter 2: Introduction To Logic Circuits: 2009 Spring CS211 Digital Systems & LabDocument45 pagesChapter 2: Introduction To Logic Circuits: 2009 Spring CS211 Digital Systems & Labkatral-jamerson-9379No ratings yet

- Title The Title of This Project Is International Human ResourcesDocument8 pagesTitle The Title of This Project Is International Human Resourceskatral-jamerson-9379No ratings yet

- Worksheets: Excel Allows To Have Many Worksheets in A Same File. This Facility AllowsDocument3 pagesWorksheets: Excel Allows To Have Many Worksheets in A Same File. This Facility Allowskatral-jamerson-9379No ratings yet

- Proclimb Procross Torsional Conversion KitDocument8 pagesProclimb Procross Torsional Conversion KitcpcracingNo ratings yet

- Diagramas Eléctricos NISSAN XTERRA 2WD V6-4.0L (VQ40DE) 2007Document64 pagesDiagramas Eléctricos NISSAN XTERRA 2WD V6-4.0L (VQ40DE) 2007Héctor GutiérrezNo ratings yet

- SAAMI Z299.5 Abusive Mishandling Approved 3 14 2016Document12 pagesSAAMI Z299.5 Abusive Mishandling Approved 3 14 2016Gil CarvalhoNo ratings yet

- Buyers Guide 19 127065Document149 pagesBuyers Guide 19 127065p.viala.kNo ratings yet

- Kunjaw Medika Adijaya 2021Document35 pagesKunjaw Medika Adijaya 2021NahmaKids100% (1)

- Diploma in Cybersecurity Specialist Co-OpDocument2 pagesDiploma in Cybersecurity Specialist Co-OpFaraz FaiziNo ratings yet

- YOLO-LITE: A Real-Time Object Detection Algorithm Optimized For Non-GPU ComputersDocument8 pagesYOLO-LITE: A Real-Time Object Detection Algorithm Optimized For Non-GPU ComputersDeepak Kumar SinghNo ratings yet

- 190 Service Manual - Aspire 1450Document107 pages190 Service Manual - Aspire 1450Soporte Tecnico Buenos AiresNo ratings yet

- 25 (G.R. No. 213207. February 15, 2022)Document43 pages25 (G.R. No. 213207. February 15, 2022)faith.dungca02No ratings yet

- Chapter 1 PDFDocument2 pagesChapter 1 PDFAizenNo ratings yet

- Case Rohaya & Yusuf IbrahimsDocument13 pagesCase Rohaya & Yusuf IbrahimsIqram MeonNo ratings yet

- Notificatio of Designated Officers and Local AreasDocument12 pagesNotificatio of Designated Officers and Local AreasKiran RaviNo ratings yet

- (Northern Samar Colleges, Inc.: NAME: George M. Bendanillo CELLPHONE#: 09068927203 Surname A-JDocument4 pages(Northern Samar Colleges, Inc.: NAME: George M. Bendanillo CELLPHONE#: 09068927203 Surname A-JジョージNo ratings yet

- GEO140-1 Field Geology - OrientationDocument10 pagesGEO140-1 Field Geology - Orientationluke buetaNo ratings yet

- The National Insurance Board Funeral Grant Application NI8: (Please Use Capitals Letters)Document4 pagesThe National Insurance Board Funeral Grant Application NI8: (Please Use Capitals Letters)Allison Nadine MarchandNo ratings yet

- Sensitivity AnalysisDocument10 pagesSensitivity AnalysisMORSHEDNo ratings yet

- Rasmol AssignmentDocument3 pagesRasmol Assignmentalem010No ratings yet

- Defining Your Idea, Product, And/Or Service (1) : Osong Fabrice MakiaDocument1 pageDefining Your Idea, Product, And/Or Service (1) : Osong Fabrice Makiangoufor atemafacNo ratings yet

- Happiness Rats (STUDENT)Document2 pagesHappiness Rats (STUDENT)bieliqpl112No ratings yet

- Zone2 CSR Rates PunjabDocument251 pagesZone2 CSR Rates Punjabgreatwellwisher100% (1)

- Public Law 625: The Women's Armed Services Integration Act of 1948Document2 pagesPublic Law 625: The Women's Armed Services Integration Act of 1948asolis23No ratings yet

- Comparative Study of Public and Private Telecom Wireless Services in IndiaDocument4 pagesComparative Study of Public and Private Telecom Wireless Services in Indiajonny bravoNo ratings yet

- Business Idea Contest OverviewDocument2 pagesBusiness Idea Contest OverviewBryan MendozaNo ratings yet

- Step by Step GuideDocument5 pagesStep by Step GuideSourav SahaNo ratings yet

- AMBA AHB Bus Protocol Checker With Efficient Debugging MechanismDocument4 pagesAMBA AHB Bus Protocol Checker With Efficient Debugging MechanismClaudia FountaineNo ratings yet

- Proposed Blended Learning Model For Don Mariano Marcos Memorial State University - South La Union Campus (Dmmmsu-Sluc)Document8 pagesProposed Blended Learning Model For Don Mariano Marcos Memorial State University - South La Union Campus (Dmmmsu-Sluc)Jose JarlathNo ratings yet

- Water Supply and Sanitation Final ExamDocument9 pagesWater Supply and Sanitation Final ExamTILAYEYIDEG50% (2)