Professional Documents

Culture Documents

Module Butterfly: # (Parameter, Parameter ) (Input CLK, Input RST - N

Module Butterfly: # (Parameter, Parameter ) (Input CLK, Input RST - N

Uploaded by

AbhaySharma0 ratings0% found this document useful (0 votes)

8 views4 pagesverilog

Original Title

Butterfly V

Copyright

© © All Rights Reserved

Available Formats

DOC, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentverilog

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

0 ratings0% found this document useful (0 votes)

8 views4 pagesModule Butterfly: # (Parameter, Parameter ) (Input CLK, Input RST - N

Module Butterfly: # (Parameter, Parameter ) (Input CLK, Input RST - N

Uploaded by

AbhaySharmaverilog

Copyright:

© All Rights Reserved

Available Formats

Download as DOC, PDF, TXT or read online from Scribd

Download as doc, pdf, or txt

You are on page 1of 4

// Copyright (c) 2012 Ben Reynwar

// Released under MIT License (see LIC!"#t$t)

/%

I&ple&ents a 'utter(y &odule )or a **T#

Ta+es co&ple$ nu&'ers ,- ./- .B and returns

0/ 1 ./ 2 ,%.B

0B 1 ./ 3 ,%.B

It can ta+e input no &ore )re4uently than once e5ery

two steps# This is so- hope)ully- less &ultiply

'loc+s can 'e used#

%/

module butterfy

#(

// The width o) &6in#

parameter M_WDTH = 0,

// The width o) the input- output and twiddle )actors#

parameter X_WDTH = 0

)

(

input wire clk,

input wire rst_n,

// &6in contains data that passes through this 'loc+ with no change#

// It is delayed )or 7 counts li+e $6nd38y6nd#

input wire [M_WDTH-1:0] m_in,

// The twiddle )actor#

input wire signed [2*X_WDTH-1:0] ,

// ./

input wire signed [2*X_WDTH-1:0] !",

// .B

input wire signed [2*X_WDTH-1:0] !b,

// "et to 1 when new data is present on inputs#

// Cannot 'e set to 1 )or two consecuti5e steps#

input wire !_n#,

// delayed 5ersion o) &6in#

output reg [M_WDTH-1:0] m_$ut,

// 0/ 1 ./ 2 ,%.B

// 0B 1 ./ 3 ,%.B

// ,hen y6nd11 y6re and y6i& are outputing 0/#

// The step a)ter they are outputting 0B#

output wire signed [2*X_WDTH-1:0] y,

output reg y_n#

)%

// "et wire to the real and i&ag parts )or con5enience#

wire signed [X_WDTH-1:0] _re%

wire signed [X_WDTH-1:0] _im%

assign _re = [2*X_WDTH-1:X_WDTH]%

assign _im = [X_WDTH-1:0]%

wire signed [X_WDTH-1:0] !"_re%

wire signed [X_WDTH-1:0] !"_im%

assign !"_re = !"[2*X_WDTH-1:X_WDTH]%

assign !"_im = !"[X_WDTH-1:0]%

wire signed [X_WDTH-1:0] !b_re%

wire signed [X_WDTH-1:0] !b_im%

assign !b_re = !b[2*X_WDTH-1:X_WDTH]%

assign !b_im = !b[X_WDTH-1:0]%

reg signed [X_WDTH-1: 0] y_re%

reg signed [X_WDTH-1: 0] y_im%

assign y = &y_re, y_im'%

// 9elayed &6in#

reg signed [M_WDTH-1:0] m[1:0]%

// 9elayed ./

reg signed [X_WDTH-1:0] ("_re[1:0]%

reg signed [X_WDTH-1:0] ("_im[1:0]%

// 9elayed .B

reg signed [X_WDTH-1:0] (b_re%

reg signed [X_WDTH-1:0] (b_im%

// 9elayed ,

reg signed [X_WDTH-1:0] _re%

reg signed [X_WDTH-1:0] _im%

// 9elayed $6nd

reg signed !_n#_$l#[2:0]%

// "torage )or output o) &ultipliers

reg signed [2*X_WDTH-1:0] (b_m1%

reg signed [2*X_WDTH-1:0] (b_m2%

// , % .B

reg signed [X_WDTH-1:0] (b_re%

wire signed [X_WDTH-1:0] (b_im%

assign (b_im = ((b_m1 >>> (X_WDTH-2)) + ((b_m2 >>> (X_WDTH-2))%

reg signed [X_WDTH-1:0] (b_im_$l#%

// ,ire o) longer length )or adding or su'stracting ,%.B to ./#

// I) we don:t create longer wires )or the& then we can lose the

// high 'it# The contents o) these wires are downshi)ted into a

// nor&al si;e )or use#

wire signed [X_WDTH)0] (1_re_bi*%

wire signed [X_WDTH)0] (1_im_bi*%

assign (1_re_bi* = ("_re[0] + (b_re%

assign (1_im_bi* = ("_im[0] + (b_im%

wire signed [X_WDTH)0] (2_re_bi*%

wire signed [X_WDTH)0] (2_im_bi*%

assign (2_re_bi* = ("_re[1] - (b_re%

assign (2_im_bi* = ("_im[1] - (b_im_$l#%

always + (posedge clk or negedge rst_n)

begin

if (!rst_n)

begin

y_n# <= 1,b0%

end

else

begin

// "et delay )or $6nd6old and &#

!_n#_$l#[0] <= !_n#%

!_n#_$l#[1] <= !_n#_$l#[0]%

!_n#_$l#[2] <= !_n#_$l#[1]%

m[0] <= m_in%

m[1] <= m[0]%

m_$ut <= m[1]%

// "T/< 1

if (!_n#)

begin

("_re[0] <= !"_re%

("_im[0] <= !"_im%

_re <= _re%

_im <= _im%

(b_re <= !b_re%

(b_im <= !b_im%

// ,e per)or& two &ultiplications )or calculate the real part

// o) ,%.B#

(b_m1 <= !b_re*_re%

(b_m2 <= !b_im*_im%

if (!_n#_$l#[0])

-#is.l"y(/01121) 34 *$t ne #"t" t$ ste.s in " r$5/)%

end

if (!_n#_$l#[0])

// "T/< 2

begin

// !ow start the &ultiplications )or the i&ag part o) ,%,B#

(b_m1 <= (b_re*_im%

(b_m2 <= (b_im*_re%

// 9ownshi)t the &ultiplied results into nor&al width and

// su'stract the&#

// =5er(ow is not possi'le upon su'straction since we

// +now that , and .B 'oth ha5e &agnitude less than 1

// so their &ultiple &ust also#

(b_re <= ((b_m1 >>> (X_WDTH-2)) - ((b_m2 >>> (X_WDTH-2))%

end

// "T/< 7

if (!_n#_$l#[1])

begin

// ,e only need to shi)t the re4uired delayed data

// with ./ e5ery two steps since new input cannot

// arri5e &ore )re4uently than that#

// ./ is needed 'y a wire calculating ;26re6'ig and ;e6i&6'ig

// ne$t step#

("_re[1] <= ("_re[0]%

("_im[1] <= ("_im[0]%

// =utput 0/#

y_n# <= 1,b1%

y_re <= (1_re_bi* >>> 1%

y_im <= (1_im_bi* >>> 1%

(b_im_$l# <= (b_im%

end

// "T/< >

if (!_n#_$l#[2])

begin

// =utput 0B#

y_n# <= 1,b0%

y_re <= (2_re_bi* >>> 1%

y_im <= (2_im_bi* >>> 1%

end

end

end

endmodule

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5822)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Chapter 10 DC Machine Part 3Document31 pagesChapter 10 DC Machine Part 3Shobanraj LetchumananNo ratings yet

- Written Exam Questions Anglo Eastern 3Document17 pagesWritten Exam Questions Anglo Eastern 3SiRf Pyaar HaiNo ratings yet

- Erbe Service Manual Icc200 Icc300h-E Icc350Document266 pagesErbe Service Manual Icc200 Icc300h-E Icc350tonybimbo73% (15)

- Vertical Roller Mill SummaryDocument20 pagesVertical Roller Mill SummaryPhyo Thura Htay100% (3)

- Aspen Planning and Scheduling SeminarDocument49 pagesAspen Planning and Scheduling SeminarGoutam Giri100% (2)

- Jack JK-6380 PDFDocument21 pagesJack JK-6380 PDFRolando Gonzalez SibajaNo ratings yet

- Chapter 2Document51 pagesChapter 2AbhaySharmaNo ratings yet

- State and Verify Demorgan's Theorem Using NAND Gates OnlyDocument1 pageState and Verify Demorgan's Theorem Using NAND Gates OnlyAbhaySharmaNo ratings yet

- Serial No Name Photo Short Name Estd. City/Town State/UT WebsiteDocument4 pagesSerial No Name Photo Short Name Estd. City/Town State/UT WebsiteAbhaySharmaNo ratings yet

- Assignment Sheet-1: VLSI Technology and Design UNIT-2Document1 pageAssignment Sheet-1: VLSI Technology and Design UNIT-2AbhaySharmaNo ratings yet

- List If NITsDocument2 pagesList If NITsAbhaySharmaNo ratings yet

- Experiment 21: Design and Simulate 3-Bit Gray Counter Using Verilog HDLDocument3 pagesExperiment 21: Design and Simulate 3-Bit Gray Counter Using Verilog HDLAbhaySharmaNo ratings yet

- TVSS Asco Power Serie 400Document2 pagesTVSS Asco Power Serie 400rcam37170No ratings yet

- Excavation and TimberingDocument22 pagesExcavation and TimberingGanga DahalNo ratings yet

- FHD 821 E4Document4 pagesFHD 821 E4Mario UrsuNo ratings yet

- Employee Welfare Facilities Project ReportDocument119 pagesEmployee Welfare Facilities Project ReportBabasab Patil (Karrisatte)100% (2)

- A2Z On Global WarmingDocument162 pagesA2Z On Global WarmingDavid GoldingNo ratings yet

- EngineeringDocument3 pagesEngineeringanand shrigondekarNo ratings yet

- Naive Bayes Spam ClassifierDocument44 pagesNaive Bayes Spam ClassifierGudGud Tan0% (1)

- False Ceiling PDFDocument2 pagesFalse Ceiling PDFSteve50% (2)

- GEMS Block Modelling LABSDocument70 pagesGEMS Block Modelling LABSAl Pach100% (1)

- Manheim - Post-Sale Results - 062316Document12 pagesManheim - Post-Sale Results - 062316carlosogunNo ratings yet

- Utar Sose2014 YhseowDocument36 pagesUtar Sose2014 YhseowSeow Yoke HockNo ratings yet

- Smartcon 4000Document20 pagesSmartcon 4000செல்வமாரியப்பன் சீனிவாசன்No ratings yet

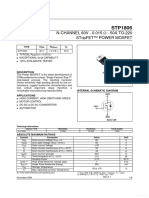

- STP 1806Document9 pagesSTP 1806David OweiNo ratings yet

- WorldQuant University CatalogDocument40 pagesWorldQuant University CatalogImam slaouiNo ratings yet

- Smisen Specs SCPL - 23-24 - SPC - PEPL - LCF - 01Document3 pagesSmisen Specs SCPL - 23-24 - SPC - PEPL - LCF - 01Glen CarterNo ratings yet

- Logic Gates in PneumaticsDocument20 pagesLogic Gates in PneumaticsManideep AlluNo ratings yet

- FactoryTalk View SE Network Station Architecture ConsiderationsDocument6 pagesFactoryTalk View SE Network Station Architecture Considerations1meander23No ratings yet

- Ms Word MCQDocument19 pagesMs Word MCQUsman Ubair50% (2)

- An Introduction To Well Control Calculations For Drilling OperationsDocument7 pagesAn Introduction To Well Control Calculations For Drilling OperationsEleonora LetorNo ratings yet

- LPPT 25-2019Document68 pagesLPPT 25-2019Tweed3ANo ratings yet

- 3760 LT LPG Domestic TankDocument5 pages3760 LT LPG Domestic TankDaniel Edward Omondi100% (1)

- Supplier ChartsDocument14 pagesSupplier ChartsMuhammad BilalNo ratings yet

- 005056AE19D41EE99CC433064FA74A07Document1 page005056AE19D41EE99CC433064FA74A07Jan Reoven SialanaNo ratings yet

- DKM (RA Training) PDFDocument114 pagesDKM (RA Training) PDFTMZNo ratings yet