Professional Documents

Culture Documents

Datasheet of FAN7554

Datasheet of FAN7554

Uploaded by

AnowarSadatCopyright:

Available Formats

You might also like

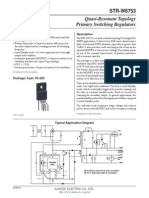

- Data Visualization in Tableau - Car Insurance Claim ProjectDocument51 pagesData Visualization in Tableau - Car Insurance Claim ProjectTunde Asaaju50% (2)

- Irazu EULA AgreementDocument7 pagesIrazu EULA AgreementLiqiang HeNo ratings yet

- AN7554Document22 pagesAN7554Corban MihaiNo ratings yet

- FAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorDocument17 pagesFAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorVijay MistryNo ratings yet

- DM 0565 RDocument20 pagesDM 0565 R81968No ratings yet

- 60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsDocument14 pages60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsIBSDIALLO0% (1)

- 1M0365RDocument11 pages1M0365RAndro DackNo ratings yet

- CM6800GIPDocument18 pagesCM6800GIPAndré Frota PaivaNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- Green Current Mode PWM Controller: Features DescriptionDocument12 pagesGreen Current Mode PWM Controller: Features Descriptionceny123No ratings yet

- STR W6735Document14 pagesSTR W6735proctepNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- FSDH0165Document9 pagesFSDH0165Giovanni Carrillo VillegasNo ratings yet

- LM 2587 DatasheetDocument26 pagesLM 2587 DatasheetAnonymous vKD3FG6RkNo ratings yet

- SSC2001S Application NoteDocument18 pagesSSC2001S Application NoteGerardo Mendez CamarilloNo ratings yet

- Fs6s1265re PDFDocument11 pagesFs6s1265re PDFHelton AmorimNo ratings yet

- Inverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterDocument9 pagesInverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterFurqan MemonNo ratings yet

- KA1H0165RDocument12 pagesKA1H0165RJtzabalaNo ratings yet

- Fan 7313Document11 pagesFan 7313KathafiNo ratings yet

- Viper 53Document24 pagesViper 53Cadena CesarNo ratings yet

- 5 M 0965 QT UDocument12 pages5 M 0965 QT UcesarlcaNo ratings yet

- STR W6735 DatasheetDocument13 pagesSTR W6735 DatasheetloagerNo ratings yet

- STR W6753 DatasheetDocument8 pagesSTR W6753 DatasheetjgerabmNo ratings yet

- L4949Document11 pagesL4949Николай КръстевNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- LM350 DatasheetDocument12 pagesLM350 DatasheetOmarVelasquezC.No ratings yet

- 161 20551 0 FS7M0880Document16 pages161 20551 0 FS7M0880Edwin Vitovis TorresNo ratings yet

- 7 M 0880Document18 pages7 M 0880Mahmoued YasinNo ratings yet

- Regulating Pulse Width Modulators: Features DescriptionDocument7 pagesRegulating Pulse Width Modulators: Features DescriptionkkaytugNo ratings yet

- Data SheetDocument7 pagesData Sheetitamar_123No ratings yet

- IC KA3S0680RF DatasheetDocument12 pagesIC KA3S0680RF Datasheetnaupas007No ratings yet

- 5H0165RDocument12 pages5H0165RDomingo ArroyoNo ratings yet

- Ka 5q0765rt (Sps Fairchild)Document10 pagesKa 5q0765rt (Sps Fairchild)Cristian Steven RuizNo ratings yet

- FSDM07652R DatasheetDocument16 pagesFSDM07652R Datasheetmarianos67No ratings yet

- Apl 5930Document17 pagesApl 5930zanaturNo ratings yet

- LM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorDocument22 pagesLM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorVinoth Kumar RajendranNo ratings yet

- AZ7500BC D1.3 070427nDocument13 pagesAZ7500BC D1.3 070427nroozbehxoxNo ratings yet

- DL 0165 RDocument20 pagesDL 0165 Rledu035No ratings yet

- Tlp250 Application NoteDocument7 pagesTlp250 Application NoteHeriberto Flores Ampie100% (1)

- Ka1 (H0) 265RDocument10 pagesKa1 (H0) 265RminiecateNo ratings yet

- LD7523 DS 00Document18 pagesLD7523 DS 00Eduardo LaloNo ratings yet

- TLP 2601Document9 pagesTLP 2601Sherif OkdaNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-X6759NDocument9 pagesOff-Line Quasi-Resonant Switching Regulators: STR-X6759Nch3o10836266No ratings yet

- TLP358 Datasheet en 20120306Document16 pagesTLP358 Datasheet en 20120306Kumaran ChakravarthyNo ratings yet

- Datasheet STR 6757Document11 pagesDatasheet STR 6757Walter CarreroNo ratings yet

- TLP350 Gate DriverDocument9 pagesTLP350 Gate Driversandeepbabu28No ratings yet

- CS2841BD14Document10 pagesCS2841BD14giapy0000No ratings yet

- Lm2577 Adj MDCDocument27 pagesLm2577 Adj MDCroozbehxoxNo ratings yet

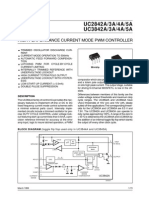

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNo ratings yet

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiNo ratings yet

- L6565Document18 pagesL6565Sergio Daniel BarretoNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- SG2525A SG3525A: Regulating Pulse Width ModulatorsDocument12 pagesSG2525A SG3525A: Regulating Pulse Width ModulatorsMagelicanNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Richtek RT9742Document20 pagesRichtek RT9742zequinha2002No ratings yet

- Mag B550M MortarDocument1 pageMag B550M MortarOsled Rondón LuzardoNo ratings yet

- Java How To Program, 5/e Test Item File 1 of 6Document6 pagesJava How To Program, 5/e Test Item File 1 of 6Leonardo MatteraNo ratings yet

- Easter Secret Code Word CardsDocument11 pagesEaster Secret Code Word CardsClaudia MacarieNo ratings yet

- Power Systems Optimal Placement and Sizing of STATCOM in Multi-Objective Optimization Approach and Using NSGA-II AlgorithmDocument8 pagesPower Systems Optimal Placement and Sizing of STATCOM in Multi-Objective Optimization Approach and Using NSGA-II AlgorithmscribsunilNo ratings yet

- Module 2 BDADocument40 pagesModule 2 BDAARYA MURALI ECE-2020-24No ratings yet

- ADVC3 Brosura NULEC PDFDocument8 pagesADVC3 Brosura NULEC PDFCristina AntohiNo ratings yet

- Rehabilitation and ProstheticsDocument2 pagesRehabilitation and ProstheticsAmit BhattNo ratings yet

- The Deep Focus 2015 Marketing Outlook ReportDocument30 pagesThe Deep Focus 2015 Marketing Outlook ReportDeepFocusNY100% (2)

- CPHIMS Candidate HandbookDocument31 pagesCPHIMS Candidate HandbookAun SharifNo ratings yet

- Null 9Document51 pagesNull 9Nitesh GargNo ratings yet

- CR Cr25.0 - Service ManualDocument541 pagesCR Cr25.0 - Service ManualManuelNo ratings yet

- LogDocument13 pagesLogWahono Bagoes Adjie WibowoNo ratings yet

- SD-651 Low-Profile Plug-In Smoke Detectors: GeneralDocument2 pagesSD-651 Low-Profile Plug-In Smoke Detectors: GeneralAhmad MuzayyinNo ratings yet

- Dev Singh .Net ResumeDocument2 pagesDev Singh .Net Resumepritesh khareNo ratings yet

- Computer Organization and Assembly Language: Week 1 To 3 Dr. Muhammad Nouman DurraniDocument68 pagesComputer Organization and Assembly Language: Week 1 To 3 Dr. Muhammad Nouman DurranipokaNo ratings yet

- MSDocument6 pagesMSyana_harsanaNo ratings yet

- Commands To Check Memory Usage On LinuxDocument9 pagesCommands To Check Memory Usage On LinuxAnonymous gfw31FXbLvNo ratings yet

- Describe ObjectDocument11 pagesDescribe ObjectFerri AinurrofikiNo ratings yet

- Metal Detection Combination DatasheetDocument2 pagesMetal Detection Combination DatasheetRohit DNo ratings yet

- Setdns WebuihwDocument1 pageSetdns Webuihwlina seraNo ratings yet

- Francoise Kempfbvc@Document1 pageFrancoise Kempfbvc@Anonymous n6EISgJRJSNo ratings yet

- D 014 Dyn Wind 02Document4 pagesD 014 Dyn Wind 02sanan KhanNo ratings yet

- Blue Techno Agency Digital Company Online Business Partnership Plan PresentationDocument17 pagesBlue Techno Agency Digital Company Online Business Partnership Plan PresentationHuy Nguyen Tran NhatNo ratings yet

- 2022 Threat Detection Report Full VersionDocument80 pages2022 Threat Detection Report Full VersionCarmelo ToledoNo ratings yet

- Eur 16262 en PDFDocument2 pagesEur 16262 en PDFNatashaNo ratings yet

- SAP GUI Inst GuideDocument16 pagesSAP GUI Inst Guidevinodk33506100% (1)

- Facial Emotion Detection Using Convolutional Neural Network Artificial Intelligence ProjectDocument6 pagesFacial Emotion Detection Using Convolutional Neural Network Artificial Intelligence ProjectSanket Ghatte100% (1)

Datasheet of FAN7554

Datasheet of FAN7554

Uploaded by

AnowarSadatCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Datasheet of FAN7554

Datasheet of FAN7554

Uploaded by

AnowarSadatCopyright:

Available Formats

2000 Fairchild Semiconductor International

www.fairchildsemi.com

Rev. 5.0

Features

Current Mode Control

Pulse by pulse current limiting

Low external components

Lowest cost SMPS solution

Under-Voltage Lockout( UVLO): 9V/15V

Stand-by Current: Typ. 100uA

Power Saving Mode Current: Typ. 200uA

Operating Current: Typ. 7mA

Soft start

On/Off control

Over Load Protection(OLP)

Over Voltage Protection(OVP)

Over Current Protection(OCP)

Over Current Limit(OCL)

Operating Frequency up to 500kHz

1A Totem-pole Output Current

Applications

Off-Line & DC-DC Converter

Description

FAN7554 is fixed frequency current-mode PWM controller.

It is specially designed for off-line and DC-to-DC converter

applications with minimal external components. These inte-

grated circuits feature a trimmed oscillator for precise duty

cycle control, a temperature compensated reference, high

gain error amplifier, current sensing comparator, and a high

current totempole output. Ideally suited for driving a power

MOSFET. In addition to the general protection function of

PWM IC, FAN7554 has various protection function such as

Over Load Protection, Over Current Protection, Over Volt-

age Protection, which include Built-in auto-restart circuit,

and Over Current Latch. Moreover, it corporates on-off con-

trol circuit and soft start circuit. It also offer low power con-

sumption is stand-by condition.

FAN7554

Versatile PWM Controller

8-DIP

8-SOP

1

1

FAN7554

2

Internal Block Diagram

Absolute Maximum Ratings

( Ta = 25C, unless otherwise specified )

Temperature Characteristics

( -25C Ta 85C )

Parameter Symbol Value Unit

Supply Voltage Vcc 30 V

Output Current IO 1 A

Input Voltage to FB Pin VFB -0.3 to VSD V

Input Voltage to IS Pin VIS -0.3 to VOC V

Power Dissipation PD 1 W

Operating Temperature TOPR -25 to +85 C

Storage Temperature TSTG -55 to + 150 C

Parameter Symbol Value Unit

Vref Temperature Stability VREF3 0.5 %

Fosc Temperature Stability FOSC2 5 %

OSC

6

7

1

5

4

3

8

FB

Rt/Ct Vcc

OUT

GND

I S

2

S/S

+

1.5V

+

3.5V

+

!

0.3V

14V

+

15V/9V

UVLO

+

2V

OLP

+

6V

5uA

Vcc

+

Offset(0.1V)

PWM

R

MAX. 1V

2R

UVLO-out

S

Q

R

CLK

PWR

/

SAVE

on

off

Vref

S

Q

R

1k

Vref

100uA

Vref

1mA

+

Vref

S R

Q

OVP

34V

OVP-out

OCL-out

OCL

FAN7554

3

PIN Array

PIN Definitions

Pin Number Pin Name Pin Function Descrition

1 FB

Inverting(-) Input of PWM Comparator,

On/Off Control & OLP Sensing Terminal.

2 S/S Soft Start

3 IS

Non-Inverting(+) Input of PWM Comparator,

OCL Sensing Terminal

4 Rt/Ct Oscillator Time Constant(Rt/Ct)

5 GND Ground

6 OUT Output of gate Driver

7 Vcc Power Supply

8 Vref Output of 5V Reference(Max. 100mA)

Vref Vcc OUT GND

7 77 7 6 66 6 5 55 5 8 88 8

2 22 2 3 33 3 4 44 4 " "" "

Y YY Y W WW W W WW W

A AA A N NN N 7 77 7 5 55 5 5 55 5 4 44 4 F FF F

Rt/Ct IS S/S FB

FAN7554

4

Electrical Characteristics

( Refer to circuit Ta = 25C, Vcc=16V, Rt=10k, Ct=3.3nF unless otherwise specified )

Parameter Symbol Conditions Min. Typ. Max. Unit

< REFERENCE SECTION >

Reference Output Voltage VREF Tj=25C , Iref=1mA 4.90 5.00 5.10 V

Line Regulation VREF1 Vcc=12V~25V - 6 20 mV

Load Regulation VREF2 Iref=1mA~20mA - 6 25 mV

Short Circuit Output Current ISC Tj=25C - 0.1 0.18 A

< OSCILLATOR SECTION >

Oscillation Frequency FOSC Tj=25C 45 50 55 kHz

Frequency Change with Vcc FOSC1 Vcc=12V~25V - 0.05 1.0 %

Ramp High Voltage VRH - - 2.8 - V

Ramp Low Voltage VRL - - 1.2 - V

< PWM SECTION >

Sense Threshold Voltage(Vocp) VTH(IS) VFB =5V 0.8 1.0 1.2 V

Feedback Threshold Voltage VTH(FB) VIS =0V 0.2 0.3 0.4 V

Feedback Source Current IFB VFB = 0V, VS/S = 5V - 1.0 - mA

Max. Duty Cycle D(MAX) - 92 95 98 %

Min. Duty Cycle D(MIN) - - - 0 %

< PROTECTION SECTION >

Shutdown Delay Current ISD 4V VFB VSD 3.5 5 6.5 uA

Shutdown Feedback Voltage VSD VFB > 5V 5.4 6 6.6 V

Over Current Latch Protection VOC VIS > 1.5V, ton > 500nS 1.6 2 2.4 V

Over Voltage Protection VOVP - 30 34 38 V

< ON/OFF CONTROL SECTION >

Off Mode Sink Current ISINK VFB < VTH(FB), VS/S = 5V - 4 - mA

Off Threshold Voltage VOFF VFB < VTH(FB) 1.2 1.5 1.8 V

< SOFT-START SECTION >

Soft Start Current IS/S VFB = 5V, VS/S = 0V - 1.1 - mA

Soft Start Limit Voltage VLIM(S/S) Vcc = 16V - 5.2 - V

<OUTPUT SECTION>

Low Output Voltage1 VOL1 Io = 50mA - 0.15 0.4 V

High Output Voltage1 VOH1 Io = 50mA 13 15 17 V

Low Output Voltage2 VOL2 Io = 200mA - 1.5 2.5 V

High Output Voltage2 VOH2 Vcc=18V, Io=200mA 12 14 16 V

Rising Time tR Tj=25C, CL = 1nF - 80 - nS

Falling Time tF Tj=25C, CL = 1nF - 40 - nS

<UVLO SECTION>

Start Threshold Voltage VTH(ST) - 13.2 15 16.2 V

Min. Operating Voltage VOPR(M) - 8.2 9 10.2 V

FAN7554

5

Electrical Characteristics (Continued)

( Refer to circuit Ta = 25C, Vcc=16V, Rt=10k, Ct=3.3nF unless otherwise specified )

Parameter Symbol Conditions Min. Typ. Max. Unit

<TOTAL STANDBY CURRENT SECTION>

Start-up Current IST Vcc = 14V - 0.1 0.2 mA

Operating Supply Current IOP Vcc 30V - 7 10 mA

Off State Current IOFF Vcc=14V,VFB<VTH(FB),VS/S<VOF - 0.2 0.4 mA

FAN7554

6

Typical Perfomance Characteristics

[ Rt vs. Freqency ] [ Rt vs. Freqency ] [ Rt vs. Freqency ] [ Rt vs. Freqency ]

0.1

1.0

10.0

100.0

1000.0

10000.0

1 10 100

Rt[Kohm]

F

r

e

q

u

e

n

c

y

[

k

H

z

]

0.33n

1.1n

3.3n

11n

33n

[ Ct vs Dead time ] [ Ct vs Dead time ] [ Ct vs Dead time ] [ Ct vs Dead time ]

0.100

1.000

10.000

100.000

0.1 1 10 100

Ct[nF]

D

e

a

d

T

i

m

e

[

u

s

e

c

]

1K

2K

5K

10K

20K

50K

100K

[ Ct vs Duty ] [ Ct vs Duty ] [ Ct vs Duty ] [ Ct vs Duty ]

15.0

25.0

35.0

45.0

55.0

65.0

75.0

85.0

95.0

0.1 1 10 100

Ct [nF]

D

u

t

y

[

%

]

1K

2K

5K

10K

20K

50K

100K

[ Cload vs Tr & Tf ] [ Cload vs Tr & Tf ] [ Cload vs Tr & Tf ] [ Cload vs Tr & Tf ] 50Khz,95% duty

0

100

200

300

400

500

600

700

800

1 10 100

Cload [ nF]

T

i

m

e

[

n

s

e

c

]

Tr

Tf

Figure 1. Rt vs Frequency Figure 2. Ct vs Dead Time

Figure 3. Ct vs Duty Figure 4. Cload vs Tr & Tf

FAN7554

7

Typical Perfomance Characteristics(Continued)

temp. vs Ist

0.070

0.080

0.090

0.100

0.110

0.120

-25 0 25 50 75

temp [!]

I

s

t

[

m

A

]

temp. vs Iop

6.50

6.70

6.90

7.10

7.30

-25 0 25 50 75

temp [ !]

I

o

p

[

m

A

]

temp. vs Vref

4.930

4.932

4.934

4.936

4.938

-25 0 25 50 75

temp. [!]

V

r

e

f

[

V

]

temp. vs [ Ist / (Ist at 25!) ]

0.90

0.95

1.00

1.05

1.10

1.15

-25 0 25 50 75

temp [!]

temp. vs [ Iop / (Iop at 25!) ]

0.96

0.98

1.00

1.02

1.04

-25 0 25 50 75

temp [ !]

temp. vs [ Vref / (Vref / Vref at 25!)

]

0.998

0.999

1.000

1.001

1.002

-25 0 25 50 75

temp. [!]

Figure 1. Temperature vs lst (at 25 C)

Figure 2. Temperature vs lst

Figure 3. Temperature vs lop (at 25 C)

Figure 4. Temperature vs lop

Figure 5. Temperature vs Vref (at 25 C) Figure 6. Temperature vs Vref

FAN7554

8

Typical Perfomance Characteristics(Continued)

temp. vs Fosc

52.00

53.00

54.00

55.00

56.00

-25 0 25 50 75

temp [!]

F

o

s

c

[

k

H

z

]

temp. vs Vth(st)

14.40

14.60

14.80

15.00

15.20

-25 0 25 50 75

temp. [!]

V

t

h

(

s

t

)

[

V

]

temp. vs Vopr(min)

9.27

9.28

9.29

9.30

9.31

-25 0 25 50 75

temp. [!]

V

o

p

r

(

m

i

n

)

[

V

]

temp. vs [ Fosc / ( Fosc at 25!) ]

0.960

0.980

1.000

1.020

1.040

1.060

-25 0 25 50 75

temp [!]

temp. vs normalized Vth(st)

0.980

0.990

1.000

1.010

1.020

-25 0 25 50 75

temp. [!]

temp. vs normalized Vopr(min)

0.998

0.999

1.000

1.001

1.002

-25 0 25 50 75

temp. [!]

Figure 7.Temperature vs Fosc(at 25 C) Figure 8. Temperature vs Fosc

Figure 9. Temperature vs Norm Alized Vth(st) Figure 10. Temperature vs Vth(st)

Figure 11. Temperature vs Alized Vopr(min) Figure 12. Temperature vs Vopr(min)

FAN7554

9

Operation Description

FAN7554 has all the basic features of the current mode SMPS control IC. Furthermore, as a PWM (Pulse Width Modulation)

control IC, FAN7554 modulates the pulse width by comparing the input current sense voltage level to the feedback voltage

level. Its basic configuration includes a UVLO with 6V hysteresis, 5V bandgap reference, low start-up current, oscillator that

can oscillate up to 500KHz depending on Rt/Ct (connected externally), PWM logic circuit , MOSFET gate drive, feedback cir-

cuit that has the current source and soft start function. Its protection circuit has delayed shutdown and over current shutdown

functions. Of the two protection functions, the delayed shutdown forces the IC to charge the feedback capacitor Cfb with cur-

rent source in the IC for the additional delay time if there is an error or overload from a system feedback loop failure or if there

is a transient state. Then it forces a system shutdown after a specified time. Then a MOSFET breakdown etc. causes over cur-

rent to flow. The over current shutdown is the protection function that stops all of control operations to protect the IC and sys-

tem. As an Auto-restart circuit, the shutdown circuit resets when Vcc becomes less than the under voltage.

Start-Up

Start-Up circuit drives the FAN7554 IC using the low start up current. It is made up of the Under Voltage Lock Out (UVLO),

the protection for low voltage conditions, and a 5V reference (Vref), which supplies Bias voltage to the Control Circuit , after

Start Threshold Voltage. The Starting voltage of the UVLO is 15V , and the minimum voltage after turn on is 9V. It has a 6V

hysteresis. The minimum operating current for start up threshold is typically 100uA, and this can minimize the power loss

from the starting resistor. Vref is designed with the bandgap reference circuit with its superior temperature characteristics and

supplies power to all FAN7554 circuits and Rt/Ct, with the exceptions of the ULVO circuit and ON/OFF control circuit. Fur-

thermore, as for the Good Logic block, it either makes the output drive in low or discharges the soft start capacitor or feedback

capacitor.

Soft Start

The SMPS output load usually contains a capacitive load component. During initial start up, the output voltage increases at a

fixed time constant because of this component. If the feedback loop, which controls the output voltage, was to start without

the soft start circuit, the feedback loop would appear to be open during initial startup , and This would drive the voltage in

feedback pin up to 1V as a maximum voltage.

During this time, the peak value of the drain current would stay at the maximum value, and the maximum power would be

delivered to the secondary load side from the start. If maximum power was supplied to the secondary side at start for a fixed

time in the SMPS, this can put severe stress on the entire circuit to prevent such a case, the soft start function is needed and

included in this control system. At start up, the soft start capacitor Cs is charged with 1mA and 100uA current sources.

The voltage of the inverting terminal of the PWM comparator increases to 1/3 of the Cs voltage at a fixed time constant. Sub-

sequently, the drain peak current is limited by the gradual increase in the Cs voltage and this causes the output voltage to

increase smoothly. When the Cs voltage becomes greater than 3V, diode Ds turns off and the inverting terminal voltage

becomes no longer a function of the Cs voltage but of the feedback signal. Then, Cs voltage charges to 5V using 100uA. The

soft start capacitor Cs is discharged when the UVLO Good Logic starts, so soft start is repeated at re-start.

7

SV

Vref

3

Internal Bias

Good Logic

VDD

UVLO

15V/9V

Vref ICC

[mA]

7.0

0.01

9V

16V

VCC

[V]

Figure 1. Low Current Start-Up & Bandgap Reference Circuit Figure 2. Start-Up & Circuit Characteristics

FAN7554

10

Oscillator

The oscillator frequency is programmed by values selected for timing components Rt and Ct. Capacitor Ct is charged to almost

2.8V through resistor Rt from the 5V reference and discharged to 1.2V by the current sink. The oscillator generates the clock

signal during the timing capacitor's Ct discharge. The gate drive output becomes low during the clock time. Rt and Ct selec-

tions determines the oscillator frequency and maximum duty cycle. Charge and discharge times can be calculated through the

equations below.

Charging time : tc = 0.55RtCt

Discharging time : td = RtCtln[(0.0063Rt - 2.7) / (0.0063Rt - 4.0)]

where the oscillator frequency : fosc = (tc + td)-1

When Rt > 5K, fosc = 1 / (0.55RtCt) = 1.8 / (RtCt)

FAN7554 has almost 100% maximum duty cycle. This duty cycle clamp is useful generally in the flyback or forward con-

verter. To optimize the device's performance, the external clock signal blanks the output to low during deadtime. This limits

the maximum duty cycle.

Dmax = tc / (tc + td)

SOFT

START

2

2R

1mA R

Vof f

+

-

1 FB

Cs Cf b

PWM

LOGI C

5V

100uA

5V

Vcc

5uA

[Soft Start Circuit & Circuit Flow]

Ds

Figure 3. Soft Start Circuit & Circuit Flow

1mA

SOFT

START

PWM

LOGIC

Cs

i nt er na l cl ock

[ Rt << 5" ]

Vl ow ( 1. 2V)

Vhi gh ( 2. 8V)

t c t d

i nt er nal cl ock

s awt oot h wavef or m

Vl ow ( 1. 2V)

Vhi gh ( 2. 8V)

t c t d

s awt oot h wavef or m

[ Rt > 5" ]

[Sawtooth & Clock Waveform]

2. 8V

/ 1. 2V

Rt

Di s char ge

Gat e Dr i ve

Cl ock

s w

Ct

8

4

Vr ef

Rt / Ct

[ Oscillator Circuit ]

+

-

Clock

Gate Drive

Figure 4. Oscillator Circuit

Figure 5. Sawtooth & Clock Waveform

Discharge

Ct

Vhigh (2.8V)

Sawtooth waveform

Vlow (1.2V)

internal clock

Vhigh (2.8V)

Sawtooth waveform

Vlow (1.2V)

internal clock

tc td

tc

td

FAN7554

11

Feedback

The feedback section can control the feedback voltage and execute delayed shutdown simultaneously. The error voltage fed

back from the secondary side output voltage and the voltage sensed by the MOSFET sense terminal are compared to drive the

gate and modulate the pulse width to control output voltage. For normal operation, the feedback voltage is between 0~3V and,

when it is 3V, the MOSFET drain current is maximum. During normal operation, the feedback capacitor is charged through the

internally designed current sources, 1mA and 5uA, and is then discharged to the secondary side photo-coupler to control the

output voltage.

Delayed Shutdown

When the feedback loop is operating normally, the feedback voltage remains between 0~3V. If the load at the output terminal

overloads or an error develops in the feedback loop, the delayed shutdown circuit starts. If the abnormal state, which feedback

capacitor discharge is stopped by the photo-coupler, the delayed shutdown circuit converts to the charging mode. When the

feedback voltage is less than 3V, the feedback capacitor is charged through 1mA and 5uA; when the feedback voltage becomes

greater than 3V, the capacitor is charged through 5uA because diode D1 turns off. When the feedback voltage is less than 3V,

the charge slope becomes an exponential function due to the IC internal resistance, and, greater than 3V, the charge slope

becomes linear. When the feedback voltage reaches almost 6V, the delayed shutdown with the latch circuit shutsvdown the IC.

The shutdown circuit is configured for auto-restart, so it automatically restarts when when Vcc reaches the under voltage 9V.

Gat e

[Feedback & PWM Circuit ]

2R

1mA R

Vof f

+

-

1 FB

Cf b

S

R

Q

OSC

Cl ock

Dr i ve

D1

5V

Vcc

5uA

Rs

DRAI N

6

Out

3

I S

Figure 6. Feedback & PWM Circuit

OSC

C1

Clock

Gate

Drive

DRAIN

Gat e

2R

1mA

R

1 FB

Cf b

6V

( X)

Vof f

+

-

S

R

Q

os c

Cl ock Dr i ve

Shut down

Over Cur r ent

Compar at or

5V

Vcc

5uA

+

-

Si gnal

S

R

Q

UVLO Out

Rs

3

I S

DRAI N

6

Out

D1 D2

Clock

Gate

Drive

DRAIN

Over Current

Comparator

Figure 7-A . Delayed Shutdown & Feedback Circuit

FAN7554

12

Gate Driver

Gate Drive circuit has the Totem-Pole Output configuration. The output has 1A Peak Current and 200mA Average Current

drive ability.

ON/OFF Control

The FAN7554 does not have a pin specifically for ON/Off control but is able to use the feedback pin without extra components

for on-off control. When the circuit control unit sends the off signal, the current is forced to flow to the photo-coupler diode,

completely saturating the photo-coupler transistor. As a result, the feedback voltage discharges through the transistor. When

the feedback voltage becomes less than 0.3V, the soft start pin voltage can be droppecl depending on the internal 1K resistor

and external capacitor Cs's time constant; when the S/S pin voltage becomes less than 1.5V, turns off the Vref block and cut-

ting off all the circuit in FAN7554, with the exceptions of the ULVO circuit and On/Off control circuit. It drives the output

drive in low through the Good Logic block and discharges the Cs potential to the GND. Such double OFF control prevents

abnormal operation from a transient state or noise environment and provides for a more stable operation. Because a 5uA cur-

rent source is connected to Cfb even in off state, Cfb is charged if an ON signal is received. When the feedback voltage

exceeds 0.3V, it operates normally by turning on the Vref block. The operating current is about 200uA (Typ.) in off state, so the

circuit consumes low power.

t

t# t2

3V

6V

Vfb

Slope(dv/dt)= 5uA / Cfb

Shutdown Start Point

[Delayed Shutdown & Feedback Waveform]

Figure 7-B . Delayed Shutdown & Feedback Waveform

[Gate Drive Circuit ]

Vz

Vcc

Clock

Q

Shutdown

DRAIN

6

Out

Figure 8. Gate Drive Circuit

FAN7554

13

Figure 9. ON/OFF Control Circuit

Cs

PWR_

Save

2

100uA

[ON/OFF Control Circuit]

1.5V

Vref(5V)

Cfb

1

FB

5uA

15V/9V

Internal Bias

UVLO

Good Logic

5V

Vref

7

8 Vref

Vcc

Vcc

3.5V

1K

S/S

0.3V

S R

Q

Off

On

Vo

External Signal

OFF STATE

t

0.2mA

Icc

Vfb

Vs/s

t

t

0.3V

~ 3V

#.5V

0.3V

5V

5V

Vref

4.5mA

Slope(dv/dt) = #00uA / Cs

Slope(dv/dt)= 5uA / Cfb

ON SIGNAL

Slope(dv/dt) = ## * Cs

Slope(dv/dt) = (#mA+5uA) / Cfb

OFF SIGNAL

Slope(dv/dt)= (#mA+#00uA)/Cs

3V

NORMAL STAGE NORMAL STAGE

Figure 10. ON-OFF Control Circuit Waveform

FAN7554

14

Protection Circuits

FAN7554 has many built-in protection circuits that do not need additional components, providing reliability without cost

increase. These protection circuits have the Auto-restart configuration. In this configuration, the protection circuit resets when

Vcc is below UVLO stop threshold (9V) and restarts when Vcc is above UVLO start threshold voltage (15V)

-. Over Voltage Protection

Even if the feedback circuit appear to be open due to an error in the secondary side feedback or no soldering , the switching on

the primary side still continues until the protection circuit starts; this causes the secondary side voltage to become much

greater than the rated voltage.

The over voltage protection circuit of FAN7554 senses Vcc inside the IC. If Vcc becomes greater than 34V, the protection cir-

cuit starts to operate. Because Vcc is in proportion to the output line voltage of the flyback converter, Vcc during normal oper-

ation should be appropriately maintained at less than 34V.

-. Over Load Protection

An overload is different from a short load. An overload occurs when a load becomes greater than the preset load during nor-

mal operation. for example, the IC stops itself if the SMPS outputs 110W when it exceeds the preset maximum power of

100W. If this protection circuit initiates, then this could perform an undesired execution even during a transient state. There-

fore, as a measurement against such a happening, the protection circuit in FAN7554 is forced to wait a specified time before

operating to determine whether the recognized overload is a transient or a overload state.

T i m e C o n s t a n t

= 3 R * C f b

5 u A = C f b * 3 V / t 2

6 V

3 V

0 t

t 2

t $

S h u t d o w n

[ D e l a y e d S h u t d o w n ]

R

S

Q

2 R

R

O S C .

$ m A 5 u A

V c k

V f b

V f b

*

Q

R

S

R e s e t

6 V

C f b

S h u t d o w n

V o

# $

F FF F A AA A N NN N 7 77 7 5 55 5 5 55 5 4 44 4

K A 4 3 $

D $ D 2

Figure 11. Delayed Shutdown

FAN7554

15

V r ef GND

S /S Is Rt/Ct

FAN7554

RT1 FUS E

C1

L1

C2

C3

RECT

R 5

R6

C 4

C5

C6 R3 R4

D2

D1

R1

R2

D3

R7

C 7

C10

C21

D5

D4

L2

C12 C11

+1 2V

+ 5 V

C13

C14

L4

R9

R10

R11

R12

OP1

I C3

C17

OP1

C15 C16

C20

R19

V cc OUT

F /B

1 2 3 4

8 7 6 5

C8

C22

C9

R14

R15

D6

R16

R18

R17

Figure 12. 100W Forward converter circuit with FAN7554

Application Circuit

+5V 10A

12V 2A

FAN7554

16

Part List

*Note

*(1) Box Capacitor (2) Ceramic Capacitor (3) Electorlytic Capacitor (4) Film Capacitor

Part Value Part Value Part Value

RT1 NTC:10D-11 R19 2.2k C20

332

(2)

R1 33k (1/2W) C1

0.47uF(275V)

(1)

C21

272

(2)

R2 33k (1/2W) C2

472 (1kV)

(2)

C22

333

(2)

R3 56k (2W) C3

472 (1kV)

(2)

D1 1N4004

R4 56k (2W) C4

470uF(200V)

(3)

D2 FR157

R5 220k (1W) C5

470uF(200V)

(3)

D3 UF4007

R6 220k (1W) C6

223 (630V)

(3)

D4 S30SC4M (25A)

R7 6.8 C7

33uF(35V)

(4)

D5 SBL1040CT (10A)

R9 50k (1%) C8

104

(2)

D6 1N4148

R10 50k (1%) C9

1uF(10V)

(3)

L1 Line Filter

R11 1k C10

101

(2)

L2 9.2

R12 820 C11

1000uF (16V)

(3)

L3 1ron Power 27

R13 - C12

1000uF (16V)

(3)

L4 10uH

R14 47k C13

3300uF (10V)

(3)

OP1 PC817

R15 20 C14

3300uF (10V)

(3)

FUSE 5A/250VAC

R16 7k C15 - RECT PBS406GU

R17 1k C16 - Q1 SSH8N80

R18 0.6 (1W) C17

105

(2)

- -

FAN7554

17

Mechanical Dimensions

Package

Dimensions in millimeters

8-SOP

FAN7554

18

Mechanical Dimensions (Continued)

Package

Dimensions in millimeters

8-DIP

FAN7554

19

Ordering Information

Product Number Package Operationg Temperature

FAN7554 8-DIP

-25C ~ 85C

FAN7554D 8-SOP

FAN7554

9/25/00 0.0m 001

Stock#DSxxxxxxxx

2000 Fairchild Semiconductor International

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

INTERNATIONAL. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, and (c) whose failure to

perform when properly used in accordance with

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER

DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.

You might also like

- Data Visualization in Tableau - Car Insurance Claim ProjectDocument51 pagesData Visualization in Tableau - Car Insurance Claim ProjectTunde Asaaju50% (2)

- Irazu EULA AgreementDocument7 pagesIrazu EULA AgreementLiqiang HeNo ratings yet

- AN7554Document22 pagesAN7554Corban MihaiNo ratings yet

- FAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorDocument17 pagesFAN7602 - Green Current Mode PWM Controller - Fairchild SemiconductorVijay MistryNo ratings yet

- DM 0565 RDocument20 pagesDM 0565 R81968No ratings yet

- 60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsDocument14 pages60 W-Universal Input/90 W-230 Vac Input PWM Switching RegulatorsIBSDIALLO0% (1)

- 1M0365RDocument11 pages1M0365RAndro DackNo ratings yet

- CM6800GIPDocument18 pagesCM6800GIPAndré Frota PaivaNo ratings yet

- L 6565Document17 pagesL 6565tatatabuchoNo ratings yet

- Green Current Mode PWM Controller: Features DescriptionDocument12 pagesGreen Current Mode PWM Controller: Features Descriptionceny123No ratings yet

- STR W6735Document14 pagesSTR W6735proctepNo ratings yet

- Fan 7530Document20 pagesFan 7530aldo_suviNo ratings yet

- FSDH0165Document9 pagesFSDH0165Giovanni Carrillo VillegasNo ratings yet

- LM 2587 DatasheetDocument26 pagesLM 2587 DatasheetAnonymous vKD3FG6RkNo ratings yet

- SSC2001S Application NoteDocument18 pagesSSC2001S Application NoteGerardo Mendez CamarilloNo ratings yet

- Fs6s1265re PDFDocument11 pagesFs6s1265re PDFHelton AmorimNo ratings yet

- Inverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterDocument9 pagesInverter For Air Conditioner IGBT/Power MOS FET Gate Drive Industrial InverterFurqan MemonNo ratings yet

- KA1H0165RDocument12 pagesKA1H0165RJtzabalaNo ratings yet

- Fan 7313Document11 pagesFan 7313KathafiNo ratings yet

- Viper 53Document24 pagesViper 53Cadena CesarNo ratings yet

- 5 M 0965 QT UDocument12 pages5 M 0965 QT UcesarlcaNo ratings yet

- STR W6735 DatasheetDocument13 pagesSTR W6735 DatasheetloagerNo ratings yet

- STR W6753 DatasheetDocument8 pagesSTR W6753 DatasheetjgerabmNo ratings yet

- L4949Document11 pagesL4949Николай КръстевNo ratings yet

- SG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorDocument10 pagesSG3525A Pulse Width Modulator Control Circuit: 1% and The ErrorJayesh SuryavanshiNo ratings yet

- LM350 DatasheetDocument12 pagesLM350 DatasheetOmarVelasquezC.No ratings yet

- 161 20551 0 FS7M0880Document16 pages161 20551 0 FS7M0880Edwin Vitovis TorresNo ratings yet

- 7 M 0880Document18 pages7 M 0880Mahmoued YasinNo ratings yet

- Regulating Pulse Width Modulators: Features DescriptionDocument7 pagesRegulating Pulse Width Modulators: Features DescriptionkkaytugNo ratings yet

- Data SheetDocument7 pagesData Sheetitamar_123No ratings yet

- IC KA3S0680RF DatasheetDocument12 pagesIC KA3S0680RF Datasheetnaupas007No ratings yet

- 5H0165RDocument12 pages5H0165RDomingo ArroyoNo ratings yet

- Ka 5q0765rt (Sps Fairchild)Document10 pagesKa 5q0765rt (Sps Fairchild)Cristian Steven RuizNo ratings yet

- FSDM07652R DatasheetDocument16 pagesFSDM07652R Datasheetmarianos67No ratings yet

- Apl 5930Document17 pagesApl 5930zanaturNo ratings yet

- LM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorDocument22 pagesLM3478 High Efficiency Low-Side N-Channel Controller For Switching RegulatorVinoth Kumar RajendranNo ratings yet

- AZ7500BC D1.3 070427nDocument13 pagesAZ7500BC D1.3 070427nroozbehxoxNo ratings yet

- DL 0165 RDocument20 pagesDL 0165 Rledu035No ratings yet

- Tlp250 Application NoteDocument7 pagesTlp250 Application NoteHeriberto Flores Ampie100% (1)

- Ka1 (H0) 265RDocument10 pagesKa1 (H0) 265RminiecateNo ratings yet

- LD7523 DS 00Document18 pagesLD7523 DS 00Eduardo LaloNo ratings yet

- TLP 2601Document9 pagesTLP 2601Sherif OkdaNo ratings yet

- Off-Line Quasi-Resonant Switching Regulators: STR-X6759NDocument9 pagesOff-Line Quasi-Resonant Switching Regulators: STR-X6759Nch3o10836266No ratings yet

- TLP358 Datasheet en 20120306Document16 pagesTLP358 Datasheet en 20120306Kumaran ChakravarthyNo ratings yet

- Datasheet STR 6757Document11 pagesDatasheet STR 6757Walter CarreroNo ratings yet

- TLP350 Gate DriverDocument9 pagesTLP350 Gate Driversandeepbabu28No ratings yet

- CS2841BD14Document10 pagesCS2841BD14giapy0000No ratings yet

- Lm2577 Adj MDCDocument27 pagesLm2577 Adj MDCroozbehxoxNo ratings yet

- UC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerDocument16 pagesUC2842A/3A/4A/5A UC3842A/3A/4A/5A: High Performance Current Mode PWM ControllerCortés BernaNo ratings yet

- UC3845ANDocument15 pagesUC3845ANMiloud ChouguiNo ratings yet

- L6565Document18 pagesL6565Sergio Daniel BarretoNo ratings yet

- Transition-Mode PFC Controller: 1 FeaturesDocument17 pagesTransition-Mode PFC Controller: 1 Featuresadriancho66No ratings yet

- SG2525A SG3525A: Regulating Pulse Width ModulatorsDocument12 pagesSG2525A SG3525A: Regulating Pulse Width ModulatorsMagelicanNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetNo ratings yet

- Simulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetFrom EverandSimulation of Some Power Electronics Case Studies in Matlab Simpowersystem BlocksetRating: 2 out of 5 stars2/5 (1)

- Richtek RT9742Document20 pagesRichtek RT9742zequinha2002No ratings yet

- Mag B550M MortarDocument1 pageMag B550M MortarOsled Rondón LuzardoNo ratings yet

- Java How To Program, 5/e Test Item File 1 of 6Document6 pagesJava How To Program, 5/e Test Item File 1 of 6Leonardo MatteraNo ratings yet

- Easter Secret Code Word CardsDocument11 pagesEaster Secret Code Word CardsClaudia MacarieNo ratings yet

- Power Systems Optimal Placement and Sizing of STATCOM in Multi-Objective Optimization Approach and Using NSGA-II AlgorithmDocument8 pagesPower Systems Optimal Placement and Sizing of STATCOM in Multi-Objective Optimization Approach and Using NSGA-II AlgorithmscribsunilNo ratings yet

- Module 2 BDADocument40 pagesModule 2 BDAARYA MURALI ECE-2020-24No ratings yet

- ADVC3 Brosura NULEC PDFDocument8 pagesADVC3 Brosura NULEC PDFCristina AntohiNo ratings yet

- Rehabilitation and ProstheticsDocument2 pagesRehabilitation and ProstheticsAmit BhattNo ratings yet

- The Deep Focus 2015 Marketing Outlook ReportDocument30 pagesThe Deep Focus 2015 Marketing Outlook ReportDeepFocusNY100% (2)

- CPHIMS Candidate HandbookDocument31 pagesCPHIMS Candidate HandbookAun SharifNo ratings yet

- Null 9Document51 pagesNull 9Nitesh GargNo ratings yet

- CR Cr25.0 - Service ManualDocument541 pagesCR Cr25.0 - Service ManualManuelNo ratings yet

- LogDocument13 pagesLogWahono Bagoes Adjie WibowoNo ratings yet

- SD-651 Low-Profile Plug-In Smoke Detectors: GeneralDocument2 pagesSD-651 Low-Profile Plug-In Smoke Detectors: GeneralAhmad MuzayyinNo ratings yet

- Dev Singh .Net ResumeDocument2 pagesDev Singh .Net Resumepritesh khareNo ratings yet

- Computer Organization and Assembly Language: Week 1 To 3 Dr. Muhammad Nouman DurraniDocument68 pagesComputer Organization and Assembly Language: Week 1 To 3 Dr. Muhammad Nouman DurranipokaNo ratings yet

- MSDocument6 pagesMSyana_harsanaNo ratings yet

- Commands To Check Memory Usage On LinuxDocument9 pagesCommands To Check Memory Usage On LinuxAnonymous gfw31FXbLvNo ratings yet

- Describe ObjectDocument11 pagesDescribe ObjectFerri AinurrofikiNo ratings yet

- Metal Detection Combination DatasheetDocument2 pagesMetal Detection Combination DatasheetRohit DNo ratings yet

- Setdns WebuihwDocument1 pageSetdns Webuihwlina seraNo ratings yet

- Francoise Kempfbvc@Document1 pageFrancoise Kempfbvc@Anonymous n6EISgJRJSNo ratings yet

- D 014 Dyn Wind 02Document4 pagesD 014 Dyn Wind 02sanan KhanNo ratings yet

- Blue Techno Agency Digital Company Online Business Partnership Plan PresentationDocument17 pagesBlue Techno Agency Digital Company Online Business Partnership Plan PresentationHuy Nguyen Tran NhatNo ratings yet

- 2022 Threat Detection Report Full VersionDocument80 pages2022 Threat Detection Report Full VersionCarmelo ToledoNo ratings yet

- Eur 16262 en PDFDocument2 pagesEur 16262 en PDFNatashaNo ratings yet

- SAP GUI Inst GuideDocument16 pagesSAP GUI Inst Guidevinodk33506100% (1)

- Facial Emotion Detection Using Convolutional Neural Network Artificial Intelligence ProjectDocument6 pagesFacial Emotion Detection Using Convolutional Neural Network Artificial Intelligence ProjectSanket Ghatte100% (1)