Professional Documents

Culture Documents

DM74LS194A 4-Bit Bidirectional Universal Shift Register: General Description Features

DM74LS194A 4-Bit Bidirectional Universal Shift Register: General Description Features

Uploaded by

AnjaliTiwariCopyright:

Available Formats

You might also like

- IATA TaxDocument1,510 pagesIATA TaxMiguelRevera100% (1)

- IC TroubleshootingDocument64 pagesIC TroubleshootingKriti TyagiNo ratings yet

- 74LS194Document6 pages74LS194ChanjayNo ratings yet

- M54HC194 M74HC194: 4 Bit Pipo Shift RegisterDocument12 pagesM54HC194 M74HC194: 4 Bit Pipo Shift RegisternooorNo ratings yet

- Datasheet PDFDocument4 pagesDatasheet PDFMauricio MontañoNo ratings yet

- Electronics Exercise 3: Uni-Polar Stepper Motor Controller / DriverDocument7 pagesElectronics Exercise 3: Uni-Polar Stepper Motor Controller / Driverabdou_scribdNo ratings yet

- M54HC195 M74HC195: 8 Bit Pipo Shift RegisterDocument13 pagesM54HC195 M74HC195: 8 Bit Pipo Shift RegisternooorNo ratings yet

- Counters Registersv2Document37 pagesCounters Registersv2DERICK TIMOTHY CASTRONo ratings yet

- D D D D: SN74ALS166 Parallel-Load 8-Bit Shift RegisterDocument16 pagesD D D D: SN74ALS166 Parallel-Load 8-Bit Shift Registerpraveenverma1990No ratings yet

- Ic HCF4094Document12 pagesIc HCF4094Dewa StudioNo ratings yet

- 8-Bit Shift Registers SN54/74LS166Document4 pages8-Bit Shift Registers SN54/74LS166Kokhito BlackHoleNo ratings yet

- MC14027B Dual J-K Flip-Flop: FeaturesDocument6 pagesMC14027B Dual J-K Flip-Flop: Featuresmarcos cordovaNo ratings yet

- Lecture 7Document27 pagesLecture 7Emmad AhmedNo ratings yet

- Digital Logic DesignDocument28 pagesDigital Logic DesignMohit PrajapatNo ratings yet

- Ade Mod4Document24 pagesAde Mod4Sud UiNo ratings yet

- 8-Bit Shift Registers With 3-State Output Registers: FeaturesDocument16 pages8-Bit Shift Registers With 3-State Output Registers: Featuressyed umarjunaidNo ratings yet

- 74 Ls 74Document6 pages74 Ls 74LucianamxsNo ratings yet

- HCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsDocument14 pagesHCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsfabioboogNo ratings yet

- Counters and DisplaysDocument4 pagesCounters and Displayswafi alNo ratings yet

- Data SheetDocument7 pagesData SheetmegmanojsterNo ratings yet

- 74HCT4040Document7 pages74HCT4040So Was RedNo ratings yet

- 8 Bit Sipo Shift Register: Order CodesDocument13 pages8 Bit Sipo Shift Register: Order Codeslesa33No ratings yet

- CD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopDocument7 pagesCD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopCristian MancholaNo ratings yet

- Shift RegistersDocument23 pagesShift RegistersFasih Ur Rehman BukhariNo ratings yet

- MC74F544Document4 pagesMC74F544ir.setia.utamaNo ratings yet

- 74ac74 - DFFDocument13 pages74ac74 - DFFHoàng Đạt LưuNo ratings yet

- DECSE - Chapter 3 1Document24 pagesDECSE - Chapter 3 1KrithiiNo ratings yet

- M54HC165 M74HC165: 8 Bit Piso Shift RegisterDocument13 pagesM54HC165 M74HC165: 8 Bit Piso Shift RegisternooorNo ratings yet

- 8-Bit Shift Register With 8-Bit Output RegisterDocument11 pages8-Bit Shift Register With 8-Bit Output RegisterDavid RoseNo ratings yet

- 8-Bit Shift Register With 8-Bit Output RegisterDocument11 pages8-Bit Shift Register With 8-Bit Output RegisterWILLIAM AGUDELONo ratings yet

- M54/74HC160/161 M54/74HC162/163: Synchronous Presettable 4-Bit CounterDocument16 pagesM54/74HC160/161 M54/74HC162/163: Synchronous Presettable 4-Bit CounterMohammed El-AwamryNo ratings yet

- CD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopDocument7 pagesCD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopJose MariaNo ratings yet

- LatchDocument8 pagesLatchSheela ShivaramNo ratings yet

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument22 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesRavi Shankar 31No ratings yet

- 74LS174 Flip-Flop DDocument7 pages74LS174 Flip-Flop DmarcosrubenriosNo ratings yet

- 74 Ls 1092Document6 pages74 Ls 1092JuanDiegoNo ratings yet

- Registers and CountersDocument47 pagesRegisters and Counterssheela lNo ratings yet

- Data Sheet: 74HC595 74HCT595Document29 pagesData Sheet: 74HC595 74HCT595EmaxxSeverusNo ratings yet

- Lab 12 PDFDocument5 pagesLab 12 PDFsharonNo ratings yet

- Lab 12Document5 pagesLab 12sharonNo ratings yet

- DLD Chapter 6 DLDDocument35 pagesDLD Chapter 6 DLDAttiq RehmanNo ratings yet

- 74HC HCT164 CNV 2Document9 pages74HC HCT164 CNV 2KevinNo ratings yet

- DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument5 pagesDM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsJoão AlmeidaNo ratings yet

- CSE 205: Digital Logic DesignDocument53 pagesCSE 205: Digital Logic DesignAfifa murshida NazinNo ratings yet

- 74HC595Document10 pages74HC595frickytoNo ratings yet

- Registers and CountersDocument61 pagesRegisters and CountersKritiraj KalitaNo ratings yet

- Hoja Caracteristicas 7474 PDFDocument6 pagesHoja Caracteristicas 7474 PDFArun UpadhyayaNo ratings yet

- Lab Session # 8 Implementation of Registers: 3.1 Parallel-Load RegisterDocument8 pagesLab Session # 8 Implementation of Registers: 3.1 Parallel-Load RegisterAhmad M. HammadNo ratings yet

- Registers & Counters: Compiled By: BUDZDocument19 pagesRegisters & Counters: Compiled By: BUDZVien Ako ReviloNo ratings yet

- Data Sheet: 74HC/HCT166Document10 pagesData Sheet: 74HC/HCT166vetchboyNo ratings yet

- Week 7Document11 pagesWeek 7p.l.giang2451No ratings yet

- Unit-VI Counters and Shift RegistersDocument20 pagesUnit-VI Counters and Shift RegistersVarsha SenthilNo ratings yet

- Toshiba 74HC595D (X34TTD-410-02) E 20160209-909557Document10 pagesToshiba 74HC595D (X34TTD-410-02) E 20160209-909557Vanesa RiveraNo ratings yet

- Data Sheet: 74HC/HCT165Document10 pagesData Sheet: 74HC/HCT165Thế TùngNo ratings yet

- MM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description FeaturesDocument8 pagesMM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description Featureskumar_santosh1989100% (1)

- Solution - Ass # 9 - CH 9 - s2016Document3 pagesSolution - Ass # 9 - CH 9 - s2016Abigail EngleNo ratings yet

- 74173Document11 pages74173zunaidur_rashidNo ratings yet

- MM74HC123A FairchildSemiconductorDocument9 pagesMM74HC123A FairchildSemiconductorАлексей ГомоновNo ratings yet

- HCF4017B: Decade Counter With 10 Decoded OutputsDocument11 pagesHCF4017B: Decade Counter With 10 Decoded Outputs19thmnlfreemsNo ratings yet

- DM74LS85 4-Bit Magnitude ComparatorDocument6 pagesDM74LS85 4-Bit Magnitude ComparatorhayssamNo ratings yet

- Datasheet 74139Document6 pagesDatasheet 74139Gerardo AldanaNo ratings yet

- SN5474LS95B 4-Bit Shift RegisterDocument6 pagesSN5474LS95B 4-Bit Shift RegisterhayssamNo ratings yet

- SN74LS95 4-Bit Parallel-Access Shift RegistersDocument8 pagesSN74LS95 4-Bit Parallel-Access Shift RegistershayssamNo ratings yet

- ASTM (Berat Jenis Semen)Document2 pagesASTM (Berat Jenis Semen)Efri Dwiyanto100% (1)

- What Made The Tata Nano A Failure: A Winter Project OnDocument90 pagesWhat Made The Tata Nano A Failure: A Winter Project Onyash ranaNo ratings yet

- Do Menu ItemDocument11 pagesDo Menu ItemHuy LamNo ratings yet

- Case - The Tao of Timbuk2Document2 pagesCase - The Tao of Timbuk2Saikat Mukherjeee100% (1)

- Kiln Performance - Efficiency FormulasDocument12 pagesKiln Performance - Efficiency FormulasMohamed ZayedNo ratings yet

- Example ReportDocument4 pagesExample ReportFirzanNo ratings yet

- Article 1500408825Document7 pagesArticle 1500408825fennilubisNo ratings yet

- Drop BoxDocument77 pagesDrop BoxBetty Elizabeth Moreno CarrascoNo ratings yet

- ISO 9001 2015 Quality Manual Template For Service IndustryDocument21 pagesISO 9001 2015 Quality Manual Template For Service IndustryJose Luis Zimic100% (1)

- FortiManager DatasheetDocument13 pagesFortiManager DatasheetmagnusfischerNo ratings yet

- Thesis On Climate Change and Agriculture in IndiaDocument8 pagesThesis On Climate Change and Agriculture in Indiabk4pfxb7100% (1)

- Megaman PatternDocument9 pagesMegaman PatternBelen Solis Maravillas100% (2)

- Ai Business Case EbookDocument23 pagesAi Business Case EbookAjaya Kumar67% (3)

- Rules For Working On AMOS: Rule No.1:: Analysis of Moment Structure (Amos)Document18 pagesRules For Working On AMOS: Rule No.1:: Analysis of Moment Structure (Amos)Rjendra LamsalNo ratings yet

- Feasibility Study About The Establishment of An Ice Cream Car BusinessDocument9 pagesFeasibility Study About The Establishment of An Ice Cream Car BusinesshebaNo ratings yet

- Why Invest in RomaniaDocument21 pagesWhy Invest in RomaniaAlexandru Vlad CiocirlanNo ratings yet

- 1978 Handbook of Birds of India and Pakistan Vol 1 by Ali and Ripley S PDFDocument481 pages1978 Handbook of Birds of India and Pakistan Vol 1 by Ali and Ripley S PDFsreelathapNo ratings yet

- Family Case Study On The Billones Family 1Document63 pagesFamily Case Study On The Billones Family 1Ivy Mae DecenaNo ratings yet

- Scientific Measurement Planning GuideDocument16 pagesScientific Measurement Planning Guidedeez neufNo ratings yet

- Thread & FastenerDocument35 pagesThread & Fastenermani317No ratings yet

- Ttlga 1250Document2 pagesTtlga 1250anerak0412No ratings yet

- Quiz 1Document2 pagesQuiz 1Niño Jay C. GastonesNo ratings yet

- E-Marking Notes On Physics HSSC I May 2018Document30 pagesE-Marking Notes On Physics HSSC I May 2018Hasnain AsifNo ratings yet

- 1.1 Engl 1010Document3 pages1.1 Engl 1010Joey ÁlvarezNo ratings yet

- Aditya Solanki Expriment No.2Document5 pagesAditya Solanki Expriment No.2Kertik SinghNo ratings yet

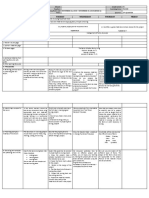

- DLL - Tle-He 6 - Q3 - W5Document5 pagesDLL - Tle-He 6 - Q3 - W5Jayjay Roniel100% (2)

- Non Dir. O/C Relay ARGUS - 7SR1102: 1. General Data & InformationDocument6 pagesNon Dir. O/C Relay ARGUS - 7SR1102: 1. General Data & InformationAnonymous dH3DIEtzNo ratings yet

- HTW-1390 T5: Tunge Modeller Standard StatiskDocument6 pagesHTW-1390 T5: Tunge Modeller Standard StatiskjhonnyNo ratings yet

DM74LS194A 4-Bit Bidirectional Universal Shift Register: General Description Features

DM74LS194A 4-Bit Bidirectional Universal Shift Register: General Description Features

Uploaded by

AnjaliTiwariOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DM74LS194A 4-Bit Bidirectional Universal Shift Register: General Description Features

DM74LS194A 4-Bit Bidirectional Universal Shift Register: General Description Features

Uploaded by

AnjaliTiwariCopyright:

Available Formats

2000 Fairchild Semiconductor Corporation DS006407 www.fairchildsemi.

com

August 1986

Revised March 2000

D

M

7

4

L

S

1

9

4

A

4

-

B

i

t

B

i

d

i

r

e

c

t

i

o

n

a

l

U

n

i

v

e

r

s

a

l

S

h

i

f

t

R

e

g

i

s

t

e

r

DM74LS194A

4-Bit Bidirectional Universal Shift Register

General Description

This bidirectional shift register is designed to incorporate

virtually all of the features a system designer may want in a

shift register; they feature parallel inputs, parallel outputs,

right-shift and left-shift serial inputs, operating-mode-con-

trol inputs, and a direct overriding clear line. The register

has four distinct modes of operation, namely:

Parallel (broadside) load

Shift right (in the direction Q

A

toward Q

D

)

Shift left (in the direction Q

D

toward Q

A

)

Inhibit clock (do nothing)

Synchronous parallel loading is accomplished by applying

the four bits of data and taking both mode control inputs,

S0 and S1, HIGH. The data is loaded into the associated

flip-flops and appear at the outputs after the positive transi-

tion of the clock input. During loading, serial data flow is

inhibited.

Shift right is accomplished synchronously with the rising

edge of the clock pulse when S0 is HIGH and S1 is LOW.

Serial data for this mode is entered at the shift-right data

input. When S0 is LOW and S1 is HIGH, data shifts left

synchronously and new data is entered at the shift-left

serial input.

Clocking of the flip-flop is inhibited when both mode control

inputs are LOW.

Features

I Parallel inputs and outputs

I Four operating modes:

Synchronous parallel load

Right shift

Left shift

Do nothing

I Positive edge-triggered clocking

I Direct overriding clear

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Connection Diagram

Order Number Package Number Package Description

DM74LS194AM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

DM74LS194AN N16E 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

www.fairchildsemi.com 2

D

M

7

4

L

S

1

9

4

A

Function Table

H = HIGH Level (steady state)

L = LOW Level (steady state)

X = Dont Care (any input, including transitions)

= Transition from LOW-to-HIGH level

a, b, c, d = The level of steady state input at inputs A, B, C or D, respectively.

Q

A0

, Q

B0

, Q

C0

, Q

D0

= The level of Q

A

, Q

B

, Q

C

, or Q

D

, respectively, before the indicated steady state input conditions were established.

Q

An

, Q

Bn

, Q

Cn

, Q

Dn

= The level of Q

A

, Q

B

, Q

C

, respectively, before the most-recent transition of the clock.

Logic Diagram

Inputs Outputs

Clear

Mode

Clock

Serial Parallel

Q

A

Q

B

Q

C

Q

D

S1 S0 Left Right A B C D

L X X X X X X X X X L L L L

H X X L X X X X X X Q

A0

Q

B0

Q

C0

Q

D0

H H H X X a b c d a b c d

H L H X H X X X X H Q

An

Q

Bn

Q

Cn

H L H X L X X X X L Q

An

Q

Bn

Q

Cn

H H L H X X X X X Q

Bn

Q

Cn

Q

Dn

H

H H L L X X X X X Q

Bn

Q

Cn

Q

Dn

L

H L L X X X X X X X Q

A0

Q

B0

Q

C0

Q

D0

3 www.fairchildsemi.com

D

M

7

4

L

S

1

9

4

A

Absolute Maximum Ratings(Note 1)

Note 1: The Absolute Maximum Ratings are those values beyond which

the safety of the device cannot be guaranteed. The device should not be

operated at these limits. The parametric values defined in the Electrical

Characteristics tables are not guaranteed at the absolute maximum ratings.

The Recommended Operating Conditions table will define the conditions

for actual device operation.

Recommended Operating Conditions

Note 2: C

L

= 15 pF, T

A

= 25C and V

CC

= 5V.

Note 3: C

L

= 50 pF, R

L

= 2 k, T

A

= 25C and V

CC

= 5V.

Note 4: T

A

= 25C and V

CC

= 5V.

Electrical Characteristics

over recommended operating free air temperature range (unless otherwise noted)

Note 5: All typicals are at V

CC

= 5V, T

A

= 25C.

Note 6: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 7: With all outputs open, inputs A through D grounded, and 4.5V applied to S0, S1, CLEAR, and the serial inputs, I

CC

is tested with momentary ground,

then 4.5V applied to CLOCK.

Supply Voltage 7V

Input Voltage 7V

Operating Free Air Temperature Range 0C to +70C

Storage Temperature Range 65C to +150C

Symbol Parameter Min Nom Max Units

V

CC

Supply Voltage 4.75 5 5.25 V

V

IH

HIGH Level Input Voltage 2 V

V

IL

LOW Level Input Voltage 0.8 V

I

OH

HIGH Level Output Current 0.4 mA

I

OL

LOW Level Output Current 8 mA

f

CLK

Clock Frequency (Note 2) 0 25

MHz

Clock Frequency (Note 3) 0 20

t

W

Pulse Width Clock 20

ns

(Note 4) Clear 20

t

SU

Setup Time Mode 30

ns

(Note 4) Data 20

t

H

Hold Time (Note 4) 0 ns

t

REL

Clear Release Time (Note 4) 25 ns

T

A

Free Air Operating Temperature 0 70 C

Symbol Parameter Conditions Min

Typ

Max Units

(Note 5)

V

I

Input Clamp Voltage V

CC

= Min, I

I

= 18 mA 1.5 V

V

OH

HIGH Level V

CC

= Min, I

OH

= Max

2.7 3.4 V

Output Voltage V

IL

= Max, V

IH

= Min

V

OL

LOW Level V

CC

= Min, I

OL

= Max

0.35 0.5

Output Voltage V

IL

= Max, V

IH

= Min V

I

OL

= 4 mA, V

CC

= Min 0.4

I

I

Input Current @ Max Input Voltage V

CC

= Max, V

I

= 7V 0.1 mA

I

IH

HIGH Level Input Current V

CC

= Max, V

I

= 2.7V 20 A

I

IL

LOW Level Input Current V

CC

= Max, V

I

= 0.4V 0.4 mA

I

OS

Short Circuit Output Current V

CC

= Max (Note 6) 20 100 mA

I

CC

Supply Current V

CC

= Max (Note 7) 15 23 mA

www.fairchildsemi.com 4

D

M

7

4

L

S

1

9

4

A

Switching Characteristics

at V

CC

= 5V and T

A

= 25C

Note 8: All typicals are at V

CC

= 5V, T

A

= 25C.

Note 9: Not more than one output should be shorted at a time, and the duration should not exceed one second.

Note 10: With all outputs open, inputs A through D grounded, and 4.5V applied to S0, S1, CLEAR, and the serial inputs, I

CC

is tested with momentary

ground, then 4.5V applied to CLOCK.

Timing Diagram

Typical Clear, Load, Right-Shift, Left-Shift, Inhibit, and Clear Sequences

Symbol Parameter

From (Input) C

L

= 50 pF, R

L

= 2 k

Units

To (Output) Min Max

f

MAX

Maximum Clock Frequency 20 MHz

t

PLH

Propagation Delay Time Clock to Any Q

26 ns

LOW-to-HIGH Level Output

t

PHL

Propagation Delay Time Clock to Any Q

35 ns

HIGH-to-LOW Level Output

t

PHL

Propagation Delay Time Clear to Any Q

38 ns

HIGH-to-LOW Output

5 www.fairchildsemi.com

D

M

7

4

L

S

1

9

4

A

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

Package Number M16A

www.fairchildsemi.com 6

D

M

7

4

L

S

1

9

4

A

4

-

B

i

t

B

i

d

i

r

e

c

t

i

o

n

a

l

U

n

i

v

e

r

s

a

l

S

h

i

f

t

R

e

g

i

s

t

e

r

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and

Fairchild reserves the right at any time without notice to change said circuitry and specifications.

LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD

SEMICONDUCTOR CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the

body, or (b) support or sustain life, and (c) whose failure

to perform when properly used in accordance with

instructions for use provided in the labeling, can be rea-

sonably expected to result in a significant injury to the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be rea-

sonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

You might also like

- IATA TaxDocument1,510 pagesIATA TaxMiguelRevera100% (1)

- IC TroubleshootingDocument64 pagesIC TroubleshootingKriti TyagiNo ratings yet

- 74LS194Document6 pages74LS194ChanjayNo ratings yet

- M54HC194 M74HC194: 4 Bit Pipo Shift RegisterDocument12 pagesM54HC194 M74HC194: 4 Bit Pipo Shift RegisternooorNo ratings yet

- Datasheet PDFDocument4 pagesDatasheet PDFMauricio MontañoNo ratings yet

- Electronics Exercise 3: Uni-Polar Stepper Motor Controller / DriverDocument7 pagesElectronics Exercise 3: Uni-Polar Stepper Motor Controller / Driverabdou_scribdNo ratings yet

- M54HC195 M74HC195: 8 Bit Pipo Shift RegisterDocument13 pagesM54HC195 M74HC195: 8 Bit Pipo Shift RegisternooorNo ratings yet

- Counters Registersv2Document37 pagesCounters Registersv2DERICK TIMOTHY CASTRONo ratings yet

- D D D D: SN74ALS166 Parallel-Load 8-Bit Shift RegisterDocument16 pagesD D D D: SN74ALS166 Parallel-Load 8-Bit Shift Registerpraveenverma1990No ratings yet

- Ic HCF4094Document12 pagesIc HCF4094Dewa StudioNo ratings yet

- 8-Bit Shift Registers SN54/74LS166Document4 pages8-Bit Shift Registers SN54/74LS166Kokhito BlackHoleNo ratings yet

- MC14027B Dual J-K Flip-Flop: FeaturesDocument6 pagesMC14027B Dual J-K Flip-Flop: Featuresmarcos cordovaNo ratings yet

- Lecture 7Document27 pagesLecture 7Emmad AhmedNo ratings yet

- Digital Logic DesignDocument28 pagesDigital Logic DesignMohit PrajapatNo ratings yet

- Ade Mod4Document24 pagesAde Mod4Sud UiNo ratings yet

- 8-Bit Shift Registers With 3-State Output Registers: FeaturesDocument16 pages8-Bit Shift Registers With 3-State Output Registers: Featuressyed umarjunaidNo ratings yet

- 74 Ls 74Document6 pages74 Ls 74LucianamxsNo ratings yet

- HCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsDocument14 pagesHCF4094B: 8 Stage Shift and Store Bus Register With 3-State OutputsfabioboogNo ratings yet

- Counters and DisplaysDocument4 pagesCounters and Displayswafi alNo ratings yet

- Data SheetDocument7 pagesData SheetmegmanojsterNo ratings yet

- 74HCT4040Document7 pages74HCT4040So Was RedNo ratings yet

- 8 Bit Sipo Shift Register: Order CodesDocument13 pages8 Bit Sipo Shift Register: Order Codeslesa33No ratings yet

- CD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopDocument7 pagesCD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopCristian MancholaNo ratings yet

- Shift RegistersDocument23 pagesShift RegistersFasih Ur Rehman BukhariNo ratings yet

- MC74F544Document4 pagesMC74F544ir.setia.utamaNo ratings yet

- 74ac74 - DFFDocument13 pages74ac74 - DFFHoàng Đạt LưuNo ratings yet

- DECSE - Chapter 3 1Document24 pagesDECSE - Chapter 3 1KrithiiNo ratings yet

- M54HC165 M74HC165: 8 Bit Piso Shift RegisterDocument13 pagesM54HC165 M74HC165: 8 Bit Piso Shift RegisternooorNo ratings yet

- 8-Bit Shift Register With 8-Bit Output RegisterDocument11 pages8-Bit Shift Register With 8-Bit Output RegisterDavid RoseNo ratings yet

- 8-Bit Shift Register With 8-Bit Output RegisterDocument11 pages8-Bit Shift Register With 8-Bit Output RegisterWILLIAM AGUDELONo ratings yet

- M54/74HC160/161 M54/74HC162/163: Synchronous Presettable 4-Bit CounterDocument16 pagesM54/74HC160/161 M54/74HC162/163: Synchronous Presettable 4-Bit CounterMohammed El-AwamryNo ratings yet

- CD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopDocument7 pagesCD40174BC - CD40175BC Hex D-Type Flip-Flop - Quad D-Type Flip-FlopJose MariaNo ratings yet

- LatchDocument8 pagesLatchSheela ShivaramNo ratings yet

- DM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesDocument22 pagesDM74LS174 - DM74LS175 Hex/Quad D-Type Flip-Flops With Clear: General Description FeaturesRavi Shankar 31No ratings yet

- 74LS174 Flip-Flop DDocument7 pages74LS174 Flip-Flop DmarcosrubenriosNo ratings yet

- 74 Ls 1092Document6 pages74 Ls 1092JuanDiegoNo ratings yet

- Registers and CountersDocument47 pagesRegisters and Counterssheela lNo ratings yet

- Data Sheet: 74HC595 74HCT595Document29 pagesData Sheet: 74HC595 74HCT595EmaxxSeverusNo ratings yet

- Lab 12 PDFDocument5 pagesLab 12 PDFsharonNo ratings yet

- Lab 12Document5 pagesLab 12sharonNo ratings yet

- DLD Chapter 6 DLDDocument35 pagesDLD Chapter 6 DLDAttiq RehmanNo ratings yet

- 74HC HCT164 CNV 2Document9 pages74HC HCT164 CNV 2KevinNo ratings yet

- DM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsDocument5 pagesDM74LS73A Dual Negative-Edge-Triggered Master-Slave J-K Flip-Flops With Clear and Complementary OutputsJoão AlmeidaNo ratings yet

- CSE 205: Digital Logic DesignDocument53 pagesCSE 205: Digital Logic DesignAfifa murshida NazinNo ratings yet

- 74HC595Document10 pages74HC595frickytoNo ratings yet

- Registers and CountersDocument61 pagesRegisters and CountersKritiraj KalitaNo ratings yet

- Hoja Caracteristicas 7474 PDFDocument6 pagesHoja Caracteristicas 7474 PDFArun UpadhyayaNo ratings yet

- Lab Session # 8 Implementation of Registers: 3.1 Parallel-Load RegisterDocument8 pagesLab Session # 8 Implementation of Registers: 3.1 Parallel-Load RegisterAhmad M. HammadNo ratings yet

- Registers & Counters: Compiled By: BUDZDocument19 pagesRegisters & Counters: Compiled By: BUDZVien Ako ReviloNo ratings yet

- Data Sheet: 74HC/HCT166Document10 pagesData Sheet: 74HC/HCT166vetchboyNo ratings yet

- Week 7Document11 pagesWeek 7p.l.giang2451No ratings yet

- Unit-VI Counters and Shift RegistersDocument20 pagesUnit-VI Counters and Shift RegistersVarsha SenthilNo ratings yet

- Toshiba 74HC595D (X34TTD-410-02) E 20160209-909557Document10 pagesToshiba 74HC595D (X34TTD-410-02) E 20160209-909557Vanesa RiveraNo ratings yet

- Data Sheet: 74HC/HCT165Document10 pagesData Sheet: 74HC/HCT165Thế TùngNo ratings yet

- MM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description FeaturesDocument8 pagesMM74HC574 3-STATE Octal D-Type Edge-Triggered Flip-Flop: General Description Featureskumar_santosh1989100% (1)

- Solution - Ass # 9 - CH 9 - s2016Document3 pagesSolution - Ass # 9 - CH 9 - s2016Abigail EngleNo ratings yet

- 74173Document11 pages74173zunaidur_rashidNo ratings yet

- MM74HC123A FairchildSemiconductorDocument9 pagesMM74HC123A FairchildSemiconductorАлексей ГомоновNo ratings yet

- HCF4017B: Decade Counter With 10 Decoded OutputsDocument11 pagesHCF4017B: Decade Counter With 10 Decoded Outputs19thmnlfreemsNo ratings yet

- DM74LS85 4-Bit Magnitude ComparatorDocument6 pagesDM74LS85 4-Bit Magnitude ComparatorhayssamNo ratings yet

- Datasheet 74139Document6 pagesDatasheet 74139Gerardo AldanaNo ratings yet

- SN5474LS95B 4-Bit Shift RegisterDocument6 pagesSN5474LS95B 4-Bit Shift RegisterhayssamNo ratings yet

- SN74LS95 4-Bit Parallel-Access Shift RegistersDocument8 pagesSN74LS95 4-Bit Parallel-Access Shift RegistershayssamNo ratings yet

- ASTM (Berat Jenis Semen)Document2 pagesASTM (Berat Jenis Semen)Efri Dwiyanto100% (1)

- What Made The Tata Nano A Failure: A Winter Project OnDocument90 pagesWhat Made The Tata Nano A Failure: A Winter Project Onyash ranaNo ratings yet

- Do Menu ItemDocument11 pagesDo Menu ItemHuy LamNo ratings yet

- Case - The Tao of Timbuk2Document2 pagesCase - The Tao of Timbuk2Saikat Mukherjeee100% (1)

- Kiln Performance - Efficiency FormulasDocument12 pagesKiln Performance - Efficiency FormulasMohamed ZayedNo ratings yet

- Example ReportDocument4 pagesExample ReportFirzanNo ratings yet

- Article 1500408825Document7 pagesArticle 1500408825fennilubisNo ratings yet

- Drop BoxDocument77 pagesDrop BoxBetty Elizabeth Moreno CarrascoNo ratings yet

- ISO 9001 2015 Quality Manual Template For Service IndustryDocument21 pagesISO 9001 2015 Quality Manual Template For Service IndustryJose Luis Zimic100% (1)

- FortiManager DatasheetDocument13 pagesFortiManager DatasheetmagnusfischerNo ratings yet

- Thesis On Climate Change and Agriculture in IndiaDocument8 pagesThesis On Climate Change and Agriculture in Indiabk4pfxb7100% (1)

- Megaman PatternDocument9 pagesMegaman PatternBelen Solis Maravillas100% (2)

- Ai Business Case EbookDocument23 pagesAi Business Case EbookAjaya Kumar67% (3)

- Rules For Working On AMOS: Rule No.1:: Analysis of Moment Structure (Amos)Document18 pagesRules For Working On AMOS: Rule No.1:: Analysis of Moment Structure (Amos)Rjendra LamsalNo ratings yet

- Feasibility Study About The Establishment of An Ice Cream Car BusinessDocument9 pagesFeasibility Study About The Establishment of An Ice Cream Car BusinesshebaNo ratings yet

- Why Invest in RomaniaDocument21 pagesWhy Invest in RomaniaAlexandru Vlad CiocirlanNo ratings yet

- 1978 Handbook of Birds of India and Pakistan Vol 1 by Ali and Ripley S PDFDocument481 pages1978 Handbook of Birds of India and Pakistan Vol 1 by Ali and Ripley S PDFsreelathapNo ratings yet

- Family Case Study On The Billones Family 1Document63 pagesFamily Case Study On The Billones Family 1Ivy Mae DecenaNo ratings yet

- Scientific Measurement Planning GuideDocument16 pagesScientific Measurement Planning Guidedeez neufNo ratings yet

- Thread & FastenerDocument35 pagesThread & Fastenermani317No ratings yet

- Ttlga 1250Document2 pagesTtlga 1250anerak0412No ratings yet

- Quiz 1Document2 pagesQuiz 1Niño Jay C. GastonesNo ratings yet

- E-Marking Notes On Physics HSSC I May 2018Document30 pagesE-Marking Notes On Physics HSSC I May 2018Hasnain AsifNo ratings yet

- 1.1 Engl 1010Document3 pages1.1 Engl 1010Joey ÁlvarezNo ratings yet

- Aditya Solanki Expriment No.2Document5 pagesAditya Solanki Expriment No.2Kertik SinghNo ratings yet

- DLL - Tle-He 6 - Q3 - W5Document5 pagesDLL - Tle-He 6 - Q3 - W5Jayjay Roniel100% (2)

- Non Dir. O/C Relay ARGUS - 7SR1102: 1. General Data & InformationDocument6 pagesNon Dir. O/C Relay ARGUS - 7SR1102: 1. General Data & InformationAnonymous dH3DIEtzNo ratings yet

- HTW-1390 T5: Tunge Modeller Standard StatiskDocument6 pagesHTW-1390 T5: Tunge Modeller Standard StatiskjhonnyNo ratings yet