Professional Documents

Culture Documents

Vedic Multiplier

Vedic Multiplier

Uploaded by

muthuraj14007Copyright:

Available Formats

You might also like

- Lemmon AnswersDocument12 pagesLemmon Answersrichard33% (3)

- Design of High Speed Vedic Multiplier Using Vedic Mathematics TechniquesDocument5 pagesDesign of High Speed Vedic Multiplier Using Vedic Mathematics TechniquesPramod KumarNo ratings yet

- Vedic Algorithms To Develop Green Chips For FutureDocument3 pagesVedic Algorithms To Develop Green Chips For FutureeditorijsaaNo ratings yet

- DSP Operation Using Vedic MathematicsDocument78 pagesDSP Operation Using Vedic Mathematicsnaveen mNo ratings yet

- Design, Implementation and Performance Analysis of An Integrated Vedic Multiplier ArchitectureDocument7 pagesDesign, Implementation and Performance Analysis of An Integrated Vedic Multiplier ArchitectureAbhijeet KumarNo ratings yet

- Performance Analysis of Vedic Multiplier in Hardware Implementation of Biomedical ApplicationsDocument4 pagesPerformance Analysis of Vedic Multiplier in Hardware Implementation of Biomedical ApplicationsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- VLSI Implementation of Vedic Multiplier Using Urdhva - Tiryakbhyam Sutra in VHDL Environment: A NoveltyDocument8 pagesVLSI Implementation of Vedic Multiplier Using Urdhva - Tiryakbhyam Sutra in VHDL Environment: A NoveltyInternational Organization of Scientific Research (IOSR)No ratings yet

- Performance Analysis of Vedic Multiplier in Signal Processing ApplicationsDocument4 pagesPerformance Analysis of Vedic Multiplier in Signal Processing ApplicationsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Literature Survey: Preyesh Dalmia Et Al (2018)Document3 pagesLiterature Survey: Preyesh Dalmia Et Al (2018)yuvaraaj aletiNo ratings yet

- Fdocuments - in - Review Paper On High Speed Karatsuba Multiplier and Vedic MultiplicationDocument5 pagesFdocuments - in - Review Paper On High Speed Karatsuba Multiplier and Vedic MultiplicationMahi BodanapuNo ratings yet

- Design and Implementation of FPGA Based 64-Bit MAC Unit Using VEDIC Multiplier and Reversible Logic GatesDocument8 pagesDesign and Implementation of FPGA Based 64-Bit MAC Unit Using VEDIC Multiplier and Reversible Logic GatesAmruth GhodkeNo ratings yet

- Journal RefDocument8 pagesJournal RefANAND P RNo ratings yet

- PX C 3904350Document6 pagesPX C 3904350Paramesh WaranNo ratings yet

- Design and Implementation of High Speed 32 Bit Vedic Arithmetic Unit On FPGADocument25 pagesDesign and Implementation of High Speed 32 Bit Vedic Arithmetic Unit On FPGAAshish Phuse100% (2)

- Implementation of Multiplier Using Vedic AlgorithmDocument5 pagesImplementation of Multiplier Using Vedic AlgorithmDwarakaManeekantaAddagiriNo ratings yet

- Vedic Mathematics Based Research PaperDocument4 pagesVedic Mathematics Based Research Paperarushi_somaniNo ratings yet

- Area and Speed Wise Superior Vedic Multiplier For FPGA Based Arithmetic CircuitsDocument6 pagesArea and Speed Wise Superior Vedic Multiplier For FPGA Based Arithmetic CircuitsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Application of Vedic Mathematics in Computer ArchitectureDocument6 pagesApplication of Vedic Mathematics in Computer ArchitectureInternational Journal of Research in Engineering and Science100% (1)

- Implementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA ToolDocument5 pagesImplementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA TooltechiealyyNo ratings yet

- PG Students Seminar-234Document20 pagesPG Students Seminar-234Sp SwainNo ratings yet

- Ijert Ijert: Design of 6 Bit Vedic Multiplier Using Vedic SutraDocument8 pagesIjert Ijert: Design of 6 Bit Vedic Multiplier Using Vedic Sutraerparveenkaur86No ratings yet

- Fast Combinational Architecture For A Vedic DividerDocument5 pagesFast Combinational Architecture For A Vedic DividerkopperundeviNo ratings yet

- Low Power 64bit Multiplier Design by Vedic MathematicsDocument4 pagesLow Power 64bit Multiplier Design by Vedic MathematicsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- FPGA and ASIC Vedic MultiplierDocument4 pagesFPGA and ASIC Vedic MultiplierJagannath KbNo ratings yet

- Reference 5Document12 pagesReference 5Ramesh NairNo ratings yet

- ASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsDocument10 pagesASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsNeem PlantNo ratings yet

- Implementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA ToolDocument5 pagesImplementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA Toolrbangaram_1No ratings yet

- An Efficient Bit Reduction Binary Multiplication Algorithm Using Vedic MethodsDocument4 pagesAn Efficient Bit Reduction Binary Multiplication Algorithm Using Vedic MethodsShubham MishraNo ratings yet

- Efficient Design of Single Precision Floating Point Multiplier PaperDocument6 pagesEfficient Design of Single Precision Floating Point Multiplier Papermohamedfisal7476No ratings yet

- Design of 32 Bit Vedic Multiplier Using Carry Look Ahead AdderDocument5 pagesDesign of 32 Bit Vedic Multiplier Using Carry Look Ahead AdderGRD JournalsNo ratings yet

- Booth EncoderDocument8 pagesBooth EncoderThahsin ThahirNo ratings yet

- Optimized High Performance Multiplier Using Vedic MathematicsDocument6 pagesOptimized High Performance Multiplier Using Vedic MathematicsPradeepNo ratings yet

- Design and Analysis of An Efficient 16-Bit MultiplierDocument6 pagesDesign and Analysis of An Efficient 16-Bit MultiplierChandra shekara mnNo ratings yet

- High Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDocument5 pagesHigh Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDrSakthivelNo ratings yet

- Low Power Square and Cube Architectures Using Vedic Sutras: G L, C - V R, R GDocument4 pagesLow Power Square and Cube Architectures Using Vedic Sutras: G L, C - V R, R GAshishKumarNo ratings yet

- Design of Fast Dadda Multiplier Using Vedic Mathematics: Sathish@svce - Ac.inDocument8 pagesDesign of Fast Dadda Multiplier Using Vedic Mathematics: Sathish@svce - Ac.inSohini RoyNo ratings yet

- Implementation of High Performance Binary Squarer: Pradeep M C, Ramesh SDocument7 pagesImplementation of High Performance Binary Squarer: Pradeep M C, Ramesh SAbhijeet KumarNo ratings yet

- A Reconfigurable Coprocessor For Redundant Radix-4 ArithmeticDocument24 pagesA Reconfigurable Coprocessor For Redundant Radix-4 ArithmeticManish BansalNo ratings yet

- Design For 4-Bit Vedic Multiplier Using VHDL ModuleDocument12 pagesDesign For 4-Bit Vedic Multiplier Using VHDL Modulekathik goudNo ratings yet

- A Reduced-Bit Multiplication Algorithm For Digital ArithmeticDocument6 pagesA Reduced-Bit Multiplication Algorithm For Digital ArithmeticSanthosh KumarNo ratings yet

- MBE ReportDocument25 pagesMBE ReportasreemadhuriNo ratings yet

- Design and Implementation of Efficient 4x4 Vedic Multiplier For DSP ApplicationsDocument6 pagesDesign and Implementation of Efficient 4x4 Vedic Multiplier For DSP Applicationsrakesh hiremathNo ratings yet

- Ijece V3i3p103Document4 pagesIjece V3i3p103Ram RamNo ratings yet

- Mhairul, 004Document7 pagesMhairul, 004Harish NayakNo ratings yet

- PJCTTDocument5 pagesPJCTTSharmila ReddyNo ratings yet

- Vedic Maths in Digital Signal ProcessingDocument6 pagesVedic Maths in Digital Signal ProcessingSwanand RaikarNo ratings yet

- Implementation of 24 Bit High Speed Floating Point Vedic MultiplierDocument5 pagesImplementation of 24 Bit High Speed Floating Point Vedic MultiplierNam LeNo ratings yet

- Mini-Project Report FinalDocument36 pagesMini-Project Report FinalRDUNo ratings yet

- Ijert Ijert: Performance Evaluation and Comparison of Multipliers Using Vedic AlgorithmsDocument5 pagesIjert Ijert: Performance Evaluation and Comparison of Multipliers Using Vedic AlgorithmsRajesh BathijaNo ratings yet

- Design and Implementation of High Speed Vedic Multiplier Using Brent Kung Adder On FPGADocument4 pagesDesign and Implementation of High Speed Vedic Multiplier Using Brent Kung Adder On FPGAIJSTENo ratings yet

- Comparative Study of Single Precision Floating Point Division Using Different Computational AlgorithmsDocument9 pagesComparative Study of Single Precision Floating Point Division Using Different Computational AlgorithmsIJRES teamNo ratings yet

- A Noval Approach of FFTDocument3 pagesA Noval Approach of FFTSijo MathewNo ratings yet

- IJMET 09 10 014ggggggggggggggDocument11 pagesIJMET 09 10 014ggggggggggggggAhmad AlasadiNo ratings yet

- Residue To Binary Converter For A Four Moduli SetDocument12 pagesResidue To Binary Converter For A Four Moduli SetIJRASETPublicationsNo ratings yet

- Design and Analysis of High Speed, Area Optimized 32x32-Bit Multiply Accumulate Unit Based On Vedic MathematicsDocument5 pagesDesign and Analysis of High Speed, Area Optimized 32x32-Bit Multiply Accumulate Unit Based On Vedic MathematicsAneesh Raveendran100% (1)

- Tomar2017 18 PDFDocument13 pagesTomar2017 18 PDFPriya SinghNo ratings yet

- Paper 15282Document7 pagesPaper 15282publishlambertNo ratings yet

- Implementation of High-Speed Modified Radix-8 Booth Multiplier For Signed and Unsigned NumbersDocument9 pagesImplementation of High-Speed Modified Radix-8 Booth Multiplier For Signed and Unsigned NumbersRajeshwar DhankarNo ratings yet

- Acquired Experiences With Computational Tool MS SV Used in Electronic Circuit DesignDocument12 pagesAcquired Experiences With Computational Tool MS SV Used in Electronic Circuit DesignKhadar BashaNo ratings yet

- SPSTDocument40 pagesSPSTpraveen4a0No ratings yet

- Entrepreneurial India: An Overview of Pre - Post Independence and Contemporary Small-Scale EnterprisesDocument8 pagesEntrepreneurial India: An Overview of Pre - Post Independence and Contemporary Small-Scale EnterprisesInternational Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Computations in Quotient RingsDocument7 pagesComputations in Quotient RingsInternational Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Analysis of Water Quality Parameters of Ground and Surface Water in Siltara Industrial Area, Raipur, Chhattisgarh, INDIADocument8 pagesAnalysis of Water Quality Parameters of Ground and Surface Water in Siltara Industrial Area, Raipur, Chhattisgarh, INDIAInternational Journal of Creative Mathematical Sciences and Technology100% (1)

- New Row Maxima Method To Solve Multi-Objective Transportation Problem Under Fuzzy Conditions A. J. Khan and D. K. Das Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 42 - 46Document5 pagesNew Row Maxima Method To Solve Multi-Objective Transportation Problem Under Fuzzy Conditions A. J. Khan and D. K. Das Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 42 - 46International Journal of Creative Mathematical Sciences and Technology100% (1)

- Editorial MemberDocument1 pageEditorial MemberInternational Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Surface Roughness Analysis in Machining of Glass Fiber Reinforced Epoxy Composite With Carbide Tool Using Taguchi A. K. Parida Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 67 - 73Document7 pagesSurface Roughness Analysis in Machining of Glass Fiber Reinforced Epoxy Composite With Carbide Tool Using Taguchi A. K. Parida Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 67 - 73International Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Kinetic Study of Carboxylate Ester With Hydroxamate Ions in Cationic Micro-Emulsion System D. K. Pandey, C. S. Meshram and S. Biswas Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 34 - 41Document8 pagesKinetic Study of Carboxylate Ester With Hydroxamate Ions in Cationic Micro-Emulsion System D. K. Pandey, C. S. Meshram and S. Biswas Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 34 - 41International Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Exercise Set 2.1Document26 pagesExercise Set 2.1hassan.muradNo ratings yet

- CHENG Field and Wave Electromagnetics ChengDocument515 pagesCHENG Field and Wave Electromagnetics ChengSanJeev Dani PeDrosa100% (1)

- Math 231 Section 4.1 (Sol)Document8 pagesMath 231 Section 4.1 (Sol)a.abouelenin3009No ratings yet

- Quadratic Simultaneous EquationsDocument19 pagesQuadratic Simultaneous EquationsSri Devi NagarjunaNo ratings yet

- Chapter - 1.6 Repetitive StructuresDocument93 pagesChapter - 1.6 Repetitive StructureshaileyNo ratings yet

- Prof. AR Rao Mathematics Comp.-2019 (Fysy) and Prof. AR Rao Maths Project Comp.-2019 NotificationsDocument4 pagesProf. AR Rao Mathematics Comp.-2019 (Fysy) and Prof. AR Rao Maths Project Comp.-2019 NotificationsJAY BHARATBHAI LAKHANINo ratings yet

- Paper On Navier-Stokes EquationsDocument11 pagesPaper On Navier-Stokes EquationsVSTomarNo ratings yet

- CARBayes STDocument37 pagesCARBayes STSiswanto HarvardNo ratings yet

- Degrees of Freedom and Precedence OrdersDocument8 pagesDegrees of Freedom and Precedence OrdersRITA ANGELICA JIMENEZ FERRONo ratings yet

- Partial Differential Equations and Finite Difference MethodsDocument15 pagesPartial Differential Equations and Finite Difference MethodsHozan MuhammadNo ratings yet

- MATHEMATICS (2nd Quarterly Examination) - Grade 7-10Document11 pagesMATHEMATICS (2nd Quarterly Examination) - Grade 7-10Gian HipolitoNo ratings yet

- Model TheoryDocument73 pagesModel TheoryMizanur RahmanNo ratings yet

- On The Mathematical Foundations of Electrical Circuit TheoryDocument18 pagesOn The Mathematical Foundations of Electrical Circuit TheorysdNo ratings yet

- Nov 2003 P2Document12 pagesNov 2003 P2api-26543952No ratings yet

- Unit 1 Module 1 FeaDocument53 pagesUnit 1 Module 1 FeaBharathi KannaNo ratings yet

- Information Booklet 2023 Latest by 02.05.23Document12 pagesInformation Booklet 2023 Latest by 02.05.23mahesh.revisitNo ratings yet

- ASO Sample Questions by AchieversDocument2 pagesASO Sample Questions by AchieversMks ViratNo ratings yet

- Factoring Quadratic Expressions HomeworkDocument6 pagesFactoring Quadratic Expressions Homeworkcfd13b82100% (1)

- University of Applied Sciences AustriaDocument2 pagesUniversity of Applied Sciences AustriaGerman Language SchoolNo ratings yet

- Module 2-Data ScienceDocument3 pagesModule 2-Data ScienceAerol MagpileNo ratings yet

- Trapezoids Talk - A Paper by Michael KeytonDocument7 pagesTrapezoids Talk - A Paper by Michael KeytonAbhi Ram100% (1)

- A Spurious Power Suppression Technique ForDocument8 pagesA Spurious Power Suppression Technique Forapi-19929244No ratings yet

- DPP - 40 - MDocument2 pagesDPP - 40 - Mshalini singhNo ratings yet

- Two Pairs of Archimedean Circles in The ArbelosDocument2 pagesTwo Pairs of Archimedean Circles in The ArbelosDũng Nguyễn TiếnNo ratings yet

- Lecture Notes em Fields Nov 2012Document153 pagesLecture Notes em Fields Nov 2012Nithindev GuttikondaNo ratings yet

- Setting Out CurvesDocument2 pagesSetting Out CurvesMemNo ratings yet

- First Order Logic: Artificial Intelligence COSC-3112 Ms. Humaira AnwerDocument24 pagesFirst Order Logic: Artificial Intelligence COSC-3112 Ms. Humaira AnwerKhizrah RafiqueNo ratings yet

- Math 20-1 Formula SheetDocument2 pagesMath 20-1 Formula SheetTayson PreteNo ratings yet

- Thoughts Upon Reading Marko RodinDocument17 pagesThoughts Upon Reading Marko Rodinreflatus13100% (3)

Vedic Multiplier

Vedic Multiplier

Uploaded by

muthuraj14007Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Vedic Multiplier

Vedic Multiplier

Uploaded by

muthuraj14007Copyright:

Available Formats

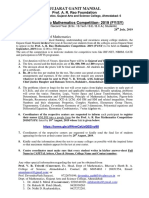

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

Urdhva Triyakbhyam Sutra: Application of Vedic Mathematics for a

High Speed Multiplier

R. Senapati1, B. K. Bhoi2

1, 2

VSS University of Technology, Burla, Odisha, India

Abstract: This paper proposed the design of high speed Vedic Multiplier using the

techniques of Ancient Indian Vedic Mathematics that have been modified to improve

performance. Vedic Mathematics is the ancient system of mathematics which has a

unique technique of calculations based on 16 Sutras. The work has proved the efficiency

of Urdhva Triyagbhyam- Vedic method for multiplication which strikes a difference in

the actual process of multiplication itself. It enables parallel generation of intermediate

products, eliminates unwanted multiplication steps with zeros and scaled to higher bit

levels using Karatsuba algorithm with the compatibility to different data types. Urdhva

tiryakbhyam Sutra is most efficient Sutra (Algorithm), giving minimum delay for

multiplication of all types of numbers, either small or large. Further, the Verilog HDL

coding of Urdhva tiryakbhyam Sutra for 32x32 bits multiplication and their FPGA

implementation by Xilinx Synthesis Tool on Spartan 3E kit have been done. The

synthesis results show that the computation time for calculating the product of 32x32 bits

is 29.256 ns.

Keywords: Vedic mathematics, urdhva triyakbhyam sutra, karatsuba - ofman algorithm.

INTRODUCTION

Multiplication is an important fundamental function in arithmetic operations. Multiplicationbased operations such as Multiply and Accumulate(MAC) and inner product are among some of

the frequently used ComputationIntensive Arithmetic Functions(CIAF) currently implemented in

many Digital Signal Processing (DSP) applications such as convolution, Fast Fourier

Transform(FFT), filtering and in microprocessors in its arithmetic and logic unit [1]. Since

multiplication dominates the execution time of most DSP algorithms, so there is a need of high

speed multiplier. Currently, multiplication time is still the dominant factor in determining the

instruction cycle time of a DSP chip.

The demand for high speed processing has been increasing as a result of expanding computer

and signal processing applications. Higher throughput arithmetic operations are important to

achieve the desired performance in many real-time signal and image processing applications [2].

One of the key arithmetic operations in such applications is multiplication and the development

of fast multiplier circuit has been a subject of interest over decades. Reducing the time delay and

power consumption are very essential requirements for many applications [2, 3]. This work

presents different multiplier architectures. Multiplier based on Vedic Mathematics is one of the

fast and low power multiplier. Minimizing power consumption for digital systems involves

optimization at all levels of the design. This optimization includes the technology used to

implement the digital circuits, the circuit style and topology, the architecture for implementing

59

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

the circuits and at the highest level the algorithms that are being implemented. Digital multipliers

are the most commonly used components in any digital circuit design. They are fast, reliable and

efficient components that are utilized to implement any operation. Depending upon the

arrangement of the components, there are different types of multipliers available. Particular

multiplier architecture is chosen based on the application.

In many DSP algorithms, the multiplier lies in the critical delay path and ultimately determines

the performance of algorithm. The speed of multiplication operation is of great importance in

DSP as well as in general processor. In the past multiplication was implemented generally with a

sequence of addition, subtraction and shift operations. There have been many algorithms

proposals in literature to perform multiplication, each offering different advantages and having

tradeoff in terms of speed, circuit complexity, area and power consumption.

The multiplier is a fairly large block of a computing system. The amount of circuitry involved

is directly proportional to the square of its resolution i.e. A multiplier of size n bits has n2 gates.

For multiplication algorithms performed in DSP applications latency and throughput are the two

major concerns from delay perspective. Latency is the real delay of computing a function, a

measure of how long the inputs to a device are stable is the final result available on outputs.

Throughput is the measure of how many multiplications can be performed in a given period of

time; multiplier is not only a high delay block but also a major source of power dissipation.

That's why if one also aims to minimize power consumption, it is of great interest to reduce the

delay by using various delay optimizations.

Digital multipliers are the core components of all the digital signal processors (DSPs) and the

speed of the DSP is largely determined by the speed of its multipliers[9]. Two most common

multiplication algorithms followed in the digital hardware are array multiplication algorithm and

Booth multiplication algorithm. The computation time taken by the array multiplier is

comparatively less because the partial products are calculated independently in parallel. The

delay associated with the array multiplier is the time taken by the signals to propagate through

the gates that form the multiplication array. Booth multiplication is another important

multiplication algorithm. Large booth arrays are required for high speed multiplication and

exponential operations which in turn require large partial sum and partial carry registers.

Multiplication of two n-bit operands using a radix-4 booth recording multiplier requires

approximately n / (2m) clock cycles to generate the least significant half of the final product,

where m is the number of Booth recorder adder stages. Thus, a large propagation delay is

associated with this case. Due to the importance of digital multipliers in DSP, it has always been

an active area of research and a number of interesting multiplication algorithms have been

reported in the literature [4].

In this, Urdhva tiryakbhyam Sutra is first applied to the binary number system and is used to

develop digital multiplier architecture. This is shown to be very similar to the popular array

multiplier architecture. This Sutra also shows the effectiveness of to reduce the NXN multiplier

structure into an efficient 4X4 multiplier structures. Nikhilam Sutra is then discussed and is

shown to be much more efficient in the multiplication of large numbers as it reduces the

multiplication of two large numbers to that of two smaller ones. The proposed multiplication

algorithm is then illustrated to show its computational efficiency by taking an example of

reducing a 4X4-bit multiplication to a single 2X2-bit multiplication operation [4]. This work

60

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

presents a systematic design methodology for fast and area efficient digit multiplier based on

Vedic mathematics .The Multiplier Architecture is based on the Vertical and Crosswise

algorithm of ancient Indian Vedic Mathematics [5].

VEDIC MATHEMATICS

Vedic mathematics is part of four Vedas (books of wisdom). It is part of Sthapatya- Veda

(book on civil engineering and architecture), which is an upa-veda (supplement) of Atharva

Veda. It gives explanation of several mathematical terms including arithmetic, geometry (plane,

co-ordinate), trigonometry, quadratic equations, factorization and even calculus.

His Holiness Jagadguru Shankaracharya Bharati Krishna Teerthaji Maharaja (1884- 1960)

comprised all this work together and gave its mathematical explanation while discussing it for

various applications. Swamiji constructed 16 sutras (formulae) and 16 Upa sutras (sub formulae)

after extensive research in Atharva Veda. Obviously these formulae are not to be found in

present text of Atharva Veda because these formulae were constructed by Swamiji himself.

Vedic mathematics is not only a mathematical wonder but also it is logical. Thats why it has

such a degree of eminence which cannot be disapproved. Due these phenomenal characteristics,

Vedic maths has already crossed the boundaries of India and has become an interesting topic of

research abroad. Vedic maths deals with several basic as well as complex mathematical

operations. Especially, methods of basic arithmetic are extremely simple and powerful [2, 3].

The word Vedic is derived from the word Veda which means the store-house of all

knowledge. Vedic mathematics is mainly based on 16 Sutras (or aphorisms) dealing with various

branches of mathematics like arithmetic, algebra, geometry etc. These methods and ideas can be

directly applied to trigonometry, plain and spherical geometry, conics, calculus (both differential

and integral), and applied mathematics of various kinds. As mentioned earlier, all these Sutras

were reconstructed from ancient Vedic texts early in the last century. Many Sub-sutras were also

discovered at the same time, which are not discussed here. The beauty of Vedic mathematics lies

in the fact that it reduces the otherwise cumbersome-looking calculations in conventional

mathematics to a very simple one. This is so because the Vedic formulae are claimed to be based

on the natural principles on which the human mind works. This is a very interesting field and

presents some effective algorithms which can be applied to various branches of engineering such

as computing and digital signal processing [ 1,4].

The multiplier architecture can be generally classified into three categories. First is the serial

multiplier which emphasizes on hardware and minimum amount of chip area. Second is parallel

multiplier (array and tree) which carries out high speed mathematical operations. But the

drawback is the relatively larger chip area consumption. Third is serial- parallel multiplier which

serves as a good trade-off between the times consuming serial multiplier and the area consuming

parallel multipliers.

61

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

DESIGN OF VEDIC MULTIPLIER

A. Urdhva-Triyagbhyam (Vertically and Crosswise)

Urdhva tiryakbhyam Sutra is a general multiplication formula applicable to all cases of

multiplication. It literally means Vertically and Crosswise. To illustrate this multiplication

scheme, let us consider the multiplication of two decimal numbers (5498 x 2314). The

conventional methods already know to us will require 16 multiplications and 15 additions.

An alternative method of multiplication using Urdhva tiryakbhyam Sutra is shown in Fig. 1. The

numbers to be multiplied are written on two consecutive sides of the square as shown in the

figure. The square is divided into rows and columns where each row/column corresponds to one

of the digit of either a multiplier or a multiplicand. Thus, each digit of the multiplier has a small

box common to a digit of the multiplicand. These small boxes are partitioned into two halves by

the crosswise lines. Each digit of the multiplier is then independently multiplied with every digit

of the multiplicand and the two-digit product is written in the common box. All the digits lying

on a crosswise dotted line are added to the previous carry. The least significant digit of the

obtained number acts as the result digit and the rest as the carry for the next step. Carry for the

first step (i.e., the dotted line on the extreme right side) is taken to be zero [9].

62

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

The design starts first with Multiplier design, that is 2x2 bit multiplier as shown in figure 2.

Here, Urdhva Tiryakbhyam Sutra or Vertically and Crosswise Algorithm[4] for

multiplication has been effectively used to develop digital multiplier architecture. This algorithm

is quite different from the traditional method of multiplication, which is to add and shift the

partial products.

63

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

To scale the multiplier further, Karatsuba - Ofman algorithm can be employed [6]. KaratsubaOfman algorithm is considered as one of the fastest ways to multiply long integers. It is based on

the divide and conquer strategy [9]. A multiplication of 2n digit integer is reduced to two n digit

multiplications, one (n+1) digit multiplication, two n digit subtractions, two left shift operations,

two n digit additions and two 2n digit additions.

The algorithm can be explained as follows:

Let X and Y are the binary representation of two long integers:

k 1

X xi 2

i 0

k 1

Y y

i 0

We wish to compute the product XY. Using the divide and conquer strategy, the operands X and

Y can be decomposed into equal size parts XH and XL, YH and YL, where subscripts H and L

represent high and low order bits of X and Y respectively.

Let k= 2n. If k is odd, it can be right padded with a zero.

n

X 2

Y 2

n 1

x 2

in

i 0

n 1

n 1

xi 2 X H 2 n X L

i 0

n 1

y 2 y 2 Y

i 0

i n

i 0

2 n YL

The product XY can be computed as follows:

P X *Y

( X H 2 n X L )(YH 2 n YL )

For Multiplier, first the basic blocks, that are the 2x2 bit multipliers have been made and then,

using these blocks, 4x4 block has been made by adding the partial products using carry save

adders and then using this 4x4 block, 8x8 bit block, 16x16 bit block and then finally 32 x 32 bit

Multiplier as shown in figure 3 has been made [7].

IMPLEMENTATION OF VEDIC MULTIPLIER

The proposed multiplications were implemented using two different coding techniques viz.,

conventional shift & add and Vedic technique for 4, 8, 16, and 32 bit multipliers. It is evident

that there is a considerable increase in speed of the Vedic architecture.

64

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

Size

8 bit

16 bit

32 bit

Algorithm

Karatsuba Algorithm

Optimized Vedic Multiplier

Karatsuba Algorithm

Optimized Vedic Multiplier

Karatsuba Algorithm

Optimized Vedic Multiplier

Delay in ns

31.029

13.418

46.811

20.643

82.231

29.256

Table 1: Delay Composition for different multiplier

The worst case propagation delay in the Optimized Vedic multiplier case was found to be

29.256ns. To compare it with other implementations the design was synthesized on XILINX:

SPARTAN: xc3s500e-5fg320[17]. Table 1 shows the synthesis result for various

implementations. The result obtained from proposed Vedic multiplier is faster than Karatsuba

Algorithm.

CONCLUSION

The designs of 32x32 bits Vedic multiplier have been implemented on Spartan XC3S500-5FG320. The design is based on Vedic method of multiplication [3]. The worst case propagation

delay in the Optimized Vedic multiplier case is 31.526ns. It is therefore seen that the Vedic

multipliers are much more faster than the conventional multipliers. This gives us method for

hierarchical multiplier design. So the design complexity gets reduced for inputs of large no of

bits and modularity gets increased. Urdhva tiryakbhyam, Nikhilam and Anurupye sutras are such

algorithms which can reduce the delay, power and hardware requirements for multiplication of

numbers. FPGA implementation of this multiplier shows that hardware realization of the Vedic

mathematics algorithms is easily possible. The high speed multiplier algorithm exhibits improved

efficiency in terms of speed.

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

Wallace, C.S., A suggestion for a fast multiplier, IEEE Trans. Elec. Comput., vol. EC-13,

no. 1, pp. 14-17, Feb. 1964.

Booth, A.D., A signed binary multiplication technique, Quarterly Journal of Mechanics

and Applied Mathematics, vol. 4, pt. 2, pp. 236- 240, 1951.

Jagadguru Swami Sri Bharath, Krsna Tirathji, Vedic Mathematics or Sixteen Simple

Sutras From The Vedas, Motilal Banarsidas, Varanasi(India),1986.

A.P. Nicholas, K.R Williams, J. Pickles, Application of Urdhava Sutra, Spiritual Study

Group, Roorkee (India),1984.

Neil H.E Weste, David Harris, Ayan anerjee,CMOS VLSI Design, A Circuits and

Systems Perspective,Third Edition, Published by Person Education, PP-327-328]

Mrs. M. Ramalatha, Prof. D. Sridharan, VLSI Based High Speed Karatsuba Multiplier for

Cryptographic Applications Using Vedic Mathematics, IJSCI, 2007

M.C. Hanumantharaju, H. Jayalaxmi, R.K. Renuka, M. Ravishankar, "A High Speed Block

65

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

International Journal of Creative Mathematical Sciences & Technology (IJCMST) 1(1): 59-66, 2012

ISSN (P): 2319 7811, ISSN (O): 2319 782X

[8]

[9]

Convolution Using Ancient Indian Vedic Mathematics," ICCIMA, vol. 2, pp.169-173,

International Conference on Computational Intelligence and Multimedia Applications,

2007.

Harpreet Singh Dhilon And Abhijit Mitra,A Reduced-Bit Multiplication Algorithm For

Digital Arithmetic International Journal of Computational and Mathematical Sciences,

Waset, Spring, 2008.

S. Kumaravel, Ramalatha Marimuthu, "VLSI Implementation of High Performance RSA

Algorithm Using Vedic Mathematics," ICCIMA, vol. 4,pp.126-128, International

Conference on Computational Intelligence and Multimedia Applications (ICCIMA 2007),

2007.

66

Corresponding Author: R. Senapati, VSS University of Technology,

Burla, Odisha, India

You might also like

- Lemmon AnswersDocument12 pagesLemmon Answersrichard33% (3)

- Design of High Speed Vedic Multiplier Using Vedic Mathematics TechniquesDocument5 pagesDesign of High Speed Vedic Multiplier Using Vedic Mathematics TechniquesPramod KumarNo ratings yet

- Vedic Algorithms To Develop Green Chips For FutureDocument3 pagesVedic Algorithms To Develop Green Chips For FutureeditorijsaaNo ratings yet

- DSP Operation Using Vedic MathematicsDocument78 pagesDSP Operation Using Vedic Mathematicsnaveen mNo ratings yet

- Design, Implementation and Performance Analysis of An Integrated Vedic Multiplier ArchitectureDocument7 pagesDesign, Implementation and Performance Analysis of An Integrated Vedic Multiplier ArchitectureAbhijeet KumarNo ratings yet

- Performance Analysis of Vedic Multiplier in Hardware Implementation of Biomedical ApplicationsDocument4 pagesPerformance Analysis of Vedic Multiplier in Hardware Implementation of Biomedical ApplicationsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- VLSI Implementation of Vedic Multiplier Using Urdhva - Tiryakbhyam Sutra in VHDL Environment: A NoveltyDocument8 pagesVLSI Implementation of Vedic Multiplier Using Urdhva - Tiryakbhyam Sutra in VHDL Environment: A NoveltyInternational Organization of Scientific Research (IOSR)No ratings yet

- Performance Analysis of Vedic Multiplier in Signal Processing ApplicationsDocument4 pagesPerformance Analysis of Vedic Multiplier in Signal Processing ApplicationsInternational Journal of Innovative Science and Research TechnologyNo ratings yet

- Literature Survey: Preyesh Dalmia Et Al (2018)Document3 pagesLiterature Survey: Preyesh Dalmia Et Al (2018)yuvaraaj aletiNo ratings yet

- Fdocuments - in - Review Paper On High Speed Karatsuba Multiplier and Vedic MultiplicationDocument5 pagesFdocuments - in - Review Paper On High Speed Karatsuba Multiplier and Vedic MultiplicationMahi BodanapuNo ratings yet

- Design and Implementation of FPGA Based 64-Bit MAC Unit Using VEDIC Multiplier and Reversible Logic GatesDocument8 pagesDesign and Implementation of FPGA Based 64-Bit MAC Unit Using VEDIC Multiplier and Reversible Logic GatesAmruth GhodkeNo ratings yet

- Journal RefDocument8 pagesJournal RefANAND P RNo ratings yet

- PX C 3904350Document6 pagesPX C 3904350Paramesh WaranNo ratings yet

- Design and Implementation of High Speed 32 Bit Vedic Arithmetic Unit On FPGADocument25 pagesDesign and Implementation of High Speed 32 Bit Vedic Arithmetic Unit On FPGAAshish Phuse100% (2)

- Implementation of Multiplier Using Vedic AlgorithmDocument5 pagesImplementation of Multiplier Using Vedic AlgorithmDwarakaManeekantaAddagiriNo ratings yet

- Vedic Mathematics Based Research PaperDocument4 pagesVedic Mathematics Based Research Paperarushi_somaniNo ratings yet

- Area and Speed Wise Superior Vedic Multiplier For FPGA Based Arithmetic CircuitsDocument6 pagesArea and Speed Wise Superior Vedic Multiplier For FPGA Based Arithmetic CircuitsInternational Journal of computational Engineering research (IJCER)No ratings yet

- Application of Vedic Mathematics in Computer ArchitectureDocument6 pagesApplication of Vedic Mathematics in Computer ArchitectureInternational Journal of Research in Engineering and Science100% (1)

- Implementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA ToolDocument5 pagesImplementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA TooltechiealyyNo ratings yet

- PG Students Seminar-234Document20 pagesPG Students Seminar-234Sp SwainNo ratings yet

- Ijert Ijert: Design of 6 Bit Vedic Multiplier Using Vedic SutraDocument8 pagesIjert Ijert: Design of 6 Bit Vedic Multiplier Using Vedic Sutraerparveenkaur86No ratings yet

- Fast Combinational Architecture For A Vedic DividerDocument5 pagesFast Combinational Architecture For A Vedic DividerkopperundeviNo ratings yet

- Low Power 64bit Multiplier Design by Vedic MathematicsDocument4 pagesLow Power 64bit Multiplier Design by Vedic MathematicsInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- FPGA and ASIC Vedic MultiplierDocument4 pagesFPGA and ASIC Vedic MultiplierJagannath KbNo ratings yet

- Reference 5Document12 pagesReference 5Ramesh NairNo ratings yet

- ASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsDocument10 pagesASIC Design of A High Speed Low Power Circuit For Factorial Calculation Using Ancient Vedic MathematicsNeem PlantNo ratings yet

- Implementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA ToolDocument5 pagesImplementation of An Efficient Multiplier Based On Vedic Mathematics Using EDA Toolrbangaram_1No ratings yet

- An Efficient Bit Reduction Binary Multiplication Algorithm Using Vedic MethodsDocument4 pagesAn Efficient Bit Reduction Binary Multiplication Algorithm Using Vedic MethodsShubham MishraNo ratings yet

- Efficient Design of Single Precision Floating Point Multiplier PaperDocument6 pagesEfficient Design of Single Precision Floating Point Multiplier Papermohamedfisal7476No ratings yet

- Design of 32 Bit Vedic Multiplier Using Carry Look Ahead AdderDocument5 pagesDesign of 32 Bit Vedic Multiplier Using Carry Look Ahead AdderGRD JournalsNo ratings yet

- Booth EncoderDocument8 pagesBooth EncoderThahsin ThahirNo ratings yet

- Optimized High Performance Multiplier Using Vedic MathematicsDocument6 pagesOptimized High Performance Multiplier Using Vedic MathematicsPradeepNo ratings yet

- Design and Analysis of An Efficient 16-Bit MultiplierDocument6 pagesDesign and Analysis of An Efficient 16-Bit MultiplierChandra shekara mnNo ratings yet

- High Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDocument5 pagesHigh Speed Reconfigurable FFT Design by Vedic Mathematics: Ashish Raman, Anvesh Kumar and R.K.SarinDrSakthivelNo ratings yet

- Low Power Square and Cube Architectures Using Vedic Sutras: G L, C - V R, R GDocument4 pagesLow Power Square and Cube Architectures Using Vedic Sutras: G L, C - V R, R GAshishKumarNo ratings yet

- Design of Fast Dadda Multiplier Using Vedic Mathematics: Sathish@svce - Ac.inDocument8 pagesDesign of Fast Dadda Multiplier Using Vedic Mathematics: Sathish@svce - Ac.inSohini RoyNo ratings yet

- Implementation of High Performance Binary Squarer: Pradeep M C, Ramesh SDocument7 pagesImplementation of High Performance Binary Squarer: Pradeep M C, Ramesh SAbhijeet KumarNo ratings yet

- A Reconfigurable Coprocessor For Redundant Radix-4 ArithmeticDocument24 pagesA Reconfigurable Coprocessor For Redundant Radix-4 ArithmeticManish BansalNo ratings yet

- Design For 4-Bit Vedic Multiplier Using VHDL ModuleDocument12 pagesDesign For 4-Bit Vedic Multiplier Using VHDL Modulekathik goudNo ratings yet

- A Reduced-Bit Multiplication Algorithm For Digital ArithmeticDocument6 pagesA Reduced-Bit Multiplication Algorithm For Digital ArithmeticSanthosh KumarNo ratings yet

- MBE ReportDocument25 pagesMBE ReportasreemadhuriNo ratings yet

- Design and Implementation of Efficient 4x4 Vedic Multiplier For DSP ApplicationsDocument6 pagesDesign and Implementation of Efficient 4x4 Vedic Multiplier For DSP Applicationsrakesh hiremathNo ratings yet

- Ijece V3i3p103Document4 pagesIjece V3i3p103Ram RamNo ratings yet

- Mhairul, 004Document7 pagesMhairul, 004Harish NayakNo ratings yet

- PJCTTDocument5 pagesPJCTTSharmila ReddyNo ratings yet

- Vedic Maths in Digital Signal ProcessingDocument6 pagesVedic Maths in Digital Signal ProcessingSwanand RaikarNo ratings yet

- Implementation of 24 Bit High Speed Floating Point Vedic MultiplierDocument5 pagesImplementation of 24 Bit High Speed Floating Point Vedic MultiplierNam LeNo ratings yet

- Mini-Project Report FinalDocument36 pagesMini-Project Report FinalRDUNo ratings yet

- Ijert Ijert: Performance Evaluation and Comparison of Multipliers Using Vedic AlgorithmsDocument5 pagesIjert Ijert: Performance Evaluation and Comparison of Multipliers Using Vedic AlgorithmsRajesh BathijaNo ratings yet

- Design and Implementation of High Speed Vedic Multiplier Using Brent Kung Adder On FPGADocument4 pagesDesign and Implementation of High Speed Vedic Multiplier Using Brent Kung Adder On FPGAIJSTENo ratings yet

- Comparative Study of Single Precision Floating Point Division Using Different Computational AlgorithmsDocument9 pagesComparative Study of Single Precision Floating Point Division Using Different Computational AlgorithmsIJRES teamNo ratings yet

- A Noval Approach of FFTDocument3 pagesA Noval Approach of FFTSijo MathewNo ratings yet

- IJMET 09 10 014ggggggggggggggDocument11 pagesIJMET 09 10 014ggggggggggggggAhmad AlasadiNo ratings yet

- Residue To Binary Converter For A Four Moduli SetDocument12 pagesResidue To Binary Converter For A Four Moduli SetIJRASETPublicationsNo ratings yet

- Design and Analysis of High Speed, Area Optimized 32x32-Bit Multiply Accumulate Unit Based On Vedic MathematicsDocument5 pagesDesign and Analysis of High Speed, Area Optimized 32x32-Bit Multiply Accumulate Unit Based On Vedic MathematicsAneesh Raveendran100% (1)

- Tomar2017 18 PDFDocument13 pagesTomar2017 18 PDFPriya SinghNo ratings yet

- Paper 15282Document7 pagesPaper 15282publishlambertNo ratings yet

- Implementation of High-Speed Modified Radix-8 Booth Multiplier For Signed and Unsigned NumbersDocument9 pagesImplementation of High-Speed Modified Radix-8 Booth Multiplier For Signed and Unsigned NumbersRajeshwar DhankarNo ratings yet

- Acquired Experiences With Computational Tool MS SV Used in Electronic Circuit DesignDocument12 pagesAcquired Experiences With Computational Tool MS SV Used in Electronic Circuit DesignKhadar BashaNo ratings yet

- SPSTDocument40 pagesSPSTpraveen4a0No ratings yet

- Entrepreneurial India: An Overview of Pre - Post Independence and Contemporary Small-Scale EnterprisesDocument8 pagesEntrepreneurial India: An Overview of Pre - Post Independence and Contemporary Small-Scale EnterprisesInternational Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Computations in Quotient RingsDocument7 pagesComputations in Quotient RingsInternational Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Analysis of Water Quality Parameters of Ground and Surface Water in Siltara Industrial Area, Raipur, Chhattisgarh, INDIADocument8 pagesAnalysis of Water Quality Parameters of Ground and Surface Water in Siltara Industrial Area, Raipur, Chhattisgarh, INDIAInternational Journal of Creative Mathematical Sciences and Technology100% (1)

- New Row Maxima Method To Solve Multi-Objective Transportation Problem Under Fuzzy Conditions A. J. Khan and D. K. Das Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 42 - 46Document5 pagesNew Row Maxima Method To Solve Multi-Objective Transportation Problem Under Fuzzy Conditions A. J. Khan and D. K. Das Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 42 - 46International Journal of Creative Mathematical Sciences and Technology100% (1)

- Editorial MemberDocument1 pageEditorial MemberInternational Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Surface Roughness Analysis in Machining of Glass Fiber Reinforced Epoxy Composite With Carbide Tool Using Taguchi A. K. Parida Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 67 - 73Document7 pagesSurface Roughness Analysis in Machining of Glass Fiber Reinforced Epoxy Composite With Carbide Tool Using Taguchi A. K. Parida Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 67 - 73International Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Kinetic Study of Carboxylate Ester With Hydroxamate Ions in Cationic Micro-Emulsion System D. K. Pandey, C. S. Meshram and S. Biswas Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 34 - 41Document8 pagesKinetic Study of Carboxylate Ester With Hydroxamate Ions in Cationic Micro-Emulsion System D. K. Pandey, C. S. Meshram and S. Biswas Volume - 1, Number - 1 Publication Year: 2012, Page(s) : 34 - 41International Journal of Creative Mathematical Sciences and TechnologyNo ratings yet

- Exercise Set 2.1Document26 pagesExercise Set 2.1hassan.muradNo ratings yet

- CHENG Field and Wave Electromagnetics ChengDocument515 pagesCHENG Field and Wave Electromagnetics ChengSanJeev Dani PeDrosa100% (1)

- Math 231 Section 4.1 (Sol)Document8 pagesMath 231 Section 4.1 (Sol)a.abouelenin3009No ratings yet

- Quadratic Simultaneous EquationsDocument19 pagesQuadratic Simultaneous EquationsSri Devi NagarjunaNo ratings yet

- Chapter - 1.6 Repetitive StructuresDocument93 pagesChapter - 1.6 Repetitive StructureshaileyNo ratings yet

- Prof. AR Rao Mathematics Comp.-2019 (Fysy) and Prof. AR Rao Maths Project Comp.-2019 NotificationsDocument4 pagesProf. AR Rao Mathematics Comp.-2019 (Fysy) and Prof. AR Rao Maths Project Comp.-2019 NotificationsJAY BHARATBHAI LAKHANINo ratings yet

- Paper On Navier-Stokes EquationsDocument11 pagesPaper On Navier-Stokes EquationsVSTomarNo ratings yet

- CARBayes STDocument37 pagesCARBayes STSiswanto HarvardNo ratings yet

- Degrees of Freedom and Precedence OrdersDocument8 pagesDegrees of Freedom and Precedence OrdersRITA ANGELICA JIMENEZ FERRONo ratings yet

- Partial Differential Equations and Finite Difference MethodsDocument15 pagesPartial Differential Equations and Finite Difference MethodsHozan MuhammadNo ratings yet

- MATHEMATICS (2nd Quarterly Examination) - Grade 7-10Document11 pagesMATHEMATICS (2nd Quarterly Examination) - Grade 7-10Gian HipolitoNo ratings yet

- Model TheoryDocument73 pagesModel TheoryMizanur RahmanNo ratings yet

- On The Mathematical Foundations of Electrical Circuit TheoryDocument18 pagesOn The Mathematical Foundations of Electrical Circuit TheorysdNo ratings yet

- Nov 2003 P2Document12 pagesNov 2003 P2api-26543952No ratings yet

- Unit 1 Module 1 FeaDocument53 pagesUnit 1 Module 1 FeaBharathi KannaNo ratings yet

- Information Booklet 2023 Latest by 02.05.23Document12 pagesInformation Booklet 2023 Latest by 02.05.23mahesh.revisitNo ratings yet

- ASO Sample Questions by AchieversDocument2 pagesASO Sample Questions by AchieversMks ViratNo ratings yet

- Factoring Quadratic Expressions HomeworkDocument6 pagesFactoring Quadratic Expressions Homeworkcfd13b82100% (1)

- University of Applied Sciences AustriaDocument2 pagesUniversity of Applied Sciences AustriaGerman Language SchoolNo ratings yet

- Module 2-Data ScienceDocument3 pagesModule 2-Data ScienceAerol MagpileNo ratings yet

- Trapezoids Talk - A Paper by Michael KeytonDocument7 pagesTrapezoids Talk - A Paper by Michael KeytonAbhi Ram100% (1)

- A Spurious Power Suppression Technique ForDocument8 pagesA Spurious Power Suppression Technique Forapi-19929244No ratings yet

- DPP - 40 - MDocument2 pagesDPP - 40 - Mshalini singhNo ratings yet

- Two Pairs of Archimedean Circles in The ArbelosDocument2 pagesTwo Pairs of Archimedean Circles in The ArbelosDũng Nguyễn TiếnNo ratings yet

- Lecture Notes em Fields Nov 2012Document153 pagesLecture Notes em Fields Nov 2012Nithindev GuttikondaNo ratings yet

- Setting Out CurvesDocument2 pagesSetting Out CurvesMemNo ratings yet

- First Order Logic: Artificial Intelligence COSC-3112 Ms. Humaira AnwerDocument24 pagesFirst Order Logic: Artificial Intelligence COSC-3112 Ms. Humaira AnwerKhizrah RafiqueNo ratings yet

- Math 20-1 Formula SheetDocument2 pagesMath 20-1 Formula SheetTayson PreteNo ratings yet

- Thoughts Upon Reading Marko RodinDocument17 pagesThoughts Upon Reading Marko Rodinreflatus13100% (3)