Professional Documents

Culture Documents

Experiment 11: Aim: Eda Tool Used: Methodology

Experiment 11: Aim: Eda Tool Used: Methodology

Uploaded by

Thomas JamesOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Experiment 11: Aim: Eda Tool Used: Methodology

Experiment 11: Aim: Eda Tool Used: Methodology

Uploaded by

Thomas JamesCopyright:

Available Formats

FPGA/ CPLD LAB

EXPERIMENT 11

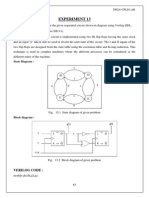

AIM : To design and simulate Universal Shift Register using Verilog HDL.

EDA TOOL USED : Xilinx ISE 8.1i

METHODOLOGY : A register is composed of a group of FFs to store a group of bits. A universal shift

register is an integrated logic circuit that can transfer data in three different modes. Like a parallel register it

can load and transmit data in parallel. Like shift registers it can load and transmit data in serial fashions,

through left shifts or right shifts. In addition, the universal shift register can combine the capabilities of both

parallel and shift registers to accomplish tasks that neither basic type of register can perform on its own. In

order for the universal shift register to operate in a specific mode, it must first select the mode. To

accomplish mode selection the universal register uses a set of two selector switches, S[1] and S[0] as shown

in table. Its parallel outputs are A[0], A[1], A[2], A[3] and parallel inputs are I[0], I[1], I[2], I[3]. The control

of right and left shift is governed by rtin and lfin respectively. Universal shift registers, as all other types of

registers, are used in computers as memory elements. In fact, all the operations in a digital system are

performed on registers. Examples of such operations include multiplication, division, and data transfer.

Operating mode

Hold

Shift right

Shift left

Parallel load

S[1]

0

0

1

1

S[0]

0

1

0

1

Fig. 11.1 Block diagram of Universal Shift register

52

FPGA/ CPLD LAB

VERILOG CODE :

module muxd2(I0, I1, I2, I3, S0, S1, Y);

input I0, I1, I2, I3, S0, S1;

output Y;

assign {Y}=S0?(S1?I3:I1):(S1?I2:I0);

endmodule

module dff(d,clk,res, q);

input d,clk,res;

initial

begin

output reg q;

q<=0;

end

always@(posedge clk or posedge res)

begin

if (res)

begin q<=0; end

else

begin q<=d; end

end

endmodule

module universal(clk,s1,s0,dinl,dinr, q, i, doutl,doutr);

input clk,s1,s0,dinl,dinr;

input [3:0]i;

wire [3:0] d; output [3:0]q; output doutl,doutr;

muxd2 m1(q[3],dinr,q[2],i[3],s0,s1,d[3]);

muxd2 m2(q[2],q[3],q[1],i[2],s0,s1,d[2]);

muxd2 m3(q[1],q[2],q[0],i[1],s0,s1,d[1]);

muxd2 m4(q[0],q[1],dinl,i[0],s0,s1,d[0]);

dff d1(d[3],clk,res,q[3]); dff d2(d[2],clk,res,q[2]); dff d3(d[1],clk,res,q[1]);

dff d4(d[0],clk,res,q[0]); and(doutl,s1,~s0,q[3]); and(doutr,~s1,s0,q[0]);

endmodule

RTL SCHEMATIC VIEW :

(a)

53

FPGA/ CPLD LAB

(b)

(c)

(d)

Fig. 11.2 RTL schematic of Universal Shift register

OUTPUT WAVEFORM :

Fig. 11.3 Output waveform of Universal Shift register

54

FPGA/ CPLD LAB

RESULT : Universal Shift Register is successfully implemented and its operation is verified by

simulation.

55

You might also like

- DSD LabDocument42 pagesDSD LabArun GoyalNo ratings yet

- Adobe Scan 23 Nov 2023Document11 pagesAdobe Scan 23 Nov 2023Hanisha SelviNo ratings yet

- Cadence Nclaunch LabDocument86 pagesCadence Nclaunch Labsweety987No ratings yet

- Unit 2Document15 pagesUnit 2Rajasekaran RNo ratings yet

- 8085 Processor Unit I: Mr. S. VinodDocument52 pages8085 Processor Unit I: Mr. S. VinodVinod SrinivasanNo ratings yet

- CHAPTER7Document10 pagesCHAPTER7RoopaNarsiNo ratings yet

- DSD Lab 9 HandoutDocument5 pagesDSD Lab 9 HandoutMuhammad AnasNo ratings yet

- Intel 8085Document80 pagesIntel 8085vsalaiselvamNo ratings yet

- BY Prof. Y. P. Jadhav Physics Department Smt. CHM College, Ulhasnagar - 3Document52 pagesBY Prof. Y. P. Jadhav Physics Department Smt. CHM College, Ulhasnagar - 3Prof. Yashavant p. JadhavNo ratings yet

- Cs 2 12th ExperimentDocument73 pagesCs 2 12th ExperimentShubham0% (1)

- Presentation 1Document7 pagesPresentation 1ece19637ec003No ratings yet

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003No ratings yet

- DLD Lab 12Document13 pagesDLD Lab 12abdullahakhtarkhan55No ratings yet

- Xapp 465Document17 pagesXapp 465chakri474No ratings yet

- EC 303 Chapter 2Document48 pagesEC 303 Chapter 2PrevenaManiamNo ratings yet

- 8085 Microprocessor - Block DiagramDocument5 pages8085 Microprocessor - Block DiagramShreyash ShindeNo ratings yet

- Cs2 Practical PDFDocument62 pagesCs2 Practical PDFMaitri ShahNo ratings yet

- Digital Electronics (Physics) - Shift RegistersDocument11 pagesDigital Electronics (Physics) - Shift Registersjoyalsaju319No ratings yet

- Emailing Fourth Module - IAMDocument35 pagesEmailing Fourth Module - IAMBhbNo ratings yet

- UNIT 3 MechatronicsDocument38 pagesUNIT 3 MechatronicsMuthuvel M67% (6)

- AdderDocument2 pagesAdderVIKRAM KUMARNo ratings yet

- Mpa Question Bank1Document16 pagesMpa Question Bank1Sharon FrancisNo ratings yet

- Design Alternatives For A 4-Bit Universal Shift Register Using Clock Pulse Sense LatchDocument10 pagesDesign Alternatives For A 4-Bit Universal Shift Register Using Clock Pulse Sense Latchcreative nprintNo ratings yet

- Microprocessors and Microcontrollers Answer KeyDocument14 pagesMicroprocessors and Microcontrollers Answer KeyselvaNo ratings yet

- Register Dan Shif RegisterDocument15 pagesRegister Dan Shif RegisterTsamarul HizbiNo ratings yet

- Architechture of 8085Document4 pagesArchitechture of 8085udit_mca_blyNo ratings yet

- MSAP Project SoDocument8 pagesMSAP Project SoBernardo SoNo ratings yet

- 16 Shift RegistersDocument6 pages16 Shift RegistersSohil VohraNo ratings yet

- DSD AssignmentDocument16 pagesDSD AssignmentEZRA MOHAMMEDNo ratings yet

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- EE309 MP Mod1 Ktunotes - inDocument17 pagesEE309 MP Mod1 Ktunotes - inDivya KrishnanNo ratings yet

- Mc14500b Icu HandbookDocument112 pagesMc14500b Icu HandbookpedroMdiasNo ratings yet

- Unit - VI DEDocument60 pagesUnit - VI DErahulbixt23No ratings yet

- Ec2002 8085 L2,3,4Document35 pagesEc2002 8085 L2,3,4himadeepthi sayaniNo ratings yet

- Ee8551 8085 NotesDocument31 pagesEe8551 8085 NotesKUMARANSCRNo ratings yet

- Block Diagram of 8085Document32 pagesBlock Diagram of 8085Shabd ShashankNo ratings yet

- Digital ApplicationsDocument14 pagesDigital Applications22e132No ratings yet

- Unit 3Document24 pagesUnit 3Raja BenitaNo ratings yet

- Microprocessors Architecture NotesDocument18 pagesMicroprocessors Architecture Notesenockkibet800No ratings yet

- Digital Systems II Chapter 3Document35 pagesDigital Systems II Chapter 3Luthando SopangisaNo ratings yet

- An Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreDocument35 pagesAn Introduction To INTEL 8085 Microprocessor: By:Ravindra Nadh.V, Assistant Professor, GST, BangaloreVasudev Rao KonjetiNo ratings yet

- Prepared by NITHIN JOHN: Module-1Document15 pagesPrepared by NITHIN JOHN: Module-1Nithin JohnNo ratings yet

- Unit V Pin Diagram of 8085 MicroprocessorDocument14 pagesUnit V Pin Diagram of 8085 MicroprocessorFLOWERNo ratings yet

- Lab 7: VHDL 16-Bit ShifterDocument6 pagesLab 7: VHDL 16-Bit ShifterAvinash VikramNo ratings yet

- An Over View of 8085Document12 pagesAn Over View of 8085nskprasad89No ratings yet

- MPI GTU Study Material E-Notes Unit-3 13052022115048AMDocument15 pagesMPI GTU Study Material E-Notes Unit-3 13052022115048AMmailsender787No ratings yet

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- An Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorDocument24 pagesAn Introduction To Microprocessor Architecture Using 8085 As A Classic ProcessorArnold JohnNo ratings yet

- Vlsi Laboratory: Experiment-6Document4 pagesVlsi Laboratory: Experiment-6Sarvraj Singh RtNo ratings yet

- Chapter2 MicroprocessorDocument95 pagesChapter2 MicroprocessorsagarNo ratings yet

- DCS-2 Practical File Part-1Document26 pagesDCS-2 Practical File Part-1ykr007No ratings yet

- Irjet V5i3295 PDFDocument3 pagesIrjet V5i3295 PDFchaitanya sNo ratings yet

- 1st Experiment ManualDocument5 pages1st Experiment Manualdevonlaratt359No ratings yet

- Blockdiagramof 8085Document40 pagesBlockdiagramof 8085Akhil NameirakpamNo ratings yet

- Field Programmable Gate ArrayDocument18 pagesField Programmable Gate ArrayTushar GargNo ratings yet

- Basic Concepts of MicroprocessorsDocument32 pagesBasic Concepts of MicroprocessorsAakrati SharmaNo ratings yet

- Lab 09 Handout Universal Shift RegisterDocument4 pagesLab 09 Handout Universal Shift RegisterMuhammad SaudNo ratings yet

- Exp 1 Induction To 8085 Micro PDocument10 pagesExp 1 Induction To 8085 Micro Phardik ChanderaNo ratings yet

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationFrom EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationNo ratings yet

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960From EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960No ratings yet

- High Performance 8-Bit Display Interface AD9980: Features Functional Block DiagramDocument44 pagesHigh Performance 8-Bit Display Interface AD9980: Features Functional Block DiagramThomas JamesNo ratings yet

- Design Methodologies and ToolsDocument95 pagesDesign Methodologies and ToolsThomas JamesNo ratings yet

- FPGA-Based Feature DetectionDocument9 pagesFPGA-Based Feature DetectionThomas JamesNo ratings yet

- DSP 2 LowpassfilterDocument20 pagesDSP 2 LowpassfilterDr-Atul Kumar DwivediNo ratings yet

- B - Tech - B - Arch Degree Exam November, December 2015 NTFNDocument2 pagesB - Tech - B - Arch Degree Exam November, December 2015 NTFNThomas JamesNo ratings yet

- Experiment 13: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 13: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Experiment 12: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 12: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Program 15Document4 pagesProgram 15Thomas JamesNo ratings yet

- Experiment 13: Aim: Eda Tool Used: MethodologyDocument2 pagesExperiment 13: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Experiment 6: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 6: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Experiment 5: Aim: Eda Tool Used: MethodologyDocument4 pagesExperiment 5: Aim: Eda Tool Used: MethodologyThomas JamesNo ratings yet

- Digital Signal Processing Lab (EC2156) : Thomas James Thomas REG NO: 2014TMPGI01 M.Tech (Digital Systems)Document4 pagesDigital Signal Processing Lab (EC2156) : Thomas James Thomas REG NO: 2014TMPGI01 M.Tech (Digital Systems)Thomas JamesNo ratings yet

- Digital Signal Processing LabDocument4 pagesDigital Signal Processing LabThomas JamesNo ratings yet

- Program 9Document4 pagesProgram 9Thomas JamesNo ratings yet

- Experiment 2 (B) : Aim: To Write A MATLAB Program To Receive An Input Sequence From The User and ToDocument4 pagesExperiment 2 (B) : Aim: To Write A MATLAB Program To Receive An Input Sequence From The User and ToThomas JamesNo ratings yet

- Program 15Document4 pagesProgram 15Thomas JamesNo ratings yet

- Program 14Document3 pagesProgram 14Thomas JamesNo ratings yet