Professional Documents

Culture Documents

9/1/2014 Labor Day: Tentative Plan of Lectures

9/1/2014 Labor Day: Tentative Plan of Lectures

Uploaded by

Sourav SamantaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

9/1/2014 Labor Day: Tentative Plan of Lectures

9/1/2014 Labor Day: Tentative Plan of Lectures

Uploaded by

Sourav SamantaCopyright:

Available Formats

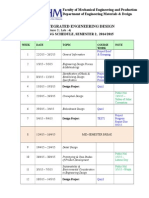

Tentative Plan of Lectures

EEE425/591: Digital Systems and Circuits; 3:00pm-4:15pm, M/W

Instructor: Y. Kevin Cao, ycao@asu.edu

Office hour: 1:30pm-2:30pm, M/W

Week

1

Date

Class

Schedule

Homework Labortary

8/25/2014

1

Introduction

8/27/2014

2

Logic Gate Basics

HW1

2

9/1/2014

Labor Day

9/3/2014

3

CMOS Technology

Lab 1

3

9/8/2014

4

Layout and Design Rules

9/10/2014

5

CMOS Modeling (1)

4

9/15/2014

6

CMOS Modeling (2)

HW2

9/17/2014

7

Inverter Design

5

9/22/2014

8

Gate Delay and Power Consumption

Lab 2

9/24/2014

9

Technology Scaling

6

9/29/2014

Midterm I

10/1/2014

10

Combinational Static Logic

7

10/6/2014

11

Timing Analysis in Logic Design

10/8/2014

12

Gate Sizing: Logical Efforts (1)

HW3

8

10/13/2014

Fall Break

10/15/2014

13

Gate Sizing: Logical Efforts (2)

Lab 3

9

10/20/2014

14

Gate Sizing: Logical Efforts (3)

10/22/2014

15

Pass Gate Logic

HW4

10

10/27/2014

16

Dynamic Logic (1)

10/29/2014

17

Dynamic Logic (2)

11

11/3/2014

Midterm II

11/5/2014

18

Adder Design

Lab 4/5

12

11/10/2014

19

Multipliers and Shifters

11/12/2014

20

Sequential Circuits Design

HW5

13

11/17/2014

21

Latches and Flip Flops

11/19/2014

22

Timing Issues in Latches and FFs (1)

14

11/24/2014

23

Timing Issues in Latches and FFs (2)

HW6

11/26/2014

24

Clocking and Synchronous Design

15

12/1/2014

25

Interconnect Technology and Timing

12/3/2014

Final Exam

16

12/10/2014

Final Exam (12:10-2:00pm)

* The date of homework and project is when the assignment starts, not the due date.

You might also like

- EE4242: VLSI CircuitsDocument2 pagesEE4242: VLSI CircuitsFahad NibirNo ratings yet

- MECH 411 Course Outline - Fall 2016Document4 pagesMECH 411 Course Outline - Fall 2016JohnNo ratings yet

- Managing the Testing Process: Practical Tools and Techniques for Managing Hardware and Software TestingFrom EverandManaging the Testing Process: Practical Tools and Techniques for Managing Hardware and Software TestingRating: 4 out of 5 stars4/5 (8)

- School of Electrical Engineering and Computer Science Time Table MS (CS) - 3Document6 pagesSchool of Electrical Engineering and Computer Science Time Table MS (CS) - 3Rida AmjadNo ratings yet

- Chemical Process Dynamics and Control SyllabusDocument2 pagesChemical Process Dynamics and Control SyllabusStephen XieNo ratings yet

- ECE3362 Syllabus Fall 2014Document3 pagesECE3362 Syllabus Fall 2014Gershom BenjaminNo ratings yet

- ELEC2133Summer 2013 2014Document10 pagesELEC2133Summer 2013 2014Sydney FinestNo ratings yet

- Course Outline - Ece365Document5 pagesCourse Outline - Ece365Mohamad Taib MiskonNo ratings yet

- Verilog HDL SyllabusDocument3 pagesVerilog HDL Syllabusprajap102No ratings yet

- Syllabus Final For IEE 572 Fall 2014 - Uniandes PDFDocument5 pagesSyllabus Final For IEE 572 Fall 2014 - Uniandes PDFtopo1228No ratings yet

- Ece206l SyllDocument7 pagesEce206l SyllBlaze MooreNo ratings yet

- ISEN 320 - Operations Research I (Fall 2017)Document4 pagesISEN 320 - Operations Research I (Fall 2017)sam256256No ratings yet

- Kannur University BSC Computer ScienceDocument86 pagesKannur University BSC Computer ScienceJinu Madhavan50% (2)

- CHEG 443 Syllabus 2014 FinalDocument3 pagesCHEG 443 Syllabus 2014 FinalCortez VaughanNo ratings yet

- MIT4700 Computer-Aided Design & ManufacturingDocument3 pagesMIT4700 Computer-Aided Design & ManufacturingAshley SmoakNo ratings yet

- EEE 3342C 0002 Syllabus Fall2014Document3 pagesEEE 3342C 0002 Syllabus Fall2014Jesus MarcanoNo ratings yet

- BSE Electronics SyllabusDocument110 pagesBSE Electronics SyllabusJinu MadhavanNo ratings yet

- Log BookDocument6 pagesLog BookPratham VasaniNo ratings yet

- 2014 EME165 Heat Transfer SyllabusDocument2 pages2014 EME165 Heat Transfer SyllabusLaura CraigNo ratings yet

- Takwin EE501 JUN 2014 - LatestDocument4 pagesTakwin EE501 JUN 2014 - LatesttamNo ratings yet

- Mapua EECE Researh Colloquium-Nov2014Document2 pagesMapua EECE Researh Colloquium-Nov2014Jairus CastroNo ratings yet

- Bachelor of TechnologyDocument65 pagesBachelor of TechnologyShivangi SharmaNo ratings yet

- ICS 202: Data Structures (3-3-4) : King Fahd University of Petroleum & MineralsDocument5 pagesICS 202: Data Structures (3-3-4) : King Fahd University of Petroleum & MineralshorsenightNo ratings yet

- It445ccna Study 2013 0819Document12 pagesIt445ccna Study 2013 0819Arman AzmiNo ratings yet

- Final Syllabus ECE 3rd Semester4,5,6,7,8Document99 pagesFinal Syllabus ECE 3rd Semester4,5,6,7,8Anuj DevgunNo ratings yet

- CS 7290 - Advanced Microarchitecture: DescriptionDocument2 pagesCS 7290 - Advanced Microarchitecture: DescriptionChandan MalleshNo ratings yet

- Infosheet2020w CSC258 v003Document2 pagesInfosheet2020w CSC258 v003Hanif Nur IlhamNo ratings yet

- EEE 4373 and EEL 5934 Radio Frequency Electronics Syllabus Fall 2017Document11 pagesEEE 4373 and EEL 5934 Radio Frequency Electronics Syllabus Fall 2017Rosemond FabienNo ratings yet

- Advanced Digital Design For DSP and Communications - EE278Document3 pagesAdvanced Digital Design For DSP and Communications - EE278Mayam AyoNo ratings yet

- A SicDocument3 pagesA SicSudha SriramNo ratings yet

- Course Outline - ENGR 233 - Fall 2023Document5 pagesCourse Outline - ENGR 233 - Fall 2023abner645No ratings yet

- SyllabusDocument7 pagesSyllabusAlexaa ANo ratings yet

- Syllabus 564Document4 pagesSyllabus 564Ambati MuthyaNo ratings yet

- Lecture 1-CircuitDocument19 pagesLecture 1-CircuitAnonymous dACYntXYntNo ratings yet

- CVEN2002Document9 pagesCVEN2002Patrick RungrugeecharoenNo ratings yet

- LecturePlan BDA40804 Sem2 - 1415Document2 pagesLecturePlan BDA40804 Sem2 - 1415Acap AliasNo ratings yet

- Visveswaraya Technological University SchemeDocument2 pagesVisveswaraya Technological University SchemeAkash Chandra0% (1)

- Scope and Objective of The CourseDocument2 pagesScope and Objective of The CourseAnimesh ChoudharyNo ratings yet

- DDVHDL - PlanningDocument1 pageDDVHDL - Planningshabbir470No ratings yet

- CSC 2304 SyllabusDocument3 pagesCSC 2304 SyllabusAmine NaitlhoNo ratings yet

- UT Dallas Syllabus For Ce3320.002.09s Taught by Mehrdad Nourani (Nourani)Document4 pagesUT Dallas Syllabus For Ce3320.002.09s Taught by Mehrdad Nourani (Nourani)UT Dallas Provost's Technology GroupNo ratings yet

- EECS 4360 Syllabus (Aug 2017)Document4 pagesEECS 4360 Syllabus (Aug 2017)Raghul VishnuNo ratings yet

- IT 111.01E Computer - Aided Design (CAD) Course Syllabus: Spring 2013 Web Enhanced BasedDocument5 pagesIT 111.01E Computer - Aided Design (CAD) Course Syllabus: Spring 2013 Web Enhanced BasedChoy Aming AtutuboNo ratings yet

- IT 111.01E Computer - Aided Design (CAD) Course Syllabus: Spring 2013 Web Enhanced BasedDocument5 pagesIT 111.01E Computer - Aided Design (CAD) Course Syllabus: Spring 2013 Web Enhanced BasedYE KONo ratings yet

- Syllabus S16 PDFDocument5 pagesSyllabus S16 PDFrenju91No ratings yet

- Time Table For M.E./M.Tech./ M.Arch. Degree Examinations - January-2014Document14 pagesTime Table For M.E./M.Tech./ M.Arch. Degree Examinations - January-2014Tiruchengode VinothNo ratings yet

- IPU VLSI SyllabusDocument40 pagesIPU VLSI SyllabusAbhinav SinghNo ratings yet

- Ati ChennaiDocument17 pagesAti ChennaiprismsmpNo ratings yet

- Syllabus - ELEC371 FL2023Document6 pagesSyllabus - ELEC371 FL2023Mohammad ChowdhuryNo ratings yet

- 3final Syllabus CSE 3rd Semester4,5,6,7,8Document112 pages3final Syllabus CSE 3rd Semester4,5,6,7,8karunNo ratings yet

- ISTM183B - A+ Practical Application: Proposed ScheduleDocument3 pagesISTM183B - A+ Practical Application: Proposed ScheduleKyle ScottNo ratings yet

- Ece 255 Electronic Circuit Analysis and Design Fall 2017: Division 2: Chew TR 1:30PM - 2:45PM ECE 170Document3 pagesEce 255 Electronic Circuit Analysis and Design Fall 2017: Division 2: Chew TR 1:30PM - 2:45PM ECE 170Dildar Khan BhatiNo ratings yet

- Real-Time Systems: Scheduling, Analysis, and VerificationFrom EverandReal-Time Systems: Scheduling, Analysis, and VerificationNo ratings yet

- Using Aspect-Oriented Programming for Trustworthy Software DevelopmentFrom EverandUsing Aspect-Oriented Programming for Trustworthy Software DevelopmentRating: 3 out of 5 stars3/5 (1)

- Modernisation, Mechanisation and Industrialisation of Concrete StructuresFrom EverandModernisation, Mechanisation and Industrialisation of Concrete StructuresNo ratings yet

- Implementation of Large-Scale Education AssessmentsFrom EverandImplementation of Large-Scale Education AssessmentsPetra LietzNo ratings yet

- Three Essays on Operations Scheduling with Job Classes and Time WindowsFrom EverandThree Essays on Operations Scheduling with Job Classes and Time WindowsNo ratings yet