Professional Documents

Culture Documents

Simulation of Booth Multiplier With Verilog-XL: Robert D'Angelo & Scott Smith

Simulation of Booth Multiplier With Verilog-XL: Robert D'Angelo & Scott Smith

Uploaded by

Shuvra SahaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Simulation of Booth Multiplier With Verilog-XL: Robert D'Angelo & Scott Smith

Simulation of Booth Multiplier With Verilog-XL: Robert D'Angelo & Scott Smith

Uploaded by

Shuvra SahaCopyright:

Available Formats

Simulation of Booth Multiplier with Verilog-XL

November 30, 2011

Robert DAngelo & Scott Smith

Tufts University

Electrical and Computer Engineering

EE-103 Lab 3: Part II

Professor:

Dr. Valencia Joyner Koomson

Abstract

In this lab an 8x8 modified booth multiplier is designed and tested at the gate level using the AMS

simulator in Cadence Design System. Using logic gate primitives constructed in Part I of this lab exercise,

the following blocks were simulated to complete the booth multiplier architecture: half-adder, full-adder,

4-bit carry lookahead adder (CLA), 12-bit CLA, CLA logic, booth encoder, and booth decoder. Each of

these blocks along with the complete architecture of the multiplier were simulated successfully. There is

an average delay of ??? per multiply operation.

CONTENTS

LIST OF FIGURES

Contents

Abstract

1 Booth Multiplier Overview

1.1 Booths Algorithm . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

1.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

5

5

2 Design and Simulation

2.1 Booth Encoder . . . . . . . . . . . . .

2.2 Booth Decoder . . . . . . . . . . . . .

2.3 Twelve-bit Carry Lookahead Adder . .

2.4 Sign Extension Trick . . . . . . . . . .

2.5 Signed 8x8 Modified Booth Multiplier

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

3 Conclusions

6

6

12

22

32

34

39

List of Figures

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

Modified Booth Multiplier Architecture . . . . . . .

Booth Encoder Schematic . . . . . . . . . . . . . . .

Booth Encoder Symbol . . . . . . . . . . . . . . . . .

Booth Encoder Test Bench Schematic . . . . . . . .

Booth Encoder AMS Simulation . . . . . . . . . . .

4-bit Booth Encoder Schematic . . . . . . . . . . . .

4-bit Booth Encoder Symbol . . . . . . . . . . . . .

4-bit Booth Encoder Test Bench Schematic . . . . .

4-bit Booth Encoder AMS Simulation . . . . . . . .

Booth Decoder Schematic . . . . . . . . . . . . . . .

Booth Decoder Symbol . . . . . . . . . . . . . . . . .

Half Adder Schematic . . . . . . . . . . . . . . . . .

Half Adder Symbol . . . . . . . . . . . . . . . . . . .

Half Adder Verilog X Simulation . . . . . . . . . . .

8-bit Booth Decoder Symbol . . . . . . . . . . . . .

8-bit Booth Decoder Schematic . . . . . . . . . . . .

8-bit Booth Decoder Test Bench Schematic . . . . .

8-bit Booth Decoder AMS Simulation . . . . . . . .

Full Adder Schematic . . . . . . . . . . . . . . . . .

Full Adder Symbol . . . . . . . . . . . . . . . . . . .

Full Adder Verilog X Simulation . . . . . . . . . . .

4-bit Adder Schematic . . . . . . . . . . . . . . . . .

4-bit Adder Symbol . . . . . . . . . . . . . . . . . . .

Four input NAND gate . . . . . . . . . . . . . . . . .

Five input NAND gate . . . . . . . . . . . . . . . . .

Carry Lookahead Logic Schematic . . . . . . . . . .

4-bit Adder Simulation . . . . . . . . . . . . . . . . .

12-bit Carry Lookahead Adder Symbol . . . . . . . .

12-bit Carry Lookahead Adder Testbench Schematic

12-bit Carry Lookahead Adder Schematic . . . . . .

12-bit Carry Lookahead Adder AMS Simulation . . .

Sign Extension Trick with Half Adders . . . . . . . .

Sign Extension Trick with Inverter . . . . . . . . . .

8x8 Booth Multiplier Symbol . . . . . . . . . . . . .

8x8 Booth Multiplier Testbench Schematic . . . . . .

8x8 Booth Multiplier Schematic . . . . . . . . . . . .

8x8 Booth MultiplierAMS Simulation . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

6

7

8

8

9

10

11

11

12

13

14

14

15

15

16

17

18

19

22

23

23

24

24

25

25

26

27

28

28

29

30

33

33

34

34

35

36

LIST OF TABLES

LIST OF TABLES

List of Tables

1

2

3

4

5

Booth Encoding . . . . . . . . . . . . . . . . . .

Booth Encoder Truth Table . . . . . . . . . . . .

Booth Decoder Truth Table (NEG not included)

Sign Extension Truth Table . . . . . . . . . . . .

Delay Summary . . . . . . . . . . . . . . . . . . .

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

5

7

13

32

39

1

1.1

BOOTH MULTIPLIER OVERVIEW

Booth Multiplier Overview

Booths Algorithm

Traditional hardware multiplication is performed in the same way multiplication is done by hand: partial

products are computed, shifted appropriately, and summed. This algorithm can be slow if there are many

partial products (i.e. many bits) because the output must wait until each sum is performed. Booths algorithm cuts the number of required partial products in half. This increases the speed by reducing the total

number of partial product sums that must take place.

The algorithm exploits the fact that multiplication by a sequence of 1s can be computed simply with

inversions and shifts, simpler operations than adding. This algorithm first encodes the start, middle, end,

or absence of a sequence of 1s in the multiplier term from groupings of three bits, each with an overlapping

bit from the previous grouping. These encodings are then used to compute the partial products from the

multiplicand by either multiplying it by 1 (i.e. no change), multiplying it by 2 (shift left one bit), or

multiplying it by -1 (2s complement). The encodings are shown in Table 1. These partial products are

shifted by two bits for each partial product after the first. The product is equal to the sum of these terms.

Table 1: Booth Encoding

Grouping Partial Product

000

0*Multiplicand

001

1*Multiplicand

010

1*Multiplicand

011

2*Multiplicand

100

-2*Multiplicand

101

-1*Multiplicand

110

-1*Multiplicand

111

0*Multiplicand

1.2

Architecture

Figure 1 below shows a block diagram of the proposed Booth multiplier implementation. This circuit

takes in two 8-bit binary numbers and outputs the 16-bit product. The multiplier, X[7:0], is divided into four

groupings: 0, X0, X1; X1, X2, X3; X3, X4, X5; X5, X6, X7. Each of these groupings is passed into a Booth

encoder, which outputs bits corresponding to the operations described in Table 1 (x0, x1, x2, x-1). Each

group of these selection bits are sent to a Booth decoder block, which outputs the appropriate partial product

term based on the selected operation. These partial products are then sign extended so that sign bits are

taken into account during the summing. Finally, the canonical shift and add multiplication is implemented

using 12-bit carry lookahead adders (CLA). The first two bits of each partial product are passed directly

to the output to account for the shifting. A standard array multiplier would typically require 8 partial

products, and thus 8 adders. However, this implementation reduces the number of partial products to only

four, significantly improving speed. Furthermore, the CLA provides another speed boost to the system.

DESIGN AND SIMULATION

Figure 1: Modified Booth Multiplier Architecture

2

2.1

Design and Simulation

Booth Encoder

Single Booth Encoder

Table 2 shows the truth table for a Booth encoder. The encoder takes inputs x2i+1 , x2i , and x2i1 from

the multiplier bus and produces a 1 or a 0 for each operation: single, double, negative. Figure 2 shows the

schematic that implements Table 2. Figure 3 shows a symbol view of the encoder. This block was simulated

using the Analog Mixed Signal (AMS) simulator. Figure 4 shows the simulation results. Based on the

simulation, this block has a propogation delay of ???. The Verilog test bench code, which sweeps all test

cases can be seen in Program Listing 1.

2.1

Booth Encoder

x2i+1

0

0

0

0

1

1

1

1

Table 2: Booth Encoder Truth Table

x2i x2i1

P Pi

Single Double

0

0

0

0

0

0

1

Y

1

0

1

0

Y

1

0

1

1

2Y

0

1

0

0

-2Y

0

1

0

1

-Y

1

0

1

0

-Y

1

0

1

1

-0 (=0)

0

0

Figure 2: Booth Encoder Schematic

DESIGN AND SIMULATION

Negate

0

0

0

0

1

1

1

1

2.1

Booth Encoder

DESIGN AND SIMULATION

Figure 3: Booth Encoder Symbol

Figure 4: Booth Encoder Test Bench Schematic

2.1

Booth Encoder

DESIGN AND SIMULATION

Figure 5: Booth Encoder AMS Simulation

// V e r i l o g HDL f o r " lab3_sims " , " v e r i l o g _ 3 i n _ s t i m " " f u n c t i o n a l "

timescale 1 ns /1 ps

module v e r i l o g _ 3 i n _ s t i m ( inout wire VDD,

inout wire VSS ,

output reg [ 2 : 0 ] OUT ) ;

assign VDD = 1 b1 ;

assign VSS = 1 b0 ;

reg c l o c k ;

i n i t i a l begin

c l o c k = 1 b0 ;

OUT = 3 b000 ;

end

always begin

#25.0 c l o c k = ~ c l o c k ;

end

always @ ( posedge c l o c k ) begin

OUT = #1.0 OUT + 3 b001 ;

end

always @ ( negedge c l o c k ) begin

i f ( OUT == 3 b111 )

#50 $ f i n i s h ;

end

endmodule

Listing 1: Booth Encoder Verilog Stimulus

Complete Booth Encoder

Four single bit encoders are combined to produce a complete Booth encoder as shown in Figure 6. This

block was generated to simplify the final schematic. Figure 7 shows a symbol view of this block. This block

was simulated using AMS. Figure 8 shows the test bench schematic. The Verilog test bench block with all

test cases can be viewed in Program Listing 2. The simulation results are displayed in Figure 9.

2.1

Booth Encoder

Figure 6: 4-bit Booth Encoder Schematic

10

DESIGN AND SIMULATION

2.1

Booth Encoder

DESIGN AND SIMULATION

Figure 7: 4-bit Booth Encoder Symbol

Figure 8: 4-bit Booth Encoder Test Bench Schematic

r

// V e r i l o g HDL f o r " lab3_sims " , " v e r i l o g _ 8 i n _ s t i m " " f u n c t i o n a l "

timescale 1 ns /1 ps

module v e r i l o g _ 8 i n _ s t i m ( inout wire VDD,

inout wire VSS ,

output reg [ 7 : 0 ] OUT ) ;

assign VDD = 1 b1 ;

assign VSS = 1 b0 ;

reg c l o c k ;

i n i t i a l begin

c l o c k = 1 b0 ;

OUT = 8 h00 ;

end

always begin

#25.0 c l o c k = ~ c l o c k ;

end

always @ ( posedge c l o c k ) begin

OUT = #1.0 OUT + 8 h01 ;

end

always @ ( negedge c l o c k ) begin

i f ( OUT == 8 hFF )

$finish ;

end

endmodule

Listing 2: Booth Encoder Verilog Stimulus

11

2.2

Booth Decoder

DESIGN AND SIMULATION

Figure 9: 4-bit Booth Encoder AMS Simulation

2.2

Booth Decoder

Single Bit Booth Decoder

Table 3 shows a truth table of the decoder block for generating a single bit of a partial product with inputs

from the encoder output bits and two of the multiplicand bits. This truth table does not show the partial

product if it is negated. This function is accomplished by simply performing the XOR of the PPij in the table

with the NEG output of the Booth encoder so that if NEG is asserted, the output is invertered; however, if

NEG is low, the output is unchanged. From Table 3 it can be seen that if SNG is asserted Yj is passed to

the output indicating multiply by unity. If DBL is asserted, Yj-1 is passed to the output, indicating a shift

by one bit to the left. If SNG and DBL are both zero, the output is zero. SNG and DBL cannot both be

asserted, so these cases are not shown. Figure 10 shows a gate level implementation of the single bit Booth

decoder, and Figure 11 shows a symbol view. This block has a worst case delay of about 7ns.

12

2.2

Booth Decoder

DESIGN AND SIMULATION

Table 3: Booth Decoder Truth Table (NEG not included)

SNG Yj DBL Yj-1 PPij (pre-xor)

0

0

0

0

0

0

0

0

1

0

0

0

1

0

0

0

0

1

1

1

0

1

0

0

0

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

0

0

0

0

1

0

0

1

0

1

1

0

0

1

1

1

0

1

1

Figure 10: Booth Decoder Schematic

13

2.2

Booth Decoder

DESIGN AND SIMULATION

Figure 11: Booth Decoder Symbol

Half Adder

The single bit decoder blocks invert the partial product bits when NEG is asserted; however, one must

be added to the least significant bit (LSB) so that 2s complement convention is followed. A cascade of

half-adders at the output (shown in Figure XX) implements this sum. Figure 9 shows a gate level view of

the half adder. This circuit produces a sum bit from the XOR of inputs A and B and a carry bit from the

function A AND B. The NAND and Inverter primitives are used to create the AND function. Figure 10

shows the symbol view, Figure 11 shows a functional simulation, and Figure 12 shows the Verilog stimulus

code.

Figure 12: Half Adder Schematic

14

2.2

Booth Decoder

Figure 13: Half Adder Symbol

Figure 14: Half Adder Verilog X Simulation

// V e r i l o g s t i m u l u s f i l e .

// P l e a s e do not c r e a t e a module i n t h i s f i l e .

initial

begin

#10

#10

#10

#10

end

A = 1 b0 ;

A = 1 b0 ;

A = 1 b1 ;

A = 1 b1 ;

$finish ;

B

B

B

B

=

=

=

=

1 b0 ;

1 b1 ;

1 b0 ;

1 b1 ;

Listing 3: Booth Encoder Verilog Stimulus

15

DESIGN AND SIMULATION

2.2

Booth Decoder

DESIGN AND SIMULATION

Eight-bit Decoder

In order to produce a complete partial product, an 8-bit Booth decoder block was implemented. This decoder

consists of nine single bit Booth decoders, each of which sends its partial product bit to a half adder. Each

half adder sums the current partial product bit with the carry from the previous half adder. The first half

adder sums the NEG bit with the first partial product bit, PP<0>. This step completes the 2s complement

representation of the partial product by adding 1 to the LSB if NEG is asserted. In the first decoder, the

Yj1 bit is tied to VSS (0). This connection ensures that when DBL is asserted, a zero is shifted in.

Note that this schematic actually produces a 9-bit output. The 9th bit is produced by connecting Yj1

of the 9th decoder to Y<7>, the MSB of the multiplicand. If a shift is occuring, the 9th bit, PP<8>, will

be correctly replaced with the 8th bit, Y<7>. If no shift occurs, PP<8> will become a sign extension bit

that is simply equal to the MSB, i.e. the sign bit, Y<7>.

Figure 15 shows a symbol view of the 8-bit decoder, and Figure 16 shows a gate level schematic. This

circuit was simulated using AMS. Figure 17 shows the test bench schematic used in the simulation, and

Figure 18 shows the simulation results. The verilog code of the test bench block is shown in Listing 4. All

test cases simulated successfully. This block has a worst case delay of about 33ns.

Figure 15: 8-bit Booth Decoder Symbol

16

2.2

Booth Decoder

Figure 16: 8-bit Booth Decoder Schematic

17

DESIGN AND SIMULATION

2.2

Booth Decoder

DESIGN AND SIMULATION

Figure 17: 8-bit Booth Decoder Test Bench Schematic

18

2.2

Booth Decoder

DESIGN AND SIMULATION

Figure 18: 8-bit Booth Decoder AMS Simulation

19

2.2

Booth Decoder

DESIGN AND SIMULATION

// V e r i l o g HDL f o r " lab3_sims " , " booth_decode_9bit_v1_tb1 " " f u n c t i o n a l "

// T e s t b e n c h f o r booth_decode_9bit_v1_tb1

module booth_decode_9bit_v1_tb1 ( output wire Xm1,

output wire X0 ,

output wire Xp1 ,

output reg [ 7 : 0 ] Y,

input wire [ 8 : 0 ] PP,

inout wire VDD,

inout wire VSS ) ;

parameter

parameter

parameter

parameter

parameter

parameter

parameter

parameter

NUM0

NUM1

NUM2

NUM3

NUM4

NUM5

NUM6

NUM7

=

=

=

=

=

=

=

=

8 b00000000 ;

8 b00000001 ;

8 b11111110 ;

8 b11111111 ;

8 b10101010 ;

8 b01010101 ;

8 b10000000 ;

8 b11001100 ;

reg c l k ;

reg [ 2 : 0 ] X;

reg [ 3 : 0 ] s e l ;

assign VDD = 1 b1 ;

assign VSS = 1 b0 ;

assign Xm1 = X [ 0 ] ;

assign X0 = X [ 1 ] ;

assign Xp1 = X [ 2 ] ;

// I n i t i a l i z e v a r i a b l e s .

i n i t i a l begin

c l k = 1 b0 ;

X = 3 b000 ;

s e l = 4 h0 ;

end

// C lo c k f o r a d v a n c i n g t h r o u g h t h e t e s t c a s e s .

always begin

#50.0 c l k = ~ c l k ;

end

// Counter f o r X t o g e n e r a t e a l l p o s s i b i l i t i e s .

always @ ( posedge c l k ) begin

X = X + 3 b001 ;

end

// s e l v a r i a b l e t o i t e r a t e t h r o u g h t h e c a s e s t a t e m e n t b e l o w .

always @ ( posedge c l k ) begin

20

2.2

Booth Decoder

DESIGN AND SIMULATION

i f ( X == 3 b000 ) begin

s e l = s e l + 4 h1 ;

end

end

// D i f f e r e n t c a s e s f o r Y.

always @ ( s e l or Y) begin

case ( s e l )

4 h1 : begin

Y = NUM0;

end

4 h2 : begin

Y = NUM1;

end

4 h3 : begin

Y = NUM2;

end

4 h4 : begin

Y = NUM3;

end

4 h5 : begin

Y = NUM4;

end

4 h6 : begin

Y = NUM5;

end

4 h7 : begin

Y = NUM6;

end

4 h8 : begin

Y = NUM7;

end

default : begin

Y = 8 h00 ;

end

endcase

end

// End s i m u l a t i o n when we f i n i s h l o o k i n g a t a l l our c a s e s .

always @ ( posedge c l k ) begin

i f ( s e l == 4 h8 ) begin

i f ( X == 3 b111 ) begin

#100;

$finish ;

end

end

end

endmodule

Listing 4: Booth Encoder Verilog Stimulus

21

2.3

2.3

Twelve-bit Carry Lookahead Adder

DESIGN AND SIMULATION

Twelve-bit Carry Lookahead Adder

Full Adder

The first block required for a multi-bit adder is the full adder. This circuit is identical to the half adder

except that it has an additional input, Cin, so that a carry from a previous addition may be passed along.

Furthermore, instead of a carry out, Cout, propogate (P) and generate (G) signals are produced. The logic

for this schematic is as follows:

S = A B Cin

(2.1)

P =AB

(2.2)

G=AB

(2.3)

These two signals can be used to generate the carry out bit simultaneously for faster addition (see 4-bit

Carry Lookahead Adder). Figure 19 shows a gate level implementation of the full adder schematic. Note

that ~G is also generated. This bit can be used instead of G to simplify some of carry lookahead logic.

Figure 20 shows a symbol view of the full adder. This block was verified using Verilog X. The simulation

output can be seen in Figure 21, and the stimulus code can be seen in Listing 5. All possible inputs were

swept, and all outputs were correct. There is a average of 4ns propagation delay from input to sum.

Figure 19: Full Adder Schematic

22

2.3

Twelve-bit Carry Lookahead Adder

Figure 20: Full Adder Symbol

Figure 21: Full Adder Verilog X Simulation

// V e r i l o g s t i m u l u s f i l e .

// P l e a s e do not c r e a t e a module i n t h i s f i l e .

initial

begin

#10

#10

#10

#10

#10

#10

#10

#10

end

A = 1 b0 ;

A = 1 b0 ;

A = 1 b0 ;

A = 1 b0 ;

A = 1 b1 ;

A = 1 b1 ;

A = 1 b1 ;

A = 1 b1 ;

$finish ;

B

B

B

B

B

B

B

B

=

=

=

=

=

=

=

=

1 b0 ;

1 b0 ;

1 b1 ;

1 b1 ;

1 b0 ;

1 b0 ;

1 b1 ;

1 b1 ;

Cin

Cin

Cin

Cin

Cin

Cin

Cin

Cin

=

=

=

=

=

=

=

=

1 b0 ;

1 b1 ;

1 b0 ;

1 b1 ;

1 b0 ;

1 b1 ;

1 b0 ;

1 b1 ;

Listing 5: Booth Encoder Verilog Stimulus

23

DESIGN AND SIMULATION

2.3

Twelve-bit Carry Lookahead Adder

DESIGN AND SIMULATION

Four-bit Carry Lookahead Adder

In order to improve the speed of the adder, carry lookahead logic was employed to compute the carry bits

while simultaneously computing the sum bits. This method becomes less effective as the number of bits

surpasses four; therefore, a 4-bit CLA was implemented. This block can be cascaded to produce higher bit

adders.

Figure 22: 4-bit Adder Schematic

Figure 23: 4-bit Adder Symbol

Figure 22 shows the schematic diagram of the 4-bit CLA, and Figure 23 shows a symbol view. This

circuit consists of four full adders, which each pass propogate and generate signals to the CLA logic, which

24

2.3

Twelve-bit Carry Lookahead Adder

DESIGN AND SIMULATION

computes the carry bits and feeds them into the carry-in input of the appropriate full adders. The carry bits

are generated by the CLA based on the following logic:

Si = Ai Bi Ci = Pi Ci

(2.4)

Ci+1 = Gi + Ci Pi

(2.5)

Expanding Eq 2.5 for each carry bit of the four bit adder yields Eq 2.6-2.9, which contains only the first

carry in bit and propogate and generate bits. Thus, the carry bits can be computed in parallel with the sum

bits, which increases the speed of the adder compared to a ripple style adder.

C1 = G0 + C0 P0

(2.6)

C2 = G1 + G0 P1 + C0 P0 P1

(2.7)

C3 = G2 + G1 P2 + G0 P1 P2 + C0 P0 P1 P2

(2.8)

C4 = G3 + G2 P3 + G1 P2 P3 + G0 P1 P2 P3 + C0 P0 P1 P2 P3

(2.9)

Observing these equations reveals that two more primitive gates are required to implement this logic:

four and five input NAND gates. These gates were constructed using the logic primitives designed in Part

I of this lab exercise. The schematics for the four and five input NAND gates are shown in Figure 24 and

Figure 25, respectively. The CLA logic circuit that implements Eq 2.6-2.9 is shown in Figure 26. The code

in Program Listing 6 was used to simulate the adder. Results are shown in Figure 27. All test cases were

successful.

Figure 24: Four input NAND gate

Figure 25: Five input NAND gate

25

2.3

Twelve-bit Carry Lookahead Adder

Figure 26: Carry Lookahead Logic Schematic

26

DESIGN AND SIMULATION

2.3

Twelve-bit Carry Lookahead Adder

Figure 27: 4-bit Adder Simulation

// V e r i l o g s t i m u l u s f i l e .

// P l e a s e do not c r e a t e a module i n t h i s f i l e .

initial

begin

A0 = 1 b0 ; A1

B0 = 1 b0 ; B1

Cin = 1 b0 ;

#10 A0 = 1 b1 ; A1

B0 = 1 b1 ; B1

Cin = 1 b1 ;

#10 A0 = 1 b0 ; A1

B0 = 1 b0 ; B1

Cin = 1 b1 ;

#20 $ f i n i s h ;

end

= 1 b0 ; A2 = 1 b0 ; A3 = 1 b1 ;

= 1 b0 ; B2 = 1 b0 ; B3 = 1 b1 ;

= 1 b1 ; A2 = 1 b1 ; A3 = 1 b1 ;

= 1 b1 ; B2 = 1 b1 ; B3 = 1 b1 ;

= 1 b0 ; A2 = 1 b0 ; A3 = 1 b0 ;

= 1 b0 ; B2 = 1 b0 ; B3 = 1 b0 ;

Listing 6: Booth Encoder Verilog Stimulus

27

DESIGN AND SIMULATION

2.3

Twelve-bit Carry Lookahead Adder

DESIGN AND SIMULATION

12-bit Carry Lookahead Adder

In order to sum the 9-bit partial products from the decoders, a 12-bit CLA was implemented from the 4-bit

CLA blocks. The block level schematic is shown in Figure 28. A symbol view of this circuit is shown in Figure

26. This circuit cascades four bit CLAs in the same way that the four bit CLAs cascade full adders. Within

the original CLA logic schematic in Figure 24 the carry out bits of each four bit adder are also computed.

This implementation provides another layer of carry lookahead logic for the 12-bit adder to further improve

speed. This circuit was tested using the testbench schematic shown in Figure 27. The simulation results can

be seen in Figure 29. The verilog code of the stimulus block is shown in Program Listing 7. All test cases

were successful in this simulation. The average propagation delay was 8ns to compute one sum.

Figure 28: 12-bit Carry Lookahead Adder Symbol

Figure 29: 12-bit Carry Lookahead Adder Testbench Schematic

28

2.3

Twelve-bit Carry Lookahead Adder

DESIGN AND SIMULATION

Figure 30: 12-bit Carry Lookahead Adder Schematic

29

2.3

Twelve-bit Carry Lookahead Adder

DESIGN AND SIMULATION

Figure 31: 12-bit Carry Lookahead Adder AMS Simulation

// V e r i l o g HDL f o r " ee103 " , " a d d e r _ 1 2 b i t _ v s t i m " " f u n c t i o n a l "

module adder_12bit_vstim ( output reg [ 1 1 : 0 ] A,

output reg [ 1 1 : 0 ] B,

output reg Cin ,

inout wire VDD,

inout wire VSS ) ;

reg c l k ;

reg [ 3 : 0 ] s e l ;

i n i t i a l begin

s e l = 4 b0000 ;

c l k = 1 b0 ;

A = 1 2 h000 ;

B = 1 2 h000 ;

Cin = 1 b0 ;

end

always begin

#25.0 c l k = ~ c l k ;

end

always @ ( posedge c l k ) begin

s e l = s e l + 4 b0001 ;

end

always @ ( s e l ) begin

case ( s e l )

4 b0001 : begin

A = 1 2 h7FF ;

B = 1 2 h001 ;

Cin = 1 b0 ; // S = 800

end

4 b0010 : begin

A = 1 2 h08F ;

B = 1 2 h07F ;

Cin = 1 b0 ; // S = 10E

end

4 b0011 : begin

30

2.3

Twelve-bit Carry Lookahead Adder

A = 1 2 hF00 ;

B = 1 2 h100 ;

Cin = 1 b0 ; //

end

4 b0100 : begin

A = 1 2 h800 ;

B = 1 2 hFFF ;

Cin = 1 b0 ; //

end

4 b0101 : begin

A = 1 2 h07F ;

B = 1 2 hF71 ;

Cin = 1 b0 ; //

end

4 b0110 : begin

A = 1 2 h7FF ;

B = 1 2 h001 ;

Cin = 1 b1 ; //

end

4 b0111 : begin

A = 1 2 h08F ;

B = 1 2 h07F ;

Cin = 1 b1 ; //

end

4 b1000 : begin

A = 1 2 hF00 ;

B = 1 2 h100 ;

Cin = 1 b1 ; //

end

4 b1001 : begin

A = 1 2 h800 ;

B = 1 2 hFFF ;

Cin = 1 b1 ; //

end

4 b1010 : begin

A = 1 2 h07F ;

B = 1 2 hF71 ;

Cin = 1 b1 ; //

end

default : begin

#50 $ f i n i s h ;

end

endcase

end

endmodule

S = ( 1 ) 000

S = ( 1 ) 7FF

S = FF0

S = 801

S = 10F

S = ( 1 ) 001

S = ( 1 ) 800

S = FF1

Listing 7: Booth Encoder Verilog Stimulus

31

DESIGN AND SIMULATION

2.4

2.4

Sign Extension Trick

DESIGN AND SIMULATION

Sign Extension Trick

When summing the partial products to compute the final product, each partial product must be sign extended by different amounts (i.e. the first partial product must be extended by 6 bits, the second by 4, etc.)

so that the sign bits of each partial product are reproduced correctly. The sign extension would require extra

logic; however, the following technique preserves the sign bits without having to sign extend each partial

product:

1. Invert the MSB of each partial product generated by the decoder.

2. Add 1 to the MSB of the first partial product.

3. Add 1 in front of each partial product.

This technique was implemented by first placing an inverter between the MSB of each 9-bit partial product

and the corresponding input bit of the 12-bit adder. Then, the 10th input bit to each of the 12-bit adders

is connected to VDD. This effectively adds 1 in front of each partial product. For the first partial product,

however, this cannot be done. Adding 1 to the MSB could produce a carry bit, which must be taken into

account. Furthermore, adding 1 in front of the MSB of the first partial product would produce a carry

if the previous addition of 1 to the MSB produced a carry. This can be accomplished by cascading two

half adders where each has one input tied to VDD, the first adder has a second input tied to the MSB of

the first partial product, and the second adder has a second input connected to the carry out of the first

adder. The two sums and final carry are then tied to input bits 6, 7 and 8 of the 12-bit adder respectively.

However, this method will be quite slow. Table 4 shows the truth table for the addition. PP08 is the MSB

of the first partial product, ~PP08 is the inverted PP08 from step 1 above. B6-B8 refer to the inputs to the

12-bit adder. Since ~PP08 can only be 1 or 0, there are only two possibilities for the addition. If ~PP08 =

1, a carry will be produced by the first addition, and another carry will be produced by the second addition

resulting in B8B7B6 = 011. If ~PP8 = 0, no carry will be produced and B8B7B6 = 100. From the truth

table it can be seen that B6 = B7 = ~PP08, and B8 = PP08. Thus, this circuit can be simplified to simply

connecting these nodes as such. The two approaches are shown in Figure 32 and Figure 33.

Table 4: Sign Extension Truth Table

~PP08 PP08 B8 B7 B6

0

1

1

0

0

1

0

0

1

1

32

2.4

Sign Extension Trick

DESIGN AND SIMULATION

Figure 32: Sign Extension Trick with Half Adders

Figure 33: Sign Extension Trick with Inverter

33

2.5

2.5

Signed 8x8 Modified Booth Multiplier

DESIGN AND SIMULATION

Signed 8x8 Modified Booth Multiplier

From the blocks discussed above an 8x8 modified Booth multiplier was constructed following the architecture

proposed in Section 1.2. The final schematic of the modified Booth multiplier is shown in Figure 36, and

a symbol view is shown in Figure 34. This circuit takes in two 8-bit 2s complement binary numbers and

produces a 16-bit output equal to the product of the two inputs. This circuit was simulated using AMS. The

test bench schematic is shown in Figure 35. The simulation results are shown in Figure 37, and the stimulus

code is shown in Program Listing 8. Unfortunately, this circuit does not operate as desired. Four of the

output bits are incorrect. We believe this is due to a flaw in our implementation of the sign extension trick.

The test case shows the output for every combination of 107, 105, -107 and -105. The delay is measured at

35ns per multiply, worst case.

Figure 34: 8x8 Booth Multiplier Symbol

Figure 35: 8x8 Booth Multiplier Testbench Schematic

34

2.5

Signed 8x8 Modified Booth Multiplier

Figure 36: 8x8 Booth Multiplier Schematic

35

DESIGN AND SIMULATION

2.5

Signed 8x8 Modified Booth Multiplier

DESIGN AND SIMULATION

Figure 37: 8x8 Booth MultiplierAMS Simulation

// V e r i l o g HDL f o r " lab3_sims " , " b o o t h _ m u l t i p l i e r _ t o p _ t b 1 " " f u n c t i o n a l "

// T e s t b e n c h f o r b o o t h _ m u l t i p l i e r _ t o p _ v 1

// S c o t t Smith

// November 28 , 2011

// STATUS SEEMS TO WORK

module boo th_m ultip lier_ top_t b1 ( output reg

output reg

input wire

inout wire

inout wire

[ 7 : 0 ] X,

[ 7 : 0 ] Y,

[ 1 5 : 0 ] P,

VDD,

VSS ) ;

// This t e s t u s e s two numbers i n v a r i o u s s i g n c o n f i g u r a t i o n s

// and o r d e r s (8 c a s e s t o t a l ) .

// parameter NUM1p = 8 b01101001 ; // +105

// parameter NUM1n = 8 b10010111 ; // 105 (151 u n s i g n e d )

// parameter NUM2p = 8 b01101011 ; // +107

// parameter NUM2n = 8 b10010101 ; // 107 (149 u n s i g n e d )

parameter NUM1p = 8 b00000000 ; // 0

parameter NUM1n = 8 b00000000 ; // 0 ( c a r r y l o s t )

parameter NUM2p = 8 b00000001 ; // 1

parameter NUM2n = 8 b11111111 ; // 1

reg c l k ;

reg [ 3 : 0 ] s e l ;

assign VDD = 1 b1 ;

assign VSS = 1 b0 ;

// I n i t i a l i z e v a r i a b l e s .

i n i t i a l begin

c l k = 1 b0 ;

s e l = 4 h0 ;

X = 8 h00 ;

Y = 8 h00 ;

end

// C lo c k f o r a d v a n c i n g t h r o u g h t h e t e s t c a s e s .

36

2.5

Signed 8x8 Modified Booth Multiplier

DESIGN AND SIMULATION

always begin

#50.0 c l k = ~ c l k ;

end

// s e l v a r i a b l e t o i t e r a t e t h r o u g h t h e c a s e s t a t e m e n t b e l o w .

always @ ( posedge c l k ) begin

s e l = s e l + 4 h1 ;

end

// D i f f e r e n t t e s t c a s e s u s i n g t h e p a r a m t e r s ab o ve .

always @ ( s e l or X or Y) begin

case ( s e l )

4 h0 : begin

X = NUM1p;

Y = NUM2p;

end

4 h1 : begin

X = NUM1n;

Y = NUM2p;

end

4 h2 : begin

X = NUM1p;

Y = NUM2n;

end

4 h3 : begin

X = NUM1n;

Y = NUM2n;

end

4 h4 : begin

X = NUM2p;

Y = NUM1p;

end

4 h5 : begin

X = NUM2n;

Y = NUM1p;

end

4 h6 : begin

X = NUM2p;

Y = NUM1n;

end

4 h7 : begin

X = NUM2n;

Y = NUM1n;

end

//c a s e s where a number i s m u l t i p l i e d by i t s e l f //

4 h8 : begin

X = NUM1p;

Y = NUM1p;

end

4 h9 : begin

37

2.5

Signed 8x8 Modified Booth Multiplier

X = NUM1p;

Y = NUM1n;

end

4 hA : begin

X = NUM1n;

Y = NUM1p;

end

4 hB : begin

X = NUM1n;

Y = NUM1n;

end

4 hC : begin

X = NUM2p;

Y = NUM2p;

end

4 hD : begin

X = NUM2p;

Y = NUM2n;

end

4 hE : begin

X = NUM2n;

Y = NUM2p;

end

4 hF : begin

X = NUM2n;

Y = NUM2n;

end

default : begin

X = X;

Y = Y;

end

endcase

end

// End s i m u l a t i o n when we f i n i s h

always @ ( negedge c l k ) begin

i f ( s e l == 4 hF ) begin

// Add some d e l a y s i n c e t h i s

// b u t d o e s not t e l l us what

#200;

$finish ;

end

end

// Add code t o do e r r o r c h e c k i n g

endmodule

DESIGN AND SIMULATION

l o o k i n g a t a l l our c a s e s .

c l k c a u s e s t h e i n p u t s t o update ,

i s g o i n g on a t t h e o u t p u t .

automatically . . .

Listing 8: Booth Encoder Verilog Stimulus

38

CONCLUSIONS

Conclusions

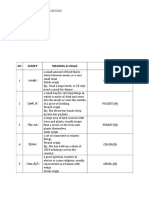

Table 5 below summarizes the delay seen through each block in this design. Several techniques can be used

in the final project to reduce these delay times.

Table 5: Delay Summary

Block

Propagation Delay

Half Adder

4ns

Full Adder

4ns

4-bit Adder

8ns

12-bit Adder

8ns

Single Bit Decoder

7ns

Booth Multiplier

35ns

This lab demonstrates the successful gate level implementation of an 8-bit signed modified booth multiplier. However, the most significant four bits are incorrect. We believe this is due to our sign extension

implementation. The first step of the final project will be to debug this technique. This design will be

optimized for maximum speed using IBMs 180nm process, CMRF7SF. A layout will be constructed and

post layout simulation will be performed so that this device can be manufactured.

39

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5834)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (903)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (824)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (405)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- All Interfaces in FPMDocument1 pageAll Interfaces in FPMmachnik1486624No ratings yet

- Finxter WorldsMostDensePythonCheatSheetDocument1 pageFinxter WorldsMostDensePythonCheatSheetmachnik1486624No ratings yet

- Python Quick ReferenceDocument1 pagePython Quick Referencemachnik14866240% (1)

- Sri Dakshinamurthy Stotram - Hindupedia, The Hindu EncyclopediaDocument7 pagesSri Dakshinamurthy Stotram - Hindupedia, The Hindu Encyclopediamachnik1486624No ratings yet

- NO Script Meaning & Usage WordDocument2 pagesNO Script Meaning & Usage Wordmachnik1486624No ratings yet

- Sardar Vallabhbhai Patel SpeechDocument1 pageSardar Vallabhbhai Patel Speechmachnik14866240% (1)

- Procedure For Displaying The Flight ModelDocument1 pageProcedure For Displaying The Flight Modelmachnik1486624No ratings yet

- ABAP Object Oriented Approach For Reports - RedesignDocument4 pagesABAP Object Oriented Approach For Reports - Redesignmachnik1486624No ratings yet

- Cat1 Segmentals PDFDocument1 pageCat1 Segmentals PDFmachnik1486624No ratings yet

- FNA Practice Materials Cat 1Document6 pagesFNA Practice Materials Cat 1machnik1486624No ratings yet

- 1.FPGA Design Flow Processes PropertiesDocument5 pages1.FPGA Design Flow Processes Propertiesmachnik1486624No ratings yet

- Tamil LearningDocument13 pagesTamil Learningmachnik1486624No ratings yet

- DSP Lab Sample Viva QuestionsDocument5 pagesDSP Lab Sample Viva Questionsmachnik1486624No ratings yet

- From Bangalore To Ooty! - Team-BHPDocument17 pagesFrom Bangalore To Ooty! - Team-BHPmachnik1486624No ratings yet

- RTO Work For KarnatakaDocument5 pagesRTO Work For Karnatakamachnik1486624No ratings yet

- FPGA Design With VerilogDocument2 pagesFPGA Design With Verilogmachnik1486624No ratings yet

- Modelling Latches and FlipflopsDocument9 pagesModelling Latches and Flipflopsmachnik1486624No ratings yet

- UNIT 1 (Number Systems) : TUTORIAL SHEET: 151 174 10110111 AB3 1023 15C 101111 C35 261 11011001 1375Document10 pagesUNIT 1 (Number Systems) : TUTORIAL SHEET: 151 174 10110111 AB3 1023 15C 101111 C35 261 11011001 1375Sanjay MalviyaNo ratings yet

- MAZAKManuals1066 PDFDocument27 pagesMAZAKManuals1066 PDFAntonio LucasNo ratings yet

- Module1 - Central Concepts of AutomataDocument21 pagesModule1 - Central Concepts of AutomataChempa TustiNo ratings yet

- Computing Theory-Comp303 BestnotesDocument99 pagesComputing Theory-Comp303 BestnotesSad DasNo ratings yet

- Digital Logic Design: Federal Urdu University of Arts Science and Technology IslamabadDocument29 pagesDigital Logic Design: Federal Urdu University of Arts Science and Technology IslamabadPirzada SwatiNo ratings yet

- (Vadhan) PseudorandomnessDocument227 pages(Vadhan) PseudorandomnessPawan KumarNo ratings yet

- DEE 1224 Digital Electronics: Number Systems and CodesDocument69 pagesDEE 1224 Digital Electronics: Number Systems and CodessamNo ratings yet

- Rift Valley Universty Bishoftu Campus Department of Computer ScienceDocument12 pagesRift Valley Universty Bishoftu Campus Department of Computer SciencesolmaNo ratings yet

- Not Expected From RohitDocument358 pagesNot Expected From RohitSachin GuptaNo ratings yet

- ECE257 Numerical Methods and Scientific ComputingDocument36 pagesECE257 Numerical Methods and Scientific ComputinggtgreatNo ratings yet

- Clique ProblemDocument10 pagesClique ProblemAman GuptaNo ratings yet

- Verilog Cheat Sheet: S Winberg and J TaylorDocument2 pagesVerilog Cheat Sheet: S Winberg and J TaylorMohamed ElsahatNo ratings yet

- Chapter 2 Computer ArithmeticDocument56 pagesChapter 2 Computer ArithmeticrajkumarNo ratings yet

- FinalDocument7 pagesFinalynkitapNo ratings yet

- 2-Lecture Notes Lesson1 3Document7 pages2-Lecture Notes Lesson1 3kstu1112No ratings yet

- Chapter 2 Instruction Sets of 8086 Part 2Document30 pagesChapter 2 Instruction Sets of 8086 Part 2zlight HagosNo ratings yet

- Computer Organization and Architecture (18EC35) - Machine Instructions and Programs - Part 1 (Module 1)Document60 pagesComputer Organization and Architecture (18EC35) - Machine Instructions and Programs - Part 1 (Module 1)Shrishail Bhat100% (1)

- cs302 Assignment 2 by Dilshad AhmadDocument7 pagescs302 Assignment 2 by Dilshad AhmadMUHAMMAD NABEEL SHAHNo ratings yet

- Unit V:: Design and Analysis of AlgorithmsDocument7 pagesUnit V:: Design and Analysis of AlgorithmsSairam N100% (1)

- Asmworkbook PDFDocument77 pagesAsmworkbook PDFShakila ShakiNo ratings yet

- Math Base SystemsDocument66 pagesMath Base SystemsAngel MarieNo ratings yet

- Hexadecimal To Binary ConversionDocument2 pagesHexadecimal To Binary ConversionArlene PolinarNo ratings yet

- Formal Languages and Automata Theory PDFDocument6 pagesFormal Languages and Automata Theory PDFAddeppali .venkata Sai prathyushaNo ratings yet

- Number System ConversionsDocument24 pagesNumber System ConversionssujathaNo ratings yet

- The Theory of AutomataDocument53 pagesThe Theory of AutomataAbhinav KumarNo ratings yet

- Lect5 FSMDocument23 pagesLect5 FSMSangeetha BajanthriNo ratings yet

- 1 Numbering SystemsDocument22 pages1 Numbering SystemsShubham VermaNo ratings yet

- ECE468 Computer Organization & Architecture ALU Design II: °this 1-Bit ALU Will Perform AND, OR, and ADDDocument16 pagesECE468 Computer Organization & Architecture ALU Design II: °this 1-Bit ALU Will Perform AND, OR, and ADDNarender KumarNo ratings yet

- Automata, Computability, and Formal Language: Spring 2021Document17 pagesAutomata, Computability, and Formal Language: Spring 2021Milion NugusieNo ratings yet

- Adder Cum SubtractorDocument4 pagesAdder Cum SubtractorCHERISMA100% (2)