Professional Documents

Culture Documents

0 ratings0% found this document useful (0 votes)

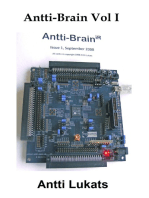

145 viewsAltera CPLD Learning Board Manual

Altera CPLD Learning Board Manual

Uploaded by

Miguel Torres AlvarezThis document describes an Altera CPLD development board intended for learning and prototyping.

The board uses an Altera MAXII EPM240T100C5N CPLD and has 65 I/O ports that are labeled to help users learn how to configure pin assignments. It includes features like 8 digital tubes, 8 LEDs, buttons, a buzzer, and a 50MHz crystal for clocking the CPLD.

The board is powered by an external 5V DC supply and programs the CPLD via JTAG using a ByteBlasterII cable. Pin assignments are described for the digital tubes, LEDs, buttons, and buzzer to facilitate user development on the

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You might also like

- Xilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingDocument4 pagesXilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingjackNo ratings yet

- Xilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingDocument4 pagesXilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingjackNo ratings yet

- Xilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyDocument5 pagesXilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyjackNo ratings yet

- Dragon12 Plus Hcs12 Manual Rev FDocument42 pagesDragon12 Plus Hcs12 Manual Rev FWaseem Sadeh100% (1)

- Xilinx XC2C256-7TQ144C - Wireless Technology - Cloud ComputingDocument5 pagesXilinx XC2C256-7TQ144C - Wireless Technology - Cloud ComputingjackNo ratings yet

- 1 PIC Evaluation Board User ManualDocument22 pages1 PIC Evaluation Board User ManualKavin Sengodan100% (1)

- Xilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyDocument4 pagesXilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyjackNo ratings yet

- 1.3inch LCD Module User Manual enDocument15 pages1.3inch LCD Module User Manual enDeddy ChenNo ratings yet

- Xilinx XC2C256-7TQ144I - Wireless Technology - Consumer ElectronicsDocument5 pagesXilinx XC2C256-7TQ144I - Wireless Technology - Consumer ElectronicsjackNo ratings yet

- Xilinx XC2C256-7VQ100I - Consumer Electronics - Wireless TechnologyDocument5 pagesXilinx XC2C256-7VQ100I - Consumer Electronics - Wireless TechnologyjackNo ratings yet

- Xilinx XC2C256-7CP132I - Cloud Computing - Artificial IntelligenceDocument5 pagesXilinx XC2C256-7CP132I - Cloud Computing - Artificial IntelligencejackNo ratings yet

- Apa External Isp AnDocument18 pagesApa External Isp AnMathew P ZachariaNo ratings yet

- Xilinx XC2C64A-5VQ44C - Wireless Technology - 5G TechnologyDocument4 pagesXilinx XC2C64A-5VQ44C - Wireless Technology - 5G TechnologyjackNo ratings yet

- Franky DIY Compressed PDFDocument21 pagesFranky DIY Compressed PDFAlexandre SouzaNo ratings yet

- Xilinx XC2C256-7VQG100C - 5G Technology - Cloud ComputingDocument5 pagesXilinx XC2C256-7VQG100C - 5G Technology - Cloud ComputingjackNo ratings yet

- Xilinx XC2C64A-7QFG48I - Medical Equipment - Artificial IntelligenceDocument4 pagesXilinx XC2C64A-7QFG48I - Medical Equipment - Artificial IntelligencejackNo ratings yet

- Xilinx XC2C256-6CPG132C - Wireless Technology - Internet of ThingsDocument5 pagesXilinx XC2C256-6CPG132C - Wireless Technology - Internet of ThingsjackNo ratings yet

- Xilinx XC2C64A-7VQG100C - Industrial Control - Wireless TechnologyDocument4 pagesXilinx XC2C64A-7VQG100C - Industrial Control - Wireless TechnologyjackNo ratings yet

- Xilinx XC2C256-7TQG144I - Wireless Technology - Internet of ThingsDocument5 pagesXilinx XC2C256-7TQG144I - Wireless Technology - Internet of ThingsjackNo ratings yet

- Xilinx XC2C64A-7VQG44C - 5G Technology - Industrial ControlDocument4 pagesXilinx XC2C64A-7VQG44C - 5G Technology - Industrial ControljackNo ratings yet

- 03 - NuMicro Tools Installation and PracticeDocument27 pages03 - NuMicro Tools Installation and PracticeNhật Phạm LongNo ratings yet

- Xilinx XC2C256-7VQG100I - Medical Equipment - Industrial ControlDocument5 pagesXilinx XC2C256-7VQG100I - Medical Equipment - Industrial ControljackNo ratings yet

- FA Mainboard CV512H-B42Document53 pagesFA Mainboard CV512H-B42Salomon ChiquilloNo ratings yet

- Philips CH - Qfu1.1e LaDocument227 pagesPhilips CH - Qfu1.1e Lanikola166083% (6)

- Xilinx XC2C256-6VQ100C - 5G Technology - Wireless TechnologyDocument5 pagesXilinx XC2C256-6VQ100C - 5G Technology - Wireless TechnologyjackNo ratings yet

- P1022 Qoriq Integrated Processor Design Checklist: Application NoteDocument41 pagesP1022 Qoriq Integrated Processor Design Checklist: Application NoteDanielle AtkinsNo ratings yet

- Xilinx XC2C64A-7VQ44I - Cloud Computing - 5G TechnologyDocument4 pagesXilinx XC2C64A-7VQ44I - Cloud Computing - 5G TechnologyjackNo ratings yet

- Mainboard ESC Model RS485M MDocument35 pagesMainboard ESC Model RS485M MHo Thanh BinhNo ratings yet

- Xilinx XC2C256-7FT256I - Internet of Things - Artificial IntelligenceDocument5 pagesXilinx XC2C256-7FT256I - Internet of Things - Artificial IntelligencejackNo ratings yet

- Daewoo Sl-150t, Sl-150pDocument74 pagesDaewoo Sl-150t, Sl-150plachiondoNo ratings yet

- Training de Pioneer Plasma 6 GeneracinDocument62 pagesTraining de Pioneer Plasma 6 GeneracinToni Martin SebéNo ratings yet

- Philips 32pfl5605 LC9.3LDocument85 pagesPhilips 32pfl5605 LC9.3Ldivubi20040% (1)

- Evaluation Board s08dz60Document2 pagesEvaluation Board s08dz60Warren O LeddaNo ratings yet

- T D A 4 8 6 3 - Getting Started With T D A 4 8 6 3: AN-PFC-TDA 4863-2Document16 pagesT D A 4 8 6 3 - Getting Started With T D A 4 8 6 3: AN-PFC-TDA 4863-2Andi Mahardi HendrawanNo ratings yet

- Xilinx XC2C384-10TQ144I - Medical Equipment - Industrial ControlDocument4 pagesXilinx XC2C384-10TQ144I - Medical Equipment - Industrial ControljackNo ratings yet

- HDM Fpga AsicDocument157 pagesHDM Fpga AsicDeepika KumariNo ratings yet

- S3esk Picoblaze Dac ControlDocument15 pagesS3esk Picoblaze Dac Controlkaruneee7003No ratings yet

- Dell EMC S4048-ON Switch Release Notes: Document Revision HistoryDocument12 pagesDell EMC S4048-ON Switch Release Notes: Document Revision Historylakis lalakis888No ratings yet

- Xilinx XC2C32A-6QFG32I - 5G Technology - Wireless TechnologyDocument4 pagesXilinx XC2C32A-6QFG32I - 5G Technology - Wireless TechnologyjackNo ratings yet

- 003-BCD To7seg cd74hc4543Document11 pages003-BCD To7seg cd74hc45430jonnypapa0No ratings yet

- LPKF CatalogDocument132 pagesLPKF CatalogMarcio MOnte100% (1)

- Log In: Using 74HC595 To Expand Output Pins of A PIC Microcontroller: Assembly CodeDocument8 pagesLog In: Using 74HC595 To Expand Output Pins of A PIC Microcontroller: Assembly CodeSalim BlognetNo ratings yet

- DI-G002-SA GDS-101C UPGRADE COLOUR PCA-6135 To PCA-6742VE 20101120 PDFDocument18 pagesDI-G002-SA GDS-101C UPGRADE COLOUR PCA-6135 To PCA-6742VE 20101120 PDFSeamen 777No ratings yet

- HP Probook 4510s Wistron S-Class Intel Rev Pv-01 SCHDocument62 pagesHP Probook 4510s Wistron S-Class Intel Rev Pv-01 SCHCristian ValentinNo ratings yet

- Xilinx XC2C256-7FTG256I - Internet of Things - 5G TechnologyDocument5 pagesXilinx XC2C256-7FTG256I - Internet of Things - 5G TechnologyjackNo ratings yet

- CV9202H A39Document49 pagesCV9202H A39Zoi LleshiNo ratings yet

- Xilinx XC2C512-10FTG256I - Wireless Technology - Internet of ThingsDocument5 pagesXilinx XC2C512-10FTG256I - Wireless Technology - Internet of ThingsjackNo ratings yet

- Xilinx XC2C256-6FT256C - Consumer Electronics - Medical EquipmentDocument5 pagesXilinx XC2C256-6FT256C - Consumer Electronics - Medical EquipmentjackNo ratings yet

- UG-2864HSWEG01 User Guide PDFDocument20 pagesUG-2864HSWEG01 User Guide PDFSachin KhandareNo ratings yet

- Philips Chassis Tpm5.2e-LaDocument59 pagesPhilips Chassis Tpm5.2e-Larolandas1970No ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipFrom EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNo ratings yet

- Engineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconFrom EverandEngineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconRating: 1 out of 5 stars1/5 (1)

- Neo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23From EverandNeo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23No ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Course Slides 2018Document484 pagesCourse Slides 2018venkatNo ratings yet

- MTech VLSI 1st Year Assignment QuestionsDocument2 pagesMTech VLSI 1st Year Assignment QuestionsG.Kishore Kumar Asst. Professor, ECE DepartmentNo ratings yet

- SPLDS-PPT 1Document88 pagesSPLDS-PPT 1ramakrishnaNo ratings yet

- Chapter 1 Introduction 1Document9 pagesChapter 1 Introduction 1Vijay SagarNo ratings yet

- DatabkDocument1,041 pagesDatabkKikey Stephanie Méndez100% (2)

- 05 Unit V DTEDocument217 pages05 Unit V DTEKrunal WaniNo ratings yet

- BCD To 7 SegmentDocument6 pagesBCD To 7 SegmentAndhe PraveedNo ratings yet

- PSD834 F 2Document129 pagesPSD834 F 2Тестер ХелперовNo ratings yet

- VLSI System DesignDocument91 pagesVLSI System DesigneleenaamohapatraNo ratings yet

- Linear and Digital IC Applications PDFDocument47 pagesLinear and Digital IC Applications PDFgautham100% (3)

- Chap - 05-Digital Hardware ImplementationDocument20 pagesChap - 05-Digital Hardware Implementationcharbelkhalil05No ratings yet

- Mit Academy SDNDocument51 pagesMit Academy SDNkhairul fahmiNo ratings yet

- CS302 MID Term GIGA FILE PDFDocument69 pagesCS302 MID Term GIGA FILE PDFattiqueNo ratings yet

- Chapter 1Document26 pagesChapter 1Kanekii HaiseNo ratings yet

- Introduction To Real-Time Embedded Syste PDFDocument65 pagesIntroduction To Real-Time Embedded Syste PDFbenjarrayNo ratings yet

- Fpga Based Vga Driver and Arcade GameDocument37 pagesFpga Based Vga Driver and Arcade GamefreeTerpNo ratings yet

- ELVIS III InformationDocument21 pagesELVIS III InformationahmedNo ratings yet

- Ece5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Document3 pagesEce5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Daniel MNo ratings yet

- Fpga Lec 3-4 Logic ImplementationDocument64 pagesFpga Lec 3-4 Logic Implementationvikas310No ratings yet

- Digital Electronics and Communication Systems: CurriculumDocument83 pagesDigital Electronics and Communication Systems: CurriculumKishor GowdaNo ratings yet

- Documentation Standards Documentation Standards: Documentation of A Digital System Basic Rules of Block DiagramDocument16 pagesDocumentation Standards Documentation Standards: Documentation of A Digital System Basic Rules of Block DiagramAsher WayneNo ratings yet

- 2017 Book IntroductionToLogicCircuitsLog PDFDocument468 pages2017 Book IntroductionToLogicCircuitsLog PDFCarlos Alberto López DuarteNo ratings yet

- CoreEL TechnologiesDocument10 pagesCoreEL TechnologiesSaurabh SinghNo ratings yet

- Textbook PLD Based Design With VHDL RTL Design Synthesis and Implementation 1St Edition Vaibbhav Taraate Auth Ebook All Chapter PDFDocument53 pagesTextbook PLD Based Design With VHDL RTL Design Synthesis and Implementation 1St Edition Vaibbhav Taraate Auth Ebook All Chapter PDFdeborah.calcote388100% (6)

- FPGAs - CHRONOLOGICAL DEVELOPMENTS AND CHALLENGESDocument13 pagesFPGAs - CHRONOLOGICAL DEVELOPMENTS AND CHALLENGESIAEME PublicationNo ratings yet

- Complex Programmable Logic Device - Wikipedia, The Free EncyclopediaDocument3 pagesComplex Programmable Logic Device - Wikipedia, The Free EncyclopediaSuneelkrishna RallabhandiNo ratings yet

- Embedded System TechnologiesDocument37 pagesEmbedded System TechnologiesjayaprahasNo ratings yet

- Beeprog2C: (Ord - No. 60-0059)Document7 pagesBeeprog2C: (Ord - No. 60-0059)hariz harizNo ratings yet

- Full Download PDF of (Ebook PDF) Advanced Digital Design With The Verilog HDL 2nd Edition All ChapterDocument43 pagesFull Download PDF of (Ebook PDF) Advanced Digital Design With The Verilog HDL 2nd Edition All Chapterlilkovdubrar38100% (7)

- Unit 4 Modulation DevicesDocument99 pagesUnit 4 Modulation Devicesrahul nelakurtiNo ratings yet

Altera CPLD Learning Board Manual

Altera CPLD Learning Board Manual

Uploaded by

Miguel Torres Alvarez0 ratings0% found this document useful (0 votes)

145 views10 pagesThis document describes an Altera CPLD development board intended for learning and prototyping.

The board uses an Altera MAXII EPM240T100C5N CPLD and has 65 I/O ports that are labeled to help users learn how to configure pin assignments. It includes features like 8 digital tubes, 8 LEDs, buttons, a buzzer, and a 50MHz crystal for clocking the CPLD.

The board is powered by an external 5V DC supply and programs the CPLD via JTAG using a ByteBlasterII cable. Pin assignments are described for the digital tubes, LEDs, buttons, and buzzer to facilitate user development on the

Original Description:

Manual del CPLD M240

Original Title

CPLD_M240

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document describes an Altera CPLD development board intended for learning and prototyping.

The board uses an Altera MAXII EPM240T100C5N CPLD and has 65 I/O ports that are labeled to help users learn how to configure pin assignments. It includes features like 8 digital tubes, 8 LEDs, buttons, a buzzer, and a 50MHz crystal for clocking the CPLD.

The board is powered by an external 5V DC supply and programs the CPLD via JTAG using a ByteBlasterII cable. Pin assignments are described for the digital tubes, LEDs, buttons, and buzzer to facilitate user development on the

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

145 views10 pagesAltera CPLD Learning Board Manual

Altera CPLD Learning Board Manual

Uploaded by

Miguel Torres AlvarezThis document describes an Altera CPLD development board intended for learning and prototyping.

The board uses an Altera MAXII EPM240T100C5N CPLD and has 65 I/O ports that are labeled to help users learn how to configure pin assignments. It includes features like 8 digital tubes, 8 LEDs, buttons, a buzzer, and a 50MHz crystal for clocking the CPLD.

The board is powered by an external 5V DC supply and programs the CPLD via JTAG using a ByteBlasterII cable. Pin assignments are described for the digital tubes, LEDs, buttons, and buzzer to facilitate user development on the

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 10

www.sz-21eda.

com

Altera

manual

CPLD

QQ:906606596

Learning

board

www.sz-21eda.com

Table of Contents

A: development board intended use ................................. ..3

Two: development board hardware description ................................. ..4

Three: Hardware Circuit Description ....................................... ..5

www.sz-21eda.com

A: development board intended use

The development board using Altera's MAXII series EPM240T100C5N

chip design. Also compatible EPM570T100C5N ,. To help users reduce

costs and accelerate learning user quick access to the programmable logic

device design and development fields. Provides a hardware platform to

help users quickly learn programmable logic devices.

The development board using the JTAG interface for programming the

chip. Distribution ByteBlasterII download cable can download all FPGA /

CPLD chip Altera Corporation.

Development board has 65 I / O ports are cited by pin out, the board

has marked. Cited by pin out of the I / O user can configure the pin

assignment. Facilitate users to develop their own products. The maximum

development cost savings for the user to learn.

www.sz-21eda.com

Two: development board hardware description

1) MAXII U1 EPM240T100C5

2) 8 dynamic digital tube

3) 8 LED lights

4) BELL

5) five separate keys

6) JTAG download mode

7) Power mode: external 5V DC power supply

8) 50M active crystal

www.sz-21eda.com

Three: Hardware Circuit Description

1 Power supply

Using an external 5V DC power supply. Please note that the polarity of

the external 5V DC power supply. Positive with respect to the.

2 Active Crystals

Using 50M Hz to CPLD's P12 provides crystal clock frequency is

active.

www.sz-21eda.com

3 Digital tube

I / O ports are assigned as follows:

LED1:P86

LED2:P87

LED3:P96

LED4:P89

LED5:P97

LED6:P91

LED7:P92

LED8:P95

AH

LEDA : P85

LEDB : P84

LEDC : P83

LEDD : P82

LEDE : P81

LEDF : P78

LEDG : P77

LEDH : P76

When LED To LED8 LowLEDA To LEDDP For low

power

www.sz-21eda.com

Usually digital tube light

4 LED

I / O ports are assigned as follows:

D30 : P51

D31 : P52

D32 : P53

D33 : P54

D34 : P55

D35 : P56

D36 : P57

D37 : P58

www.sz-21eda.com

When the I / O port is low LED light

5 Keys to use.

I/O Port assigned as follows:

DEV_CLK

:P44

K1

:P29

K2

:P28

K3

:P27

K4

:P26

When key Is low when pressed

www.sz-21eda.com

6 BELL

BELL Use the I / O port, when P50 is low beep sounds

when the BELL

7 No use of I / O

No use of I / O are connected out, see the specific labeling

learning board, the board more cleary.

www.sz-21eda.com

You might also like

- Xilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingDocument4 pagesXilinx XC2C128-7VQ100C - Artificial Intelligence - Cloud ComputingjackNo ratings yet

- Xilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingDocument4 pagesXilinx XC2C128-6VQG100C - 5G Technology - Cloud ComputingjackNo ratings yet

- Xilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyDocument5 pagesXilinx XC2C128-7VQG100C - 5G Technology - Wireless TechnologyjackNo ratings yet

- Dragon12 Plus Hcs12 Manual Rev FDocument42 pagesDragon12 Plus Hcs12 Manual Rev FWaseem Sadeh100% (1)

- Xilinx XC2C256-7TQ144C - Wireless Technology - Cloud ComputingDocument5 pagesXilinx XC2C256-7TQ144C - Wireless Technology - Cloud ComputingjackNo ratings yet

- 1 PIC Evaluation Board User ManualDocument22 pages1 PIC Evaluation Board User ManualKavin Sengodan100% (1)

- Xilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyDocument4 pagesXilinx XC2C128-7VQG100I - Medical Equipment - 5G TechnologyjackNo ratings yet

- 1.3inch LCD Module User Manual enDocument15 pages1.3inch LCD Module User Manual enDeddy ChenNo ratings yet

- Xilinx XC2C256-7TQ144I - Wireless Technology - Consumer ElectronicsDocument5 pagesXilinx XC2C256-7TQ144I - Wireless Technology - Consumer ElectronicsjackNo ratings yet

- Xilinx XC2C256-7VQ100I - Consumer Electronics - Wireless TechnologyDocument5 pagesXilinx XC2C256-7VQ100I - Consumer Electronics - Wireless TechnologyjackNo ratings yet

- Xilinx XC2C256-7CP132I - Cloud Computing - Artificial IntelligenceDocument5 pagesXilinx XC2C256-7CP132I - Cloud Computing - Artificial IntelligencejackNo ratings yet

- Apa External Isp AnDocument18 pagesApa External Isp AnMathew P ZachariaNo ratings yet

- Xilinx XC2C64A-5VQ44C - Wireless Technology - 5G TechnologyDocument4 pagesXilinx XC2C64A-5VQ44C - Wireless Technology - 5G TechnologyjackNo ratings yet

- Franky DIY Compressed PDFDocument21 pagesFranky DIY Compressed PDFAlexandre SouzaNo ratings yet

- Xilinx XC2C256-7VQG100C - 5G Technology - Cloud ComputingDocument5 pagesXilinx XC2C256-7VQG100C - 5G Technology - Cloud ComputingjackNo ratings yet

- Xilinx XC2C64A-7QFG48I - Medical Equipment - Artificial IntelligenceDocument4 pagesXilinx XC2C64A-7QFG48I - Medical Equipment - Artificial IntelligencejackNo ratings yet

- Xilinx XC2C256-6CPG132C - Wireless Technology - Internet of ThingsDocument5 pagesXilinx XC2C256-6CPG132C - Wireless Technology - Internet of ThingsjackNo ratings yet

- Xilinx XC2C64A-7VQG100C - Industrial Control - Wireless TechnologyDocument4 pagesXilinx XC2C64A-7VQG100C - Industrial Control - Wireless TechnologyjackNo ratings yet

- Xilinx XC2C256-7TQG144I - Wireless Technology - Internet of ThingsDocument5 pagesXilinx XC2C256-7TQG144I - Wireless Technology - Internet of ThingsjackNo ratings yet

- Xilinx XC2C64A-7VQG44C - 5G Technology - Industrial ControlDocument4 pagesXilinx XC2C64A-7VQG44C - 5G Technology - Industrial ControljackNo ratings yet

- 03 - NuMicro Tools Installation and PracticeDocument27 pages03 - NuMicro Tools Installation and PracticeNhật Phạm LongNo ratings yet

- Xilinx XC2C256-7VQG100I - Medical Equipment - Industrial ControlDocument5 pagesXilinx XC2C256-7VQG100I - Medical Equipment - Industrial ControljackNo ratings yet

- FA Mainboard CV512H-B42Document53 pagesFA Mainboard CV512H-B42Salomon ChiquilloNo ratings yet

- Philips CH - Qfu1.1e LaDocument227 pagesPhilips CH - Qfu1.1e Lanikola166083% (6)

- Xilinx XC2C256-6VQ100C - 5G Technology - Wireless TechnologyDocument5 pagesXilinx XC2C256-6VQ100C - 5G Technology - Wireless TechnologyjackNo ratings yet

- P1022 Qoriq Integrated Processor Design Checklist: Application NoteDocument41 pagesP1022 Qoriq Integrated Processor Design Checklist: Application NoteDanielle AtkinsNo ratings yet

- Xilinx XC2C64A-7VQ44I - Cloud Computing - 5G TechnologyDocument4 pagesXilinx XC2C64A-7VQ44I - Cloud Computing - 5G TechnologyjackNo ratings yet

- Mainboard ESC Model RS485M MDocument35 pagesMainboard ESC Model RS485M MHo Thanh BinhNo ratings yet

- Xilinx XC2C256-7FT256I - Internet of Things - Artificial IntelligenceDocument5 pagesXilinx XC2C256-7FT256I - Internet of Things - Artificial IntelligencejackNo ratings yet

- Daewoo Sl-150t, Sl-150pDocument74 pagesDaewoo Sl-150t, Sl-150plachiondoNo ratings yet

- Training de Pioneer Plasma 6 GeneracinDocument62 pagesTraining de Pioneer Plasma 6 GeneracinToni Martin SebéNo ratings yet

- Philips 32pfl5605 LC9.3LDocument85 pagesPhilips 32pfl5605 LC9.3Ldivubi20040% (1)

- Evaluation Board s08dz60Document2 pagesEvaluation Board s08dz60Warren O LeddaNo ratings yet

- T D A 4 8 6 3 - Getting Started With T D A 4 8 6 3: AN-PFC-TDA 4863-2Document16 pagesT D A 4 8 6 3 - Getting Started With T D A 4 8 6 3: AN-PFC-TDA 4863-2Andi Mahardi HendrawanNo ratings yet

- Xilinx XC2C384-10TQ144I - Medical Equipment - Industrial ControlDocument4 pagesXilinx XC2C384-10TQ144I - Medical Equipment - Industrial ControljackNo ratings yet

- HDM Fpga AsicDocument157 pagesHDM Fpga AsicDeepika KumariNo ratings yet

- S3esk Picoblaze Dac ControlDocument15 pagesS3esk Picoblaze Dac Controlkaruneee7003No ratings yet

- Dell EMC S4048-ON Switch Release Notes: Document Revision HistoryDocument12 pagesDell EMC S4048-ON Switch Release Notes: Document Revision Historylakis lalakis888No ratings yet

- Xilinx XC2C32A-6QFG32I - 5G Technology - Wireless TechnologyDocument4 pagesXilinx XC2C32A-6QFG32I - 5G Technology - Wireless TechnologyjackNo ratings yet

- 003-BCD To7seg cd74hc4543Document11 pages003-BCD To7seg cd74hc45430jonnypapa0No ratings yet

- LPKF CatalogDocument132 pagesLPKF CatalogMarcio MOnte100% (1)

- Log In: Using 74HC595 To Expand Output Pins of A PIC Microcontroller: Assembly CodeDocument8 pagesLog In: Using 74HC595 To Expand Output Pins of A PIC Microcontroller: Assembly CodeSalim BlognetNo ratings yet

- DI-G002-SA GDS-101C UPGRADE COLOUR PCA-6135 To PCA-6742VE 20101120 PDFDocument18 pagesDI-G002-SA GDS-101C UPGRADE COLOUR PCA-6135 To PCA-6742VE 20101120 PDFSeamen 777No ratings yet

- HP Probook 4510s Wistron S-Class Intel Rev Pv-01 SCHDocument62 pagesHP Probook 4510s Wistron S-Class Intel Rev Pv-01 SCHCristian ValentinNo ratings yet

- Xilinx XC2C256-7FTG256I - Internet of Things - 5G TechnologyDocument5 pagesXilinx XC2C256-7FTG256I - Internet of Things - 5G TechnologyjackNo ratings yet

- CV9202H A39Document49 pagesCV9202H A39Zoi LleshiNo ratings yet

- Xilinx XC2C512-10FTG256I - Wireless Technology - Internet of ThingsDocument5 pagesXilinx XC2C512-10FTG256I - Wireless Technology - Internet of ThingsjackNo ratings yet

- Xilinx XC2C256-6FT256C - Consumer Electronics - Medical EquipmentDocument5 pagesXilinx XC2C256-6FT256C - Consumer Electronics - Medical EquipmentjackNo ratings yet

- UG-2864HSWEG01 User Guide PDFDocument20 pagesUG-2864HSWEG01 User Guide PDFSachin KhandareNo ratings yet

- Philips Chassis Tpm5.2e-LaDocument59 pagesPhilips Chassis Tpm5.2e-Larolandas1970No ratings yet

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- VLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipFrom EverandVLSI Design for Video Coding: H.264/AVC Encoding from Standard Specification to ChipNo ratings yet

- Engineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconFrom EverandEngineering the CMOS Library: Enhancing Digital Design Kits for Competitive SiliconRating: 1 out of 5 stars1/5 (1)

- Neo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23From EverandNeo Geo Architecture: Architecture of Consoles: A Practical Analysis, #23No ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksFrom EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksNo ratings yet

- The Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsFrom EverandThe Fourth Terminal: Benefits of Body-Biasing Techniques for FDSOI Circuits and SystemsSylvain ClercNo ratings yet

- Course Slides 2018Document484 pagesCourse Slides 2018venkatNo ratings yet

- MTech VLSI 1st Year Assignment QuestionsDocument2 pagesMTech VLSI 1st Year Assignment QuestionsG.Kishore Kumar Asst. Professor, ECE DepartmentNo ratings yet

- SPLDS-PPT 1Document88 pagesSPLDS-PPT 1ramakrishnaNo ratings yet

- Chapter 1 Introduction 1Document9 pagesChapter 1 Introduction 1Vijay SagarNo ratings yet

- DatabkDocument1,041 pagesDatabkKikey Stephanie Méndez100% (2)

- 05 Unit V DTEDocument217 pages05 Unit V DTEKrunal WaniNo ratings yet

- BCD To 7 SegmentDocument6 pagesBCD To 7 SegmentAndhe PraveedNo ratings yet

- PSD834 F 2Document129 pagesPSD834 F 2Тестер ХелперовNo ratings yet

- VLSI System DesignDocument91 pagesVLSI System DesigneleenaamohapatraNo ratings yet

- Linear and Digital IC Applications PDFDocument47 pagesLinear and Digital IC Applications PDFgautham100% (3)

- Chap - 05-Digital Hardware ImplementationDocument20 pagesChap - 05-Digital Hardware Implementationcharbelkhalil05No ratings yet

- Mit Academy SDNDocument51 pagesMit Academy SDNkhairul fahmiNo ratings yet

- CS302 MID Term GIGA FILE PDFDocument69 pagesCS302 MID Term GIGA FILE PDFattiqueNo ratings yet

- Chapter 1Document26 pagesChapter 1Kanekii HaiseNo ratings yet

- Introduction To Real-Time Embedded Syste PDFDocument65 pagesIntroduction To Real-Time Embedded Syste PDFbenjarrayNo ratings yet

- Fpga Based Vga Driver and Arcade GameDocument37 pagesFpga Based Vga Driver and Arcade GamefreeTerpNo ratings yet

- ELVIS III InformationDocument21 pagesELVIS III InformationahmedNo ratings yet

- Ece5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Document3 pagesEce5017 Digital-Design-with-fpga Eth 1.0 40 Ece5017Daniel MNo ratings yet

- Fpga Lec 3-4 Logic ImplementationDocument64 pagesFpga Lec 3-4 Logic Implementationvikas310No ratings yet

- Digital Electronics and Communication Systems: CurriculumDocument83 pagesDigital Electronics and Communication Systems: CurriculumKishor GowdaNo ratings yet

- Documentation Standards Documentation Standards: Documentation of A Digital System Basic Rules of Block DiagramDocument16 pagesDocumentation Standards Documentation Standards: Documentation of A Digital System Basic Rules of Block DiagramAsher WayneNo ratings yet

- 2017 Book IntroductionToLogicCircuitsLog PDFDocument468 pages2017 Book IntroductionToLogicCircuitsLog PDFCarlos Alberto López DuarteNo ratings yet

- CoreEL TechnologiesDocument10 pagesCoreEL TechnologiesSaurabh SinghNo ratings yet

- Textbook PLD Based Design With VHDL RTL Design Synthesis and Implementation 1St Edition Vaibbhav Taraate Auth Ebook All Chapter PDFDocument53 pagesTextbook PLD Based Design With VHDL RTL Design Synthesis and Implementation 1St Edition Vaibbhav Taraate Auth Ebook All Chapter PDFdeborah.calcote388100% (6)

- FPGAs - CHRONOLOGICAL DEVELOPMENTS AND CHALLENGESDocument13 pagesFPGAs - CHRONOLOGICAL DEVELOPMENTS AND CHALLENGESIAEME PublicationNo ratings yet

- Complex Programmable Logic Device - Wikipedia, The Free EncyclopediaDocument3 pagesComplex Programmable Logic Device - Wikipedia, The Free EncyclopediaSuneelkrishna RallabhandiNo ratings yet

- Embedded System TechnologiesDocument37 pagesEmbedded System TechnologiesjayaprahasNo ratings yet

- Beeprog2C: (Ord - No. 60-0059)Document7 pagesBeeprog2C: (Ord - No. 60-0059)hariz harizNo ratings yet

- Full Download PDF of (Ebook PDF) Advanced Digital Design With The Verilog HDL 2nd Edition All ChapterDocument43 pagesFull Download PDF of (Ebook PDF) Advanced Digital Design With The Verilog HDL 2nd Edition All Chapterlilkovdubrar38100% (7)

- Unit 4 Modulation DevicesDocument99 pagesUnit 4 Modulation Devicesrahul nelakurtiNo ratings yet