Professional Documents

Culture Documents

Compal La-8981p r1.0 Schematics

Compal La-8981p r1.0 Schematics

Uploaded by

Kiran VeesamOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Compal La-8981p r1.0 Schematics

Compal La-8981p r1.0 Schematics

Uploaded by

Kiran VeesamCopyright:

Available Formats

A

ZZZ

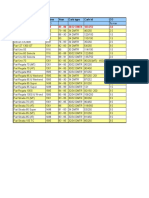

PCB

MB

DA80000TI10

ZZZ1

1

DDR

Samsung

X76-S@

X76418BOL01

ZZZ1

DDR

Hynix

X76-H@

Compal Confidential

X76418BOL02

S1

Frame

Nvdia(T30L) + DDRIIIL

V0JET (A210)_ LA8981P

REV: 1.0

2012-06-11

The content in this document contains confidential information of Compal Electronics, Inc.

that is protected under all applicable trade secrets laws and regulations.

If you are not the intended recipient or otherwise authorized to receive such information,

please do not copy, distribute or otherwise use the information contained herein and please

destroy this communication accordingly.

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

Cover Page

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

E

Sheet

of

35

Rev

1.0

Compal Confidential

Model Name : NVIDIA T30L System Block Diagram

12MHz

32KHz

DDR3L

1GB

Power ON

PMU

CORE_PWR_REQ

TPS6591104

CPU_PWR_REQ

JTAG

Debug

Test Point

SYS_RESET_N

VIN

PWR_I2C

PMU_32K_IN

PWR_I2S

UART4

TPS62361

Audience

eS305

Audio Codec

WM8903

EEPROM

AT24C02C

Thermal

NCT72

BATTERY

Nvidia

Touch Panel

Control

T30L

GEN2_I2C

LVDS

LVDS Transmitter

SN75LVDS83

Client

Standard USB

Host

CAMERA

2M

UART2

Broadcom

BCM47511

UART3

SDMMC3

AzureWave

AW-NH660

LCD

Micro USB

3

Speaker x 2

(1W)

GPS Antenna

GEN2_I2C

10.1" LCD

1280*800

Audio AMP

APA2010

MIC & HP Jack

BT/WLAN Antenna

3

CIS(MIPI)

CAM_I2C

GEN1_I2C

SDMMC4

(1.8V)

eMMC

SDMMC1

(3.3V)

GYRO Sensor IME G-Sensor

KXTF9-4100

MPU-3050

HS uSD slot

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Title

SYSTEM BLOCK

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

E

Sheet

of

35

Rev

1.0

V0JET (A210)

Voltage Rails

V0JET

VDD_1V8_PMU_VRTC

VDD_PMU_LDO4

(VDD_1V2_RTC_TEGRA)

VDD_PMU_LDO5

(+VDD_3V3_SDMMC1_TEGRA)

VDD_PMU_LDO6

(+AVDD_1V2_DSI_CSI_TEGRA)

VDD_PMU_LDO7

(+AVDD_1V1_PLL_TEGRA)

VDD_PMU_LDO8

(+VDD_1V0_DDR_HS_TEGRA)

L: A211

H:

A210

PCB_ID1

L:

H:

NH660

PCB_ID2

L:

H: A210/A211

PCB_ID3

L:

H: A210/A211

ON

V0JET

Vender PN

ON

K4B2G0846D-HYH9

DDR3L (Samaung)

H5TC2G83CFR-H9A

(Hynix)

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

ON

DDR RX power rail

OFF

OFF

ON

T30 VDD_CPU Power

OFF

OFF

ON

T30 VDD_CORE Power

OFF

OFF

DDR power rail

OFF

OFF

OFF

OFF

ON

OFF

OFF

ON

OFF

OFF

ON

Power for RTC and always-on core logic

VDD_1V2_MEM

VDD_1V35_DDR3_MEM

VDD_1V0_GEN

VDD_1V2_SOC

VDD_1V35_DDR3_MEM

VDD_PMU_LDO1

VDD_PMU_LDO2

VDD_PMU_LDO3

ON

Power for always-on

VDD_5V0_SBY

PVT

IDLE

AC or battery power rail for power circuit.

B+

DVT

DCIN

Adapter power supply (12V)

VIN

EVT

PCB_ID0

Standby

ACIN

Power Plane

T30 VDD_RTC power rail

OFF

OFF

ON

T30 VDDIO_SDMMC1 power rail

OFF

OFF

ON

T30 AVDD_DSI power rail

OFF

OFF

T30 AVDD_PLL power rail

OFF

OFF

T30 VDD_DDR_HS power rail

OFF

OFF

+5VS

5V System power rail

OFF

OFF

+3VALW

3.3V System power rail

OFF

OFF

OFF

OFF

MP

Acer PN

NAND_D4

NAND_D5

KN.2GB0B.038

KN.2GB0G.003

EDJ2108EDBG-DJ-FEl

KN.2GB09.001

(Elpida)

DVT

PVT

Board ID0

V0JET

EVT

0

Board ID1

MP

+3VS

3.3V power rail for standby mode

1.8V System power rail

OFF

OFF

+AVDD_1V8_USB_PLL_TEGRA

T30 USB power rail

OFF

OFF

+T30S_USB1

+VDD_2V85_EMMC

+LEDVDD

+LCDVDD

+VDD_1V8_AUDIO_LDO

+2.8V_2M_AVDD_R

+VDD_3V3_SDCARD

+VDD_CAM_1V8

+VDD_3V3_FUSE_TEGRA

+VDD_1V8_SENSOR

+VDD_3V3_SENSOR

USB power rail

OFF

OFF

OFF

OFF

LCD power rail

OFF

OFF

LCD power rail

OFF

OFF

Audio power rail

OFF

OFF

CAMERA power rail

OFF

OFF

Micro SD power rail

OFF

OFF

CAMERA power rail

OFF

OFF

T30 VPP_Fuse power rail

OFF

OFF

3.3V Sensor power rail

OFF

OFF

3.3V Sensor power rail

OFF

OFF

VDD_1V8_GEN

Core voltage for EMMC

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

Notes List

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

1

Sheet

of

35

Rev

1.0

4/22 GMI

LCD_DC0

LCD_DC1

CRT_HSYNC

CRT_VSYNC

DDC_SCL

DDC_SDA

HDMI_INT

AG12

LCD_D00

LCD_D01

LCD_D02

LCD_D03

LCD_D04

LCD_D05

LCD_D06

LCD_D07

LCD_D08

LCD_D09

LCD_D10

LCD_D11

LCD_D12

LCD_D13

LCD_D14

LCD_D15

LCD_D16

LCD_D17

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

(15)

GMI_A16

GMI_A17

GMI_A18

GMI_A19

GMI_CS0*

GMI_CS1*

GMI_CS2*

GMI_CS3*

GMI_CS4*

GMI_CS6*

GMI_CS7*

GMI_ADV*

GMI_CLK

GMI_RST*

GMI_WAIT

GMI_WP*

GMI_IORDY

PD

AJ9

AG10

AH12

PD

PD

PD

AG15

AJ15

AC10

AJ13

AH10

PU

PU

PU

PU

PU

AE15

AE12

PD

PD

AD13

AJ16

PU

PU

AG14

AJ10

Z

Z

AG13

GMI_OE*

GMI_WR*

LCD_PWM_OUT (15)

DISPOFF# (15)

EN_T30S_FUSE_3V3 (23)

IMG_EN (15)

PCB_ID0

PCB_ID1

PCB_ID2

E6

A4

GMI_DQS

BOOT_PD

0_0402_5%

R403

1

1

1

X76@

2

1 100K_0402_5%

NAND_D5

R43

2 X76@

1 100K_0402_5%

NAND_D6

R84

1 100K_0402_5%

NAND_D7

R85

1 100K_0402_5%

NAND_D4

R5

2 X76@

1 100K_0402_5%

NAND_D5

R6

1 100K_0402_5%

NAND_D6

R7

1 100K_0402_5%

NAND_D7

R8

1 100K_0402_5%

PCB_ID0

R63

PCB_ID1

R87

BOARD_ID1

R78

R88

V10 M

R17

GEN2_I2C_SCL (15)

GEN2_I2C_SDA (15)

1 100K_0402_5%

A210@

1 100K_0402_5%

1 100K_0402_5%

R12

PCB_ID0

R152 2

PCB_ID1

R153 2

PCB_ID2

R154 2

1 100K_0402_5%

A211@

1 100K_0402_5%

A211@

1 100K_0402_5%

A211@

BOARD_ID0

R79

BOARD_ID1

R89

2

@

2

@

EN_WIFI_VDD

2.2K_0402_1%

1 100K_0402_5%

NH660@

1 100K_0402_5%

R10

+VDD_3V3_GMI_TEGRA

1 100K_0402_5%

R100 2

BOARD_ID0

SD_DET# (21,7) +VDD_3V3_GMI_TEGRA

FORCE_RECOVERY#

NOR_BOOT

R22 2

R11

GEN2_I2C_SCL

GEN2_I2C_SDA

R38

PCB_ID2

Z

Z

+VDD_3V3_GMI_TEGRA

NAND_D4

A210@

100K_0402_5%

1 R24

+VDD_3V3_GMI_TEGRA

TS_PWR_EN

2 100K_0402_5% +VDD_3V3_GMI_TEGRA

G3 Z

TS_RST# (15)

+VDD_3V3_GMI_TEGRA

G5

G7

1 100K_0402_5%

Change BOM structure

@ R18

100K_0402_5%

TEMP_ALERT# (7)

2.2K_0402_1%

EN_3V3_EMMC1 (14)

EN_3V3_SDCARD (21)

X76@

R14 1

LVDS_SHTDN# (15)

R2

+VDD_3V3_GMI_TEGRA

TS_INT# (15)

EN_SENSOR_3V3

CHARGER_STAT (27)

C3

BOOT_PD

PU

D4

B4

D5

F2

G4

VIB_EN_T30S (22)

TS_PWR_EN (15)

EN_VDDLCD_T30S (15)

EN_WIFI_VDD (25)

10K_0402_5%

R1411 1 @

PU

PU

1

BOARD_ID0

1

BOARD_ID1

J4

K7

F6

A3

D6

J5

J7

1 100K_0402_5%

EN_SENSOR_3V3 (23)

H4

J6

C4

J3

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

LCD_DE (15)

LCD_HSYNC (15)

LCD_VSYNC (15)

100K_0402_5%

LCD_SCK

LCD_CS0*

LCD_CS1*

LCD_SDOUT

LCD_SDIN

AE8

AF12

AD10

AK15

AK16

AK10

AK12

AG16

AG8

AD15

AK9

AJ12

AF9

AC12

AD12

AE18

AF13

AH15

AE9

AE10

AH13

AH9

AE13

AK13

NV_LCD_PCLK

1 100K_0402_5%

1 100K_0402_5%

V10 M

DVT BOARD_ID[1..0] -->0..1

DVT PCB_ID[3..00] --> 1111

+VDD_3V3_GMI_TEGRA

T30L-P-A3-1.2G_FCBGA728

1

LCD_PWR0

LCD_PWR1

LCD_PWR2

PU

PD

PU

PU

100K_0402_5%

LCD_M1

PD

R1

K4B2G0846D-HYH9 [7..4] -->0000

H5TC2G83CFR-H9A [7..4] -->0001

NAND_D4

NAND_D5

NAND_D6

NAND_D7

LCD_D00

LCD_D01

LCD_D02

LCD_D03

LCD_D04

LCD_D05

LCD_D06

LCD_D07

LCD_D08

LCD_D09

LCD_D10

LCD_D11

LCD_D12

LCD_D13

LCD_D14

LCD_D15

LCD_D16

LCD_D17

LCD_D18

LCD_D19

LCD_D20

LCD_D21

LCD_D22

LCD_D23

AG11

AH16

AG9

AF16

AF10

NAND_D0

Change BOM structure to DDR3L

LCD_PCLK

LCD_WR*

LCD_DE

LCD_HSYNC

LCD_VSYNC

(1.8 ~ 3.3V)

NAND[D0:D3] -- boot strap EMMC 0001

NAND[D4:D7] -- ram code

For Boost Strap

VDDIO_LCD_1

VDDIO_LCD_2

C2

NAND_D0

BOOT_PD

2

C4

Z

Z

Z

Z

Z

Z

Z

Z

PD

PD

PD

PD

Z

Z

Z

Z

AB13

AC13

F8

G6

D3

E4

G2

D2

B3

G1

H6

F4

E7

F3

F5

F7

J2

F1

20mA

GMI_AD00

GMI_AD01

GMI_AD02

GMI_AD03

GMI_AD04

GMI_AD05

GMI_AD06

GMI_AD07

GMI_AD08

GMI_AD09

GMI_AD10

GMI_AD11

GMI_AD12

GMI_AD13

GMI_AD14

GMI_AD15

C1

0.1U_0402_10V7K

0.1U_0402_10V7K

+3VS

VDDIO_GMI_1

VDDIO_GMI_2

VDDIO_GMI_3

C147

C1

C2

D1

2

U1I

(1.8/3.3V)

110mA

+3VS

0.1U_0402_10V7K

12P_0402_50V4Z 12P_0402_50V4Z

2

8/22 LCD

U1D

RF

+VDD_3V3_LCD_TEGRA

+VDD_3V3_GMI_TEGRA

LCD_PCLK (15)

C3

+VDD_3V3_GMI_TEGRA

27NH_LQG15HS27NJ02D_5%_0402

2

1

C165

C164

4.7U_0402_6.3V6M

L49

LCD_PCLK_R 1

1

3300P_0402_50V7K

R453

2

1

47_0402_5%

NV_LCD_PCLK

R23

47K_0402_1%

2

+VDD_1V8_SYS_TEGRA

9/29 Leakage Issue

U1K

(22,7) VOL_DOWN#

B

A

1

4

Q44

S TR DMN3150LW-7 1N SOT-323-3

S

Vth=1.4V

74AUP1G02GW_TSSOP5

AVDD_HDMI_1

AVDD_HDMI_2

(3.3V)

HDMI_TXCN

HDMI_TXCP

HDMI_TXD0N

HDMI_TXD0P

@R420

0_0402_5%

2

HDMI_TXD1N

HDMI_TXD1P

HDMI_TXD2N

HDMI_TXD2P

AF7

AVDD_HDMI_PLL

(1.8V)

@R425

0_0402_5%

HDMI_PROBE

AJ4

AH4

AH6

AJ6

AK7

AJ7

+VDD_1V8_SDMMC4_TEGRA

U1E

AG1

SDMMC4 : eMMC

5/22 SDMMC4

AH3

(1.2/1.8V)

20mA

VDD_1V8_GEN

HDMI_RSET

D8

HDMI_RSET

AK3

AK4

AE4

AF4

@ R26

1K_0402_1%

C5

4.7U_0402_6.3V6M

T30L-P-A3-1.2G_FCBGA728

2

C6

VDDIO_SDMMC4

SDMMC4_DAT0

SDMMC4_DAT1

SDMMC4_DAT2

SDMMC4_DAT3

SDMMC4_DAT4

SDMMC4_DAT5

SDMMC4_DAT6

SDMMC4_DAT7

0.1U_0402_10V7K

SDMMC4_CLK

SDMMC4_CMD

+VDD_1V8_SYS_TEGRA

2

C115

U54

1

2

3

4

A0

A1

A2

GND

1

VCC

WP

SCL

SDA

8

7

6

5

SDMMC4_RST*

9/22 VDAC

AK6

AVDD_VDAC

(2.8V)

VDAC_R

VDAC_G

VDAC_B

Z

Z

Z

Z

Z

Z

Z

Z

A9

C7

PU

PU

C9

EMMC_DA0

EMMC_DA1

EMMC_DA2

EMMC_DA3

EMMC_DA4

EMMC_DA5

EMMC_DA6

EMMC_DA7

(14)

(14)

(14)

(14)

(14)

(14)

(14)

(14)

EMMC_CLK (14)

EMMC_CMD (14)

EMMC_RST# (14)

AB7

AA9

AA7

A

BOARD_ID_WP (7)

PWR_I2C_SCL (16,17,29,31,33,7)

PWR_I2C_SDA (16,17,29,31,33,7)

VDAC_VREF

need check with WC of GPIO

AT24C02C-XHM-T_TSSOP8

VDAC_RSET

need check with SW Roger

AA5

AA6

T30L-P-A3-1.2G_FCBGA728

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

T30L-P-A3-1.2G_FCBGA728

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

B9

B6

C6

A6

B7

A7

D7

D9

U1J

0.1U_0402_10V6K

PN:SA00004KS00

2k bit

A

47K_0402_1%

2 FORCE_RECOVERY#

2

G

R54

1M_0402_1%

10/22 HDMI

R90

1

U55

(22,7) VOL_UP#

Modify R10&R11 from mount to unmount

G Vcc

T30L-P-A3-1.2G_FCBGA728

Title

T30L-LCD/CRT/HDMI/NAND

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

1

Sheet

of

35

Rev

1.0

1

C13

C12

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

SDMMC1 : SD card

+VDD_3V3_SDMMC1_TEGRA

1

C11

C10

2

4.7U_0402_6.3V6M

1

D

4.7U_0402_6.3V6M

+VDD_1V35_MEM_TEGRA

+VDD_1V35_MEM_TEGRA U1C

VDD_1V35_DDR3_MEM

U1P

PU

PU

SDMMC_CLK (21)

SDMMC_CMD (21)

0.1U_0402_10V7K

M6

N6

SDMMC1_CLK

SDMMC1_CMD

SDMMC_DAT0 (21)

SDMMC_DAT1 (21)

SDMMC_DAT2 (21)

SDMMC_DAT3 (21)

C15

SDMMC1_DAT0

SDMMC1_DAT1

SDMMC1_DAT2

SDMMC1_DAT3

PU

PU

PU

PU

C22

K1

K3

K2

K4

0.1U_0402_10V7K

VDDIO_SDMMC1

4.7U_0402_6.3V6M

C17 1

(1.8/2.8 ~ 3.3V)

J1

C14

20mA

0.1U_0402_10V7K

17/22 SDMMC1

VDD_PMU_LDO5

50OHM_NETCLASS2

3/22 DDR3/LPDDR2

740mA

DDR_DQ[31..0]

(1.2/1.25/1.35/1.5)

G16

G19

H15

H16

H18

H19

H21

H22

J15

J16

J18

J19

J21

J23

K22

K23

VDDIO_DDR_01

VDDIO_DDR_02

VDDIO_DDR_03

VDDIO_DDR_04

VDDIO_DDR_05

VDDIO_DDR_06

VDDIO_DDR_07

VDDIO_DDR_08

VDDIO_DDR_09

VDDIO_DDR_10

VDDIO_DDR_11

VDDIO_DDR_12

VDDIO_DDR_13

VDDIO_DDR_14

VDDIO_DDR_15

VDDIO_DDR_16

DDR_DQ00

DDR_DQ01

DDR_DQ02

DDR_DQ03

DDR_DQ04

DDR_DQ05

DDR_DQ06

DDR_DQ07

DDR_DQ08

DDR_DQ09

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

+VDD_3V3_SDMMC1_TEGRA

+VDD_3V3_DDR_RX_TEGRA

50mA

CP_GPIO (27)

DDR_DM0

DDR_DM1

DDR_DM2

DDR_DM3

VDD_PMU_LDO8

30mA

E10

H9

C24

: WIFI

(1.00V)

VDD_DDR_HS_1

VDD_DDR_HS_2

DDR_DQS0N

DDR_DQS0P

4.7U_0402_6.3V6M

C110

1U_0402_10V6K

C109

1U_0402_10V6K

C111

1U_0402_10V6K

C30

+VDD_1V8_SDMMC3_TEGRA

VDD_DDR_RX

+VDD_1V0_DDR_HS_TEGRA

T30L-P-A3-1.2G_FCBGA728

SDMMC3

(2.8/3.3V)

A27

C23

+3VS

4.7U_0402_6.3V6M

1U_0402_10V6K

C21

C20

1U_0402_10V6K

PD

Z

C19

K5

N5

1U_0402_10V6K

CLK2_OUT

CLK2_REQ

Z

Z

1U_0402_10V6K

GPIO_PV2

GPIO_PV3

M5

M1

C18

SDMMC1_COMP_PDR30 1

33.2_0402_1%

K6

SDMMC1_COMP_PD

1U_0402_10V6K

SDMMC1_COMP_PU

33.2_0402_1%

SDMMC1_COMP_PUR29 1

L4

DDR_DQS1N

DDR_DQS1P

DDR_DQS2N

DDR_DQS2P

DDR_DQS3N

DDR_DQS3P

6/22 SDMMC3

(1.8/2.8 ~ 3.3V)

24mA

C26 1

G24

VDDIO_SDMMC3

C25

0.1U_0402_10V7K

4.7U_0402_6.3V6M

VDD_1V8_GEN

L27

J26

J28

K26

J27

K25

K24

K28

SDMMC3_DAT0

SDMMC3_DAT1

SDMMC3_DAT2

SDMMC3_DAT3

SDMMC3_DAT4

SDMMC3_DAT5

SDMMC3_DAT6

SDMMC3_DAT7

WFMMC_DAT0 (25)

WFMMC_DAT1 (25)

WFMMC_DAT2 (25)

WFMMC_DAT3 (25)

EN_3V3_EMMC (14)

R64

G30 PU

J29 PU

SDMMC3_CLK

SDMMC3_CMD

J25

SDMMC3_COMP_PU

K27

SDMMC3_COMP_PD

PU

PU

PU

PU

PU

PU

PU

PU

1 100K_0402_5%

WFMMC_CLK (25)

WFMMC_CMD (25)

33.2_0402_1%

SDMMC3_COMP_PUR31 1

SDMMC3_COMP_PDR32 1

33.2_0402_1%

DDR_BA0

DDR_BA1

DDR_BA2

NV DG V1.1

15/22 HSIC

V6

V7

DDR_CKE0

DDR_CKE1

2.2P_0402_50V8

W6

DDR_CLKN

(1.8V)

0.01U_0402_25V7

IC_USB_DN

IC_USB_DP

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

50OHM_NETCLASS2

DDR_DM0 (11)

DDR_DM1 (12)

DDR_DM2 (11)

DDR_DM3 (12)

50OHM_NETCLASS2

50OHM_NETCLASS2

50OHM_NETCLASS2

B12

A12

DDR_DQS1_PAIR

E24

D23

DDR_DQS2_PAIR

DDR_DQS0N (11)

DDR_DQS0P (11)

DDR_DQS0_PAIR

DDR_DQS1N (12)

DDR_DQS1P (12)

DDR_DQS1_PAIR

DDR_DQS2N (11)

DDR_DQS2P (11)

DDR_DQS2_PAIR

E12

D11

DDR_DQS3N (12)

DDR_DQS3P (12)

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

DDR_A[14..0]

50OHM_NETCLASS2

(11,12)

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_RAS# (11,12)

DDR_CAS# (11,12)

DDR_WE# (11,12)

B

DDR_BA0 (11,12)

DDR_BA1 (11,12)

DDR_BA2 (11,12)

DDR_CS0# (11,12)

DDR_A15 (11,12)

D16 Trace 50ohm

F18

DDR_ODT0 (11,12)

F19 Trace 50ohm

E18

DDR_CKE0 (11,12)

D27

D26

E9

F9

DDR_CLKN (11,12)

DDR_CLKP (11,12)

1

10K_0402_5%

R55

QUSE0

QUSE1

QUSE2

QUSE3

+VDD_1V35_MEM_TEGRA

DDR_RESET# (11,12)

R33

2 0_0402_5%

R34

2 0_0402_5%

2

C482

16/22 IC_USB

DDR_QUSE0

DDR_QUSE1

DDR_QUSE2

DDR_QUSE3

R20

45.3_0402_1%

2

R21

45.3_0402_1%

AVDD_IC_USB

DDR_DQS0_PAIR

C19

1

T30L-P-A3-1.2G_FCBGA728

V9

11

12

B24

C24

DDR_CLKP

DDR_RESET

U1N

5

6

10

B18 DDR_CLKN

C18 DDR_CLKP

DDR_CLK_N

DDR_CLK

C2674

HSIC_REXT

F16 Trace 50ohm

E19 Trace 50ohm

DDR_ODT0

DDR_ODT1

HSIC_DATA

HSIC_STROBE

2

3

F15 Trace 50ohm

E21 Trace 50ohm

F21 Trace 50ohm

DDR_CS0_N

DDR_CS1_N

VDDIO_HSIC

U1M

(1.2V)

(11,12)

D19 Trace 50ohm

DDR_WE_N

T30L-P-A3-1.2G_FCBGA728

W7

DDR_DQ0

DDR_DQ1

DDR_DQ2

DDR_DQ3

DDR_DQ4

DDR_DQ5

DDR_DQ6

DDR_DQ7

DDR_DQ8

DDR_DQ9

DDR_DQ10

DDR_DQ11

DDR_DQ12

DDR_DQ13

DDR_DQ14

DDR_DQ15

DDR_DQ16

DDR_DQ17

DDR_DQ18

DDR_DQ19

DDR_DQ20

DDR_DQ21

DDR_DQ22

DDR_DQ23

DDR_DQ24

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ29

DDR_DQ30

DDR_DQ31

G18 Trace 50ohm

D17 Trace 50ohm

DDR_RAS_N

DDR_CAS_N

+VDD_1V8_SDMMC3_TEGRA

2

C22

D12

E22

G12

D20

G15

A18

D14

B19

A16

C21

A15

D15

C16

E16

D18

E15

A19

B16

DDR_A00

DDR_A01

DDR_A02

DDR_A03

DDR_A04

DDR_A05

DDR_A06

DDR_A07

DDR_A08

DDR_A09

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

U1O

D24

B25

A25

D21

A24

A21

A22

B22

C15

A13

C12

B13

C13

A10

B10

C10

G22

D22

D25

F23

G21

E25

F24

F22

F13

G13

G10

D13

G9

F10

D10

F12

+VDD_1V35_MEM_TEGRA

Note:Place at the T-point

DDR_COMP_PU

W8

W9

DDR_COMP_PD

B21

DDR_COMP_PU

R35 1

2 40.2_0402_1%

B15

DDR_COMP_PD

R36 1

2 40.2_0402_1%

T30L-P-A3-1.2G_FCBGA728

IC_USB_REXT

V8

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

T30SL-OSC/PLL/SYS/DDR

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

1

Sheet

of

35

Rev

1.0

U1L

11/22 USB

+AVDD_3V3_USB_TEGRA

U12

1

C27

+VDD_1V8_AUDIO_TEGRA

U1Q

RF note

13/22 AUDIO

CLK1_OUT

CLK1_REQ

(1.8/3.3V)

C27

F26

AUDIO_CLK

R37

2 0_0402_5%

Option

AUDIO_CLK_R (17)

VDD_1V8_GEN

+T30S_USB1

W3

W2

USB1_DN

USB1_DP

USB1_DN (21)

USB1_DP (21)

For CLIENT USB

1

T7

ACC1_DETECT

1

R1422

2 1K_0402_5%

USB1_ID (21)

+AVDD_1V8_USB_PLL_TEGRA

DAP1_SCLK

DAP1_FS

DAP1_DOUT

DAP1_DIN

G29

D28

G26

G25

PD

PD

PD

C28

C29

G27

F27

PD

PD

PD

PD

H27

A28

PU

PU

B28

J24

F29

F28

PU

PU

PU

PD

D29

G28

F25

E27

B27

D30

PU

PU

PU

PU

PD

PD

AUDIO_SEL (16)

AUDIO_RST# (16)

ES305_INT_R (16)

1

2

@ R399 0_0402_5%

L4

4

SPDIF_IN

SPDIF_OUT

AUDIO_SCLK2 (16)

AUDIO_FS2 (16)

AUDIO_DOUT2 (16)

AUDIO_DIN2 (16)

(31,7) CORE_PWR_REQ

SPI1_SCK

SPI1_CS0*

SPI1_MOSI

SPI1_MISO

R323

1M_0402_1%

(1.8V)

10mA

U4

MPZ1005S300CT_2P

5

C29

DAP2_SCLK

DAP2_FS

DAP2_DOUT

DAP2_DIN

FDG6331L_SC70-6

SB00000SM00

Q34

AVDD_USB_PLL

0.1U_0402_10V7K

VDDIO_AUDIO

C30

C28

20mA

0.1U_0402_10V7K

VDD_1V8_GEN

W5

AVDD_USB

4.7U_0402_6.3V6M

U1Q is not place on grid , need check connection

USB1_VBUS

(3.3V)

130mA

+3VS

V5

USB2_VBUS

T6

T5

USB2_DN

USB2_DP

W4

ACC2_DETECT

CORE_PWR_REQ

BATT_LEARN (27)

COMPASS_DRDY (19)

SC400003Z00

R1432 1

+USB_CLIENT

2

G

2

EN_T30S_USB1

0.1U_0402_10V6K

R42

1M_0402_1%

D18 @

C2673

USB_REXT

1

1K_0402_1%

T30L-P-A3-1.2G_FCBGA728

Q5

BSS138W-7-F_SOT323-3

CAM_I2C_SCL

C35

VDDIO_CAM

CAM_I2C_SCL

CAM_I2C_SDA

CAM_MCLK

GPIO_PBB0

GPIO_PBB3

GPIO_PBB4

GPIO_PBB5

GPIO_PBB6

GPIO_PBB7

GPIO_PCC1

GPIO_PCC2

AG5

AH7

Z

Z

AD5

Z R72

AF6

AD6

AG7

AE5

AE6

AE7

AC6

AG6

Z

Z

Z

Z

Z

Z

2M_CAM_RST# (20)

2M_CAM_PWDN (20)

PU

PU

@ R16

100K_0402_5%

DSI_D2AN

DSI_D2AP

2M_CAM_RST#

2M_CAM_PWDN

@ R25

R15 @

100K_0402_5%

@

2

CAM_MCLK (20)

R27 @

100K_0402_5%

100K_0402_5%

1

1

AA1

AB1

V10 Add

+VDD_1V8_CAM_TEGRA

+AVDD_1V2_DSI_CSI_TEGRA

AB2

AB3

1

DSI_D1AN

DSI_D1AP

2 0_0402_5%

C372

T30L-P-A3-1.2G_FCBGA728

DSI_CLKAN

DSI_CLKAP

RF note

CAM_I2C_SCL (20)

CAM_I2C_SDA (20)

1

C187

2M_CAM_DA1#_R (20)

2M_CAM_DA1_R (20)

AH2

AH1

C34

AD1

AE1

AD9

0.1U_0402_10V7K

CSI_D2BN

CSI_D2BP

4.7U_0402_6.3V6M

CSI_D1BN

CSI_D1BP

2M_CAM_CLK#_R (20)

2M_CAM_CLK_R (20)

(1.8/2.8 ~ 3.3V)

20mA

VDD_1V8_GEN

AG3

AG2

R41

2.2K_0402_1%

U1G

18/22 CAM

1

@

39P 50V J NPO 0402

R40

2.2K_0402_1%

+VDD_1V8_CAM_TEGRA

CSI_CLKBN

CSI_CLKBP

CAM_I2C_SDA

C186

39P 50V J NPO 0402

USB VBUS overvoltage protection

AE2

AE3

CSI_D2AN

CSI_D2AP

+VDD_1V8_CAM_TEGRA

AD3

AD2

10P_0402_25V8K

CSI_D1AN

CSI_D1AP

CSI_CLKAN

CSI_CLKAP

AVDD_DSI_CSI

AC4

AD4

2

2

Y4

USB_REXT

(1.2V)

AB6

C32

0.1U_0402_10V7K

4.7U_0402_6.3V6M

C31

2

G

U1H

7/22 DSI & CSI

56mA

+AVDD_1V2_DSI_CSI_TEGRA

For HOST USB

R39

BZT52-B5V6S_SOD323-2

+AVDD_3V3_USB_TEGRA

VDD_PMU_LDO6

USB_HOST_DN (21)

USB_HOST_DP (21)

V4

ACC3_DETECT

2 0_0402_5% +T30S_USB1

V3

V2

USB3_DN

USB3_DP

0.1A

10MIL

R5 R1423 1

USB3_VBUS

2 0_0402_5%

Q18

AO3413_SOT23-3

+T30S_USB1

T30L-P-A3-1.2G_FCBGA728

Vth = 1.5

HP_DET# (17)

CDC_IRQ# (17)

EN_ES305_OSC (16)

GYRO_INT_R (19)

SPI2_SCK

SPI2_CS0*

SPI2_CS1*

SPI2_CS2*

SPI2_MOSI

SPI2_MISO

AA2

AA3

R44

453_0402_1%

4

DSI_CSI_RUP

AG4

DSI_CSI_RUP

AJ3

DSI_CSI_RDN

AB4

DSI_CSI_RDN

R1424

49.9_0402_1%

R45

49.9_0402_1%

2012/05/20

Deciphered Date

2012/01/09

Title

T30L-USB/SDIO/UART/AUDIO

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

DSI_CSI_TEST_OUT

T30L-P-A3-1.2G_FCBGA728

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

E

Sheet

of

35

Rev

1.0

+VDD_1V8_SYS_TEGRA

BT_RST#

+VDD_1V8_SENSOR

For PMU RTC CLOCK

GPS_RESET#

AVDD_OSC10mA F30

1

DEBUG_UART1_RX (18,7)

BT_PD# (25)

(1.8V)

AVDD_OSC

XTAL_IN

Deep Sleep : OFF

XTAL_OUT

T30

T30_XTAL_IN

T29

T30_XTAL_OUT

H12

PLL_S_PLL_LF

+AVDD_1V1_PLL_TEGRA

H13

CLK_12M_ES305 (16)

J12

J13

AA8

AD7

(1.1V)

AVDD_PLLA_P_C

NC

(1.1V)

AVDD_PLLX

+VDD_1V8_SYS_TEGRA

AVDD_PLLU_D

(1.1V)

AVDD_PLLU_D2

AVDD_PLLE

R53

VDD_1V8_GEN 20mA

M2

M4 Z

N2 Z

N4 Z

AUDIO_UART4_TX (16)

AUDIO_UART4_RX (16)

EN_VDD_GPS (24)

EN_SENSOR_1V8# (23)

+VDD_1V8_BB_TEGRA

K29

K30

CORE_PWR_REQ

CPU_PWR_REQ

(1.8/3.3V)

VDDIO_SYS_1

VDDIO_SYS_2

SYS_CLK_REQ

CLK_32K_IN

CLK_32K_OUT

Deep Sleep : ON

100K_0402_5%

1

R379

WF_RST# (25)

BT_WAKEUP (25)

EN_SENSOR_3V3_2 (23)

R164 2

1100K_0402_5%

RB751V-40_SOD323-2

2

1

D20

+VDD_1V8_BB_TEGRA

0_0402_5%

2 R65

@

0_0402_5%

JTAG_TRST#2 R1561

JTAG_TDI

JTAG_TMS

JTAG_TCK

JTAG_RTCK

JTAG_TDO

T30L-P-A3-1.2G_FCBGA728

(22) HOT_RST#

C45

max current is 350uA

VR1 =17mV

NV_THERM_DN

(16,17,29,31,33,4,7) PWR_I2C_SCL

(16,17,29,31,33,4,7) PWR_I2C_SDA

VDD_1V8_PMU_VRTC

8

7

OWR

JTAG_TDI

R155

HDMI_CEC

JTAG_TMS

R159

TEST_MODE_EN

JTAG_RTCK

R160

JTAG_TCK

2

10K_0402_5%

2

10K_0402_5%

2

10K_0402_5%

1 100K_0402_5%

R161 2

JTAG_TRST#

R162 2

THERM#

ALERT#/ THERM2#

SCLK

SDATA

GND

100K_0402_5%

4

6

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

PD

SC_LOCK# (22)

VOL_UP# (22,4)

VOL_DOWN# (22,4)

EN_CAM_2V8 (20)

BOARD_ID_WP (4)

+VDD_1V8_SYS_TEGRA

WAKEUP_LED (27)

PCB_ID3

EN_CAM_1V8# (23)

UART_SW (18)

@ PAD T10

SHORT_DET (17)

WF_WAKE# (25)

@ PAD T14

1 @

2

R405

0_0402_5%

SD_DET# (21,4)

G_ACC_INT (19)

BT_IRQ# (25)

T27

R29

T28

R23

T22

V24

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST#

JTAG_RTCK

M30

M29

NV_THERM_DN

NV_THERM_DP

@ PAD T4

@ PAD T5

@ PAD T6

@ PAD T7

@ PAD T8

@ PAD T9

N22

AC18

R28 TEST_MODE_EN

T30L-P-A3-1.2G_FCBGA728

1 100K_0402_5%

AP_OVERHEAT# (31)

TEMP_ALERT# (4)

NCT72CMNR2G_DFN8_3x3

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

Thermal

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

T26

M23

V27

M28

N24

N30

T24

T25

R27

M26

R25

M27

N23

V28

M25

V26

PMU_CLK_32K (31)

CLK_32K_OUT (25)

100K_0402_5%

Vcc

D+

D-

1

THERMD_F_N

PWR_I2C_SCL

PWR_I2C_SDA

R60

U4

2

3

THERM_DN

THERM_DP

+VDD_1V8_SYS_TEGRA

+3VS

R58

THERMD_F_P

ACES_87036-1001-CP

@

+3VS_TH

PU

PU

PU

PU

PU

PU

PU

PU

1

1000P_0402_50V7K

R61

C46

100_0402_1%

2

1

2

JTAG_TCK

JTAG_TDI

JTAG_TDO

JTAG_TMS

JTAG_TRST_N

JTAG_RTCK

J30

N26

V25

R26

W26

R30

P27

N29

PAD T2

R62

NV_THERM_DP

1

2

3

4

5

6

7

8

9

10

GND

GND

R22

U27

SYS_CLK_REQ

0_0402_5%

0.1U_0402_10V6K

49.9_0402_1%

R59

100_0402_1%

1

2

ONKEY_R#

For JTAG

R57

1

+3VS

JDBUG1

1

2

3

4

5

6

7

8

9

10

11

12

R163

+VDD_1V8_SYS_TEGRA

CORE_PWR_REQ (31,6)

CPU_PWR_REQ (31)

T23

@ R1560

100K_0402_5%

PMU_INT# (31)

N25

R24

10K_0402_5%

KB_ROW00

KB_ROW01

KB_ROW02

KB_ROW03

KB_ROW04

KB_ROW05

KB_ROW06

KB_ROW07

KB_ROW08

KB_ROW09

KB_ROW10

KB_ROW11

KB_ROW12

KB_ROW13

KB_ROW14

KB_ROW15

ONKEY_R# (22)

R1 Z ON_KEY#

R2 Z

KB_COL00

KB_COL01

KB_COL02

KB_COL03

KB_COL04

KB_COL05

KB_COL06

KB_COL07

M22

A210@

R195

2

1

R77

100K_0402_5%

2

N3 PD

M3 PD

R4 PD

R6 PD

GPIO_PV0

GPIO_PV1

PWR_INT_N

+VDD_1V8_SYS_TEGRA

WAKE_UP_ACIN (27)

PMU_RESET_OUT_1V8# (31)

10K_0402_5%

DAP3_DIN

DAP3_DOUT

DAP3_FS

DAP3_SCLK

DEBUG_UART1_TX (18)

DEBUG_UART1_RX (18,7)

0.1U_0402_10V6K

ULPI_CLK

ULPI_DIR

ULPI_NXT

ULPI_STP

R3 PU

V1 PU

N1 PU

T3 PU

P4 PU

T4 PU

T1 PU

T2 PU

C44

C43

0.1U_0402_10V6K

ULPI_DATA0

ULPI_DATA1

ULPI_DATA2

ULPI_DATA3

ULPI_DATA4

ULPI_DATA5

ULPI_DATA6

ULPI_DATA7

PWR_I2C_SCL (16,17,29,31,33,4,7)

PWR_I2C_SDA (16,17,29,31,33,4,7)

N28

SYS_RESET_N

12/22 BB

R52

Z

Z

U1S

M24

N27

PWR_I2C_SCL

PWR_I2C_SDA

0_0402_5%

(1.8/3.3V)

1.8K_0402_5%

1.8K_0402_5%

R51

AA22

+VDD_1V8_BB_TEGRA

VDDIO_BB

(1.1V)

(1.05V)

W1

(1.1V)

AVDD_PLLM

C41

C40

54mA

VDD_PMU_LDO7

2/22 OSC, PLL & SYS

MPZ1005S300CT_2P

T30L-P-A3-1.2G_FCBGA728

VDD_1V8_GEN 20mA

U1B

L3

BT_PCM_IN (25)

BT_PCM_OUT (25)

BT_PCM_SYNC (25)

BT_PCM_CLK (25)

0

Z

AVDD_OSC

VDD_1V8_GEN

PD

PD

PD

PD

AA29

W28

AA24

AA26

For BT

4.7P_0402_50V8J

C37 1

2

0.1U_0402_10V6K

Z

BT_RST# (25)

Z

Z

GPS_PWRON (24)

Z

GPS_RESET# (24)

Z

Z DEBUG_UART1_RX_R 1@ R149

2

Z

BT_PD#

0_0402_5%

1100K_0402_5%

R372 2

For GPS

BT_UART_TXD (25)

BT_UART_RXD (25)

BT_UART_RTS# (25)

BT_UART_CTS# (25)

T30_XTAL_OUT

AA28

V30

AB30

AB27

AC25

W30

AA27

GEN1_I2C_SCL (19)

GEN1_I2C_SDA (19)

GPS_UART_TXD (24)

GPS_UART_RXD (24)

GPS_UART_RTS# (24)

GPS_UART_CTS# (24)

Y10

12MHZ_7PF_FL1200105

R50

2M_0402_5%

PU

PU

PU

PU

AC27

W27

AB29

W29

Y27

W24

CLK3_OUT

CLK3_REQ

PU

PU

PU

PU

100K_0402_5%

DAP4_DIN

DAP4_DOUT

DAP4_FS

DAP4_SCLK

Z

Z

W25

AB28

AB26

AA25

C39

GPIO_PU0

GPIO_PU1

GPIO_PU2

GPIO_PU3

GPIO_PU4

GPIO_PU5

GPIO_PU6

AB25

V29

4.7U_0402_6.3V6M

UART3_TXD

UART3_RXD

UART3_RTS*

UART3_CTS*

100K_0402_5%

CORE_PWR_REQ

CPU_PWR_REQ

C42

UART2_TXD

UART2_RXD

UART2_RTS*

UART2_CTS*

100K_0402_5%

2.2K_0402_1%

0.1U_0402_10V6K

C38

0.1U_0402_10V6K

GEN1_I2C_SCL

GEN1_I2C_SDA

4.7P_0402_50V8J

C36 1

2

T30_XTAL_IN

@

R49

R1572

(1.8/3.3V)

VDDIO_UART

R48

0.1U_0402_10V6K

AA30

PMU_OSC32KOUT (31)

10K_0402_5%

20mA

VDD_1V8_GEN

R47

2.2K_0402_1%

Open Drain

14/22 UART

100K_0402_5%

R46

U1R

R75

32.768KHZ_12.5P_1TJF125DP1A000D

1

+VDD_1V8_UART_TEGRA

(31) PMU_OSC32KIN

Y1

R56

Title

T30L-UART/OSC/PLL

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

E

Sheet

of

35

Rev

1.0

T30 Core Power

U1A

VDD_1V2_RTC_TEGRA

1/22 CORE POWER

V22

V23

VDD_PMU_LDO4

0.1U_0402_10V6K

For placement question, limint by H=0.5mm

VDD_1V0_GEN

VDD_1V0_CPU_TEGRA

J1

2

@

1

C2599

C2598

C2567

1

C2568

1

C2569

1

C2570

1

C2571

C2572

1 C2573 1 C2574 1 C2575 1 C2576 1 C2577 1 C2578 1 C2579 1 C2580

1U_0402_10V6K

1U_0402_10V6K

1U_0402_10V6K

1U_0402_10V6K

1U_0402_10V6K

VDD_1V0_CPU_TEGRA

1U_0402_10V6K

1U_0402_10V6K

JUMP_43X118

1U_0402_10V6K

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

C25661

4.7U_0402_6.3V6M

C25651

4.7U_0402_6.3V6M

C25641

4.7U_0402_6.3V6M

C25631

0.1U_0402_10V6K

H10

J10

J8

K8

K9

M7

M8

M9

N8

N9

P14

P15

P16

P17

R14

R17

T14

T17

U14

U15

U16

U17

10A@ 1.2375V(max)

(0.9 ~ 1.0V)

VDD_CPU_01

VDD_CPU_02

VDD_CPU_03

VDD_CPU_04

VDD_CPU_05

VDD_CPU_06

VDD_CPU_07

VDD_CPU_08

VDD_CPU_09

VDD_CPU_10

VDD_CPU_11

VDD_CPU_12

VDD_CPU_13

VDD_CPU_14

VDD_CPU_15

VDD_CPU_16

VDD_CPU_17

VDD_CPU_18

VDD_CPU_19

VDD_CPU_20

VDD_CPU_21

VDD_CPU_22

C2562

0.1U_0402_10V6K

For placement question, limint by H=0.5mm

VDD_1V2_CORE_TEGRA

M13

M15

M17

M19

N12

N14

N16

N18

N7

P13

P19

R12

R18

R7

R8

R9

T13

T19

T8

T9

U18

V13

V15

V17

V19

W14

W16

W18

VDD_1V2_CORE_TEGRA

0_0805_5%

1 C2590 1 C2591 1 C2592 1 C2593 1 C2594 1 C2595 1 C2596 1 C2597

C2588

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

C2589

1U_0402_10V6K

C2587

1U_0402_10V6K

C2586

1U_0402_10V6K

C2585

1U_0402_10V6K

C2584

1U_0402_10V6K

C2655

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

1U_0402_10V6K

C2656

1U_0402_10V6K

1U_0402_10V6K

4.7U_0402_6.3V6M

C25831

4.7U_0402_6.3V6M

C25821

4.7U_0402_6.3V6M

C25811

0.1U_0402_10V6K

VDD_CORE_01

VDD_CORE_02

VDD_CORE_03

VDD_CORE_04

VDD_CORE_05

VDD_CORE_06

VDD_CORE_07

VDD_CORE_08

VDD_CORE_09

VDD_CORE_10

VDD_CORE_11

VDD_CORE_12

VDD_CORE_13

VDD_CORE_14

VDD_CORE_15

VDD_CORE_16

VDD_CORE_17

VDD_CORE_18

VDD_CORE_19

VDD_CORE_20

VDD_CORE_21

VDD_CORE_22

VDD_CORE_23

VDD_CORE_24

VDD_CORE_25

VDD_CORE_26

VDD_CORE_27

VDD_CORE_28

VDD_1V2_SOC

R1392

3A@ 1.3V(max)

(1.0 ~ 1.2V)

0.1U_0402_10V6K

@ PAD T22

@ PAD T23

VDD_CPU_SENSE

GND_CPU_SENSE

AB12

VDD_CPU_SENSE_PAIR

AB15

VDD_CPU_SENSE_PAIR

Layout route as Diff. pair ( Z = 90 ohm )

90DIFF_NETCLASS1

VDD_CPU_SENSE

(33)

GND_CPU_SENSE

(33)

90DIFF_NETCLASS1

Layout route as Diff. pair ( Z = 90 ohm )

VVDD_CPU_SENSE

VGND_CORE_SENSE

AB16

VVDD_CPU_SENSE

VVDD_CPU_SENSE_PAIR

90DIFF_NETCLASS1

AA23

VGND_CORE_SENSE

VVDD_CPU_SENSE_PAIR

90DIFF_NETCLASS1

@ PAD T24

@ PAD T25

@ PAD T26

@ PAD T27

VDD_CORE_SENSE

GND_CORE_SENSE

W23

VDD_CORE_SENSE

W22

GND_CORE_SENSE

Layout route as Diff. pair ( Z = 90 ohm )

VDD_CORE_SENSE

(33)

GND_CORE_SENSE

(33)

+VDD_3V3_FUSE_TEGRA

AA4

VPP_KFUSE

R1395

10K_0402_5%

C2600

1

2

VPP_KFUSE

R1396

1K_0402_5%

2

1

VPP_FUSE

(3.3V)

40mA@ 3.3V

AB8

(3.3V)

0.1U_0402_10V6K

VDD_RTC_0001

VDD_RTC_0002

0.1U_0402_10V6K

20mA@ 1.2V

(1.0 ~ 1.2V)

0.1U_0402_10V6K

GND_001

GND_002

GND_003

GND_004

GND_005

GND_006

GND_007

GND_008

GND_009

GND_010

GND_011

GND_012

GND_013

GND_014

GND_015

GND_016

GND_017

GND_018

GND_019

GND_020

GND_021

GND_022

GND_023

GND_024

GND_025

GND_026

GND_027

GND_028

GND_029

GND_030

GND_031

GND_032

GND_033

GND_034

GND_035

GND_036

GND_037

GND_038

GND_039

GND_040

GND_041

GND_042

GND_043

GND_044

GND_045

GND_046

GND_047

GND_048

GND_049

GND_050

GND_051

GND_052

GND_053

GND_054

GND_055

GND_056

GND_057

GND_058

GND_059

GND_060

GND_061

GND_062

GND_063

GND_064

GND_065

GND_066

GND_067

GND_068

GND_069

GND_070

GND_071

GND_072

GND_073

GND_074

GND_075

GND_076

GND_077

GND_078

GND_079

GND_080

GND_081

GND_082

GND_083

GND_084

GND_085

GND_086

GND_087

GND_088

GND_089

GND_090

GND_091

GND_092

GND_093

GND_094

GND_095

GND_096

GND_097

GND_098

GND_099

GND_100

GND_101

GND_102

GND_103

GND_104

GND_105

GND_106

GND_107

GND_108

GND_109

GND_110

GND_111

GND_112

GND_113

GND_114

GND_115

GND_116

GND_117

GND_118

GND_119

GND_120

GND_121

0.1U_0402_10V6K

A2

A29

AC11

AC14

AC17

AC2

AC20

AC23

AC26

AC29

AC5

AC8

AF11

AF14

AF17

AF2

AF20

AF23

AF26

AF29

AF5

AF8

AJ1

AJ11

AJ14

AJ17

AJ2

AJ20

AJ23

AJ26

AJ29

AJ30

AJ5

AJ8

AK2

AK29

B1

B11

B14

B17

B2

B20

B23

B26

B29

B30

B5

B8

E11

E14

E17

E2

E20

E23

E26

E29

E5

E8

H11

H14

H17

H2

H20

H23

H26

H29

H5

H8

L2

L23

L26

L29

L5

L8

M12

M14

M16

M18

N13

N15

N17

N19

P12

P18

P2

P23

P26

P29

P5

P8

R13

R15

R16

R19

T12

T15

T16

T18

U13

U19

U2

U23

U26

U29

U5

U8

V12

V14

V16

V18

W12

W13

W15

W17

W19

Y2

Y23

Y26

Y29

Y5

Y8

T30L-P-A3-1.2G_FCBGA728

Issued Date

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

A

Compal Electronics, Inc.

Compal Secret Data

Security Classification

Title

T30L-Core Power

Size

Document Number

Custom

Date:

Rev

1.0

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

Sheet

H

of

35

T30 PEX Interface

U1T

20/22 PEX

T30 VI Interface

(1.05V)

AB18

AB19

AVDD_PEXA_1

AVDD_PEXA_2

PEX_L0_TXN

PEX_L0_TXP

PEX_L0_RXN

PEX_L0_RXP

AG18

AF18

POR State/ After Wake State/ Wake-Up Events

PU: Pull Up

PD: Pull Down

Z: High Impendance

R: Reset

H: Hold

W: Wake-Up Event

AJ19

AH19

PEX_L1_TXN

PEX_L1_TXP

U1F

(1.05V)

AD22

VDD_PEXA

PEX_L1_RXN

PEX_L1_RXP

AK22

AK21

19/22 VI

(1.2 / 1.8V)

AH30

PEX_L2_TXN

PEX_L2_TXP

(3.3V)

AB21

AF19

AG19

PEX_L2_RXN

PEX_L2_RXP

VDDIO_VI

VI_MCLK

VI_PCLK

AJ18

AH18

AE26

PD/H

AF25

PD/H

AD27

AG30

PD/H

PD/H

AF27

AD30

AH29

AG28

AE27

AE25

AG29

AD29

AE29

AD28

AE30

AE28

PD/H

PD/H

PD/H

PD/H/W

PD/H

PD/H

PD/H

PD/H

PD/H

PD/H

PD/H

PD/H

T30 SPARE Pins

U1V

22/22 NC

VI_HSYNC

VI_VSYNC

AK19

AK18

NC_37

NC_38

NC_39

NC_40

NC_41

NC_42

NC_43

HVDD_PEX

PEX_L3_TXN

PEX_L3_TXP

PEX_L3_RXN

PEX_L3_RXP

VI_D00

VI_D01

VI_D02

VI_D03

VI_D04

VI_D05

VI_D06

VI_D07

VI_D08

VI_D09

VI_D10

VI_D11

AK24

AK25

AJ21

AH21

AB10

AB5

AC19

AC9

C25

E13

H25

(1.05V)

AC22

AVDD_PEXB

PEX_L4_TXN

PEX_L4_TXP

AG21

AF21

T30L-P-A3-1.2G_FCBGA728

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

NC_26

NC_27

NC_28

NC_29

NC_30

NC_31

NC_32

NC_33

NC_34

NC_35

NC_36

PEX_L4_RXN

PEX_L4_RXP

(1.05V)

AE23

PEX_L5_TXN

PEX_L5_TXP

AJ24

AH24

AJ25

AH25

VDD_PEXB

PEX_L5_RXN

PEX_L5_RXP

AG22

AG23

T30 SATA Interface

(1.05V)

AE24

AVDD_PEX_PLL

PEX_CLK1N

PEX_CLK1P

AK28

AK27

AB11

AB14

AB17

AB20

AB22

AB9

AE11

AE14

AE17

AE20

F11

F14

F17

F20

J11

J14

J17

J20

J22

J9

L22

L25

L6

L9

P22

P25

P6

P9

U22

U25

U6

U9

Y22

Y25

Y6

Y9

U1U

PEX_CLK2N

PEX_CLK2P

PEX_CLK3N

PEX_CLK3P

AB24

AB23

75mA@ 1.05V

18mA@ 1.05V

10mA@ 3.3V

AH27

AJ27

120mA@ 1.05V

PEX_REFCLKN

PEX_REFCLKP

AC15

VDD_SATA

AF15

HVDD_SATA

AC16

AVDD_SATA_PLL

AG17

AVDD_SATA

(1.05V)

VDD_SATA

(1.05V)

HVDD_SATA

(3.3V)

AVDD_SATA_PLL

SATA_L0_TXN

SATA_L0_TXP

(1.05V)

SATA_L0_RXN

SATA_L0_RXP

SATA_TESTCLKN

SATA_TESTCLKP

VDDIO_PEX_CTL

PEX_L0_CLKREQ*

PEX_L0_PRSNT*

PEX_L0_RST*

PEX_L1_CLKREQ*

PEX_L1_PRSNT*

PEX_L1_RST*

PEX_L2_CLKREQ*

PEX_L2_PRSNT*

PEX_L2_RST*

PEX_WAKE*

PEX_TESTCLKN

PEX_TESTCLKP

PEX_TERMP

AD16

AE16

AE19

AD19

AJ22

AH22

(3.3V)

AF24

T30L-P-A3-1.2G_FCBGA728

21/22 NC

AVDD_SATA

SATA_TERMP

AG24

AD25

AG26

AD26

AD24

AG27

AE21

AD21

AD18

T30L-P-A3-1.2G_FCBGA728

AC21

AE22

AG25

AF22

AJ28

AH28

AG20

T30L-P-A3-1.2G_FCBGA728

Title

T30L-PEX/SATA/VI

Size

C

Date:

5

Document Number

Rev

1.0

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

1

Sheet

of

35

Title

<Title>

Size

C

Date:

5

Document Number

V0JET(A210)-LA8981P

Rev

1.0

Wednesday, June 13, 2012

1

Sheet

10

of

35

DDR3/DDR3L (page 1/2): 4pcs, 2Gbx4 memory chips: RANK 0: LOW 16 BITS

Note: Layout use the 82 ball biggest packages and co-Layout 78 ball

A210 use 78 ball H5TC2G83CFR-H9A

700mA@ 1.35V

VDD_1V35_DDR3_MEM

VDD_1V35_DDR3_MEM

1

C2605

2

VDD_1V35_DDR3_MEM

4.7U_0402_6.3V6M

B10

C2

E3

E10

B3

B9

C10

D2

D10

1

C2611

2

1

C2612

C2613

2

K4

L8

L4

K3

L9

L3

M9

M3

N9

M4

H8

M8

K8

N4

N8

DDR_BA0

DDR_BA1

DDR_BA2

J3

K9

J4

F2

F10

H2

H10

N3

DDR_RESET#

G2

DDR_ODT0

1 R1399 2

243_0402_1%

ZQ

NC_A1

NC_A11

NC_N1

NC_N11

NC_A4

NC_J8

G10

F8

G8

DDR_CKE0

DDR_CLKP

DDR_CLKN

A2

A9

B2

D9

F3

F9

J2

J10

L2

L10

N2

N10

ODT

M4_ZQ

VDD_0V675_DDR3_VREF

BA[0]

BA[1]

BA[2]

CKE

CK

CK*

C2618

VSS[0]

VSS[1]

VSS[2]

VSS[3]

VSS[4]

VSS[5]

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

NC_F2

NC_F10

NC_H2

NC_H10

RESET*

C2607

2

C2608

2

1

C2609

2

1

C2610

2

VDD_1V35_DDR3_MEM

B10

C2

E3

E10

B3

B9

C10

D2

D10

1

C2614

2

C2615

2

C2616

2

A2

A9

B2

D9

F3

F9

J2

J10

L2

L10

N2

N10

ODT

ZQ

NC_A1

NC_A11

NC_N1

NC_N11

NC_A4

NC_J8

X76@

VSSQ[0]

VSSQ[1]

VSSQ[2]

VSSQ[3]

VSSQ[4]

1

C2606

VDD_0V675_DDR3_VREF

VREFDQ

VREFCA

E2

J9

H5TC4G83MFR-PBA _FBGA82

VDD_1V35_DDR3_MEM

1

C2619

2

1

C2620

2

R1400

1K_0402_1%

VDD_0V675_DDR3_VREF

0.1U_0402_10V6K

C2617

2

VDDQ[0]

VDDQ[1]

VDDQ[2]

VDDQ[3]

0.1U_0402_10V6K

0.1U_0402_10V6K

H5TC2G83BFR-PBA_FBGA82

DDR_A15

H9

A1

A11

N1

N11

A4

J8

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]/AP

A[11]

A[12]/BC*

A[13]

A[14]

VREFDQ

VREFCA

E2

J9

0.1U_0402_10V6K

X76@

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

0.1U_0402_10V6K

RESET*

1

C2604

A3

A10

D8

G3

G9

K2

K10

M2

M10

0.1U_0402_10V6K

DDR_A15

H9

A1

A11

N1

N11

A4

J8

NC_F2

NC_F10

NC_H2

NC_H10

VDD[0]

VDD[1]

VDD[2]

VDD[3]

VDD[4]

VDD[5]

VDD[6]

VDD[7]

VDD[8]

0.1U_0402_10V6K

(12,5) DDR_A15

M1_ZQ

VSS[0]

VSS[1]

VSS[2]

VSS[3]

VSS[4]

VSS[5]

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

1

C2603

RAS*

CAS*

WE*

CS*

0.1U_0402_10V6K

1R1398

2

243_0402_1%

CKE

CK

CK*

F4

G4

H4

H3

0.1U_0402_10V6K

G2

(12,5) DDR_ODT0

BA[0]

BA[1]

BA[2]

1

C2602

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_CS0#

0.1U_0402_10V6K

N3

(12,5) DDR_RESET#

VSSQ[0]

VSSQ[1]

VSSQ[2]

VSSQ[3]

VSSQ[4]

0.1U_0402_10V6K

F2

F10

H2

H10

VDDQ[0]

VDDQ[1]

VDDQ[2]

VDDQ[3]

1

C2601

0.1U_0402_10V6K

G10

F8

G8

(12,5) DDR_CKE0

(12,5) DDR_CLKP

(12,5) DDR_CLKN

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]/AP

A[11]

A[12]/BC*

A[13]

A[14]

A3

A10

D8

G3

G9

K2

K10

M2

M10

0.1U_0402_10V6K

J3

K9

J4

(12,5) DDR_BA0

(12,5) DDR_BA1

(12,5) DDR_BA2

K4

L8

L4

K3

L9

L3

M9

M3

N9

M4

H8

M8

K8

N4

N8

VDD[0]

VDD[1]

VDD[2]

VDD[3]

VDD[4]

VDD[5]

VDD[6]

VDD[7]

VDD[8]

0.1U_0402_10V6K

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

U151A

RAS*

CAS*

WE*

CS*

0.1U_0402_10V6K

F4

G4

H4

H3

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_CS0#

DDR_A[14..0]

0.1U_0402_10V6K

(12,5)

(12,5)

(12,5)

(12,5)

(12,5)

4.7U_0402_6.3V6M

U150A

NB DDR3 design

R1401

1K_0402_1%

(12,5) DDR_DQ[31..0]

U150B

DDR_DQ4

DDR_DQ7

DDR_DQ0

DDR_DQ5

DDR_DQ2

DDR_DQ3

DDR_DQ1

DDR_DQ6

(5) DDR_DM0

(5) DDR_DQS0P

(5) DDR_DQS0N

4

B4

C8

C3

C9

E4

E9

D3

E8

A8

B8

C4

D4

X76@

U151B

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

NF/TDQS*

DM/TDQS

DQS

DQS*

DDR_DQ23

DDR_DQ18

DDR_DQ17

DDR_DQ22

DDR_DQ20

DDR_DQ19

DDR_DQ16

DDR_DQ21

(5) DDR_DM2

(5) DDR_DQS2P

(5) DDR_DQS2N

H5TC4G83MFR-PBA_FBGA82

B4

C8

C3

C9

E4

E9

D3

E8

A8

B8

C4

D4

X76@

U150

X76-S@ K4B2G0846D-HYH9

U150

X76-H@ H5TC2G83CFR-H9A

SA00005KI10

U151

X76-S@ K4B2G0846D-HYH9

U151

X76-H@H5TC2G83CFR-H9A

SA00005KI10

X76-H@H5TC2G83CFR-H9A

X76-S@ K4B2G0846D-HYH9

U153

U153

X76-H@H5TC2G83CFR-H9A

X76-S@ K4B2G0846D-HYH9

X76-E@ EDJ2108EDBG-DJ-F

X76-E@ EDJ2108EDBG-DJ-F

SA000055E10

U159

SA000055910

SA00005KI10

X76-E@ EDJ2108EDBG-DJ-F

SA000055E10

U160

SA000055910

SA00005KI10

HH5TC4G83MFR-PBA_FBGA82

SA000055E10

U155

SA000055910

U152

U152

U156

SA000055910

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

NF/TDQS*

DM/TDQS

DQS

DQS*

X76-E@ EDJ2108EDBG-DJ-F

SA000055E10

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

C

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

DDR3_part1

Document Number

Rev

1.0

V0JET(A210)-LA8981P

Date:

Wednesday, June 13, 2012

Sheet

11

of

35

DDR3/DDR3L(page 2/2): 4pcs, 2Gbx4 memory chips: RANK 0: HIGH 16 BITS

VDD_1V35_DDR3_MEM

VDD_1V35_DDR3_MEM

C2632

2

C2633

2

G2

DDR_ODT0

1R1403

2

243_0402_1%

M2_ZQ

VDD_0V675_DDR3_VREF

VREFDQ

VREFCA

DDR_A15

BA[0]

BA[1]

BA[2]

CKE

CK

CK*

RESET*

C2627

2

C2628

2

1

C2629

2

1

C2630

2

1

C2634

2

C2635

2

C2636

2

ODT

ZQ

NC_A1

NC_A11

NC_N1

NC_N11

NC_A4

NC_J8

X76@

A2

A9

B2

D9

F3

F9

J2

J10

L2

L10

N2

N10

VSS[0]

VSS[1]

VSS[2]

VSS[3]

VSS[4]

VSS[5]

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

NC_F2

NC_F10

NC_H2

NC_H10

VDD_0V675_DDR3_VREF

E2

J9

VREFDQ

VREFCA

H5TC4G83MFR-PBA_FBGA82

C2638

2

1

C2639

2

0.1U_0402_10V6K

C2637

2

H9

A1

A11

N1

N11

A4

J8

B3

B9

C10

D2

D10

VSSQ[0]

VSSQ[1]

VSSQ[2]

VSSQ[3]

VSSQ[4]

1

C2626

VDD_1V35_DDR3_MEM

B10

C2

E3

E10

VDDQ[0]

VDDQ[1]

VDDQ[2]

VDDQ[3]

0.1U_0402_10V6K

0.1U_0402_10V6K

H5TC4G83MFR-PBA _FBGA82

E2

J9

0.1U_0402_10V6K

X76@

N3

DDR_RESET#

ODT

ZQ

NC_A1

NC_A11

NC_N1

NC_N11

NC_A4

NC_J8

G10

F8

G8

F2

F10

H2

H10

M3_ZQ

H9

A1

A11

N1

N11

A4

DDR_A15 J8

J3

K9

J4

DDR_BA0

DDR_BA1

DDR_BA2

DDR_CKE0

DDR_CLKP

DDR_CLKN

A2

A9

B2

D9

F3

F9

J2

J10

L2

L10

N2

N10

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]/AP

A[11]

A[12]/BC*

A[13]

A[14]

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

4.7U_0402_6.3V6M

K4

L8

L4

K3

L9

L3

M9

M3

N9

M4

H8

M8

K8

N4

N8

A3

A10

D8

G3

G9

K2

K10

M2

M10

VDD[0]

VDD[1]

VDD[2]

VDD[3]

VDD[4]

VDD[5]

VDD[6]

VDD[7]

VDD[8]

0.1U_0402_10V6K

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

C2625

2

RAS*

CAS*

WE*

CS*

0.1U_0402_10V6K

RESET*

B3

B9

C10

D2

D10

1

C2631

F4

G4

H4

H3

0.1U_0402_10V6K

(11,5) DDR_A15

NC_F2

NC_F10

NC_H2

NC_H10

VDD_1V35_DDR3_MEM

B10

C2

E3

E10

C2624

2

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_CS0#

0.1U_0402_10V6K

1R1402

2

243_0402_1%

VSS[0]

VSS[1]

VSS[2]

VSS[3]

VSS[4]

VSS[5]

VSS[6]

VSS[7]

VSS[8]

VSS[9]

VSS[10]

VSS[11]

C2623

2

0.1U_0402_10V6K

G2

(11,5) DDR_ODT0

CKE

CK

CK*

C2622

2

0.1U_0402_10V6K

(11,5) DDR_RESET#

BA[0]

BA[1]

BA[2]

0.1U_0402_10V6K

N3

VSSQ[0]

VSSQ[1]

VSSQ[2]

VSSQ[3]

VSSQ[4]

0.1U_0402_10V6K

F2

F10

H2

H10

VDDQ[0]

VDDQ[1]

VDDQ[2]

VDDQ[3]

1

C2621

0.1U_0402_10V6K

G10

F8

G8

(11,5) DDR_CKE0

(11,5) DDR_CLKP

(11,5) DDR_CLKN

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]/AP

A[11]

A[12]/BC*

A[13]

A[14]

A3

A10

D8

G3

G9

K2

K10

M2

M10

0.1U_0402_10V6K

J3

K9

J4

(11,5) DDR_BA0

(11,5) DDR_BA1

(11,5) DDR_BA2

K4

L8

L4

K3

L9

L3

M9

M3

N9

M4

H8

M8

K8

N4

N8

VDD[0]

VDD[1]

VDD[2]

VDD[3]

VDD[4]

VDD[5]

VDD[6]

VDD[7]

VDD[8]

0.1U_0402_10V6K

DDR_A0

DDR_A1

DDR_A2

DDR_A3

DDR_A4

DDR_A5

DDR_A6

DDR_A7

DDR_A8

DDR_A9

DDR_A10

DDR_A11

DDR_A12

DDR_A13

DDR_A14

U153A

RAS*

CAS*

WE*

CS*

0.1U_0402_10V6K

F4

G4

H4

H3

DDR_RAS#

DDR_CAS#

DDR_WE#

DDR_CS0#

DDR_A[14..0]

4.7U_0402_6.3V6M

U152A

(11,5)

(11,5)

(11,5)

(11,5)

(11,5)

1

C2640

2

U153B

(11,5) DDR_DQ[31..0]

(5) DDR_DM1

(5) DDR_DQS1P

(5) DDR_DQS1N

DDR_DQ29

DDR_DQ25

DDR_DQ26

DDR_DQ27

DDR_DQ28

DDR_DQ24

DDR_DQ30

DDR_DQ31

U152B

DDR_DQ11

DDR_DQ10

DDR_DQ12

DDR_DQ13

DDR_DQ9

DDR_DQ14

DDR_DQ8

DDR_DQ15

B4

C8

C3

C9

E4

E9

D3

E8

A8

B8

C4

D4

X76@

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

NF/TDQS*

DM/TDQS

DQS

DQS*

(5) DDR_DM3

(5) DDR_DQS3P

(5) DDR_DQS3N

B4

C8

C3

C9

E4

E9

D3

E8

A8

B8

C4

D4

X76@

DQ[0]

DQ[1]

DQ[2]

DQ[3]

DQ[4]

DQ[5]

DQ[6]

DQ[7]

NF/TDQS*

DM/TDQS

DQS

DQS*

H5TC4G83MFR-PBA_FBGA82

H5TC4G83MFR-PBA_FBGA82

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

Title

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

Size

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

C

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

Date:

DDR3_part2

Document Number

Rev

1.0

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

Sheet

12

of

35

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

Title

EC(Reserved)

Size

C

Date:

Document Number

V0JET(A210)-LA8981P

Wednesday, June 13, 2012

1

Sheet

13

of

35

Rev

1.0

+VDD_2V85_EMMC

+3VS

K6

W4

Y4

AA3

AA5

0.1U_0402_10V6K

C118

10U_0402_6.3V6M

10U_0402_6.3V6M

10U_0402_6.3V6M

1

2

C120

0.1U_0402_10V6K

C117

C385

2.2U_0402_6.3V6M

DAT0

DAT1

DAT2

DAT3

DAT4

DAT5

DAT6

DAT7

VDDi

NC

NC

NC

RSTN

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VOUT

GND

NC

2

R439 G9001-300TO1U TSOT-23 5P LDO

0_0402_5%

@

EMMC_CLK_R

2

33_0402_5%

C365

1U_0402_10V4Z

D

SA00005II00

EMMC_CMD (4)

H3

H4

H5

J2

J3

J4

J5

J6

EMMC_DAT0_R

EMMC_DAT1_R

EMMC_DAT2_R

EMMC_DAT3_R

EMMC_DAT4_R

EMMC_DAT5_R

EMMC_DAT6_R

EMMC_DAT7_R

K2

C123 1

U1

U2

U3

U5

U6

U7

U10

U12

U13

U14

V1

V2

V3

V12

V13

V14

W1

W2

W3

W7

W8

W9

W10

W11

W12

W13

W14

Y1

Y3

Y6

Y7

Y8

Y9

Y10

Y11

Y12

Y13

Y14

AA1

AA2

AA7

AA8

AA9

AA10

AA11

AA12

AA13

AA14

AE1

AE14

AG2

AG13

AH4

AH6

AH9

AH11

0.1U_0402_10V6K

R104

R105

R106

R107

R108

R109

R110

R111

1

1

1

1

1

1

1

1

2 0_0402_5%

2

C122

12P_0402_50V4Z

2

2

2

2

2

2

2

2

33_0402_5%

33_0402_5%

33_0402_5%

33_0402_5%

33_0402_5%

33_0402_5%

33_0402_5%

33_0402_5%

EMMC_CLK (4)

1

R103 1

EMMC_DA0

EMMC_DA1

EMMC_DA2

EMMC_DA3

EMMC_DA4

EMMC_DA5

EMMC_DA6

EMMC_DA7

(4)

(4)

(4)

(4)

(4)

(4)

(4)

(4)

R114

EMMC_CMD_R

MMC_RST#

MMC_RST#

R112 1

2 0_0402_5%

EMMC_RST# (4)

U13

SS8GB@ KLM8G2FE3B-B001

SA00005KM10

U13

SD8GB@ SDIN5D1-8G-L

SA00005MV10

U13

SS16GB@ KLMAG2GE4A-A001

SA00005KG10

U13

SD16GB@ SDIN5C1-16G-L

SA00004XA30

1

2

3

4

5

6

7

8

9

10

11

12

SDIN5F1-64G_TFBGA169

Issued Date

Compal Electronics, Inc.

Compal Secret Data

Security Classification

2012/05/20

Deciphered Date

2012/01/09

THIS SHEET OF ENGINEERING DRAWING IS THE PROPRIETARY PROPERTY OF COMPAL ELECTRONICS, INC. AND CONTAINS CONFIDENTIAL

AND TRADE SECRET INFORMATION. THIS SHEET MAY NOT BE TRANSFERED FROM THE CUSTODY OF THE COMPETENT DIVISION OF R&D

DEPARTMENT EXCEPT AS AUTHORIZED BY COMPAL ELECTRONICS, INC. NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS

MAY BE USED BY OR DISCLOSED TO ANY THIRD PARTY WITHOUT PRIOR WRITTEN CONSENT OF COMPAL ELECTRONICS, INC.

5

0_0402_5%

EN

VSS

VSS

VSS

VSS

U8

R10

P5

M7

VSSQ

VSSQ

VSSQ

VSSQ

VSSQ

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

AA6

AA4

Y5

Y2

K4

W6

1

R102

EMMC_CMD_R

W5

close U13

(5) EN_3V3_EMMC

(4) EN_3V3_EMMC1

R113

CLK

2

0_0402_5%

R440 1

R437

2

+VDDIO_1V8_EMMC

CMD

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

VIN

C121

0.1U_0402_10V6K

VCCQ

VCCQ

VCCQ

VCCQ

VCCQ

M6

N5

T10

U9

@ C150

4.7K_0402_5%

13

14

15

16

17

18

19

20

21

22

23

24

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC