Professional Documents

Culture Documents

Lic-MayJun 2007 - IV Sem

Lic-MayJun 2007 - IV Sem

Uploaded by

Mahi Prince0 ratings0% found this document useful (0 votes)

12 views4 pageslic may

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentlic may

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

0 ratings0% found this document useful (0 votes)

12 views4 pagesLic-MayJun 2007 - IV Sem

Lic-MayJun 2007 - IV Sem

Uploaded by

Mahi Princelic may

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

Download as pdf

You are on page 1of 4

C3181

B.EJB.Tech. DEGREE EXAMINATION, MAY/JUNE 2007.

Fourth Semester

(Regulation 2004)

Eleetronies and Communication Engineering

EC 1254— LINEAR INTEGRATED CIRCUITS

(Common to B.E. (Part~Time) Third Semester Regulation 2008

‘Time : Three hours Maxim: marks

4,

St

S$

6 5

<

OO

Answer ALL questions, 2

PART A (19v9 = 9A marke) ©

Calculate the output current I of the current source 5e) ig. 1. Assume hee

of transistor is very high and Ves = 0.6V.

XS

F

Draw the cit ofa mage soures and-wsla fhe spcesion ara

output current.

‘Two voltages +Viand +\bardJavailable. Using two operational amplifiers draw

a circuit to compute (BSS Ve.

Galeulate the earetth e circuit shown in Fig.2

>

rae

5. Explain how a frequency doubler can be realized using analog multiplier.

6. A PLL with a free running frequency of 1 KHz is connected to a variable

frequeney oscillator. The frequency of oscillator is gradually increased_and

when its frequency was 850 Hz the PLL got locked. The frequency of

was decreased and it went out of lock for the oscillator frequency

Caleulate the lock range and the capture range of the PLL.

7. The input to a sampling gate is a sine wave. Plot its ouput gl ‘without a

hold capacitor. ©

8. Sestethe reason for keeping the ntagraling ie Aen ere

digital converter equal to that of mains supply vee)

16 V. Fora lad erent of 1 Ampere, altel)

and output voltage is

the power dissipated in the

10, Draw the internal diagram of

@)

@ :

CS its equivalent circuit and derive an expression for its gain. (16)

2 csist

12. (a) (i) In the cireuit given in Fig. 3, show that the input resistance

= S

Gi) Calculate the current through Ry Lp amr Fig, @)

1K

WS

& or

iw the circuit diagram of a second order Butterworth active

)

lowpass filter and derive an expression for its transfer function. (10)

ti) Design the above mentioned filter for a cutoff frequency of 1 KHz

GBP econ at4

3 C3181

)

u. @

®

16. @)

®

(Draw the bloc diagram ofa PLL and derive its transfer

(10)

Gi) Draw the cireut of FM demodulator using PLL. ©

2

6) Draw the circuit of a ROR ladder ype digital 4x Sabo converter

and explain. ®)

Gi) Draw the circuit of a four bit R-2R D/A. er with feedback

Feoistance af SH for the Op-Amp. Caleulgbe Weutput voltage for a

digital input of 0100 if the reference volt a3. @)

- &

(0 Rxplain the working of fash or converter, (8)

(ii) How many comparators gxe/feat, for a 4- bit flash ADC? For an

Input sigtal in the range-Gf Oo 10 V. What are the roforence

waltages needed? Shote how Woy can be generated using # 10 V

yeference and several isons ®

(Draw the inter gram of voltage regulator IC LM 723

ra exain ®

(i Design a vol ator using LM. 728 with short circuit current

protection aXe lowing spesfcaions. Ve = 12 V, Ik = 500 mA,

Tee = 600, ®

2 SW C2

Draw it of an 10 tuned amplifer and explain how you will

reahgalh amplifier with AGC and a video apie using this building

“sp (16)

4 C3181

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5823)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Final Report of WimaxDocument59 pagesFinal Report of WimaxMahi Prince0% (1)

- Cummins: Business Objects AssetsDocument5 pagesCummins: Business Objects AssetsMahi PrinceNo ratings yet

- BO Report Design SpecificationDocument8 pagesBO Report Design SpecificationMahi Prince100% (1)

- An Empirical Performance Evaluation of Relational Keyword Search SystemsDocument4 pagesAn Empirical Performance Evaluation of Relational Keyword Search SystemsMahi PrinceNo ratings yet

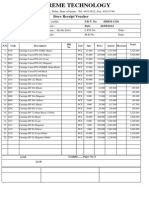

- Store Receipt Voucher: P.O Box: 80587, Doha, State of Qatar - Tel: 44513822, Fax: 44513749Document2 pagesStore Receipt Voucher: P.O Box: 80587, Doha, State of Qatar - Tel: 44513822, Fax: 44513749Mahi PrinceNo ratings yet

- Easy Way To Remember All The Main SAP Tables Used For Any DevelopmentDocument3 pagesEasy Way To Remember All The Main SAP Tables Used For Any DevelopmentMahi PrinceNo ratings yet