Professional Documents

Culture Documents

Digital Design: An Embedded Systems Approach Using Verilog: Sequential Basics

Digital Design: An Embedded Systems Approach Using Verilog: Sequential Basics

Uploaded by

avinash_yuvarajCopyright:

Available Formats

You might also like

- TTTTT Eeee AsDocument20 pagesTTTTT Eeee AsEric GongNo ratings yet

- VHDL Coding For Fpgas Unit 7: Digital System DesignDocument25 pagesVHDL Coding For Fpgas Unit 7: Digital System DesignSrinivas CherukuNo ratings yet

- Dw02 Mult 6 StageDocument4 pagesDw02 Mult 6 StageroseootyNo ratings yet

- KPMG - Implement-Grc-Technology-The-Right-WayDocument4 pagesKPMG - Implement-Grc-Technology-The-Right-WaykeizersNo ratings yet

- Sequential Circuit Design Using PLDsDocument8 pagesSequential Circuit Design Using PLDsJacob ChakoNo ratings yet

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003No ratings yet

- Fpga ApplicationsDocument6 pagesFpga ApplicationsBHEEMANPALLY SRIMANNARAYANA R2527004No ratings yet

- 6 111 l4 Seqntl BlocksDocument24 pages6 111 l4 Seqntl BlocksysakeunNo ratings yet

- L4: Sequential Building Blocks (Flip - Flops, Latches and Registers)Document24 pagesL4: Sequential Building Blocks (Flip - Flops, Latches and Registers)ggk87No ratings yet

- EXP4 - Report TaskDocument5 pagesEXP4 - Report TaskShamsul HaqueNo ratings yet

- Flip-Flops & Latches: Digital ElectronicsDocument20 pagesFlip-Flops & Latches: Digital ElectronicsGowtham PalanirajanNo ratings yet

- 412n - Unit IV - Modeling of Sequential CircuitsDocument19 pages412n - Unit IV - Modeling of Sequential CircuitsMarc Neil ApasNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersDocument28 pagesFALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersAakashNo ratings yet

- Digital ClockDocument11 pagesDigital ClockAmiin Gadari100% (4)

- Chapter - 7 (Compatibility Mode)Document32 pagesChapter - 7 (Compatibility Mode)Imran HayderNo ratings yet

- 6 RegistersDocument24 pages6 RegistersPiyooshTripathiNo ratings yet

- MOSIS Counter Report Spring 2008Document60 pagesMOSIS Counter Report Spring 2008atom_2334No ratings yet

- Decade CounterDocument3 pagesDecade CounterManohar thota100% (1)

- Experiment 10: Aim:-Verilog Implementation of Clock Divider Software UsedDocument6 pagesExperiment 10: Aim:-Verilog Implementation of Clock Divider Software UsedudayNo ratings yet

- Flip-Flops and Latches (MyHDL)Document6 pagesFlip-Flops and Latches (MyHDL)VIJAYPUTRANo ratings yet

- CS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariDocument82 pagesCS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariElizabeth AliazNo ratings yet

- Counters 1716982768Document16 pagesCounters 1716982768z7njp6msh7No ratings yet

- Fundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Document29 pagesFundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedNo ratings yet

- Assignment-10: DFF CodeDocument8 pagesAssignment-10: DFF CodeNarendra Babu GunnamNo ratings yet

- ELE-4613 Programmable Devices Learning Outcome: 3 ProjectDocument6 pagesELE-4613 Programmable Devices Learning Outcome: 3 ProjectMukul TanwarNo ratings yet

- Lab1 Scan Chain Insertion and Atpg Using Design Compiler and TetramaxDocument47 pagesLab1 Scan Chain Insertion and Atpg Using Design Compiler and TetramaxLakshmi PrasadNo ratings yet

- 21-CP-6 (Report14) DLDDocument17 pages21-CP-6 (Report14) DLDAlmaas ChaudryNo ratings yet

- Lab 6Document4 pagesLab 6marwa abdelrazikNo ratings yet

- Flip FlopsDocument29 pagesFlip FlopsShweta RoyNo ratings yet

- LN 09 Sequential Logic ModulesDocument51 pagesLN 09 Sequential Logic ModulesSrilekha VallabhaneniNo ratings yet

- Prof. Anantha Chandrakasan and Prof. Don TroxelDocument10 pagesProf. Anantha Chandrakasan and Prof. Don TroxelCristian CastroNo ratings yet

- 341 2 13 2002Document23 pages341 2 13 2002Carlos Ch GoNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogGaurav UpadhyayNo ratings yet

- General Synchronous Digital Systems and Synchronous CountersDocument27 pagesGeneral Synchronous Digital Systems and Synchronous CountersLiyanage GihanNo ratings yet

- CSE 307: Digital TechniqueDocument33 pagesCSE 307: Digital TechniquemmlabjpNo ratings yet

- Synthesis of Reversible Sequential ElementsDocument32 pagesSynthesis of Reversible Sequential ElementskamarajvlsiNo ratings yet

- ELE 4613 - ProjectDocument6 pagesELE 4613 - ProjectmukulNo ratings yet

- Topic 5: Servo Chip DesignDocument50 pagesTopic 5: Servo Chip Designboarddk1No ratings yet

- VHDL SequentialDocument5 pagesVHDL SequentialSAKETSHOURAVNo ratings yet

- Cb2re TBDocument2 pagesCb2re TBOrrette BakerNo ratings yet

- Chapter 9: Sequential Logic Modules: Prof. Soo-Ik ChaeDocument51 pagesChapter 9: Sequential Logic Modules: Prof. Soo-Ik ChaeeceaitsrajampetNo ratings yet

- Synopsys Tools For Verilog Simulation: Run GUI by Using Vcs - RIDocument19 pagesSynopsys Tools For Verilog Simulation: Run GUI by Using Vcs - RIApoorva BhattNo ratings yet

- Document 1Document4 pagesDocument 1Puneeth Kumar ReddyNo ratings yet

- EC381 Lecture16 PDFDocument24 pagesEC381 Lecture16 PDFCorazon corazonNo ratings yet

- Simulation SeminarDocument45 pagesSimulation SeminarKapasi TejasNo ratings yet

- Verilog Sequential ModelingDocument8 pagesVerilog Sequential ModelingR INI BHANDARINo ratings yet

- Flip FlopsDocument25 pagesFlip FlopsNagul MeeraNo ratings yet

- Hardware Slides 08Document30 pagesHardware Slides 08Taqi ShahNo ratings yet

- Chapter 6 Registers Counters1-1Document29 pagesChapter 6 Registers Counters1-1mary_nailynNo ratings yet

- Chap 08 Marlin 2002Document37 pagesChap 08 Marlin 2002Audrey Patrick KallaNo ratings yet

- Aim:-Implementation of Up Counter, Down Counter and Up-Down CounterDocument5 pagesAim:-Implementation of Up Counter, Down Counter and Up-Down CounterJaspreet KaurNo ratings yet

- HDL Programming AssignmentDocument7 pagesHDL Programming Assignmentpinaka paniNo ratings yet

- VHDL SynthesisDocument16 pagesVHDL SynthesisNickos PopoviciNo ratings yet

- Dic File - 7 SemDocument22 pagesDic File - 7 SemShalini SharmaNo ratings yet

- CB4CEDocument2 pagesCB4CE劉成No ratings yet

- Ee 241 Digital Circuits Final Exam Solution ManualDocument10 pagesEe 241 Digital Circuits Final Exam Solution ManualkdrdNo ratings yet

- CH 17Document52 pagesCH 17Juju salehNo ratings yet

- ASIC Va VHDL Toan TapDocument76 pagesASIC Va VHDL Toan TapCường VũNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- MathsDocument2 pagesMathsavinash_yuvarajNo ratings yet

- Course SyllabusDocument10 pagesCourse Syllabusavinash_yuvarajNo ratings yet

- 2021-2022 Final Individual TTDocument75 pages2021-2022 Final Individual TTavinash_yuvarajNo ratings yet

- Assignment 2 III BDocument3 pagesAssignment 2 III Bavinash_yuvarajNo ratings yet

- 19ELE35 QUIZ 3C Quiz 2Document1 page19ELE35 QUIZ 3C Quiz 2avinash_yuvarajNo ratings yet

- Ece Second Year 2021-2022Document77 pagesEce Second Year 2021-2022avinash_yuvarajNo ratings yet

- Assignment 2 III BDocument3 pagesAssignment 2 III Bavinash_yuvarajNo ratings yet

- Lecture A 2.Fsm ReviewDocument14 pagesLecture A 2.Fsm Reviewavinash_yuvarajNo ratings yet

- Assignment I - III BDocument3 pagesAssignment I - III Bavinash_yuvarajNo ratings yet

- Q.No Solution Marks 1Document4 pagesQ.No Solution Marks 1avinash_yuvarajNo ratings yet

- Digital Signal Processing LabDocument36 pagesDigital Signal Processing Labavinash_yuvarajNo ratings yet

- EECS 373: Design of Microprocessor-Based SystemsDocument29 pagesEECS 373: Design of Microprocessor-Based Systemsavinash_yuvarajNo ratings yet

- Org 00H MOV C, P1.7 ANL C,/P1.6 MOV P1.5, C MOV C, P1.7 CPL C ANL C, P1.6 MOV P1.4, C ORL C, P1.5 MOV P1.3, C MOV C, P1.7 ANL C, P1.6 MOV P1.2, C ENDDocument1 pageOrg 00H MOV C, P1.7 ANL C,/P1.6 MOV P1.5, C MOV C, P1.7 CPL C ANL C, P1.6 MOV P1.4, C ORL C, P1.5 MOV P1.3, C MOV C, P1.7 ANL C, P1.6 MOV P1.2, C ENDavinash_yuvarajNo ratings yet

- Datasheet de OsciloscopioDocument9 pagesDatasheet de OsciloscopioDanny Josue Love DlNo ratings yet

- ARM Twin Trip v4 Owners ManualDocument19 pagesARM Twin Trip v4 Owners ManualMichaelKubaNo ratings yet

- Salesforce CRM Implementation ChecklistDocument11 pagesSalesforce CRM Implementation Checklist5gzqvjtn6qNo ratings yet

- FR-XX-XXXX PrinterEventFile 0Document2 pagesFR-XX-XXXX PrinterEventFile 0Jp IshiNo ratings yet

- Electricity EngineeringDocument120 pagesElectricity Engineeringttai76649No ratings yet

- KANIKADocument16 pagesKANIKAKartik mondalNo ratings yet

- Introduction To Power Electronics: Robert W. Erickson University of Colorado, Boulder Fall 2015Document38 pagesIntroduction To Power Electronics: Robert W. Erickson University of Colorado, Boulder Fall 2015Engenheiro TeslandoNo ratings yet

- GSA-Region Spotlight Latin America April 2024Document8 pagesGSA-Region Spotlight Latin America April 2024Rodrigo BarretoNo ratings yet

- Role of Cyber Law in Cyber Security in IndiaDocument4 pagesRole of Cyber Law in Cyber Security in IndiaHJ ManviNo ratings yet

- MIL Q2 Module 8Document27 pagesMIL Q2 Module 8MICHAEL JIMENO100% (1)

- dm00369109 Getting Started With The ST Bluenrg Mesh Android Application StmicroelectronicsDocument23 pagesdm00369109 Getting Started With The ST Bluenrg Mesh Android Application StmicroelectronicsWallace FerreiraNo ratings yet

- Here Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyDocument1 pageHere Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyHernan BenitesNo ratings yet

- LM386 Audio Amplifier Circuits With PCBDocument20 pagesLM386 Audio Amplifier Circuits With PCBMuhammad YousafNo ratings yet

- EM FW and TFTP FAQDocument10 pagesEM FW and TFTP FAQDustin DavenportNo ratings yet

- ReadmeDocument7 pagesReadmeAshwin ReddyNo ratings yet

- Nog Mpls FRR PDFDocument232 pagesNog Mpls FRR PDFMoïse GuilavoguiNo ratings yet

- Construction Estimate &value EngineeringDocument30 pagesConstruction Estimate &value EngineeringCharles Nacorda100% (1)

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- Kautilya ResumeDocument2 pagesKautilya ResumebhanuyadavNo ratings yet

- Amazon Vs AlibabaDocument3 pagesAmazon Vs AlibabaPaulina CarmonaNo ratings yet

- Change Order FormDocument5 pagesChange Order FormM Kemal PasheryNo ratings yet

- MX-321Document6 pagesMX-321Akun Backup100% (1)

- Network 3D Blu-Ray Disc™ / DVD Player: Owner'S ManualDocument62 pagesNetwork 3D Blu-Ray Disc™ / DVD Player: Owner'S ManualIfeanyi OparaekeNo ratings yet

- AE 27 Lesson 2Document37 pagesAE 27 Lesson 2MARC BENNETH BERIÑANo ratings yet

- CSA Lab Report 1Document5 pagesCSA Lab Report 1Sadat AminNo ratings yet

- Winding Machine Manual in EnglishDocument8 pagesWinding Machine Manual in EnglishViviane CostaNo ratings yet

- Final .Mat Energy Collector Using Piezoelectric Sensor For Public ChargingDocument68 pagesFinal .Mat Energy Collector Using Piezoelectric Sensor For Public ChargingArneitou Queroyla CagungunNo ratings yet

- EDGARDocument4 pagesEDGAREdgar Joseph Quitevis SinampagaNo ratings yet

- 4X4 Keypad Interfacing With ATmega32 (LCD Display)Document6 pages4X4 Keypad Interfacing With ATmega32 (LCD Display)Emin KültürelNo ratings yet

Digital Design: An Embedded Systems Approach Using Verilog: Sequential Basics

Digital Design: An Embedded Systems Approach Using Verilog: Sequential Basics

Uploaded by

avinash_yuvarajOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Design: An Embedded Systems Approach Using Verilog: Sequential Basics

Digital Design: An Embedded Systems Approach Using Verilog: Sequential Basics

Uploaded by

avinash_yuvarajCopyright:

Available Formats

Digital Design:

An Embedded Systems

Approach Using Verilog

Chapter 4

Sequential Basics

Portions of this work are from the book, Digital Design: An

Embedded Systems Approach Using Verilog, by Peter J. Ashenden,

published by Morgan Kaufmann Publishers, Copyright 2007 Elsevier

Inc. All rights reserved.

Verilog

Sequential Basics

Sequential circuits

Outputs depend on current inputs and

previous inputs

Store state: an abstraction of the

history of inputs

Usually governed by a periodic

clock signal

Digital Design Chapter 4 Sequential Basics

Verilog

D-Flipflops

1-bit storage element

We will treat it as a basic component

clk

clk

D

Q

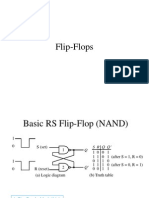

Other kinds of flipflops

SR (set/reset), JK, T (toggle)

Digital Design Chapter 4 Sequential Basics

Verilog

Registers

Store a multi-bit encoded value

One D-flipflop per bit

Stores a new value on

each clock cycle

d(0)

q(0)

q(1)

q(n)

clk

d(1)

wire [n:0] d;

reg [n:0] q;

...

D

clk

event list

always @(posedge clk)

q <= d;

d(n)

clk

D

clk

nonblockin

g

asignment

Digital Design Chapter 4 Sequential Basics

clk

Verilog

Pipelines Using Registers

Total delay = Delay1 + Delay2 + Delay3

Interval between outputs > Total delay

combinational

circuit 1

d_in

d_in

combinational

circuit 1

D

clk

combinational

circuit 2

combinational

circuit 2

combinational

circuit 3

D

clk

combinational

circuit 3

d_out

clk

clk

Clock period = max(Delay1, Delay2, Delay3)

Total delay = 3 clock period

Interval between outputs = 1 clock period

Digital Design Chapter 4 Sequential Basics

Verilog

Pipeline Example

Compute the average of corresponding

numbers in three input streams

New values arrive on each clock edge

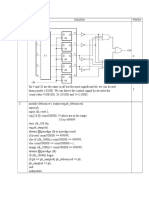

module average_pipeline ( output reg signed [5:-8] avg,

input

signed [5:-8] a, b, c,

input

clk );

wire signed [5:-8] a_plus_b, sum, sum_div_3;

reg signed [5:-8] saved_a_plus_b, saved_c, saved_sum;

...

Digital Design Chapter 4 Sequential Basics

Verilog

Pipeline Example

...

assign a_plus_b = a + b;

always @(posedge clk) begin // Pipeline register 1

saved_a_plus_b <= a_plus_b;

saved_c

<= c;

end

assign sum = saved_a_plus_b + saved_c;

always @(posedge clk)

saved_sum <= sum;

// Pipeline register 2

assign sum_div_3 = saved_sum * 14'b00000001010101;

always @(posedge clk)

avg <= sum_div_3;

// Pipeline register 3

endmodule

Digital Design Chapter 4 Sequential Basics

Verilog

D-Flipflop with Enable

Storage controlled by a clock-enable

stores only when CE = 1 on a rising

edge of the clock

clk

D

Q

CE

clk

CE

D

Q

CE is a synchronous control input

Digital Design Chapter 4 Sequential Basics

Verilog

Register with Enable

One flipflop per bit

clk and CE wired in common

wire [n:0] d;

wire

ce;

reg [n:0] q;

...

always @(posedge clk)

if (ce) q <= d;

Digital Design Chapter 4 Sequential Basics

Verilog

Register with Synchronous

Reset

Reset input forces stored value to 0

reset input must be stable around

rising edge of clk

1

clk

D

Q

CE

reset

clk

reset

CE

D

Q

always @(posedge clk)

if

(reset) q <= 0;

else if (ce)

q <= d;

Digital Design Chapter 4 Sequential Basics

10

Verilog

Register with Asynchronous

Reset

Reset input forces stored value to 0

reset can become 1 at any time, and

effect is immediate

reset should return to 0 synchronously

1

D

Q

CE

reset

clk

clk

reset

CE

D

Q

Digital Design Chapter 4 Sequential Basics

11

Verilog

Asynch Reset in Verilog

always @(posedge clk or posedge reset)

if

(reset) q <= 0;

else if (ce)

q <= d;

reset is an asynchronous control input

here

include it in the event list so that the

process responds to changes immediately

Digital Design Chapter 4 Sequential Basics

12

Verilog

Example: Accumulator

Sum a sequence of signed numbers

A new number arrives when data_en = 1

Clear sum to 0 on synch reset

module accumulator

( output reg signed [7:-12] data_out,

input

signed [3:-12] data_in,

input

data_en, clk, reset );

wire signed [7:-12] new_sum;

assign new_sum = data_out + data_in;

always @(posedge clk)

if

(reset)

data_out <= 20'b0;

else if (data_en) data_out <= new_sum;

endmodule

Digital Design Chapter 4 Sequential Basics

13

Verilog

Flipflop and Register

Variations

module flip_flop_n ( output reg Q,

output

Q_n,

input

pre_n, clr_n, D,

input

clk_n, CE );

pre

D

Q

CE

clk Q

clr

always @( negedge clk_n or

negedge pre_n or negedge clr_n ) begin

if ( !pre_n && !clr_n)

$display("Illegal inputs: pre_n and clr_n both 0");

if

(!pre_n) Q <= 1'b1;

else if (!clr_n) Q <= 1'b0;

else if (CE)

Q <= D;

end

assign Q_n = ~Q;

endmodule

Digital Design Chapter 4 Sequential Basics

14

Verilog

Shift Registers

Performs shift operation on stored data

Arithmetic scaling

Serial transfer

D(n1)

of data

0

1

D_in

D

Q

load_en

CE

clk

Q(n1)

Q(n2)

Q(0)

CE

clk

D(n2)

D

CE

clk

D(0)

load_en

CE

clk

D

CE

clk

Digital Design Chapter 4 Sequential Basics

15

Verilog

Example: Sequential

Multiplier

1616 multiply over 16 clock cycles,

using one adder

y(15...0)

y_load_en

y_ce

Shift register for multiplier bits

Shift register for lsbs of accumulated product

16-bit

shift reg

D_in

D

Q

load_en

CE

clk

16-bit

adder

x

c16

y

16-bit reg

x(15...0)

x_ce

15...0

31...16

15

P(31...15)

reset

CE

clk

CE

clk

P_reset

P_ce

clk

c0

16

17-bit reg

15-bit

shift reg

D_in Q

P(14...0)

CE

clk

Digital Design Chapter 4 Sequential Basics

16

Verilog

Latches

Level-sensitive storage

Data transmitted while enable is '1'

transparent latch

Data stored while enable is '0'

LE

D

LE

D

Q

Digital Design Chapter 4 Sequential Basics

17

Verilog

Feedback Latches

Feedback in gate circuits produces

latching behavior

Example: reset/set (RS) latch

+V

Q

R

Current RTL synthesis tools dont accept

Verilog models with unclocked feedback

Digital Design Chapter 4 Sequential Basics

18

Verilog

Latches in Verilog

Latching behavior is usually an error!

always @*

if (~sel) begin

z1 <= a1; z2 <= b1;

end

else begin

z1 <= a2; z3 <= b2;

end

Oops!

Should be

z2 <= ...

Values must be stored

for z2 while sel = 1

for z3 while sel = 0

Digital Design Chapter 4 Sequential Basics

19

Verilog

Counters

Stores an unsigned integer value

Used to count occurrences of

increments or decrements the value

events

repetitions of a processing step

Used as timers

count elapsed time intervals by

incrementing periodically

Digital Design Chapter 4 Sequential Basics

20

Verilog

Free-Running Counter

+1

clk

clk

Increments every rising edge of clk

up to 2n1, then wraps back to 0

i.e., counts modulo 2n

This counter is synchronous

all outputs governed by clock edge

Digital Design Chapter 4 Sequential Basics

21

Verilog

Example: Periodic Control

Signal

Count modulo 16 clock cycles

Control output = 1 every 8th and 12th cycle

decode count values 0111 and 1011

0

clk

1

+1

2

clk

D

ctrl

Q

clk

3

clk

clk

Digital Design Chapter 4 Sequential Basics

22

Verilog

Example: Periodic Control

Signal

module decoded_counter ( output ctrl,

input clk );

reg [3:0] count_value;

always @(posedge clk)

count_value <= count_value + 1;

assign ctrl = count_value == 4'b0111 ||

count_value == 4'b1011;

endmodule

Digital Design Chapter 4 Sequential Basics

23

Verilog

Count Enable and Reset

Use a register with control inputs

+1

D

CE

reset

clk

CE

reset

clk

Increments when CE = 1 on rising

clock edge

Reset: synch or asynch

Digital Design Chapter 4 Sequential Basics

24

Verilog

Terminal Count

Status signal indicating final count value

counter

Q0

Q1

TC

clk Qn

TC is 1 for one cycle in every 2n

cycles

frequency = clock frequency / 2n

Called a clock divider

Digital Design Chapter 4 Sequential Basics

25

Verilog

Divider Example

Alarm clock beep: 500Hz from 1MHz clock

10-bit

counter

Q

clk

count

tone2

TC

tone

CE

clk

clk

clk

count

0

1023

0

1023

1023

tone2

tone

Digital Design Chapter 4 Sequential Basics

26

Verilog

Divide by k

Decode k1 as terminal count and

reset counter register

Counter increments modulo k

Example: decade counter

Terminal count = 9

counter

clk

clk

Q0

Q1

Q2

reset Q3

Q0

Q1

Q2

Q3

Digital Design Chapter 4 Sequential Basics

27

Verilog

Decade Counter in Verilog

module decade_counter ( output reg [3:0] q,

input

clk );

always @(posedge clk)

q <= q == 9 ? 0 : q + 1;

endmodule

Digital Design Chapter 4 Sequential Basics

28

Verilog

Down Counter with Load

Load a starting value, then decrement

Terminal count = 0

Useful for interval timer

0

1

D

load

clk

clk

=0?

TC

Digital Design Chapter 4 Sequential Basics

29

Verilog

Loadable Counter in

Verilog

module interval_timer_rtl ( output

tc,

input [9:0] data,

input

load, clk );

reg [9:0] count_value;

always @(posedge clk)

if (load) count_value <= data;

else

count_value <= count_value - 1;

assign tc = count_value == 0;

endmodule

Digital Design Chapter 4 Sequential Basics

30

Verilog

Reloading Counter in

Verilog

module interval_timer_repetitive ( output

tc,

input [9:0] data,

input

load, clk );

reg [9:0] load_value, count_value;

always @(posedge clk)

if (load) begin

load_value <= data;

count_value <= data;

end

else if (count_value == 0)

count_value <= load_value;

else

count_value <= count_value - 1;

assign tc = count_value == 0;

endmodule

Digital Design Chapter 4 Sequential Basics

31

Verilog

Ripple Counter

clk

clk Q

D

Q1

clk Q

D

when previous bit changes from 1 to 0

clk Q

D

Q0

Each bit toggles between 0 and 1

clk

Q0

Q2

Q0

Q1

Q1

clk Q

D

Qn

Q2

Q2

Digital Design Chapter 4 Sequential Basics

32

Verilog

Ripple or Synch Counter?

Ripple counter is ok if

length is short

clock period long relative to flipflop

delay

transient wrong values can be tolerated

area must be minimal

E.g., alarm clock

Otherwise use a synchronous

counter

Digital Design Chapter 4 Sequential Basics

33

Verilog

Datapaths and Control

Digital systems perform sequences

of operations on encoded data

Datapath

Combinational circuits for operations

Registers for storing intermediate results

Control section: control sequencing

Generates control signals

Selecting operations to perform

Enabling registers at the right times

Uses status signals from datapath

Digital Design Chapter 4 Sequential Basics

34

Verilog

Example: Complex

Multiplier

Cartesian form, fixed-point

operands: 4 pre-, 12 post-binary-point bits

result: 8 pre-, 24 post-binary-point bits

Subject to tight area constraints

a ar jai

b br jbi

p ab pr jpi (ar br ai bi ) j (ar bi ai br )

4 multiplies, 1 add, 1 subtract

Perform sequentially using 1

multiplier, 1 adder/subtracter

Digital Design Chapter 4 Sequential Basics

35

Verilog

Complex Multiplier

Datapath

a_r

a_i

a_sel

b_r

b_i

b_sel

pp1_ce

pp2_ce

CE

p_r

p_i

CE

clk

clk

0

1

D

CE

clk

D

CE

clk

sub

p_r_ce

p_i_ce

clk

Digital Design Chapter 4 Sequential Basics

36

Verilog

Complex Multiplier in

Verilog

module multiplier

( output reg signed [7:-24] p_r, p_i,

input

signed [3:-12] a_r, a_i, b_r, b_i,

input

clk, reset, input_rdy );

reg a_sel, b_sel, pp1_ce, pp2_ce, sub, p_r_ce, p_i_ce;

wire signed [3:-12] a_operand, b_operand;

wire signed [7:-24] pp, sum

reg signed [7:-24] pp1, pp2;

...

Digital Design Chapter 4 Sequential Basics

37

Verilog

Complex Multiplier in

Verilog

assign a_operand = ~a_sel ? a_r : a_i;

assign b_operand = ~b_sel ? b_r : b_i;

assign pp = {{4{a_operand[3]}}, a_operand, 12'b0} *

{{4{b_operand[3]}}, b_operand, 12'b0};

always @(posedge clk) // Partial product 1 register

if (pp1_ce) pp1 <= pp;

always @(posedge clk) // Partial product 2 register

if (pp2_ce) pp2 <= pp;

assign sum = ~sub ? pp1 + pp2 : pp1 - pp2;

always @(posedge clk) // Product real-part register

if (p_r_ce) p_r <= sum;

always @(posedge clk) // Product imaginary-part register

if (p_i_ce) p_i <= sum;

...

endmodule

Digital Design Chapter 4 Sequential Basics

38

Verilog

Multiplier Control

Sequence

Avoid resource conflict

First attempt

1.

2.

3.

4.

5.

6.

a_r * b_r pp1_reg

a_i * b_i pp2_reg

pp1 pp2 p_r_reg

a_r * b_i pp1_reg

a_i * b_r pp2_reg

pp1 + pp2 p_i_reg

Takes 6 clock cycles

Digital Design Chapter 4 Sequential Basics

39

Verilog

Multiplier Control

Sequence

Merge steps where no resource conflict

Revised attempt

1.

2.

3.

4.

5.

a_r * b_r pp1_reg

a_i * b_i pp2_reg

pp1 pp2 p_r_reg

a_r * b_i pp1_reg

a_i * b_r pp2_reg

pp1 + pp2 p_i_reg

Takes 5 clock cycles

Digital Design Chapter 4 Sequential Basics

40

Verilog

Multiplier Control Signals

Step

a_sel

b_sel

pp1_c

e

pp2_c

e

sub

p_r_ce p_i_ce

Digital Design Chapter 4 Sequential Basics

41

Verilog

Finite-State Machines

Used the implement control sequencing

Based on mathematical automaton theory

A FSM is defined by

set of inputs:

set of outputs:

set of states: S

initial state: s0 S

transition function: : S S

output function: : S or : S

Digital Design Chapter 4 Sequential Basics

42

Verilog

FSM in Hardware

D

reset

clk

inputs

reset

current_state

next

state

logic

clk

output

logic

outputs

Mealy

FSM only

Mealy FSM: : S

Moore FSM: : S

Digital Design Chapter 4 Sequential Basics

43

Verilog

FSM Example: Multiplier

Control

One state per step

Separate idle state?

Use step 1 as idle state

Wait for input_rdy = 1

Then proceed to steps 1, 2, ...

But this wastes a cycle!

Repeat step 1 if input_rdy 1

Proceed to step 2 otherwise

Output function

Defined by table on slide 43

Moore or Mealy?

Transition function

current

_state

input_

rdy

next_

state

step1

step1

step1

step2

step2

step3

step3

step4

step4

step5

step5

step1

Digital Design Chapter 4 Sequential Basics

44

Verilog

State Encoding

Encoded in binary

Encoded value used in circuits for

transition and output function

encoding affects circuit complexity

Optimal encoding is hard to find

N states: use at least log2N bits

CAD tools can do this well

One-hot works well in FPGAs

Often use 000...0 for idle state

reset state register to idle

Digital Design Chapter 4 Sequential Basics

45

Verilog

FSMs in Verilog

Use parameters for state values

Synthesis tool can choose an

alternative encoding

parameter [2:0] step1 = 3'b000, step2 = 3'b001,

step3 = 3'b010, step4 = 3'b011,

step5 = 3'b100;

reg [2:0] current_state, next_state ;

...

Digital Design Chapter 4 Sequential Basics

46

Verilog

Multiplier Control in Verilog

always @(posedge clk or posedge reset) // State register

if (reset) current_state <= step1;

else

current_state <= next_state;

always @* // Next-state logic

case (current_state)

step1: if (!input_rdy) next_state

else

next_state

step2:

next_state

step3:

next_state

step4:

next_state

step5:

next_state

endcase

=

=

=

=

=

=

step1;

step2;

step3;

step4;

step5;

step1;

Digital Design Chapter 4 Sequential Basics

47

Verilog

Multiplier Control in Verilog

always @* begin // Output_logic

a_sel = 1'b0; b_sel = 1'b0; pp1_ce = 1'b0; pp2_ce = 1'b0;

sub = 1'b0;

p_r_ce = 1'b0; p_i_ce = 1'b0;

case (current_state)

step1: begin

pp1_ce = 1'b1;

end

step2: begin

a_sel = 1'b1; b_sel = 1'b1; pp2_ce = 1'b1;

end

step3: begin

b_sel = 1'b1; pp1_ce = 1'b1;

sub = 1'b1;

p_r_ce = 1'b1;

end

step4: begin

a_sel = 1'b1; pp2_ce = 1'b1;

end

step5: begin

p_i_ce = 1'b1;

end

endcase

end

Digital Design Chapter 4 Sequential Basics

48

Verilog

State Transition Diagrams

Bubbles to represent states

Arcs to represent transitions

0, 0

Example

S = {s1, s2, s3}

Inputs (a1, a2):

= {(0,0), (0,1), (1,0),

(1,1)}

defined by diagram

0, 1

1, 0

s1

s2

1, 1

0, 0

1, 1

s3

Digital Design Chapter 4 Sequential Basics

0, 1

1, 0

49

Verilog

State Transition Diagrams

Annotate diagram

to define output

function

Annotate states for

Moore-style outputs

Annotate arcs for

Mealy-style outputs

Example

x1, x2: Moore-style

y1, y2, y3: Mealy-style

0, 1 / 0, 1, 1

0, 0 / 0, 0, 0

1, 0 / 1, 0, 0

s1

s2

1, 0

0, 0

1, 1 / 1, 1, 1

0, 0 / 0, 0, 0

/ 0, 1, 1

s3

0, 1 / 0, 1, 1

0, 1

1, 1 / 1, 1, 1

1, 0 / 1, 0, 0

Digital Design Chapter 4 Sequential Basics

50

Verilog

Multiplier Control Diagram

Input: input_rdy

Outputs

a_sel, b_sel, pp1_ce, pp2_ce, sub, p_r_ce, p_i_ce

step1

0, 0, 1, 0, , 0, 0

step5

, , 0, 0, 0, 0, 1

step2

1, 1, 0, 1, , 0, 0

step4

1, 0, 0, 1, , 0, 0

step3

0, 1, 1, 0, 1, 1, 0

Digital Design Chapter 4 Sequential Basics

51

Verilog

Bubble Diagrams or

Verilog?

Many CAD tools provide editors for

bubble diagrams

Diagrams are visually appealing

Automatically generate Verilog for

simulation and synthesis

but can become unwieldy for complex

FSMs

Your choice...

or your manager's!

Digital Design Chapter 4 Sequential Basics

52

Verilog

Register Transfer Level

RTL a level of abstraction

data stored in registers

transferred via circuits that operate

on data

outputs

inputs

control section

Digital Design Chapter 4 Sequential Basics

53

Verilog

Clocked Synchronous

Timing

Registers driven by a common clock

Combinational circuits operate during

clock cycles (between rising clock edges)

tc

tco

Q1

tpd

D2

tsu

clk

tco

Q1

tpd

tco + tpd + tsu < tc

tsu

D2

Digital Design Chapter 4 Sequential Basics

54

Verilog

Control Path Timing

tco

tsu

tpd-s

tco + tpd-s + tpd-o + tpd-c + tsu < tc

tpd-c

tco + tpd-s + tpd-ns + tsu < tc

tpd-o

tpd-ns

tsu

Ignore tpd-s for a Moore FSM

Digital Design Chapter 4 Sequential Basics

55

Verilog

Timing Constraints

Inequalities must hold for all paths

If tco and tsu the same for all paths

Critical path

Combinational delays make the difference

The combinational path between registers

with the longest delay

Determines minimum clock period for the

entire system

Focus on it to improve performance

Reducing delay may make another path

critical

Digital Design Chapter 4 Sequential Basics

56

Verilog

Interpretation of

Constraints

1. Clock period depends on delays

System can operate at any frequency

up to a maximum

OK for systems where high

performance is not the main

requirement

2. Delays must fit within a target clock

period

Optimize critical paths to reduce delays

if necessary

May require revising RTL organization

Digital Design Chapter 4 Sequential Basics

57

Verilog

Clock Skew

clk1

Q1

D2

Q1

clk2

th

D2

Need to ensure clock edges arrive

at all registers at the same time

Use CAD tools to insert clock buffers

and route clock signal paths

Digital Design Chapter 4 Sequential Basics

58

Verilog

Off-Chip Connections

Delays going off-chip and inter-chip

Input and output pad delays, wire delays

Same timing rules apply

Use input and output registers to avoid

adding external delay to critical path

Q1

D2

Digital Design Chapter 4 Sequential Basics

59

Verilog

Asynchronous Inputs

External inputs can change at any time

Might violate setup/hold time constraints

Can induce metastable state in a flipflop

Unbounded time to

recover

1

k 2t

e

MTBF

k1 f f f 2

May violate setup/hold

k 2 0

Digital Design Chapter 4 Sequential Basics

time of subsequent

60

Verilog

Synchronizers

asynch_in

D

clk

synch_in

clk

clk

If input changes outside setup/hold window

If input changes during setup/hold window

Change is simply delayed by one cycle

First flipflop has a whole cycle to resolve

metastability

See data sheets for metastability parameters

Digital Design Chapter 4 Sequential Basics

61

Verilog

Switch Inputs and

Debouncing

Switches and push-buttons suffer from

contact bounce

Takes up to 10ms to settle

Need to debounce to avoid false triggering

+V

Requires two

inputs and two

R

resistors

Must use a breakS

Q

before-make

double-throw

Digital Design Chapter 4 Sequential Basics

62

switch

Verilog

Switch Inputs and

Debouncing

Alternative

Use a single-throw switch

Sample input at intervals longer than bounce time

Look for two successive samples with the same

value

+V

Assumption

Extra circuitry inside the

chip is cheaper than extra

components and

connections outside

Digital Design Chapter 4 Sequential Basics

63

Verilog

Debouncing in Verilog

module debouncer ( output reg pb_debounced,

input pb,

input clk, reset );

reg [18:0] count500000; // values are in the range 0 to 499999

wire

clk_100Hz;

reg

pb_sampled;

always @(posedge clk or posedge reset)

if

(reset)

count500000 <= 499999;

else if (clk_100Hz) count500000 <= 499999;

else

count500000 <= count500000 - 1;

assign clk_100Hz = count500000 == 0;

always @(posedge clk)

if (clk_100Hz) begin

if (pb == pb_sampled) pb_debounced <= pb;

pb_sampled <= pb;

end

endmodule

Digital Design Chapter 4 Sequential Basics

64

Verilog

Verifying Sequential

Circuits

Verification Testbench

Apply

Test Cases

Design Under

Verification

(DUV)

Checker

DUV may take multiple and varying

number of cycles to produce output

Checker needs to

synchronize with test generator

ensure DUV outputs occur when expected

ensure DUV outputs are correct

ensure no spurious outputs occur

Digital Design Chapter 4 Sequential Basics

65

Verilog

Example: Multiplier

Testbench

`timescale 1ns/1ns

module multiplier_testbench;

parameter t_c = 50;

reg

reg

wire signed [3:-12]

wire signed [7:-24]

clk, reset;

input_rdy;

a_r, a_i, b_r, b_i;

p_r, p_i;

real real_a_r, real_a_i, real_b_r, real_b_i,

real_p_r, real_p_i, err_p_r, err_p_i;

task apply_test ( input real a_r_test, a_i_test,

b_r_test, b_i_test );

begin

real_a_r = a_r_test; real_a_i = a_i_test;

real_b_r = b_r_test; real_b_i = b_i_test;

input_rdy = 1'b1;

@(negedge clk) input_rdy = 1'b0;

repeat (5) @(negedge clk);

end

endtask

Digital Design Chapter 4 Sequential Basics

66

Verilog

Example: Multiplier

Testbench

multiplier duv ( .clk(clk), .reset(reset),

.input_rdy(input_rdy),

.a_r(a_r), .a_i(a_i),

.b_r(b_r), .b_i(b_i),

.p_r(p_r), .p_i(p_i) );

always begin // Clock generator

#(t_c/2) clk = 1'b1;

#(t_c/2) clk = 1'b0;

end

initial begin // Reset generator

reset <= 1'b1;

#(2*t_c) reset = 1'b0;

end

Digital Design Chapter 4 Sequential Basics

67

Verilog

Example: Multiplier

Testbench

initial begin // Apply test cases

@(negedge reset)

@(negedge clk)

apply_test(0.0, 0.0, 1.0, 2.0);

apply_test(1.0, 1.0, 1.0, 1.0);

// further test cases ...

$finish;

end

assign

assign

assign

assign

a_r

a_i

b_r

b_i

=

=

=

=

$rtoi(real_a_r

$rtoi(real_a_i

$rtoi(real_b_r

$rtoi(real_b_i

*

*

*

*

2**12);

2**12);

2**12);

2**12);

Digital Design Chapter 4 Sequential Basics

68

Verilog

Example: Multiplier

Testbench

always @(posedge clk) // Check outputs

if (input_rdy) begin

real_p_r = real_a_r * real_b_r - real_a_i * real_b_i;

real_p_i = real_a_r * real_b_i + real_a_i * real_b_r;

repeat (5) @(negedge clk);

err_p_r = $itor(p_r)/2**(-24) - real_p_r;

err_p_i = $itor(p_i)/2**(-24) - real_p_i;

if (!( -(2.0**(-12)) < err_p_r && err_p_r < 2.0**(-12) &&

-(2.0**(-12)) < err_p_i && err_p_i < 2.0**(-12) ))

$display("Result precision requirement not met");

end

endmodule

Digital Design Chapter 4 Sequential Basics

69

Verilog

Asynchronous Timing

Clocked synchronous timing requires

Hard to achieve in complex multi-GHz

systems

Globally asynch, local synch (GALS) systems

global clock distribution with minimal skew

path delay between registers < clock period

Divide the systems into local clock domains

Inter-domain signals treated as asynch inputs

Simplifies clock managements and constraints

Delays inter-domain communication

Delay-insensitive asynchronous systems

no clock signals

Digital Design Chapter 4 Sequential Basics

70

Verilog

Other Clock-Related Issues

Inter-chip clocking

In multi-PCB systems

Distributing high-speed clocks on PCBs is hard

Often use slower off-chip clock, with on-chip

clock a multiple of off-chip clock

Synchronize on-chip with phase-locked loop (PLL)

treat off-PCB signals as asynch inputs

Low power design

Continuous clocking wastes power

Clock gating: turn off clock to idle subsystems

Digital Design Chapter 4 Sequential Basics

71

Verilog

Summary

Registers for storing data

Latches: level-sensitive

synchronous and asynchronous

control

clock enable, reset, preset

usually unintentional in Verilog

Counters

free-running dividers, terminal count,

reset, load, up/down

Digital Design Chapter 4 Sequential Basics

72

Verilog

Summary

RTL organization of digital systems

Finite-State Machine (FSM)

states, inputs, transition/output functions

Moore and Mealy FSMs

bubble diagrams

Clocked synch timing and constraints

datapath and control section

critical path and optimization

Asynch inputs, switch debouncing

Verification of sequential systems

Digital Design Chapter 4 Sequential Basics

73

You might also like

- TTTTT Eeee AsDocument20 pagesTTTTT Eeee AsEric GongNo ratings yet

- VHDL Coding For Fpgas Unit 7: Digital System DesignDocument25 pagesVHDL Coding For Fpgas Unit 7: Digital System DesignSrinivas CherukuNo ratings yet

- Dw02 Mult 6 StageDocument4 pagesDw02 Mult 6 StageroseootyNo ratings yet

- KPMG - Implement-Grc-Technology-The-Right-WayDocument4 pagesKPMG - Implement-Grc-Technology-The-Right-WaykeizersNo ratings yet

- Sequential Circuit Design Using PLDsDocument8 pagesSequential Circuit Design Using PLDsJacob ChakoNo ratings yet

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003No ratings yet

- Fpga ApplicationsDocument6 pagesFpga ApplicationsBHEEMANPALLY SRIMANNARAYANA R2527004No ratings yet

- 6 111 l4 Seqntl BlocksDocument24 pages6 111 l4 Seqntl BlocksysakeunNo ratings yet

- L4: Sequential Building Blocks (Flip - Flops, Latches and Registers)Document24 pagesL4: Sequential Building Blocks (Flip - Flops, Latches and Registers)ggk87No ratings yet

- EXP4 - Report TaskDocument5 pagesEXP4 - Report TaskShamsul HaqueNo ratings yet

- Flip-Flops & Latches: Digital ElectronicsDocument20 pagesFlip-Flops & Latches: Digital ElectronicsGowtham PalanirajanNo ratings yet

- 412n - Unit IV - Modeling of Sequential CircuitsDocument19 pages412n - Unit IV - Modeling of Sequential CircuitsMarc Neil ApasNo ratings yet

- FALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersDocument28 pagesFALLSEM2022-23 BECE102L TH VL2022230102875 Reference Material I 17-09-2022 Shift Registers CountersAakashNo ratings yet

- Digital ClockDocument11 pagesDigital ClockAmiin Gadari100% (4)

- Chapter - 7 (Compatibility Mode)Document32 pagesChapter - 7 (Compatibility Mode)Imran HayderNo ratings yet

- 6 RegistersDocument24 pages6 RegistersPiyooshTripathiNo ratings yet

- MOSIS Counter Report Spring 2008Document60 pagesMOSIS Counter Report Spring 2008atom_2334No ratings yet

- Decade CounterDocument3 pagesDecade CounterManohar thota100% (1)

- Experiment 10: Aim:-Verilog Implementation of Clock Divider Software UsedDocument6 pagesExperiment 10: Aim:-Verilog Implementation of Clock Divider Software UsedudayNo ratings yet

- Flip-Flops and Latches (MyHDL)Document6 pagesFlip-Flops and Latches (MyHDL)VIJAYPUTRANo ratings yet

- CS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariDocument82 pagesCS 211: Computer Architecture: Instructor: Prof. Bhagi NarahariElizabeth AliazNo ratings yet

- Counters 1716982768Document16 pagesCounters 1716982768z7njp6msh7No ratings yet

- Fundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Document29 pagesFundamentals of Digital IC Design: Haibo Wang ECE Department Southern Illinois University Carbondale, IL 62901Huzur AhmedNo ratings yet

- Assignment-10: DFF CodeDocument8 pagesAssignment-10: DFF CodeNarendra Babu GunnamNo ratings yet

- ELE-4613 Programmable Devices Learning Outcome: 3 ProjectDocument6 pagesELE-4613 Programmable Devices Learning Outcome: 3 ProjectMukul TanwarNo ratings yet

- Lab1 Scan Chain Insertion and Atpg Using Design Compiler and TetramaxDocument47 pagesLab1 Scan Chain Insertion and Atpg Using Design Compiler and TetramaxLakshmi PrasadNo ratings yet

- 21-CP-6 (Report14) DLDDocument17 pages21-CP-6 (Report14) DLDAlmaas ChaudryNo ratings yet

- Lab 6Document4 pagesLab 6marwa abdelrazikNo ratings yet

- Flip FlopsDocument29 pagesFlip FlopsShweta RoyNo ratings yet

- LN 09 Sequential Logic ModulesDocument51 pagesLN 09 Sequential Logic ModulesSrilekha VallabhaneniNo ratings yet

- Prof. Anantha Chandrakasan and Prof. Don TroxelDocument10 pagesProf. Anantha Chandrakasan and Prof. Don TroxelCristian CastroNo ratings yet

- 341 2 13 2002Document23 pages341 2 13 2002Carlos Ch GoNo ratings yet

- L5: Simple Sequential Circuits and VerilogDocument25 pagesL5: Simple Sequential Circuits and VerilogGaurav UpadhyayNo ratings yet

- General Synchronous Digital Systems and Synchronous CountersDocument27 pagesGeneral Synchronous Digital Systems and Synchronous CountersLiyanage GihanNo ratings yet

- CSE 307: Digital TechniqueDocument33 pagesCSE 307: Digital TechniquemmlabjpNo ratings yet

- Synthesis of Reversible Sequential ElementsDocument32 pagesSynthesis of Reversible Sequential ElementskamarajvlsiNo ratings yet

- ELE 4613 - ProjectDocument6 pagesELE 4613 - ProjectmukulNo ratings yet

- Topic 5: Servo Chip DesignDocument50 pagesTopic 5: Servo Chip Designboarddk1No ratings yet

- VHDL SequentialDocument5 pagesVHDL SequentialSAKETSHOURAVNo ratings yet

- Cb2re TBDocument2 pagesCb2re TBOrrette BakerNo ratings yet

- Chapter 9: Sequential Logic Modules: Prof. Soo-Ik ChaeDocument51 pagesChapter 9: Sequential Logic Modules: Prof. Soo-Ik ChaeeceaitsrajampetNo ratings yet

- Synopsys Tools For Verilog Simulation: Run GUI by Using Vcs - RIDocument19 pagesSynopsys Tools For Verilog Simulation: Run GUI by Using Vcs - RIApoorva BhattNo ratings yet

- Document 1Document4 pagesDocument 1Puneeth Kumar ReddyNo ratings yet

- EC381 Lecture16 PDFDocument24 pagesEC381 Lecture16 PDFCorazon corazonNo ratings yet

- Simulation SeminarDocument45 pagesSimulation SeminarKapasi TejasNo ratings yet

- Verilog Sequential ModelingDocument8 pagesVerilog Sequential ModelingR INI BHANDARINo ratings yet

- Flip FlopsDocument25 pagesFlip FlopsNagul MeeraNo ratings yet

- Hardware Slides 08Document30 pagesHardware Slides 08Taqi ShahNo ratings yet

- Chapter 6 Registers Counters1-1Document29 pagesChapter 6 Registers Counters1-1mary_nailynNo ratings yet

- Chap 08 Marlin 2002Document37 pagesChap 08 Marlin 2002Audrey Patrick KallaNo ratings yet

- Aim:-Implementation of Up Counter, Down Counter and Up-Down CounterDocument5 pagesAim:-Implementation of Up Counter, Down Counter and Up-Down CounterJaspreet KaurNo ratings yet

- HDL Programming AssignmentDocument7 pagesHDL Programming Assignmentpinaka paniNo ratings yet

- VHDL SynthesisDocument16 pagesVHDL SynthesisNickos PopoviciNo ratings yet

- Dic File - 7 SemDocument22 pagesDic File - 7 SemShalini SharmaNo ratings yet

- CB4CEDocument2 pagesCB4CE劉成No ratings yet

- Ee 241 Digital Circuits Final Exam Solution ManualDocument10 pagesEe 241 Digital Circuits Final Exam Solution ManualkdrdNo ratings yet

- CH 17Document52 pagesCH 17Juju salehNo ratings yet

- ASIC Va VHDL Toan TapDocument76 pagesASIC Va VHDL Toan TapCường VũNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- MathsDocument2 pagesMathsavinash_yuvarajNo ratings yet

- Course SyllabusDocument10 pagesCourse Syllabusavinash_yuvarajNo ratings yet

- 2021-2022 Final Individual TTDocument75 pages2021-2022 Final Individual TTavinash_yuvarajNo ratings yet

- Assignment 2 III BDocument3 pagesAssignment 2 III Bavinash_yuvarajNo ratings yet

- 19ELE35 QUIZ 3C Quiz 2Document1 page19ELE35 QUIZ 3C Quiz 2avinash_yuvarajNo ratings yet

- Ece Second Year 2021-2022Document77 pagesEce Second Year 2021-2022avinash_yuvarajNo ratings yet

- Assignment 2 III BDocument3 pagesAssignment 2 III Bavinash_yuvarajNo ratings yet

- Lecture A 2.Fsm ReviewDocument14 pagesLecture A 2.Fsm Reviewavinash_yuvarajNo ratings yet

- Assignment I - III BDocument3 pagesAssignment I - III Bavinash_yuvarajNo ratings yet

- Q.No Solution Marks 1Document4 pagesQ.No Solution Marks 1avinash_yuvarajNo ratings yet

- Digital Signal Processing LabDocument36 pagesDigital Signal Processing Labavinash_yuvarajNo ratings yet

- EECS 373: Design of Microprocessor-Based SystemsDocument29 pagesEECS 373: Design of Microprocessor-Based Systemsavinash_yuvarajNo ratings yet

- Org 00H MOV C, P1.7 ANL C,/P1.6 MOV P1.5, C MOV C, P1.7 CPL C ANL C, P1.6 MOV P1.4, C ORL C, P1.5 MOV P1.3, C MOV C, P1.7 ANL C, P1.6 MOV P1.2, C ENDDocument1 pageOrg 00H MOV C, P1.7 ANL C,/P1.6 MOV P1.5, C MOV C, P1.7 CPL C ANL C, P1.6 MOV P1.4, C ORL C, P1.5 MOV P1.3, C MOV C, P1.7 ANL C, P1.6 MOV P1.2, C ENDavinash_yuvarajNo ratings yet

- Datasheet de OsciloscopioDocument9 pagesDatasheet de OsciloscopioDanny Josue Love DlNo ratings yet

- ARM Twin Trip v4 Owners ManualDocument19 pagesARM Twin Trip v4 Owners ManualMichaelKubaNo ratings yet

- Salesforce CRM Implementation ChecklistDocument11 pagesSalesforce CRM Implementation Checklist5gzqvjtn6qNo ratings yet

- FR-XX-XXXX PrinterEventFile 0Document2 pagesFR-XX-XXXX PrinterEventFile 0Jp IshiNo ratings yet

- Electricity EngineeringDocument120 pagesElectricity Engineeringttai76649No ratings yet

- KANIKADocument16 pagesKANIKAKartik mondalNo ratings yet

- Introduction To Power Electronics: Robert W. Erickson University of Colorado, Boulder Fall 2015Document38 pagesIntroduction To Power Electronics: Robert W. Erickson University of Colorado, Boulder Fall 2015Engenheiro TeslandoNo ratings yet

- GSA-Region Spotlight Latin America April 2024Document8 pagesGSA-Region Spotlight Latin America April 2024Rodrigo BarretoNo ratings yet

- Role of Cyber Law in Cyber Security in IndiaDocument4 pagesRole of Cyber Law in Cyber Security in IndiaHJ ManviNo ratings yet

- MIL Q2 Module 8Document27 pagesMIL Q2 Module 8MICHAEL JIMENO100% (1)

- dm00369109 Getting Started With The ST Bluenrg Mesh Android Application StmicroelectronicsDocument23 pagesdm00369109 Getting Started With The ST Bluenrg Mesh Android Application StmicroelectronicsWallace FerreiraNo ratings yet

- Here Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyDocument1 pageHere Is The Complete Circuit of The DREAM 6800 Minus The Power SupplyHernan BenitesNo ratings yet

- LM386 Audio Amplifier Circuits With PCBDocument20 pagesLM386 Audio Amplifier Circuits With PCBMuhammad YousafNo ratings yet

- EM FW and TFTP FAQDocument10 pagesEM FW and TFTP FAQDustin DavenportNo ratings yet

- ReadmeDocument7 pagesReadmeAshwin ReddyNo ratings yet

- Nog Mpls FRR PDFDocument232 pagesNog Mpls FRR PDFMoïse GuilavoguiNo ratings yet

- Construction Estimate &value EngineeringDocument30 pagesConstruction Estimate &value EngineeringCharles Nacorda100% (1)

- CS 801D PDFDocument4 pagesCS 801D PDFarnab paulNo ratings yet

- Kautilya ResumeDocument2 pagesKautilya ResumebhanuyadavNo ratings yet

- Amazon Vs AlibabaDocument3 pagesAmazon Vs AlibabaPaulina CarmonaNo ratings yet

- Change Order FormDocument5 pagesChange Order FormM Kemal PasheryNo ratings yet

- MX-321Document6 pagesMX-321Akun Backup100% (1)

- Network 3D Blu-Ray Disc™ / DVD Player: Owner'S ManualDocument62 pagesNetwork 3D Blu-Ray Disc™ / DVD Player: Owner'S ManualIfeanyi OparaekeNo ratings yet

- AE 27 Lesson 2Document37 pagesAE 27 Lesson 2MARC BENNETH BERIÑANo ratings yet

- CSA Lab Report 1Document5 pagesCSA Lab Report 1Sadat AminNo ratings yet

- Winding Machine Manual in EnglishDocument8 pagesWinding Machine Manual in EnglishViviane CostaNo ratings yet

- Final .Mat Energy Collector Using Piezoelectric Sensor For Public ChargingDocument68 pagesFinal .Mat Energy Collector Using Piezoelectric Sensor For Public ChargingArneitou Queroyla CagungunNo ratings yet

- EDGARDocument4 pagesEDGAREdgar Joseph Quitevis SinampagaNo ratings yet

- 4X4 Keypad Interfacing With ATmega32 (LCD Display)Document6 pages4X4 Keypad Interfacing With ATmega32 (LCD Display)Emin KültürelNo ratings yet