Professional Documents

Culture Documents

DEE6113 - Practical Work3 PDF

DEE6113 - Practical Work3 PDF

Uploaded by

FonzBahariOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

DEE6113 - Practical Work3 PDF

DEE6113 - Practical Work3 PDF

Uploaded by

FonzBahariCopyright:

Available Formats

POLITEKNIK SULTAN HAJI AHMAD SHAH KUANTAN

DEPARTMENT OF ELECTRICAL ENGINEERING

DEE6113 CMOS IC DESIGN

Practical Work 3

Layout Design and Simulation of

CMOS Inverter

Practical Work

Report

(Cognitive)

Practical Skill

Marks

(Psychomotor)

Total

Marks

1.

/ 30

/ 70

/ 100

2.

/ 30

/ 70

/ 100

Registration

No.

No

Name

CLASS

LECTURER NAME

: PN. NOORFOZILA BINTI BAHARI

DATE SUBMITTED

(Note: Submit this page along with the practical skill rubric after each Practical Work is completed)

Practical Work Report Marks Distribution

Report format:

1.

Title and Outcomes

/4

2.

Result

/ 12

3.

Discussion

/ 10

4.

Conclusion

/4

TOTAL :

/ 30

DEE6113 CMOS IC Design

PRACTICAL WORK 3

3.1 TITLE: Layout Design and Simulation of CMOS Inverter.

3.2 LEARNING OUTCOMES

At the end of this practical work session, the student should be able to:

1. design the layout of:

a) vertical inverter layout.

b) horizontal inverter layout.

c) inverter with dual contact and substrate.

d) IC 4069 (CMOS inverter gate IC).

2. simulate CMOS inverter and obtain voltage transfer characteristics (VTC).

3. measure propagation delay.

3.3 EQUIPMENT/TOOLS

PC Set & Microwind 2.6a software.

3.4 PROCEDURE

Part 1 : Designing and simulating vertical CMOS inverter layout

Open the Microwind Editor window.

Select the Foundry file from File menu. Select cmos012.rul file.

Draw the CMOS inverter layout as shown in figure 3.1.

Use : NMOS size - W=6, L=2

PMOS size - W=12, L=2

Make sure to obey the design rules.

Figure 3.1: Vertical CMOS inverterLayout

Run DRC by selecting:

>Analysis>Design Rule Checker

Page | 1

DEE6113 CMOS IC Design

Save your layout.

Apply a clock to the input. Click on the clock icon, and then click on the metal at the gate. The

clock menu appears, change the name to <<Input>>.

Set the value of the input pulse as the following:

Time low = 0.2 ns

Time high = 0.2 ns

Rise time = Fall time = 0.001 ns

Click OK.

To watch the output, click on the Visible icon, and then click on the metal that connects the

Drains. Change the name to <<Output>>. Click OK. The Visible property is then sent to the

node.

Simulate the inverter layout by selecting:

>Simulate> Run Simulation>Voltage vs Time (default) on the main menu.

The timing diagram of the inverter appear, as shown in figure 3.2.

Measure the optimized area of the layout (the unit is lambda2).

Figure 3.2: Timing diagram of vertical CMOS inverter layout

Theory:

Propagation delay

From figure 3.2, when the input rises to logic 1, the output falls to logic 0, with a 5ps delay

(tpHL). When the input falls to logic 0, the output rises to logic 1, with a 15ps delay.

The propagation delay (tp) of the inverter is determined by using the following equation:

tp = ( tpHL + tpLH ) / 2 = ( 5 ps + 15ps ) / 2 = 10 ps where

tpHL = the fall time or the time it takes to change from logic 1 to logic 0.

tpLH = the rise time or the time it takes to change from logic 0 to logic 1.

Page | 2

DEE6113 CMOS IC Design

Layout optimized area

The optimized area of the layout is determined by the following:

Area = Layout Width x Layout Length = 33 x 54 = 1782 2

View the Voltage Transfer Curve (VTC) of the inverter by clicking the voltage vs. voltage tab

as shown in figure 3.2. The VTC of the inverter is shown in figure 3.3.

Figure 3.3: VTC of vertical CMOS inverter layout

Theory :

When the input voltage is low (logic 0), the output voltage is high (logic 1). As input voltage

increases, the output voltage decreases, and at the input voltage = VDD/2 boundary, the output

voltage decreases abruptly. At that point, the value of input voltage is the commutation or

interchange point of the inverter, designated as Vc. As input voltage is further increased towards

VDD, the output voltage decreases to 0 V, which corresponds to the logic 0 of the inverter.

From figure 3.3, it is determined that VDD/2 = 0.6V, which resulted in Vc = 0.541V.

Part 2 : Designing and simulating horizontal CMOS inverter layout.

Open the Microwind Editor window.

Select the Foundry file from File menu. Select cmos012.rul file.

Draw the CMOS inverter layout as shown in figure3. 4.

Use : NMOS size - W=6, L=2

PMOS size - W=12, L=2

Make sure to obey the design rules.

Run DRC by selecting:

>Analysis>Design Rule Checker

Save your layout.

Page | 3

DEE6113 CMOS IC Design

Figure 3.4: Layout of horizontal CMOS inverter layout

Simulate the inverter layout and get the:

a) timing diagram of the inverter

b) VTC of the inverter

c) Propagation delay

Part 3 : Designing and simulating CMOS inverter layout with dual contact and substrate.

N-Well

Figure 3.5: Layout of vertical CMOS inverter layout with dual contact and substrate.

Open the Microwind Editor window.

Select the Foundry file from File menu. Select cmos012.rul file.

Page | 4

DEE6113 CMOS IC Design

Draw the CMOS inverter layout as shown in figure 3.5.

Use : NMOS size - W=6, L=2

PMOS size - W=12, L=2

Make sure to obey the design rules.

Run DRC by selecting:

>Analysis>Design Rule Checker

Save your layout.

Simulate the inverter layout and get the:

a) timing diagram of the inverter

b) VTC of the inverter

Part 4 : Designing the layout of IC 4069 (CMOS inverter ).

Design the layout of IC 4069 based on the CMOS IC logic gates shown in figure 3.6.

Figure 3.6 : Internal Structure of IC 4069

Do the DRC to ensure that your design conforms to all design rules.

Measure the optimized area of the layout (the unit is 2).

3.5 RESULTS

In your report, include the following:

1. Part 1: Vertical CMOS Inverter

a) inverter layout.

b) input / output timing diagram

c) switching threshold voltage, Vc

(3 marks)

2. Part 2: Horizontal CMOS Inverter

a) inverter layout.

b) Input / output timing diagram

c) switching threshold voltage, Vc

(3 marks)

Page | 5

DEE6113 CMOS IC Design

3. Part 3: CMOS Inverter with dual contacts and substrate

a) inverter layout.

b) input / output timing diagram.

c) switching threshold voltage, Vc

(3 marks)

4. Part 4: IC 4069 (CMOS inverter gate IC) and its layout size.

a) IC layout

b) The optimized area of the IC layout

(3 marks)

3.6 DISCUSSION

1.

Make a comparison between the optimized area of the layouts in Part 1, Part 2 and Part 3.

(2 marks)

2.

Make a comparison between the values of Vc for the inverter in Part 1, Part 2, Part 3 and

Part 4.

(2 marks)

3.

Calculate the propagation delay of each layout design in Part 1, Part 2 and Part 3.

(3 marks)

4.

From the comparison in Question 2 and 3, determine which layout design is the best.

Explain your answer.

(3 marks)

3.7 CONCLUSION

Give TWO(2) conclusions for this practical work.

(4 marks)

Page | 6

DEE6113 CMOS IC Design

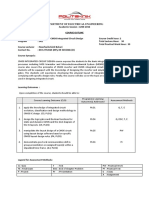

PRACTICAL SKILL ASSESSMENT RUBRIC

DEE6113 CMOS IC DESIGN

PRACTICAL WORK 3

Student Name :

Class :

Student ID# :

Date :

ASPECTS

A.

Technology feature

B.

Design rule

C.

Transistor size

D.

Metal layers

E.

F.

No DRC error

display

Layout Design

input / output /

floorplan

EXCELLENT

4-5

Use correct technology feature

for ALL parts of the layout.

Follow lambda design rule for

minimum width and spacing for

ALL polygons.

Use correct PMOS and NMOS

transistor size.

Use correct number of metal

layers and width.

Able to produce No DRC error

display for ALL layouts.

SCORE DESCRIPTION

MODERATE

2-3

Use correct technology feature

for parts of the layout.

POOR

1

SCALE

Use other technology feature.

x1

Follow lambda design rule for

MANY of the polygons.

Follow lambda design rule for

ONLY a few of the polygons.

x1

Use acceptable PMOS and NMOS

transistor size.

Use correct metal layers but

incorrect width.

Able to produce No DRC error

display for some of the layouts.

Use incorrect PMOS and

NMOS transistor size.

Use incorrect metal layers and

width.

Not able to produce No DRC

error display at ALL.

Produce acceptable floorplan

and input / output layout

design.

Not able to produce any

simulation for ALL of the

layouts.

Produce large layout size (end

product).

Produce good floorplan and

input / output layout design.

Produce appropriate floorplan

and input / output layout design.

Layout simulation

Able to produce the simulation

of ALL layouts correctly.

Able to produce the simulation

for some of the layouts correctly.

H.

Layout size (end

product)

Produce small layout size (end

product).

Produce acceptable layout size

(end product).

TOTAL

SCORE

x2

x2

x2

x2

x2

x2

/ 70

...

Supervisor Name and Signature

You might also like

- 02-Huawei OceanStor Dorado Architecture and Key Technology PDFDocument57 pages02-Huawei OceanStor Dorado Architecture and Key Technology PDFManuel DamilNo ratings yet

- O Impostor Que Vive em Mim - Brennan ManningDocument2 pagesO Impostor Que Vive em Mim - Brennan Manningsreginasoares9950100% (1)

- S.1 Ict e o T 1Document5 pagesS.1 Ict e o T 1Paul KingshipNo ratings yet

- Answer Scheme - Tutorial 1 BMMA 1323 Engineering DesignDocument8 pagesAnswer Scheme - Tutorial 1 BMMA 1323 Engineering DesignI-zad MJNo ratings yet

- AzureDEVOPS PipelineDocument1,055 pagesAzureDEVOPS PipelineKenyon Turner100% (3)

- Telecommunications Presentation PDFDocument11 pagesTelecommunications Presentation PDFcrana10No ratings yet

- Coca ColaDocument3 pagesCoca ColaBernie Victor0% (1)

- Data Comm Lab 4Document10 pagesData Comm Lab 4Sasi TharenNo ratings yet

- Electronic Communication SystemsDocument1 pageElectronic Communication Systemsveeramaniks408No ratings yet

- UMTS Protocol Stack - UMTS TutorialDocument3 pagesUMTS Protocol Stack - UMTS TutorialBiswajit MohantyNo ratings yet

- O Be Briefing 2019Document24 pagesO Be Briefing 2019ekmemonNo ratings yet

- IMT-2000 Network ArchitectureDocument6 pagesIMT-2000 Network ArchitectureMuhd Hisyam AwangNo ratings yet

- Assignment 1 Optical Fibres: Fig: An Optical Fiber Junction BoxDocument11 pagesAssignment 1 Optical Fibres: Fig: An Optical Fiber Junction BoxSagar Kale100% (1)

- Data Communication Assignment Final PDFDocument5 pagesData Communication Assignment Final PDFFahad RuhulNo ratings yet

- Mobile Lab ManualDocument56 pagesMobile Lab Manualnaitikkapadia100% (1)

- Design and Characterization of A Band-Pass Filter PDFDocument6 pagesDesign and Characterization of A Band-Pass Filter PDFjgalindesNo ratings yet

- Impedance BridgeDocument33 pagesImpedance BridgeOBscuRA caMEraNo ratings yet

- Inverse Trigonometric Functions - TN - FDocument9 pagesInverse Trigonometric Functions - TN - Fsjwjwj jeueNo ratings yet

- Ict Computer Studies Book Practical GuideDocument152 pagesIct Computer Studies Book Practical Guidekituno festo sundayNo ratings yet

- Grade 8 and 9 Mathematics SyllabiDocument31 pagesGrade 8 and 9 Mathematics SyllabiMulemba ChimfsNo ratings yet

- DSP Lecture 1Document31 pagesDSP Lecture 1Sana LiaqatNo ratings yet

- Form 1 To Form 4 Complete Computer Studies NotesDocument276 pagesForm 1 To Form 4 Complete Computer Studies NotesAmoz Musyoki100% (1)

- Questions & Answers On Genetic AlgorithmDocument15 pagesQuestions & Answers On Genetic AlgorithmPragya JainNo ratings yet

- Ol Mock 2019 575 Math p2 2019 - 1Document14 pagesOl Mock 2019 575 Math p2 2019 - 1Alphonsius WongNo ratings yet

- 25 Pure Maths Resourceful Mock 2016-2Document4 pages25 Pure Maths Resourceful Mock 2016-2BWENGYE NICHOLASNo ratings yet

- Mobile Comm ArchDocument10 pagesMobile Comm ArchndxinroyNo ratings yet

- Assignment: Network TopologiesDocument17 pagesAssignment: Network TopologiesFatima TariqNo ratings yet

- IEEE Paper FormatDocument3 pagesIEEE Paper FormatRithi VishwanathanNo ratings yet

- Refrigerent LaboratoryDocument18 pagesRefrigerent LaboratoryKRG KickFlashNo ratings yet

- Geography O Level Topical Test IndustryDocument8 pagesGeography O Level Topical Test IndustryAishatuNo ratings yet

- Earth Magnetic Field Lab Report PDFDocument6 pagesEarth Magnetic Field Lab Report PDFAiman FitryNo ratings yet

- Computer Science Paper 2 Final Revision Questions - 2017Document9 pagesComputer Science Paper 2 Final Revision Questions - 2017brightonNo ratings yet

- ET-343: Telecommunication Total Contact HoursDocument8 pagesET-343: Telecommunication Total Contact HoursIsrar UllahNo ratings yet

- Computer Generations Generation in Computer Terminology Is A Change in Technology A Computer Is/wasDocument6 pagesComputer Generations Generation in Computer Terminology Is A Change in Technology A Computer Is/wasYogendra Rajavat100% (1)

- 2014 Standard Technical Method StatementDocument19 pages2014 Standard Technical Method StatementTAHER AMMAR100% (1)

- PERT and CPM NetworksDocument50 pagesPERT and CPM NetworksAnkkit BafnaNo ratings yet

- Digital Logic FPGA Lab ManualDocument35 pagesDigital Logic FPGA Lab ManualBilal RajaNo ratings yet

- CPPDocument81 pagesCPPShriya ShriNo ratings yet

- Transmission LinesDocument19 pagesTransmission LinesNavarshi VishnubhotlaNo ratings yet

- Mobile Computing Unit 1Document175 pagesMobile Computing Unit 1haftamu GebreHiwot100% (1)

- Assignment Mec 435 PDFDocument2 pagesAssignment Mec 435 PDFilhamNo ratings yet

- Magnetic Effects of Electric Current QuestionsDocument2 pagesMagnetic Effects of Electric Current QuestionsVinod KumarNo ratings yet

- 2023-08-03 16 34 34-DIT-Call For Applications Tanzania Young Women Scholarship Under Energy Efficiency Program EU-UNDP FUNDED 20232024Document2 pages2023-08-03 16 34 34-DIT-Call For Applications Tanzania Young Women Scholarship Under Energy Efficiency Program EU-UNDP FUNDED 20232024Eng P-thegunNo ratings yet

- Chapter One: Introduction To Computer ProgramsDocument12 pagesChapter One: Introduction To Computer Programsiqa11No ratings yet

- The Copperbelt University School of Mathematics and Natural Sciences Department of Physics PH 110 Introductory PhysicsDocument3 pagesThe Copperbelt University School of Mathematics and Natural Sciences Department of Physics PH 110 Introductory PhysicsLazy BanditNo ratings yet

- Section A: Computer Science Paper 2 6023Document6 pagesSection A: Computer Science Paper 2 6023MushawatuNo ratings yet

- Notes To Schools 2024-2025 FinalDocument68 pagesNotes To Schools 2024-2025 Finaltrizzydaniels352No ratings yet

- Networking BasicsDocument137 pagesNetworking BasicsJerald Sam ThanarajNo ratings yet

- 11 Types of Networks ExplainedDocument2 pages11 Types of Networks ExplainedDwin RoscoNo ratings yet

- Landslide - Kg. PasirDocument9 pagesLandslide - Kg. PasiruyunamanNo ratings yet

- The Switch Book by Rich Seifert-NotesDocument51 pagesThe Switch Book by Rich Seifert-NotesharinijNo ratings yet

- Form 1 2023 End T3 Mathematics QS - Teacher - Co - .Ke - Set - ADocument15 pagesForm 1 2023 End T3 Mathematics QS - Teacher - Co - .Ke - Set - AYussuf Hirow100% (1)

- Lab Report Exp 3-Phy443Document10 pagesLab Report Exp 3-Phy443firdausNo ratings yet

- Zimsec Computer Science NotesDocument20 pagesZimsec Computer Science NotesFungaiNo ratings yet

- Advantages & Disadvantages of NetworksDocument8 pagesAdvantages & Disadvantages of NetworkssarbaazzNo ratings yet

- Linear Motion QDocument4 pagesLinear Motion QBonface Kenani100% (1)

- CSC128 CSC415Document11 pagesCSC128 CSC415Izzatul Atiq RosseliNo ratings yet

- Mock Test AnswerDocument6 pagesMock Test AnswermuizNo ratings yet

- FYP Report Format - F15Document38 pagesFYP Report Format - F15Funny VideosNo ratings yet

- C520BDocument4 pagesC520BSahrulRashid0% (1)

- Digit1 Lab02Document10 pagesDigit1 Lab02priyadarshini212007No ratings yet

- LP3Document15 pagesLP3Saenal TataNo ratings yet

- Dec50143 PW2Document8 pagesDec50143 PW2Muhammad JazliNo ratings yet

- Dec50143 Pw2 IzzDocument11 pagesDec50143 Pw2 Izziskandardaniel0063No ratings yet

- DEE6113 - Practical Work4 PDFDocument10 pagesDEE6113 - Practical Work4 PDFFonzBahari0% (1)

- DEE6113 - Practical Work2 PDFDocument10 pagesDEE6113 - Practical Work2 PDFFonzBahariNo ratings yet

- DEE6113 - Practical Work6 PDFDocument4 pagesDEE6113 - Practical Work6 PDFFonzBahari0% (1)

- DEE6113 - Practical Work5 PDFDocument7 pagesDEE6113 - Practical Work5 PDFFonzBahariNo ratings yet

- DEE6113 - Practical Work2 PDFDocument10 pagesDEE6113 - Practical Work2 PDFFonzBahariNo ratings yet

- DEE6113 - Practical Work4 PDFDocument10 pagesDEE6113 - Practical Work4 PDFFonzBahari0% (1)

- DEE6113 - Practical Work1 PDFDocument6 pagesDEE6113 - Practical Work1 PDFFonzBahariNo ratings yet

- DEE6113 Course Outline Jun2016Document4 pagesDEE6113 Course Outline Jun2016FonzBahariNo ratings yet

- User Manual: Model 1080arcDocument15 pagesUser Manual: Model 1080arcelyuyaNo ratings yet

- Commvault Complete License GuideDocument28 pagesCommvault Complete License GuidescribdrasmusNo ratings yet

- Cad 2 MarksDocument13 pagesCad 2 MarksAnonymous JnvCyu85No ratings yet

- Computer Network Questions With AnswersDocument2 pagesComputer Network Questions With Answersohviya100% (1)

- 24AA128/24LC128/24FC128: 128K I C Cmos Serial EepromDocument26 pages24AA128/24LC128/24FC128: 128K I C Cmos Serial EepromcraponzelNo ratings yet

- Accessing Cluster Tables in SAPDocument3 pagesAccessing Cluster Tables in SAPFactsNTipsNo ratings yet

- Chapter 4 Network TopologiesDocument53 pagesChapter 4 Network TopologiesKaruppanan KomathyNo ratings yet

- ICT Strategic Plan 2015-2017: April 2015Document23 pagesICT Strategic Plan 2015-2017: April 2015abey.mulugetaNo ratings yet

- Tl-Wa850re Qig V6Document2 pagesTl-Wa850re Qig V6Eduard Luka MudriNo ratings yet

- Project Management Foundations: Small ProjectsDocument4 pagesProject Management Foundations: Small ProjectsManu GtezNo ratings yet

- Ipfs p2p File SystemDocument11 pagesIpfs p2p File Systemeasy_astronautNo ratings yet

- Smart SensorsDocument19 pagesSmart SensorsHareesh HarshaNo ratings yet

- Iot Topic BriefDocument31 pagesIot Topic Briefvirender solankiNo ratings yet

- Connect Strain Gages To A Data Acquisition (DAQ) Device - National InstrumentsDocument6 pagesConnect Strain Gages To A Data Acquisition (DAQ) Device - National InstrumentsLuigi ChulimNo ratings yet

- CenovnikDocument5 pagesCenovnikKristijan VeljanovskiNo ratings yet

- Unit I 2 Mark QuestionsDocument5 pagesUnit I 2 Mark QuestionsDennis Ebenezer DhanarajNo ratings yet

- Network Operating SystemDocument9 pagesNetwork Operating SystemShouban Jatoi100% (1)

- Symantec DLP 10.5 System Requirements GuideDocument57 pagesSymantec DLP 10.5 System Requirements Guidefxnoob80No ratings yet

- FDSFSDDocument35 pagesFDSFSDAndreaNo ratings yet

- Symbolic URLDocument8 pagesSymbolic URLKoti BhgamNo ratings yet

- Read The Docs - Espressif PDFDocument2,201 pagesRead The Docs - Espressif PDFMiguel GarcíaNo ratings yet

- Distribution Receiver: Product Overview Base Unit FeaturesDocument3 pagesDistribution Receiver: Product Overview Base Unit FeaturesfrankmeersNo ratings yet

- VPCYB35AN - Y Series - VAIO™ Laptop & Computer - Sony IndiaDocument3 pagesVPCYB35AN - Y Series - VAIO™ Laptop & Computer - Sony IndiaSayee KrishnaNo ratings yet

- BCO 113 It Concepts & System Analysis and DesignDocument61 pagesBCO 113 It Concepts & System Analysis and DesignDiola QuilingNo ratings yet

- Micrologix Lab 2Document26 pagesMicrologix Lab 2Fernando Jaime Alonso MartínezNo ratings yet

- Microproceesor Lab ManualDocument5 pagesMicroproceesor Lab ManualrajanNo ratings yet