Professional Documents

Culture Documents

Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, Venkateshappa

Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, Venkateshappa

Uploaded by

Sumanth VarmaCopyright:

Available Formats

You might also like

- Lab Exercise #1: Introduction To The Cypress Fm4 Board and Fm4 Starter KitDocument12 pagesLab Exercise #1: Introduction To The Cypress Fm4 Board and Fm4 Starter KitAhmed HamoudaNo ratings yet

- Computer Interface Trainer (MDA-Win8086) - ProjectDocument77 pagesComputer Interface Trainer (MDA-Win8086) - Projectranahamid00783% (12)

- 70 742 Microsoft Identity With Windows Server 2016Document9 pages70 742 Microsoft Identity With Windows Server 2016NehaNo ratings yet

- EE8681 Lab ManualDocument110 pagesEE8681 Lab ManualVasunthara DNo ratings yet

- Link Budget Analysis Guide: November 21, 2014Document19 pagesLink Budget Analysis Guide: November 21, 2014Анатолий МаловNo ratings yet

- PIC12F629/675/PIC16F630/676Document24 pagesPIC12F629/675/PIC16F630/676Romel Ranin CalangNo ratings yet

- Training ReportDocument18 pagesTraining Reportpiyushji125No ratings yet

- Analog To Digital Converter: Vitrax Plus ControllerDocument13 pagesAnalog To Digital Converter: Vitrax Plus Controlleries837No ratings yet

- Question Bank-Microprocessor and ApplicaionDocument38 pagesQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- 16f8x Serial ProgDocument16 pages16f8x Serial ProgIgnacio MartiNo ratings yet

- RTL2GDSFLOWDocument23 pagesRTL2GDSFLOWAbhishek Gupta0% (1)

- BME 438 Digital Logic Design and Computer Architecture LabDocument73 pagesBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaNo ratings yet

- Application SSC02 eDocument4 pagesApplication SSC02 eDragosFlorinLismanNo ratings yet

- Mbe Fix32Document5 pagesMbe Fix32Cristina MonteiroNo ratings yet

- Introduction To Chapter 7: Ronald Tocci/Neal Widmer/Gregory MossDocument37 pagesIntroduction To Chapter 7: Ronald Tocci/Neal Widmer/Gregory MossAmmar FarooqNo ratings yet

- cs2304 System Software 2 Marks and 16 Marks With AnswerDocument18 pagescs2304 System Software 2 Marks and 16 Marks With Answermanojkumar024No ratings yet

- En 25 F 80Document33 pagesEn 25 F 80mactocheNo ratings yet

- Csc343 LAB Register File: ObjectiveDocument11 pagesCsc343 LAB Register File: ObjectiveBharavi K SNo ratings yet

- 2 Marks With AnswersDocument14 pages2 Marks With Answersprisci_durai83% (6)

- Discontinued: Synchronous FIFO 5.0Document10 pagesDiscontinued: Synchronous FIFO 5.0Prathap NsNo ratings yet

- IMA ADPCM EncDec Core SpecificationsDocument11 pagesIMA ADPCM EncDec Core SpecificationsMaria MafteiNo ratings yet

- 2 Marks Que &ansDocument30 pages2 Marks Que &ansKanthimathi SureshNo ratings yet

- PDF 2Document13 pagesPDF 2Nivedita Acharyya 2035No ratings yet

- 6713 User ManualDocument92 pages6713 User Manualsningle100% (1)

- VBMB 15 (New)Document46 pagesVBMB 15 (New)anand_duraiswamyNo ratings yet

- An, Improved Successive-Approximation Register Design For Use in A/D ConvertersDocument5 pagesAn, Improved Successive-Approximation Register Design For Use in A/D ConvertersOmer KhanNo ratings yet

- Advanced Topics: 17.1 Hardware Control Using I/O PortsDocument34 pagesAdvanced Topics: 17.1 Hardware Control Using I/O Portsbarbarossa17No ratings yet

- Embed Lab9Document10 pagesEmbed Lab9amitpanvekarNo ratings yet

- Compass OverviewDocument44 pagesCompass OverviewjersonNo ratings yet

- Design and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformDocument6 pagesDesign and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformIheb HamedNo ratings yet

- Finnal Diploma ME 111 Control ProjectDocument18 pagesFinnal Diploma ME 111 Control ProjectSharif AwadNo ratings yet

- This Set of 8051 MicroDocument21 pagesThis Set of 8051 MicroSonaliNo ratings yet

- Flash ADC Design in ElectricDocument22 pagesFlash ADC Design in ElectricNagaraj HegdeNo ratings yet

- Keypad Encoder Approval ReportDocument2 pagesKeypad Encoder Approval ReportMuzammil MetkarNo ratings yet

- Lab6 LCDDocument19 pagesLab6 LCDPatipan Jariyapum100% (4)

- Sim RimDocument13 pagesSim RimKalai VaniNo ratings yet

- 8085 Microprocessor UNIT 4Document14 pages8085 Microprocessor UNIT 4Er SarbeshNo ratings yet

- Interfacing The ADS7881 To The TMS320C6713 DSP: Application ReportDocument14 pagesInterfacing The ADS7881 To The TMS320C6713 DSP: Application ReportSashikanth BethaNo ratings yet

- AnnaDocument73 pagesAnnaDriti DasNo ratings yet

- Week 3 - Four Instruction CPUDocument8 pagesWeek 3 - Four Instruction CPUGame AccountNo ratings yet

- VHDL Implementation of BIST Technique in UART DesignDocument5 pagesVHDL Implementation of BIST Technique in UART DesignRakesh GeorgeNo ratings yet

- Traffic Light Controller Using VHDLDocument6 pagesTraffic Light Controller Using VHDLAbdoulrazakNo ratings yet

- PIC12F508/509: Memory Programming SpecificationDocument20 pagesPIC12F508/509: Memory Programming SpecificationMartin CépedaNo ratings yet

- Chapter 16 - DSPDocument58 pagesChapter 16 - DSPMaira HaiderNo ratings yet

- Laboratory 5 - ADC ManualDocument18 pagesLaboratory 5 - ADC ManualSravan KumarNo ratings yet

- Emerson DCS PresentationDocument25 pagesEmerson DCS Presentationruchikaporwal2018No ratings yet

- University Solved Answers Unit 1 SS (System Software Notes)Document12 pagesUniversity Solved Answers Unit 1 SS (System Software Notes)Vaishnavi Rave100% (1)

- 8085 PDocument31 pages8085 PAnish ChibNo ratings yet

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 pagesDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveNo ratings yet

- Microprocessors and Assembly Language EC4121: Lecture 1: Introduction By: Mohamed Elnourani 0911471315Document27 pagesMicroprocessors and Assembly Language EC4121: Lecture 1: Introduction By: Mohamed Elnourani 0911471315divine serpentNo ratings yet

- Xilinx Answer 73361 PCIe Link Training Debug Guide For US and US PlusDocument54 pagesXilinx Answer 73361 PCIe Link Training Debug Guide For US and US PlusEvamGilotraNo ratings yet

- 16 F 506Document22 pages16 F 506Kavin SengodanNo ratings yet

- Software Stage EDocument19 pagesSoftware Stage ETim TaylorNo ratings yet

- Physical Design Implementation of 16 Bit Risc ProcessorDocument7 pagesPhysical Design Implementation of 16 Bit Risc Processorashish jhaNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- Establishing Qor Flow On Emerging Technology Nodes: Pramod Sripathi Sreenivasa Reddy Kasireddy Raj Sekhar BochkarDocument33 pagesEstablishing Qor Flow On Emerging Technology Nodes: Pramod Sripathi Sreenivasa Reddy Kasireddy Raj Sekhar BochkarSumanth VarmaNo ratings yet

- Eeiol 2009mar26 Eda Ta 01Document2 pagesEeiol 2009mar26 Eda Ta 01Sumanth VarmaNo ratings yet

- An Alternative Approach To Buffer Insertion For Delay and Power Reduction in VLSI InterconnectsDocument6 pagesAn Alternative Approach To Buffer Insertion For Delay and Power Reduction in VLSI InterconnectsSumanth VarmaNo ratings yet

- Synthesis Assignment - 1Document3 pagesSynthesis Assignment - 1Sumanth VarmaNo ratings yet

- Implementing Double Data Rate I/O Signaling in Stratix & Stratix GX DevicesDocument22 pagesImplementing Double Data Rate I/O Signaling in Stratix & Stratix GX DevicesSumanth VarmaNo ratings yet

- Metastability and Synchronizers - IEEEDToct2011 PDFDocument13 pagesMetastability and Synchronizers - IEEEDToct2011 PDFSumanth VarmaNo ratings yet

- 5 AdderDocument35 pages5 AdderSumanth VarmaNo ratings yet

- Low Power Design Methodologies and FlowsDocument52 pagesLow Power Design Methodologies and FlowsSumanth VarmaNo ratings yet

- LEC Jumpstart Training OverviewDocument37 pagesLEC Jumpstart Training OverviewSumanth VarmaNo ratings yet

- Introduction To Cmos Vlsi Design: Nonideal TransistorsDocument30 pagesIntroduction To Cmos Vlsi Design: Nonideal TransistorsSumanth VarmaNo ratings yet

- Body Bias Scaling For Globalfoundries 22fdx Technology New Dimension To Explore The DesignDocument28 pagesBody Bias Scaling For Globalfoundries 22fdx Technology New Dimension To Explore The DesignSumanth VarmaNo ratings yet

- Full-Scan: (Lecture 19alt in The Alternative Sequence)Document22 pagesFull-Scan: (Lecture 19alt in The Alternative Sequence)Sumanth VarmaNo ratings yet

- Understanding and Validating The Detailed Power Report Generated by The Report - Instance - Power Voltus CommandDocument6 pagesUnderstanding and Validating The Detailed Power Report Generated by The Report - Instance - Power Voltus CommandSumanth VarmaNo ratings yet

- How Can I Easily Report Paths Which Cross Clock Domains PDFDocument3 pagesHow Can I Easily Report Paths Which Cross Clock Domains PDFSumanth VarmaNo ratings yet

- Logical Correlation Analysis On Victim and Aggressor Pairs With The Same SenseDocument3 pagesLogical Correlation Analysis On Victim and Aggressor Pairs With The Same SenseSumanth VarmaNo ratings yet

- Magic Blue Smoke Low Power General PDFDocument6 pagesMagic Blue Smoke Low Power General PDFSumanth VarmaNo ratings yet

- Magic Blue Smoke Low Power General PDFDocument6 pagesMagic Blue Smoke Low Power General PDFSumanth VarmaNo ratings yet

- Features: Frequency DividerDocument6 pagesFeatures: Frequency DividerSumanth VarmaNo ratings yet

- 3 GPPDocument95 pages3 GPPdezzgsNo ratings yet

- Prototypes For RPG IV ApisDocument10 pagesPrototypes For RPG IV Apisrachmat99No ratings yet

- FTDI Chip: USB SolutionsDocument20 pagesFTDI Chip: USB SolutionsPaloma Sousa100% (1)

- 11 - K8s On AWS ChecklistDocument8 pages11 - K8s On AWS Checklistmacod15739No ratings yet

- Lab Manual - RTOS AchitectureDocument6 pagesLab Manual - RTOS Achitectureritika jaiswalNo ratings yet

- Combiprobe UserDocument19 pagesCombiprobe Usercarver_uaNo ratings yet

- Archetype Write-Up: ImpacketDocument17 pagesArchetype Write-Up: ImpacketJiohnNo ratings yet

- Advance of Festivals in KarnatakaDocument13 pagesAdvance of Festivals in KarnatakaRhiteshNo ratings yet

- DNS, SNMP, Web ServiceDocument25 pagesDNS, SNMP, Web ServiceJayaprasannaNo ratings yet

- 4D HyperV and Exchange 2016 Powershell Cheat SheetDocument2 pages4D HyperV and Exchange 2016 Powershell Cheat Sheetm00anj00No ratings yet

- Network Access Control: Software and HarwareDocument2 pagesNetwork Access Control: Software and Harwareanurag_0290100% (1)

- V-1200HDR / V-1200HD RCS Remote Control Guide: Ver. 1.4 and LaterDocument94 pagesV-1200HDR / V-1200HD RCS Remote Control Guide: Ver. 1.4 and LateragomezagNo ratings yet

- 3 Freescale ToDocument34 pages3 Freescale ToAmine FouratiNo ratings yet

- User Guide: 5000B Data Acquisition and Logging Unit Versions 3.4 and Later HA027566/11 September 2012Document160 pagesUser Guide: 5000B Data Acquisition and Logging Unit Versions 3.4 and Later HA027566/11 September 2012Ricardo Cesar SantanaNo ratings yet

- Log Cat 1687020337817Document540 pagesLog Cat 1687020337817story waNo ratings yet

- Meb9400 OmDocument326 pagesMeb9400 Ommax51sNo ratings yet

- USB Made EasyDocument141 pagesUSB Made EasyAndres Bruno Saravia100% (1)

- Unix CommandsDocument20 pagesUnix CommandsdineshkandeNo ratings yet

- Case Study Tcp-IpDocument27 pagesCase Study Tcp-IpsarathkumarNo ratings yet

- Tcpreplay-Edit Man PageDocument22 pagesTcpreplay-Edit Man PageEduardo FloresNo ratings yet

- Gravostyle 8 Installation GuideDocument22 pagesGravostyle 8 Installation GuideIstvan GazdagNo ratings yet

- 7.7.2.2 Common Problems and Solutions For LaptopsDocument3 pages7.7.2.2 Common Problems and Solutions For LaptopsDickya Hidayah putra100% (1)

- PSPC Notes - Unit - 1Document22 pagesPSPC Notes - Unit - 1Samba SivaNo ratings yet

- AWS Security Checklist PDFDocument3 pagesAWS Security Checklist PDFAdy GokaNo ratings yet

- Computer - 2Document18 pagesComputer - 2aksahu01234No ratings yet

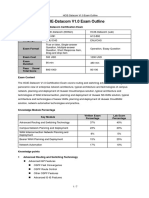

- HCIE-Datacom V1.0 Exam OutlineDocument7 pagesHCIE-Datacom V1.0 Exam Outlineabera alemayehuNo ratings yet

- Topic02 Data AcquisitionDocument26 pagesTopic02 Data AcquisitionHappy Plants BDNo ratings yet

- H801MCUD1 Board DatasheetDocument1 pageH801MCUD1 Board DatasheetPablo AntonieNo ratings yet

- Driver Settings - Color Image Quality Ps v171020Document3 pagesDriver Settings - Color Image Quality Ps v171020nourmlk1859No ratings yet

Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, Venkateshappa

Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, Venkateshappa

Uploaded by

Sumanth VarmaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, Venkateshappa

Full Chip Level Implementation of Reed Solomon Encoder: Amar Narayan, Sheetal Belaldavar, Venkateshappa

Uploaded by

Sumanth VarmaCopyright:

Available Formats

FULL CHIP LEVEL IMPLEMENTATION OF REED

SOLOMON ENCODER

1

AMAR NARAYAN, 2SHEETAL BELALDAVAR, 3VENKATESHAPPA

M.Tech Student, Dept. of ECE, MSEC, 2M.Tech Student, Dept. of ECE, MSEC, 3Associate Professor, Dept. of ECE, MSEC

Abstract- Reed-Solomon codes are block-based error correcting codes with a wide range of applications in digital

communications and storage .The Reed-Solomon encoder takes a block of digital data and adds extra "redundant" bits. The

number and type of errors that can be corrected depends on the characteristics of the Reed-Solomon code .The Reed-Solomon

Encoder is used in many Forward Error Correction (FEC) applications and in systems where data are transmitted and subject

to errors before reception . In this paper Full Chip level Implementation of Reed Solomon Encoder has been carried out. In

Full Chip Level Implementation, in order to optimize the area of the design, SIPO and PISO shift registers are implemented

and also the I/O pads, VDD and VSS pads are added in to the design. The timing, area and the power values which are

obtained during Synthesis are as follows: Timing=0.0(Met), Area=9965.160037 and Power=2.33878mW respectively and the

physical design steps such as Floor Planning, Placement, CTS, Routing and Verification are carried out in the design.

Index Terms- RS Encoder, SIPO, PISO, Floor Planning, Placement, CTS, Routing.

I. INTRODUCTION

II. IDENTIFICATION OF NUMBER OF I/O

SIGNAL PINS

The Reed-Solomon encoder takes a block of digital

data and adds extra "redundant" bits. Errors occur

during transmission or storage for a number of reasons

(for example noise or interference, scratches on a CD,

etc). The Reed-Solomon decoder processes each block

and attempts to correct errors and recover the original

data. The Reed-Solomon Encoder is used in many

Forward Error Correction (FEC) applications and in

systems where data are transmitted and subject to

errors before reception. The following figure 1 shows

the typical Reed-Solomon Encoder and Decoder

System.

In order to optimize the area of the design, i.e, the

number of I/O pins, SIPO and PISO shift registers are

implemented. The SIPO and PISO shift registers are

as explained below.

III. SIPO ( SERIAL IN PARALLEL OUT)

A serial-in/parallel-out shift register is similar to the

serial-in/ serial-out shift register in that it shifts data

into internal storage elements and shifts data out at the

serial-out, data-out, pin. It is different in that it makes

all the internal stages available as outputs. Therefore,

a serial-in/parallel-out shift register converts data

from serial format to parallel format. The following

figure 2 shows the 4 bit SIPO shift register.

(Source: Martyn Riley and Iain Richardson)

Fig 1 Typical Reed Solomon Encoder and Decoder System

The concept of area optimization plays a very

important key role in the determination of

performance of the system. In this paper in order to

optimize the area of the design, SIPO and PISO shift

registers are implemented. The Full chip level

integrated circuit consists of core (logic circuit) and

I/O PAD circuits. Logic cells (standard cell) and

macros are placed inside the core area and I/O PAD

circuits are connected to core for signal

communication with the external world. The I/O Pad

containing I/O circuit and clock circuits protects the

design from any external hazards such as Electro

Static Discharge (ESD) and noises.

Fig 2 4 bit SIPO Shift Register

PISO ( Parallel In Serial Out):A four-bit parallel in - serial out shift register is shown

in the below fig 3. The circuit uses D flip-flops and

NAND gates for entering data (ie writing) to the

Proceedings of IRF International Conference, Chennai, India, 20th April. 2014, ISBN: 978-93-84209-07-0

123

Full Chip Level Implementation of Reed Solomon Encoder

register. D0, D1, D2 and D3 are the parallel inputs,

where D0 is the most significant bit and D3 is the least

significant bit. To write data in, the mode control line

is taken to LOW and the data is clocked in. The data

can be shifted when the mode control line is HIGH as

SHIFT is active high. The register performs right

shift operation on the application of a clock pulse.

So from the Table 2 it can be concluded that the total

number of I/O signal Pins after adding SIPO and PISO

shift registers are 32 Pins.

IV. CALCULATION OF NUMBER OF VSS AND

VDD PADS

The following figure 4 shows the arrangement of the

VDD and VSS Pads on the four sides of the design.

Fig 4 Arrangement of VDD and VSS Pads

The following table 3 shows the total number of VDD

and VSS Pads and it can be concluded that the total

number of VDD and VSS Pads which are arranged on

the top, bottom, right and left sides of the design are 8

Pads.

Fig 3 4 Bit PISO Shift Register

The total number of Pins used in the Block level

implementation of the Reed Solomon Encoder design

is as shown below in the table 1.

Table 1 Total Number of Pins Used in the Block Level

Implementation

Table 3 Total Number of VDD and VSS Pads

From the table 3 it can be seen that the total number of

VDD and VSS Pads which are arranged on the top,

bottom, right and left sides of the design are 8 Pads.

V. DESIGN OF TOP DESIGN FILE (TDF)

So total number of Pins used initially in the design of

the Reed Solomon Encoder including the VSS (4 Pins)

and VDD (4 Pins) are 267 Pins. During Chip Level

Implementation of the design the Verilog code is read

after adding SIPO and PISO shift registers into the

design. Therefore the total number of Input/ Output

Signal Pins obtained after adding SIPO and PISO shift

registers are as shown below in the table 2.

In this step the .tdf file is uploaded into the compiler

using the following command:Source -echo rs_encode.tdf file is used to get the Input

arrangement of I/O cells. It contains pin and port

information and also contains information regarding

all the pads which are placed on the four sides of the

design ie. On the right, left , top and bottom.

Table 2 Total Number of I/O Pins in Chip Level

Implementation

After reading the .tdf file next step is Floor Planning.

Floorplan is carried out which includes the following

steps: Floor plan initialization

Creating power and ground rails

Pre routing Standard cell

After Floor Planning next step is Placement, during

Placement the two more files are created in the

synthesis process.

Proceedings of IRF International Conference, Chennai, India, 20th April. 2014, ISBN: 978-93-84209-07-0

124

Full Chip Level Implementation of Reed Solomon Encoder

They are

SDC Synopsys Design Constraint read_sdc

./<path/filename.sdc>

DEF Design Exchange Format read_def

./<path/filename.def>

extraction, optimization, and hold-time violation

fixing on the design. The following figure 7 shows the

CTS summary report after applying clock_opt

constraint.

Once the SDC and DEF file has been read, the macros

and standard cells are added into the design.

The following figure 5 shows the placement of macro

and standard cells.

Fig 7 CTS Summary Report

The following figure 8 shows the clock signals in the

design after CTS.

Fig 5 Placement of Macro and Standard cells

Next step after Placement is Clock Tree

Synthesis(CTS)

CTS is the process of distributing clock signals to

clock pins based on physical/layout information.. The

following figure 6 shows the clock signals in the

design before CTS.

Fig 8 Clock signals in the design after CTS

After CTS, the next step is Routing.

Routing is the physical realization of all those

interconnects between pins which are connected by an

electrical circuit.

The constraint Route_opt is used to do routing

optimization for the design. The following figure 9

shows the Routing Summary report after applying the

command route_opt.

Fig 6 Clock signals in the design before CTS

The constraint Clock_opt is used during CTS, which

performs clock tree synthesis, routing of clock nets,

Proceedings of IRF International Conference, Chennai, India, 20th April. 2014, ISBN: 978-93-84209-07-0

125

Full Chip Level Implementation of Reed Solomon Encoder

after adding the I/O, VSS and VDD pads in to the

design).

Table 4 Comparison between Area, Timing and Power

Before

After

Fig 9 Routing Report

Route optimization can be done by reducing wire

length and number of vias, and also by removing

unnecessary jogs. The following figure 10 shows the

final routed design.

Area

134181.71

9965.160037

Timing

0.74

0.00(Met)

Power

12.5113mW

2.338786mW

CONCLUSION

In this paper Full Chip level Implementation of Reed

Solomon Encoder has been carried out. During the

design implementation SIPO and PISO shift registers

are added in order to optimize the area , VDD and

VSS pads are also added in to the design. The timing,

area and the power values which are obtained during

Synthesis are as follows:= Timing = 0.00(Met),

Area=9965.160037 and Power=2.338786 Mw

respectively and the physical design steps such as

Floor Planning, Placement, CTS, Routing and

Verification.are carried out in the design.

Fig 10 Final Routed Design

REFERENCES

After Routing, Physical Verification is carried out and

which checks the correctness of the layout design.

VI. POST LAYOUT TIMING CHECK

In Post layout timing, it is necessary to carry out the

timing check (delay value) in order to meet the timing

specifications. Along with timing it is also mandatory

to carry out the power and area report checks on the

design in order to meet the given specifications. The

following table 4 shows the comparison between

timing, area and the power values which are obtained

during the synthesis process of the design (before and

[1]

Sait, S.M., and Youssef, H. (1995) VLSI Physical Design

Automation Theory and Practice. 1st edition, IEEE Press

[2]

Naveed A. Sherwani (2005) Algorithms for VLSI Physical

Design Automation: 1st edition, Springer

[3]

Khosrow Golshan, (2007) Physical Design Essentials- An

ASIC Design Implementation Perspective:1st edition,

Springer

[4]

Smith. (2008) Application Specific Integrated Circuit 2nd

edition, Pearson Education.

[5]

T. Chan, J. Cong, J. Shinnerl, K. Sze, and M. Xie. mPL6

(2006) Enhanced multilevel mixed-size placement

[6]

H. Ho, A. B. Kahng, S. Reda, and Q. Wang (2005) Power

aware placement.

Proceedings of IRF International Conference, Chennai, India, 20th April. 2014, ISBN: 978-93-84209-07-0

126

You might also like

- Lab Exercise #1: Introduction To The Cypress Fm4 Board and Fm4 Starter KitDocument12 pagesLab Exercise #1: Introduction To The Cypress Fm4 Board and Fm4 Starter KitAhmed HamoudaNo ratings yet

- Computer Interface Trainer (MDA-Win8086) - ProjectDocument77 pagesComputer Interface Trainer (MDA-Win8086) - Projectranahamid00783% (12)

- 70 742 Microsoft Identity With Windows Server 2016Document9 pages70 742 Microsoft Identity With Windows Server 2016NehaNo ratings yet

- EE8681 Lab ManualDocument110 pagesEE8681 Lab ManualVasunthara DNo ratings yet

- Link Budget Analysis Guide: November 21, 2014Document19 pagesLink Budget Analysis Guide: November 21, 2014Анатолий МаловNo ratings yet

- PIC12F629/675/PIC16F630/676Document24 pagesPIC12F629/675/PIC16F630/676Romel Ranin CalangNo ratings yet

- Training ReportDocument18 pagesTraining Reportpiyushji125No ratings yet

- Analog To Digital Converter: Vitrax Plus ControllerDocument13 pagesAnalog To Digital Converter: Vitrax Plus Controlleries837No ratings yet

- Question Bank-Microprocessor and ApplicaionDocument38 pagesQuestion Bank-Microprocessor and Applicaionchandrasekar100% (5)

- 16f8x Serial ProgDocument16 pages16f8x Serial ProgIgnacio MartiNo ratings yet

- RTL2GDSFLOWDocument23 pagesRTL2GDSFLOWAbhishek Gupta0% (1)

- BME 438 Digital Logic Design and Computer Architecture LabDocument73 pagesBME 438 Digital Logic Design and Computer Architecture LabHafiz Muhammad Ahmad RazaNo ratings yet

- Application SSC02 eDocument4 pagesApplication SSC02 eDragosFlorinLismanNo ratings yet

- Mbe Fix32Document5 pagesMbe Fix32Cristina MonteiroNo ratings yet

- Introduction To Chapter 7: Ronald Tocci/Neal Widmer/Gregory MossDocument37 pagesIntroduction To Chapter 7: Ronald Tocci/Neal Widmer/Gregory MossAmmar FarooqNo ratings yet

- cs2304 System Software 2 Marks and 16 Marks With AnswerDocument18 pagescs2304 System Software 2 Marks and 16 Marks With Answermanojkumar024No ratings yet

- En 25 F 80Document33 pagesEn 25 F 80mactocheNo ratings yet

- Csc343 LAB Register File: ObjectiveDocument11 pagesCsc343 LAB Register File: ObjectiveBharavi K SNo ratings yet

- 2 Marks With AnswersDocument14 pages2 Marks With Answersprisci_durai83% (6)

- Discontinued: Synchronous FIFO 5.0Document10 pagesDiscontinued: Synchronous FIFO 5.0Prathap NsNo ratings yet

- IMA ADPCM EncDec Core SpecificationsDocument11 pagesIMA ADPCM EncDec Core SpecificationsMaria MafteiNo ratings yet

- 2 Marks Que &ansDocument30 pages2 Marks Que &ansKanthimathi SureshNo ratings yet

- PDF 2Document13 pagesPDF 2Nivedita Acharyya 2035No ratings yet

- 6713 User ManualDocument92 pages6713 User Manualsningle100% (1)

- VBMB 15 (New)Document46 pagesVBMB 15 (New)anand_duraiswamyNo ratings yet

- An, Improved Successive-Approximation Register Design For Use in A/D ConvertersDocument5 pagesAn, Improved Successive-Approximation Register Design For Use in A/D ConvertersOmer KhanNo ratings yet

- Advanced Topics: 17.1 Hardware Control Using I/O PortsDocument34 pagesAdvanced Topics: 17.1 Hardware Control Using I/O Portsbarbarossa17No ratings yet

- Embed Lab9Document10 pagesEmbed Lab9amitpanvekarNo ratings yet

- Compass OverviewDocument44 pagesCompass OverviewjersonNo ratings yet

- Design and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformDocument6 pagesDesign and Implementation of Digital IIR & FIR Filters On DSK6713 Using CC STUDIOV6.1 PlatformIheb HamedNo ratings yet

- Finnal Diploma ME 111 Control ProjectDocument18 pagesFinnal Diploma ME 111 Control ProjectSharif AwadNo ratings yet

- This Set of 8051 MicroDocument21 pagesThis Set of 8051 MicroSonaliNo ratings yet

- Flash ADC Design in ElectricDocument22 pagesFlash ADC Design in ElectricNagaraj HegdeNo ratings yet

- Keypad Encoder Approval ReportDocument2 pagesKeypad Encoder Approval ReportMuzammil MetkarNo ratings yet

- Lab6 LCDDocument19 pagesLab6 LCDPatipan Jariyapum100% (4)

- Sim RimDocument13 pagesSim RimKalai VaniNo ratings yet

- 8085 Microprocessor UNIT 4Document14 pages8085 Microprocessor UNIT 4Er SarbeshNo ratings yet

- Interfacing The ADS7881 To The TMS320C6713 DSP: Application ReportDocument14 pagesInterfacing The ADS7881 To The TMS320C6713 DSP: Application ReportSashikanth BethaNo ratings yet

- AnnaDocument73 pagesAnnaDriti DasNo ratings yet

- Week 3 - Four Instruction CPUDocument8 pagesWeek 3 - Four Instruction CPUGame AccountNo ratings yet

- VHDL Implementation of BIST Technique in UART DesignDocument5 pagesVHDL Implementation of BIST Technique in UART DesignRakesh GeorgeNo ratings yet

- Traffic Light Controller Using VHDLDocument6 pagesTraffic Light Controller Using VHDLAbdoulrazakNo ratings yet

- PIC12F508/509: Memory Programming SpecificationDocument20 pagesPIC12F508/509: Memory Programming SpecificationMartin CépedaNo ratings yet

- Chapter 16 - DSPDocument58 pagesChapter 16 - DSPMaira HaiderNo ratings yet

- Laboratory 5 - ADC ManualDocument18 pagesLaboratory 5 - ADC ManualSravan KumarNo ratings yet

- Emerson DCS PresentationDocument25 pagesEmerson DCS Presentationruchikaporwal2018No ratings yet

- University Solved Answers Unit 1 SS (System Software Notes)Document12 pagesUniversity Solved Answers Unit 1 SS (System Software Notes)Vaishnavi Rave100% (1)

- 8085 PDocument31 pages8085 PAnish ChibNo ratings yet

- Design and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolDocument10 pagesDesign and Performance Analysis of 8-Bit RISC Processor Using Xilinx & Microwind ToolRakeshconclaveNo ratings yet

- Microprocessors and Assembly Language EC4121: Lecture 1: Introduction By: Mohamed Elnourani 0911471315Document27 pagesMicroprocessors and Assembly Language EC4121: Lecture 1: Introduction By: Mohamed Elnourani 0911471315divine serpentNo ratings yet

- Xilinx Answer 73361 PCIe Link Training Debug Guide For US and US PlusDocument54 pagesXilinx Answer 73361 PCIe Link Training Debug Guide For US and US PlusEvamGilotraNo ratings yet

- 16 F 506Document22 pages16 F 506Kavin SengodanNo ratings yet

- Software Stage EDocument19 pagesSoftware Stage ETim TaylorNo ratings yet

- Physical Design Implementation of 16 Bit Risc ProcessorDocument7 pagesPhysical Design Implementation of 16 Bit Risc Processorashish jhaNo ratings yet

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkFrom EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkNo ratings yet

- Embedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesFrom EverandEmbedded Software Design and Programming of Multiprocessor System-on-Chip: Simulink and System C Case StudiesNo ratings yet

- Establishing Qor Flow On Emerging Technology Nodes: Pramod Sripathi Sreenivasa Reddy Kasireddy Raj Sekhar BochkarDocument33 pagesEstablishing Qor Flow On Emerging Technology Nodes: Pramod Sripathi Sreenivasa Reddy Kasireddy Raj Sekhar BochkarSumanth VarmaNo ratings yet

- Eeiol 2009mar26 Eda Ta 01Document2 pagesEeiol 2009mar26 Eda Ta 01Sumanth VarmaNo ratings yet

- An Alternative Approach To Buffer Insertion For Delay and Power Reduction in VLSI InterconnectsDocument6 pagesAn Alternative Approach To Buffer Insertion For Delay and Power Reduction in VLSI InterconnectsSumanth VarmaNo ratings yet

- Synthesis Assignment - 1Document3 pagesSynthesis Assignment - 1Sumanth VarmaNo ratings yet

- Implementing Double Data Rate I/O Signaling in Stratix & Stratix GX DevicesDocument22 pagesImplementing Double Data Rate I/O Signaling in Stratix & Stratix GX DevicesSumanth VarmaNo ratings yet

- Metastability and Synchronizers - IEEEDToct2011 PDFDocument13 pagesMetastability and Synchronizers - IEEEDToct2011 PDFSumanth VarmaNo ratings yet

- 5 AdderDocument35 pages5 AdderSumanth VarmaNo ratings yet

- Low Power Design Methodologies and FlowsDocument52 pagesLow Power Design Methodologies and FlowsSumanth VarmaNo ratings yet

- LEC Jumpstart Training OverviewDocument37 pagesLEC Jumpstart Training OverviewSumanth VarmaNo ratings yet

- Introduction To Cmos Vlsi Design: Nonideal TransistorsDocument30 pagesIntroduction To Cmos Vlsi Design: Nonideal TransistorsSumanth VarmaNo ratings yet

- Body Bias Scaling For Globalfoundries 22fdx Technology New Dimension To Explore The DesignDocument28 pagesBody Bias Scaling For Globalfoundries 22fdx Technology New Dimension To Explore The DesignSumanth VarmaNo ratings yet

- Full-Scan: (Lecture 19alt in The Alternative Sequence)Document22 pagesFull-Scan: (Lecture 19alt in The Alternative Sequence)Sumanth VarmaNo ratings yet

- Understanding and Validating The Detailed Power Report Generated by The Report - Instance - Power Voltus CommandDocument6 pagesUnderstanding and Validating The Detailed Power Report Generated by The Report - Instance - Power Voltus CommandSumanth VarmaNo ratings yet

- How Can I Easily Report Paths Which Cross Clock Domains PDFDocument3 pagesHow Can I Easily Report Paths Which Cross Clock Domains PDFSumanth VarmaNo ratings yet

- Logical Correlation Analysis On Victim and Aggressor Pairs With The Same SenseDocument3 pagesLogical Correlation Analysis On Victim and Aggressor Pairs With The Same SenseSumanth VarmaNo ratings yet

- Magic Blue Smoke Low Power General PDFDocument6 pagesMagic Blue Smoke Low Power General PDFSumanth VarmaNo ratings yet

- Magic Blue Smoke Low Power General PDFDocument6 pagesMagic Blue Smoke Low Power General PDFSumanth VarmaNo ratings yet

- Features: Frequency DividerDocument6 pagesFeatures: Frequency DividerSumanth VarmaNo ratings yet

- 3 GPPDocument95 pages3 GPPdezzgsNo ratings yet

- Prototypes For RPG IV ApisDocument10 pagesPrototypes For RPG IV Apisrachmat99No ratings yet

- FTDI Chip: USB SolutionsDocument20 pagesFTDI Chip: USB SolutionsPaloma Sousa100% (1)

- 11 - K8s On AWS ChecklistDocument8 pages11 - K8s On AWS Checklistmacod15739No ratings yet

- Lab Manual - RTOS AchitectureDocument6 pagesLab Manual - RTOS Achitectureritika jaiswalNo ratings yet

- Combiprobe UserDocument19 pagesCombiprobe Usercarver_uaNo ratings yet

- Archetype Write-Up: ImpacketDocument17 pagesArchetype Write-Up: ImpacketJiohnNo ratings yet

- Advance of Festivals in KarnatakaDocument13 pagesAdvance of Festivals in KarnatakaRhiteshNo ratings yet

- DNS, SNMP, Web ServiceDocument25 pagesDNS, SNMP, Web ServiceJayaprasannaNo ratings yet

- 4D HyperV and Exchange 2016 Powershell Cheat SheetDocument2 pages4D HyperV and Exchange 2016 Powershell Cheat Sheetm00anj00No ratings yet

- Network Access Control: Software and HarwareDocument2 pagesNetwork Access Control: Software and Harwareanurag_0290100% (1)

- V-1200HDR / V-1200HD RCS Remote Control Guide: Ver. 1.4 and LaterDocument94 pagesV-1200HDR / V-1200HD RCS Remote Control Guide: Ver. 1.4 and LateragomezagNo ratings yet

- 3 Freescale ToDocument34 pages3 Freescale ToAmine FouratiNo ratings yet

- User Guide: 5000B Data Acquisition and Logging Unit Versions 3.4 and Later HA027566/11 September 2012Document160 pagesUser Guide: 5000B Data Acquisition and Logging Unit Versions 3.4 and Later HA027566/11 September 2012Ricardo Cesar SantanaNo ratings yet

- Log Cat 1687020337817Document540 pagesLog Cat 1687020337817story waNo ratings yet

- Meb9400 OmDocument326 pagesMeb9400 Ommax51sNo ratings yet

- USB Made EasyDocument141 pagesUSB Made EasyAndres Bruno Saravia100% (1)

- Unix CommandsDocument20 pagesUnix CommandsdineshkandeNo ratings yet

- Case Study Tcp-IpDocument27 pagesCase Study Tcp-IpsarathkumarNo ratings yet

- Tcpreplay-Edit Man PageDocument22 pagesTcpreplay-Edit Man PageEduardo FloresNo ratings yet

- Gravostyle 8 Installation GuideDocument22 pagesGravostyle 8 Installation GuideIstvan GazdagNo ratings yet

- 7.7.2.2 Common Problems and Solutions For LaptopsDocument3 pages7.7.2.2 Common Problems and Solutions For LaptopsDickya Hidayah putra100% (1)

- PSPC Notes - Unit - 1Document22 pagesPSPC Notes - Unit - 1Samba SivaNo ratings yet

- AWS Security Checklist PDFDocument3 pagesAWS Security Checklist PDFAdy GokaNo ratings yet

- Computer - 2Document18 pagesComputer - 2aksahu01234No ratings yet

- HCIE-Datacom V1.0 Exam OutlineDocument7 pagesHCIE-Datacom V1.0 Exam Outlineabera alemayehuNo ratings yet

- Topic02 Data AcquisitionDocument26 pagesTopic02 Data AcquisitionHappy Plants BDNo ratings yet

- H801MCUD1 Board DatasheetDocument1 pageH801MCUD1 Board DatasheetPablo AntonieNo ratings yet

- Driver Settings - Color Image Quality Ps v171020Document3 pagesDriver Settings - Color Image Quality Ps v171020nourmlk1859No ratings yet