Professional Documents

Culture Documents

Block Diagram of 555 Timer IC

Block Diagram of 555 Timer IC

Uploaded by

SreedaharCopyright:

Available Formats

You might also like

- Burglar Alarm ProjectDocument4 pagesBurglar Alarm ProjectAvik PathakNo ratings yet

- Block Diagram of 555 Timer ICDocument1 pageBlock Diagram of 555 Timer ICSreedaharNo ratings yet

- Operation 555 Timer/OscillatorDocument7 pagesOperation 555 Timer/OscillatoryuvakiraniNo ratings yet

- 555 Timer Integrated CircuitDocument8 pages555 Timer Integrated CircuitTalha WaqarNo ratings yet

- IC 555 TimerDocument6 pagesIC 555 Timeraditya pandeyNo ratings yet

- Opamp Applicationpart30Document31 pagesOpamp Applicationpart30KUNTALA DASNo ratings yet

- The Important Features of The 555 Timer AreDocument7 pagesThe Important Features of The 555 Timer ArePathella SudhakarNo ratings yet

- SE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orDocument12 pagesSE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orEFraim Manzano FranciscoNo ratings yet

- List The Features of 555 TimersDocument3 pagesList The Features of 555 TimersDivyesh DivakarNo ratings yet

- 555 Timer IC: The Important Features of The 555 Timer AreDocument5 pages555 Timer IC: The Important Features of The 555 Timer AreChara GalaNo ratings yet

- 555 TimerDocument3 pages555 TimerchandrakanthNo ratings yet

- 6.1 IC555 TIMER: Circuit ComponentsDocument8 pages6.1 IC555 TIMER: Circuit ComponentsManish PradhanNo ratings yet

- Timer 555 - ManualDocument20 pagesTimer 555 - ManualXen XeonNo ratings yet

- Report IC 555 TimerDocument17 pagesReport IC 555 TimerSantosh YadavNo ratings yet

- 555 TimerDocument12 pages555 Timerlalaine reginaldoNo ratings yet

- 555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetDocument13 pages555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetΔημητριος ΣταθηςNo ratings yet

- Operational AmplifierDocument10 pagesOperational AmplifierSalman AliNo ratings yet

- LIC Mod 2Document15 pagesLIC Mod 2Sona PrakashNo ratings yet

- Bistable MultivibratorDocument28 pagesBistable MultivibratorMansi JaisinghNo ratings yet

- 4 555timer 120916082406 Phpapp02Document14 pages4 555timer 120916082406 Phpapp02sunil1237No ratings yet

- IC555 TimerDocument8 pagesIC555 TimerRaflysyah PutraNo ratings yet

- 555 Timer 2015Document29 pages555 Timer 2015Ansor NtNo ratings yet

- How Does A 555 Timer WorkDocument3 pagesHow Does A 555 Timer WorkTonderayi MangaraNo ratings yet

- 555-Timer Class NotesDocument1 page555-Timer Class NotesPraveen KumarNo ratings yet

- Ic555Document2 pagesIc555NavJot SinghNo ratings yet

- 555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITDocument21 pages555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITRupsa SahaNo ratings yet

- 555 Timer IC Working PrincipalDocument6 pages555 Timer IC Working PrincipalApoorv GargNo ratings yet

- Ic555 TimerDocument5 pagesIc555 Timerps1976No ratings yet

- 1 Ic 555Document6 pages1 Ic 555Harish PatilNo ratings yet

- 3.1555 TIMER:: Schematic SymbolDocument10 pages3.1555 TIMER:: Schematic SymbolnagpradasNo ratings yet

- The Pinouts For The 8 Pin DIP Package Are As FollowsDocument5 pagesThe Pinouts For The 8 Pin DIP Package Are As FollowsVerstummeltNo ratings yet

- N555e Intergrated CircuitDocument6 pagesN555e Intergrated CircuitGeorge Boman SethNo ratings yet

- KDAS OPAMP APPLICATIONsDocument24 pagesKDAS OPAMP APPLICATIONsKingshuk GuptaNo ratings yet

- Integrated Circuits:) of Flip-Flop ThroughDocument13 pagesIntegrated Circuits:) of Flip-Flop ThroughShubh MishraNo ratings yet

- A Simple PWM Circuit Based On The 555 TimerDocument4 pagesA Simple PWM Circuit Based On The 555 Timermansi_angelNo ratings yet

- Important Characterstics of 555 Timer IC: Circuits Based On 5555 ICDocument6 pagesImportant Characterstics of 555 Timer IC: Circuits Based On 5555 ICManohar PotnuruNo ratings yet

- IC555 Tutorial AvinashJainDocument4 pagesIC555 Tutorial AvinashJainAvinash Jain100% (1)

- It May Thus Terminate An Output Pulse PrematurelyDocument2 pagesIt May Thus Terminate An Output Pulse Prematurelyogeh jeffrey jeremiahNo ratings yet

- 555 TimerDocument28 pages555 TimerNisha Kotyan G RNo ratings yet

- E.C.E - 210Document18 pagesE.C.E - 210xxkkassNo ratings yet

- Tda 4700Document21 pagesTda 4700lrohneNo ratings yet

- Ic Applications Lab NewDocument12 pagesIc Applications Lab NewSandy RonaldoNo ratings yet

- 555 Timer ExplainedDocument27 pages555 Timer ExplainedThe Lost WolfNo ratings yet

- Dsa 265104Document20 pagesDsa 265104foxx034No ratings yet

- A Simple PWM Circuit Based On The 555 TimerDocument5 pagesA Simple PWM Circuit Based On The 555 TimerAmit B KolekarNo ratings yet

- Abhijit H Jadhav (Roll No 02) (Roll No 58)Document15 pagesAbhijit H Jadhav (Roll No 02) (Roll No 58)ksooryakrishna1No ratings yet

- 555 PDFDocument14 pages555 PDFvpsampathNo ratings yet

- 555 Timers Modi12Document21 pages555 Timers Modi12jewixe8466No ratings yet

- 555 Timer Lecture and Lab4Document3 pages555 Timer Lecture and Lab4litogabo9No ratings yet

- Bab 4 - Timer 555 (Update)Document31 pagesBab 4 - Timer 555 (Update)NUR FATHIAH BINTI ABDUL HALIM STUDENTNo ratings yet

- Lic Eec-501 Notes Unit5 Iftm UniversityDocument14 pagesLic Eec-501 Notes Unit5 Iftm UniversitySougata GhoshNo ratings yet

- 555 TimerDocument14 pages555 TimernathmanojNo ratings yet

- Integratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVDocument5 pagesIntegratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVYogeshwaranNo ratings yet

- 555 Timer MonostableDocument3 pages555 Timer MonostablenevillejoseNo ratings yet

- 555 Timer CKTDocument1 page555 Timer CKTMamoon BarbhuyanNo ratings yet

- The 555 Timer: Monostable Bistable AstableDocument10 pagesThe 555 Timer: Monostable Bistable AstableSrikanth ThulluriNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Cordova Closed BuildDocument14 pagesCordova Closed BuildSreedaharNo ratings yet

- NCERT Book English Snapshots Class XIDocument77 pagesNCERT Book English Snapshots Class XInikhilam.com100% (8)

- All India Radio (Akashavani - Ahmedabad)Document11 pagesAll India Radio (Akashavani - Ahmedabad)SreedaharNo ratings yet

- Block Diagram of 555 Timer ICDocument1 pageBlock Diagram of 555 Timer ICSreedaharNo ratings yet

- Femtocell SolutionDocument2 pagesFemtocell SolutionSreedaharNo ratings yet

Block Diagram of 555 Timer IC

Block Diagram of 555 Timer IC

Uploaded by

SreedaharOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Block Diagram of 555 Timer IC

Block Diagram of 555 Timer IC

Uploaded by

SreedaharCopyright:

Available Formats

Block Diagram of 555 timer IC:

555 timer Block Diagram

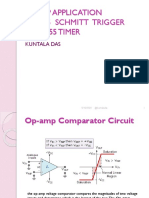

Comparator 1 has a threshold input (pin 6) and a control input (pin 5). In most applications, the control input is not

used, so that the control voltage equals +2/3 VCC. Output of this comparator is applied to set (S) input of the flip-flop.

Whenever the threshold voltage exceeds the control voltage, comparator 1 will set the flip-flop and its output is high.

A high output from the flip-flop saturates the discharge transistor and discharge the capacitor connected externally to

pin 7. The complementary signal out of the flip-flop goes to pin 3, the output. The output available at pin 3 is

low. These conditions will prevail until comparator 2 triggers the flip-flop. Even if the voltage at the threshold input

falls below 2/3 VCC, that is comparator 1 cannot cause the flip-flop to change again. It means that the comparator 1

can only force the flip-flop’s output high.

To change the output of flip-flop to low, the voltage at the trigger input must fall below + 1/3 Vcc. When this occurs,

comparator 2 triggers the flip-flop, forcing its output low. The low output from the flip-flop turns the discharge

transistor off and forces the power amplifier to output a high. These conditions will continue independent of the

voltage on the trigger input. Comparator 2 can only cause the flip-flop to output low.

From the above discussion it is concluded that for the having low output from the timer 555, the voltage on the

threshold input must exceed the control voltage or + 2/3 VCC. They also turn the discharge transistor on. To force the

output from the timer high, the voltage on the trigger input must drop below +1/3 VCC. This also turns the discharge

transistor off.

A voltage may be applied to the control input to change the levels at which the switching occurs. When not in use, a

0.01 nano Farad capacitor should be connected between pin 5 and ground to prevent noise coupled onto this pin

from causing false triggering.

Connecting the reset (pin 4) to a logic low will place a high on the output of flip-flop. The discharge transistor will go

on and the power amplifier will output a low. This condition will continue until reset is taken high. This allows

synchronization or resetting of the circuit’s operation. When not in use, reset should be tied to +VCC.

You might also like

- Burglar Alarm ProjectDocument4 pagesBurglar Alarm ProjectAvik PathakNo ratings yet

- Block Diagram of 555 Timer ICDocument1 pageBlock Diagram of 555 Timer ICSreedaharNo ratings yet

- Operation 555 Timer/OscillatorDocument7 pagesOperation 555 Timer/OscillatoryuvakiraniNo ratings yet

- 555 Timer Integrated CircuitDocument8 pages555 Timer Integrated CircuitTalha WaqarNo ratings yet

- IC 555 TimerDocument6 pagesIC 555 Timeraditya pandeyNo ratings yet

- Opamp Applicationpart30Document31 pagesOpamp Applicationpart30KUNTALA DASNo ratings yet

- The Important Features of The 555 Timer AreDocument7 pagesThe Important Features of The 555 Timer ArePathella SudhakarNo ratings yet

- SE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orDocument12 pagesSE/NE 555 Timer. It Is Basically A Monolithic Timing Circuit That Produces Accurate and Highly Stable Time Delays orEFraim Manzano FranciscoNo ratings yet

- List The Features of 555 TimersDocument3 pagesList The Features of 555 TimersDivyesh DivakarNo ratings yet

- 555 Timer IC: The Important Features of The 555 Timer AreDocument5 pages555 Timer IC: The Important Features of The 555 Timer AreChara GalaNo ratings yet

- 555 TimerDocument3 pages555 TimerchandrakanthNo ratings yet

- 6.1 IC555 TIMER: Circuit ComponentsDocument8 pages6.1 IC555 TIMER: Circuit ComponentsManish PradhanNo ratings yet

- Timer 555 - ManualDocument20 pagesTimer 555 - ManualXen XeonNo ratings yet

- Report IC 555 TimerDocument17 pagesReport IC 555 TimerSantosh YadavNo ratings yet

- 555 TimerDocument12 pages555 Timerlalaine reginaldoNo ratings yet

- 555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetDocument13 pages555 Timer IC-Block Diagram-Working-Pin Out Configuration-Data SheetΔημητριος ΣταθηςNo ratings yet

- Operational AmplifierDocument10 pagesOperational AmplifierSalman AliNo ratings yet

- LIC Mod 2Document15 pagesLIC Mod 2Sona PrakashNo ratings yet

- Bistable MultivibratorDocument28 pagesBistable MultivibratorMansi JaisinghNo ratings yet

- 4 555timer 120916082406 Phpapp02Document14 pages4 555timer 120916082406 Phpapp02sunil1237No ratings yet

- IC555 TimerDocument8 pagesIC555 TimerRaflysyah PutraNo ratings yet

- 555 Timer 2015Document29 pages555 Timer 2015Ansor NtNo ratings yet

- How Does A 555 Timer WorkDocument3 pagesHow Does A 555 Timer WorkTonderayi MangaraNo ratings yet

- 555-Timer Class NotesDocument1 page555-Timer Class NotesPraveen KumarNo ratings yet

- Ic555Document2 pagesIc555NavJot SinghNo ratings yet

- 555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITDocument21 pages555 Timer: by D.V.Kamat, Faculty Department of E&C Engg., MITRupsa SahaNo ratings yet

- 555 Timer IC Working PrincipalDocument6 pages555 Timer IC Working PrincipalApoorv GargNo ratings yet

- Ic555 TimerDocument5 pagesIc555 Timerps1976No ratings yet

- 1 Ic 555Document6 pages1 Ic 555Harish PatilNo ratings yet

- 3.1555 TIMER:: Schematic SymbolDocument10 pages3.1555 TIMER:: Schematic SymbolnagpradasNo ratings yet

- The Pinouts For The 8 Pin DIP Package Are As FollowsDocument5 pagesThe Pinouts For The 8 Pin DIP Package Are As FollowsVerstummeltNo ratings yet

- N555e Intergrated CircuitDocument6 pagesN555e Intergrated CircuitGeorge Boman SethNo ratings yet

- KDAS OPAMP APPLICATIONsDocument24 pagesKDAS OPAMP APPLICATIONsKingshuk GuptaNo ratings yet

- Integrated Circuits:) of Flip-Flop ThroughDocument13 pagesIntegrated Circuits:) of Flip-Flop ThroughShubh MishraNo ratings yet

- A Simple PWM Circuit Based On The 555 TimerDocument4 pagesA Simple PWM Circuit Based On The 555 Timermansi_angelNo ratings yet

- Important Characterstics of 555 Timer IC: Circuits Based On 5555 ICDocument6 pagesImportant Characterstics of 555 Timer IC: Circuits Based On 5555 ICManohar PotnuruNo ratings yet

- IC555 Tutorial AvinashJainDocument4 pagesIC555 Tutorial AvinashJainAvinash Jain100% (1)

- It May Thus Terminate An Output Pulse PrematurelyDocument2 pagesIt May Thus Terminate An Output Pulse Prematurelyogeh jeffrey jeremiahNo ratings yet

- 555 TimerDocument28 pages555 TimerNisha Kotyan G RNo ratings yet

- E.C.E - 210Document18 pagesE.C.E - 210xxkkassNo ratings yet

- Tda 4700Document21 pagesTda 4700lrohneNo ratings yet

- Ic Applications Lab NewDocument12 pagesIc Applications Lab NewSandy RonaldoNo ratings yet

- 555 Timer ExplainedDocument27 pages555 Timer ExplainedThe Lost WolfNo ratings yet

- Dsa 265104Document20 pagesDsa 265104foxx034No ratings yet

- A Simple PWM Circuit Based On The 555 TimerDocument5 pagesA Simple PWM Circuit Based On The 555 TimerAmit B KolekarNo ratings yet

- Abhijit H Jadhav (Roll No 02) (Roll No 58)Document15 pagesAbhijit H Jadhav (Roll No 02) (Roll No 58)ksooryakrishna1No ratings yet

- 555 PDFDocument14 pages555 PDFvpsampathNo ratings yet

- 555 Timers Modi12Document21 pages555 Timers Modi12jewixe8466No ratings yet

- 555 Timer Lecture and Lab4Document3 pages555 Timer Lecture and Lab4litogabo9No ratings yet

- Bab 4 - Timer 555 (Update)Document31 pagesBab 4 - Timer 555 (Update)NUR FATHIAH BINTI ABDUL HALIM STUDENTNo ratings yet

- Lic Eec-501 Notes Unit5 Iftm UniversityDocument14 pagesLic Eec-501 Notes Unit5 Iftm UniversitySougata GhoshNo ratings yet

- 555 TimerDocument14 pages555 TimernathmanojNo ratings yet

- Integratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVDocument5 pagesIntegratedelectronics (Unit2) 555 TIMER ASTABLE MONOSTABLE MVYogeshwaranNo ratings yet

- 555 Timer MonostableDocument3 pages555 Timer MonostablenevillejoseNo ratings yet

- 555 Timer CKTDocument1 page555 Timer CKTMamoon BarbhuyanNo ratings yet

- The 555 Timer: Monostable Bistable AstableDocument10 pagesThe 555 Timer: Monostable Bistable AstableSrikanth ThulluriNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Cordova Closed BuildDocument14 pagesCordova Closed BuildSreedaharNo ratings yet

- NCERT Book English Snapshots Class XIDocument77 pagesNCERT Book English Snapshots Class XInikhilam.com100% (8)

- All India Radio (Akashavani - Ahmedabad)Document11 pagesAll India Radio (Akashavani - Ahmedabad)SreedaharNo ratings yet

- Block Diagram of 555 Timer ICDocument1 pageBlock Diagram of 555 Timer ICSreedaharNo ratings yet

- Femtocell SolutionDocument2 pagesFemtocell SolutionSreedaharNo ratings yet