Professional Documents

Culture Documents

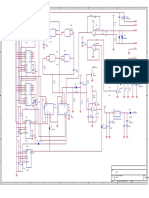

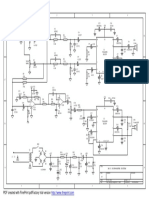

Atmega128 Board Expansion

Atmega128 Board Expansion

Uploaded by

one777Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Atmega128 Board Expansion

Atmega128 Board Expansion

Uploaded by

one777Copyright:

Available Formats

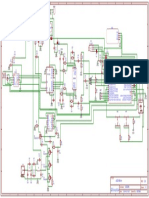

1 2 3 4 5 6 7 8

VCC5V

VCC33

C12 C13

100n 10u/16V

C3 C4 C5 C6 C19 VCC33 VCC5V

U2 100n 100n 100n 100n 10u/16V

VCC5V J4

6 28

PB3/MISO SO Vdd

7 25 1

PB2/MOSI SI Vddosc L1

8 20 2

PB1/SCK SCK Vddpll Ferrite Bead P1

19 3

Vddrx R4 270R 10k

A 4 15 4 A

PD0/INT0 #INT Vddtx PB7

5

CN1 PB6

5 27 1 6

PD1/INT1 #WOL LEDA R5 270R P1 PB5

26 7

LEDB AD0

9 7 8

PB4 #CS P7 AD1

10 9

#Reset AD2

17 2 10

R2 TPOUT+ P2 AD3

16 C10 TX (1:1) 11

VCC33 TPOUT- R6 50R AD4

12

10k AD5

13 3 RX (1:1) 13

PD2 TPIN+ R7 50R P3 AD6

12 100n VCC5V 14

R3 TPIN- AD7

8

VCC33 TP1 P8

LCD

10k R14 10R J1

1 6

Vcap P6

C7 C9 LED Backlight

10u/16V C11

R8 50R

3 22 4 VCC33

CLKout Vssosc P4

18p 23 21

OSC1 Vsspll R9 50R J2

X1 24 18 100n

OSC2 Vsstx

25MHz 11 L1 C20 1

Vssrx L1 PB7

C8 14 2 L2 Green 100n 2

Rbias Vss L2

U8 3

PB6

ENC28J60 L3 1 14 4

L3 PB4 OE1 VCC

18p L4 Yellow 4 5

R1 L4 OE2 PB5

10 6

2k3 OE3

J5 G1 13 7

G1 Frame OE4 PB4

1 G2 VCC5V 8

PB1/SCK G2 R11 180R

2 RJ45 MM-Jack 2 3 9

B PB2/MOSI PB3/MISO A1 Y1 B

3 5 6 10

PB3/MISO PD1/INT1 A2 Y2 R12 180R

4 9 8 11

PB4 PD0/INT0 A3 Y3 PB2/MOSI

5 C14 12 11 12

PD0/INT0 A4 Y4 R13 180R

6 VCC5V VCC33 100n 13

Port Usage: PD1/INT1 PB1/SCK

7 7 14

PD2 External Power GND

8 U3 15

PB0 -> Memory bank selection (128k mode)VCC33 JP2 PB0

9 20 28 74LVT125 16

PB1/SCK -> ENC28J60, pin 8 (SCK) #CS0 CE VCC

10 22 17

PB2/MOSI -> ENC28J60, pin 7 (SI) #RD OE PD3

U1 LM1117-3.3 27 18

PB3/MISO -> ENC28J60, pin 6 (SO) #WR WE

IDC 10-PIN 3 2,4 19

PB4 -> ENC28J60, pin 9 (/CS) IN OUT PD2

10 11 20

PB5 -> LCD (E) ADJ A0 A0 DQ0 AD0

9 12 21

PB6 -> LCD (R/W) A1 A1 DQ1 AD1

C1 C2 8 13 22

PB7 -> LCD (RS) 1 A2 A2 DQ2 AD2

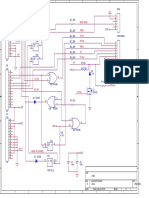

100n 100n 7 15 23

A3 A3 DQ3 AD3

6 16 24

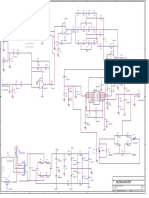

PD0/INT0 -> ENC28J60, pin 4 (/INT) A4 A4 DQ4 AD4

5 17 25

PD1/INT1 -> ENC28J60, pin 5 (/WOL) A5 A5 DQ5 AD5 PD5

4 18 26

PD2 -> ENC28J60, pin 10 (/RESET) A6 A6 DQ6 AD6 PD4

3 19

PD3 A7 A7 DQ7 AD7

25 VCC5V To VFD connector

PD4 A8 A8

24

PD5 #RESET A9 A9

21

A10 A10

23

A11 A11

B1 2 C15

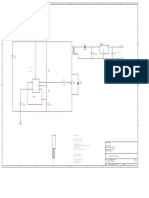

External Power (JP2): A12 A12

Reset 26 100n

A13 A13

1 U5

This one is used when the ethernet-part of the A14 A14

1 20

board is connected via header J5 and the host OE VCC

14 11

system uses 3.3V. The regulator should not be GND ALE LE J3

C used in this case. C

Bank 0 (32k x 8) 2 19 1

AD0 D1 Q1 A0 AD0

3 18 2

AD1 D2 Q2 A1 A8

VCC5V VCC5V VCC5V 4 17 3

AD2 D3 Q3 A2 AD1

5 16 4

AD3 D4 Q4 A3 A9

6 15 5

AD4 D5 Q5 A4 AD2

C18 7 14 6

AD5 D6 Q6 A5 A10

U7 100n C16 8 13 7

AD6 D7 Q7 A6 AD3

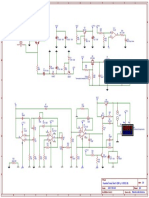

VCC5V 22 32 100n 9 12 8

#E1 Vcc AD7 D8 Q8 A7 A11

14 30 9

VCC E2 AD4

29 U4 10 10

U6C #WR #W GND A12

24 20 28 11

#RD #G #CS1 CE VCC AD5

22 74HC573 12

5 6 #RD OE A13

AY 12 13 27 13

A0 A0 DQ0 AD0 #WR WE AD6

11 14 14

A1 A1 DQ1 AD1 A14

74HC04 10 15 10 11 15

7 A2 A2 DQ2 AD2 A0 A0 DQ0 AD0 AD7

GND 9 17 9 12 #CS1 16

U6D A3 A3 DQ3 AD3 A1 A1 DQ1 AD1 A15

8 18 8 13 17

A4 A4 DQ4 AD4 A2 A2 DQ2 AD2 U6B U6A #WR

7 19 7 15 18

9 8 A5 A5 DQ5 AD5 A3 A3 DQ3 AD3 #RESET

6 20 6 16 19

A6 A6 DQ6 AD6 A4 A4 DQ4 AD4 4 3 2 1 #RD

5 21 5 17 #CS0 A15 20

A7 A7 DQ7 AD7 A5 A5 DQ5 AD5

74HC04 27 4 18 21

A8 A8 A6 A6 DQ6 AD6 ALE

26 3 19 74HC04 74HC04 22

U6E A9 A9 A7 A7 DQ7 AD7

23 25 23

A10 A10 A8 A8 VCC5V PG5

25 24 24

11 10 A11 A11 A9 A9

4 21 VCC5V 25

A12 A12 A10 A10 C17

28 23 26

A13 A13 A11 A11 100n

74HC04 3 2

A14 A14 A12 A12

D U6F 31 26 To Expansion connector D

A15 A15 A13 A13

2 16 1

A16 GND A14 A14 Memory options:

13 12

M68AF127B 14

GND 32k: Use U3 only

Title

74HC04 Bank 1 (32k x 8)

64k: Use U3 and U4 OR U7 (only lower half will be used, ATmega128 board expansion

R10 JP1 don't short JP1)

Size Number Revision

PB0

10k Enable 128k BS 2 x 64k: Use U7 only, short JP1 A3 R1A

Short to use PG5 as bank selector (Use PB0 to select memory page)

Date: 2/5/2008 Sheet of

File: F:\Work\..\AddOn.SchDoc Drawn By:

1 2 3 4 5 6 7 8

You might also like

- Aixun T3aDocument1 pageAixun T3aAndsys Electronic Innovation50% (2)

- Schematic - USDX MICRO v2.6Document1 pageSchematic - USDX MICRO v2.6luistorcatt72100% (1)

- The Fusion Marketing Bible: Fuse Traditional Media, Social Media, & Digital Media to Maximize MarketingFrom EverandThe Fusion Marketing Bible: Fuse Traditional Media, Social Media, & Digital Media to Maximize MarketingRating: 5 out of 5 stars5/5 (2)

- Alphagage + Manual - v5Document80 pagesAlphagage + Manual - v5JC Schwartz100% (2)

- Diagram - Radio & C.B. RadioDocument5 pagesDiagram - Radio & C.B. RadioAlejandro VelezNo ratings yet

- Example Short Circuit Current Faults - Scenario 9Document7 pagesExample Short Circuit Current Faults - Scenario 9PGNo ratings yet

- Schematic1 - Page1Document1 pageSchematic1 - Page1acquybongdemNo ratings yet

- Demi Winner X Ble: Demi Left Demi RightDocument1 pageDemi Winner X Ble: Demi Left Demi RightTu Do100% (2)

- UterrorDocument1 pageUterrordavNo ratings yet

- DiseqC SCHDocument1 pageDiseqC SCHnaseerak100% (2)

- Outseal PLC V5 Darlington PDFDocument1 pageOutseal PLC V5 Darlington PDFLuqman Sp100% (4)

- GSM GPRS GNSS HAT SchematicDocument1 pageGSM GPRS GNSS HAT Schematicforog100% (1)

- Schematic - LMR SDR V 1.5.A - 2021-11-23Document3 pagesSchematic - LMR SDR V 1.5.A - 2021-11-23pajrulnetNo ratings yet

- Schematic - Fuente Lineal de 0 28V y 0 002 3A - Diagrama Esquem Tico - 20190410150121Document1 pageSchematic - Fuente Lineal de 0 28V y 0 002 3A - Diagrama Esquem Tico - 20190410150121Edgar Barrios YucraNo ratings yet

- PIC Micro Project Board PDFDocument1 pagePIC Micro Project Board PDFOkiPetrus Hutauruk LumbanBaringin100% (2)

- PC8 Temperature Controlled Board Schematic Drawing 0986-30-026-00CDocument1 pagePC8 Temperature Controlled Board Schematic Drawing 0986-30-026-00Cmargono akurasiNo ratings yet

- Schematics of CM-108 All PCBDocument1 pageSchematics of CM-108 All PCBRafael OliveiraNo ratings yet

- Tinkerkit: Default Default Default DefaultDocument1 pageTinkerkit: Default Default Default DefaultHajar IkkeNo ratings yet

- TV On DVD-mst720-113Document3 pagesTV On DVD-mst720-113dann2220% (1)

- Clock ModuleDocument1 pageClock Modulespy004No ratings yet

- Laney LA65CDocument2 pagesLaney LA65Craphael12stringsNo ratings yet

- ATMEGA64M1 - CanBoard V1Document1 pageATMEGA64M1 - CanBoard V1Fabian Alfonso100% (1)

- Ups MotherboardDocument5 pagesUps MotherboardMustapha El MaouzouniNo ratings yet

- Clock CR 500WDocument3 pagesClock CR 500Wapi-3697672100% (2)

- Sic Driver Board SchematicDocument1 pageSic Driver Board Schematicluongktdt100% (2)

- Clap CKTDocument2 pagesClap CKTMunavir k100% (1)

- Sheet: Arduino-NanoDocument3 pagesSheet: Arduino-NanoGopakumar KNo ratings yet

- Arduino Isp SchematicDocument1 pageArduino Isp Schematicflo72afNo ratings yet

- REPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877aDocument1 pageREPEATER IDER ISD25xx - Repeater Ider Isd2590 16f877amanuel contrerasNo ratings yet

- 2-CH RS485 HAT SchDocDocument2 pages2-CH RS485 HAT SchDocgino ginelli100% (1)

- Microphone Power Decoupling: Released Under The Creative Commons Attribution Share-Alike 4.0 LicenseDocument1 pageMicrophone Power Decoupling: Released Under The Creative Commons Attribution Share-Alike 4.0 LicenseisubhaNo ratings yet

- Schematic 2.4G Telecontrol BoardDocument1 pageSchematic 2.4G Telecontrol Boardmarod2012.mrNo ratings yet

- Schematic 2.4G Telecontrol Board 2021-07-15Document1 pageSchematic 2.4G Telecontrol Board 2021-07-15Ash VigilNo ratings yet

- PC10Document1 pagePC10margono akurasi100% (2)

- Invertor LCD OZ9601SDocument1 pageInvertor LCD OZ9601SRenatoMaia100% (1)

- Ibanez tk999 UsDocument1 pageIbanez tk999 UsdNo ratings yet

- Mq-Dual SCH v1.6Document3 pagesMq-Dual SCH v1.6Melek UzunlarNo ratings yet

- SilentStepStick-TMC2208 v12Document2 pagesSilentStepStick-TMC2208 v12TizianoNo ratings yet

- PDF Created With Fineprint Pdffactory Trial Version: 5 4 2 1 Tda2030ADocument1 pagePDF Created With Fineprint Pdffactory Trial Version: 5 4 2 1 Tda2030AKamol PlakulNo ratings yet

- Sa2500p Rev09 - EsquemaDocument1 pageSa2500p Rev09 - EsquemaBidu BiduNo ratings yet

- PropB3 F0 WM8727Document3 pagesPropB3 F0 WM8727Paweł WalencikNo ratings yet

- Previo 07 CompletoDocument2 pagesPrevio 07 CompletoRomeo Hernandez VillaNo ratings yet

- SB 620 SchematicDocument1 pageSB 620 Schematicpdq340No ratings yet

- CKT 8Document1 pageCKT 8Juan Luis Hernandez CarrizalesNo ratings yet

- Neo600 Master SCHDocument1 pageNeo600 Master SCHEduardo FingerNo ratings yet

- LMR - SDR Rev A V 1.4 UpdateDocument3 pagesLMR - SDR Rev A V 1.4 Updatejoy mukherjiNo ratings yet

- DVD Noblex Dvd-1350: 3828 Control Borad SechmaticDocument15 pagesDVD Noblex Dvd-1350: 3828 Control Borad SechmaticMariano Ohienart100% (1)

- Sonoff Dual Schematic 1Document3 pagesSonoff Dual Schematic 1neluNo ratings yet

- Lspic (5) 24VDocument1 pageLspic (5) 24VluispacheNo ratings yet

- 5V From +5V Power SuppyDocument1 page5V From +5V Power SuppySuny Khan100% (1)

- 17mb46 2 SemaDocument8 pages17mb46 2 SemaMihai AlexandruNo ratings yet

- uSDX MicronDocument1 pageuSDX MicronAdrian AdrianNo ratings yet

- P0 P1 P2 P3 CLK Q0 Q1 Q2 Q3 CO CIN PE RST U/D: Vacuo1 Vacuo2Document1 pageP0 P1 P2 P3 CLK Q0 Q1 Q2 Q3 CO CIN PE RST U/D: Vacuo1 Vacuo2Shalon MeloNo ratings yet

- R2-750R Uart Mbus BDMDocument1 pageR2-750R Uart Mbus BDMnelson linceNo ratings yet

- Genius Holdings 電路原理圖220924Document1 pageGenius Holdings 電路原理圖220924Jomes LeeNo ratings yet

- VCC 5.0V VCC 5.0V VCC 5.0V VCC 5.0V VCC 5.0V U7Document12 pagesVCC 5.0V VCC 5.0V VCC 5.0V VCC 5.0V VCC 5.0V U7alvionitaNo ratings yet

- Usbdm SWD JS16CWJDocument6 pagesUsbdm SWD JS16CWJCesar JakobyNo ratings yet

- Ibanez BCL TC10 Schematic PDFDocument1 pageIbanez BCL TC10 Schematic PDFdNo ratings yet

- Con3 Con1 GND - B GND - A U1 LM386 1 2 3: VCC VCCDocument1 pageCon3 Con1 GND - B GND - A U1 LM386 1 2 3: VCC VCCMartijn van ToorNo ratings yet

- No 2Document1 pageNo 2rigaboNo ratings yet

- PDF Created With Fineprint Pdffactory Trial Version: M-111 Subwoofer SystemDocument1 pagePDF Created With Fineprint Pdffactory Trial Version: M-111 Subwoofer SystemIgor MNo ratings yet

- The Power of Scarcity: Leveraging Urgency and Demand to Influence Customer DecisionsFrom EverandThe Power of Scarcity: Leveraging Urgency and Demand to Influence Customer DecisionsNo ratings yet

- One Bold Move a Day: Meaningful Actions Women Can Take to Fulfill Their Leadership and Career PotentialFrom EverandOne Bold Move a Day: Meaningful Actions Women Can Take to Fulfill Their Leadership and Career PotentialNo ratings yet

- Tutorial 4NEC2 PDFDocument36 pagesTutorial 4NEC2 PDFnameistakenNo ratings yet

- 3vlithium Techinfo GeneralDocument3 pages3vlithium Techinfo GeneralDivijNo ratings yet

- Generator Exciter & Voltage ExciterDocument34 pagesGenerator Exciter & Voltage ExciterYasir MehmoodNo ratings yet

- GEHC Service Manual - Solar 8000M I Patient Monitor v5 2008 PDFDocument192 pagesGEHC Service Manual - Solar 8000M I Patient Monitor v5 2008 PDFsotaquitoNo ratings yet

- Electronic Fault DiagnosisDocument114 pagesElectronic Fault Diagnosishaura fikriyah100% (1)

- Weather Physics PDFDocument2 pagesWeather Physics PDFAnti CorruptionNo ratings yet

- Panasonic's Basic Electrical Safety TipsDocument13 pagesPanasonic's Basic Electrical Safety TipsRobert Oconer AguilarNo ratings yet

- Ga-z68p-Ds3 v2.x eDocument104 pagesGa-z68p-Ds3 v2.x ejohnsonlimNo ratings yet

- B5 - Switch-Disconnector Fuses - P - ENDocument16 pagesB5 - Switch-Disconnector Fuses - P - ENGustavo GaibarNo ratings yet

- Inside Masami's CarDocument8 pagesInside Masami's Carvintagerccar100% (2)

- Using HP Auto Port Aggregation APADocument206 pagesUsing HP Auto Port Aggregation APAWalter LopezNo ratings yet

- Control 16C/T: Two-Way 6.5" Coaxial Ceiling Loudspeaker Key FeaturesDocument2 pagesControl 16C/T: Two-Way 6.5" Coaxial Ceiling Loudspeaker Key Featuresarij hhNo ratings yet

- Ebenezer Middle School Media Center Facilities Plan: Tradition With A VisionDocument58 pagesEbenezer Middle School Media Center Facilities Plan: Tradition With A Visioncdurden1872No ratings yet

- Antena - Dualband HWXX-6516DS1-VTM - Commscope-Obi PDFDocument3 pagesAntena - Dualband HWXX-6516DS1-VTM - Commscope-Obi PDFAndrei GhitiuNo ratings yet

- Using The Stm32F334 Microcontroller Embedded High Resolution Timer To Implement A 1Mhz, LLC Topology, Digital MPPT Solar ConverterDocument30 pagesUsing The Stm32F334 Microcontroller Embedded High Resolution Timer To Implement A 1Mhz, LLC Topology, Digital MPPT Solar ConvertertombalakNo ratings yet

- Sensors & Instrumentation Notes Unit-02Document47 pagesSensors & Instrumentation Notes Unit-02shivangi sharmaNo ratings yet

- Abacus MS-DOS For Beginners PDFDocument198 pagesAbacus MS-DOS For Beginners PDFanon_483649166No ratings yet

- 2Document119 pages2api-3723664No ratings yet

- 2013 CCTV CatalogDocument295 pages2013 CCTV CatalogEPCOMUSANo ratings yet

- Pb12 NSD ManualDocument18 pagesPb12 NSD Manualfogler833No ratings yet

- Instructions For 810 Vibration Tester Firmware UpgradeDocument4 pagesInstructions For 810 Vibration Tester Firmware Upgrademridu ranjanNo ratings yet

- Natural Frequency For The Operating CaseDocument1 pageNatural Frequency For The Operating CaseHajaMideenNo ratings yet

- Clip Electronic: Operating ManualDocument48 pagesClip Electronic: Operating ManualKostas StavrianosNo ratings yet

- Ex2. A 25 MVA, 1l KV, Three-Phase Generator Has A Sub Transient Reactance of 20%. TheDocument4 pagesEx2. A 25 MVA, 1l KV, Three-Phase Generator Has A Sub Transient Reactance of 20%. TheBharath Y KNo ratings yet

- Negative Ion GeneratorDocument3 pagesNegative Ion GeneratorLa LakersNo ratings yet

- Senr9414senr9414-01 SisDocument9 pagesSenr9414senr9414-01 SisPablo Gaspar D'Agostini AmengualNo ratings yet

- NEMA MG-1 (Part 1 - 2)Document85 pagesNEMA MG-1 (Part 1 - 2)Majho CanilangNo ratings yet