Professional Documents

Culture Documents

Introduction To Digital Systems 13 - Register-Transfer Level (RTL) Systems

Introduction To Digital Systems 13 - Register-Transfer Level (RTL) Systems

Uploaded by

enggshantCopyright:

Available Formats

You might also like

- Control Tutorials For MATLAB and Simulink - Introduction - PID Controller DesignDocument15 pagesControl Tutorials For MATLAB and Simulink - Introduction - PID Controller DesignSengottu VelusamyNo ratings yet

- Control Logic DesignDocument40 pagesControl Logic Designrameshaarya9980% (5)

- VHDL 4 RTL ModelsDocument33 pagesVHDL 4 RTL ModelsNguyễn Minh NghĩaNo ratings yet

- Digital PID Controllers: Different Forms of PIDDocument11 pagesDigital PID Controllers: Different Forms of PIDสหายดิว ลูกพระอาทิตย์No ratings yet

- Experiment No 14 2018 BatchDocument14 pagesExperiment No 14 2018 BatchHafeez AliNo ratings yet

- Control System Toolbox For Matlab: IntroDocument12 pagesControl System Toolbox For Matlab: IntroMikaNo ratings yet

- Custom Single Purpose Processor DesignDocument24 pagesCustom Single Purpose Processor DesignAar Kay GautamNo ratings yet

- To Show Using MATLAB: Root Locus and PID Controller ElaborationDocument6 pagesTo Show Using MATLAB: Root Locus and PID Controller ElaborationAbdul HaseebNo ratings yet

- Write The VHDL Code That Describe: Bit CountDocument31 pagesWrite The VHDL Code That Describe: Bit CountMad Hatter MercuryNo ratings yet

- Lab Report 4 PDFDocument15 pagesLab Report 4 PDF20pwmct0739No ratings yet

- An Integer Square Root Algorithm: Example 24Document10 pagesAn Integer Square Root Algorithm: Example 24psomasalNo ratings yet

- MATLAB and Its Control ToolboxDocument41 pagesMATLAB and Its Control ToolboxzkqasimNo ratings yet

- Clase Diseño Por Medio Del LGR Usando MatlabDocument42 pagesClase Diseño Por Medio Del LGR Usando MatlabJesus Tapia GallardoNo ratings yet

- L11 RTL SystemsDocument35 pagesL11 RTL SystemsusitggsipuNo ratings yet

- Lab - Manual - Soft - Computing - PDFDocument39 pagesLab - Manual - Soft - Computing - PDFpradeep mahateNo ratings yet

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003No ratings yet

- Atienza Lab3Document18 pagesAtienza Lab3Marvin AtienzaNo ratings yet

- Lab 4 ReportDocument16 pagesLab 4 Report20pwmct0739No ratings yet

- Intro Vhdl1Document30 pagesIntro Vhdl1pandaros000No ratings yet

- Ds First LatestDocument31 pagesDs First LatestZohaib KhanNo ratings yet

- Lab 06Document7 pagesLab 06Andy MeyerNo ratings yet

- Design of A PPM Modulator With VHDLDocument10 pagesDesign of A PPM Modulator With VHDLMarcos Guerra MedinaNo ratings yet

- Systemverilog - Lecture 1Document62 pagesSystemverilog - Lecture 1Shilpa ReddyNo ratings yet

- ACS PracticalFile IshaVerma PDFDocument23 pagesACS PracticalFile IshaVerma PDFDibyendu KarmakarNo ratings yet

- Control ReportDocument15 pagesControl ReportKenshow Large50% (2)

- Program 1: Write A Program Using MATLAB To Plot Pole Zero Map While Transfer Function Is GivenDocument21 pagesProgram 1: Write A Program Using MATLAB To Plot Pole Zero Map While Transfer Function Is GivenShruti BhatnagarNo ratings yet

- Soc11 07 CodesignDocument50 pagesSoc11 07 Codesignswapna revuriNo ratings yet

- Machine Problem 4Document12 pagesMachine Problem 4JERUELNo ratings yet

- VHDL Processes: Cwru Eecs 318Document24 pagesVHDL Processes: Cwru Eecs 318KarThikNo ratings yet

- Ovation Advanced Control Algorithms: PredictorDocument10 pagesOvation Advanced Control Algorithms: PredictorMuhammad UsmanNo ratings yet

- Presented By: K.Praveen V.Sathish Kumar A.Yasar Arafath R.VenkateshwaranDocument32 pagesPresented By: K.Praveen V.Sathish Kumar A.Yasar Arafath R.Venkateshwaranprkg870% (1)

- EEE 70 Advanced Topics in Logic Design: Read Before ClassDocument30 pagesEEE 70 Advanced Topics in Logic Design: Read Before ClassPraveen MeduriNo ratings yet

- Sequential Circuit Design Using PLDsDocument8 pagesSequential Circuit Design Using PLDsJacob ChakoNo ratings yet

- Experiment No.1: Introduction To Lti Representation and Transfer Function ModelDocument7 pagesExperiment No.1: Introduction To Lti Representation and Transfer Function ModelIra CervoNo ratings yet

- Addition / Subtraction: Parts Chapters IDocument103 pagesAddition / Subtraction: Parts Chapters ITooba Sami ArifeenNo ratings yet

- ET2063 Mechatronics-ReportDocument28 pagesET2063 Mechatronics-Reportmahsanorion247No ratings yet

- EE208: Level II Control Systems Defining Transfer Functions in MatlabDocument7 pagesEE208: Level II Control Systems Defining Transfer Functions in Matlabanyany111111No ratings yet

- Acs Pract File 1Document27 pagesAcs Pract File 1deepanshumehalawat07No ratings yet

- Experiment No.1 Time Response of First Order System: 1.matlab ProgramDocument5 pagesExperiment No.1 Time Response of First Order System: 1.matlab ProgramDarshan DeepuNo ratings yet

- NI Tutorial 6463 enDocument6 pagesNI Tutorial 6463 enAmaury BarronNo ratings yet

- sc554 2014 Lecture09Document34 pagessc554 2014 Lecture09tharindu12No ratings yet

- Experiment 26 Shift Registers: ObjectivesDocument6 pagesExperiment 26 Shift Registers: ObjectivesPieyka ShafikaNo ratings yet

- Control Systems Design ToolsDocument9 pagesControl Systems Design ToolsTeguh SantosoNo ratings yet

- Note - 13 - Intro To Digital Control SystemDocument7 pagesNote - 13 - Intro To Digital Control SystemVimal Raj DNo ratings yet

- Unit 3Document24 pagesUnit 3Raja BenitaNo ratings yet

- Control System 1 PDFDocument72 pagesControl System 1 PDFElangoNo ratings yet

- Digital Filters in VHDL LabDocument5 pagesDigital Filters in VHDL LabAli AhmadNo ratings yet

- CSD Experiment No 8Document9 pagesCSD Experiment No 8Gourav PalNo ratings yet

- Combinational and Sequential Circuits DesignDocument25 pagesCombinational and Sequential Circuits DesignJadesh ChandaNo ratings yet

- VHDL Lab ProgramsDocument51 pagesVHDL Lab ProgramsvenkiNo ratings yet

- Chap6 PDFDocument24 pagesChap6 PDFSrinivas CherukuNo ratings yet

- ps3 (1) From MAE 4780Document5 pagesps3 (1) From MAE 4780fooz10No ratings yet

- Repetitive ControlDocument22 pagesRepetitive ControlShri KulkarniNo ratings yet

- Lab9 VHDLDocument8 pagesLab9 VHDLFasli CoolNo ratings yet

- Project Based Learning IcsDocument14 pagesProject Based Learning IcsAvinash YadavNo ratings yet

- Digital Logic DesignDocument106 pagesDigital Logic DesignSuraj KumarNo ratings yet

- Nonlinear Control Feedback Linearization Sliding Mode ControlFrom EverandNonlinear Control Feedback Linearization Sliding Mode ControlNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet

Introduction To Digital Systems 13 - Register-Transfer Level (RTL) Systems

Introduction To Digital Systems 13 - Register-Transfer Level (RTL) Systems

Uploaded by

enggshantOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Introduction To Digital Systems 13 - Register-Transfer Level (RTL) Systems

Introduction To Digital Systems 13 - Register-Transfer Level (RTL) Systems

Uploaded by

enggshantCopyright:

Available Formats

1

REGISTER-TRANSFER LEVEL (RTL) SYSTEMS

EXECUTION GRAPHS

CLASSIFICATION OF EXECUTION GRAPHS

according to sequencing structure

ORGANIZATION OF SYSTEMS: functional and control units

RTL SYSTEM ORGANIZATION: data and control subsystems.

vhdl SPECIFICATION OF RTL SYSTEMS

REGISTER TRANSFER, REGISTER-TRANSFER GROUP,

AND REGISTER-TRANSFER SEQUENCE

ANALYSIS AND DESIGN PROCESS FOR RTL SYSTEMS

DESIGN OF SERIAL-PARALLEL MULTIPLIER

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

2

REGISTER TRANSFER LEVEL (RTL)

1. DATA SUBSYSTEM (datapath) AND CONTROL SUBSYSTEM

2. THE STATE OF DATA SUBSYSTEM:

CONTENTS OF A SET OF REGISTERS

3. THE FUNCTION OF THE SYSTEM PERFORMED AS A SEQUENCE OF

REGISTER TRANSFERS (in one or more clock cycles)

4. A REGISTER TRANSFER:

A TRANSFORMATION PERFORMED ON A DATA WHILE THE DATA

TRANSFERRED FROM ONE REGISTER TO ANOTHER

5. THE SEQUENCE OF REGISTER TRANSFERS CONTROLLED BY THE

CONTROL SUBSYSTEM (a sequential system)

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

3

EXAMPLE OF EXECUTION GRAPH

P

7

(x) =

7

i=0

p

i

x

i

TWO ALGORITHMS:

P

7

(x) = ((((((p

7

x + p

6

)x + p

5

)x + p

4

)x + p

3

)x + p

2

)x + p

1

)x + p

0

P

7

(x) = (x

2

)(x

2

)[x

2

(p

7

x + p

6

) + (p

5

x + p

4

)] + x

2

(p

3

x + p

2

) + (p

1

x + p

0

)

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

4

Example 13.1

(a)

(b)

i = 6

BEGIN

yes

OR

V = p

7

V = V*x + p

i

i = i-1

i > 0

END

no

BEGIN

p

6

V = *x +

p

7

V = V*x + p

5

V = V*x + p

4

V = V*x + p

3

V = V*x + p

2

V = V*x + p

1

V = V*x + p

0

END

Figure 13.1: SEQUENTIAL EXECUTION GRAPHS FOR POLYNOMIAL EVALUATION: a) UNFOLDED; AND b) LOOP.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

5

BEGIN

P

7

(x) = G * F + H

END

G = B * A + C F = A * A H = D * A + E

E = p x + p

1 0

D = p x + p

3 2

C = p x + p

5 4

B = p x + p

7 6

A = x * x

(b)

(a)

BEGIN

E = p x + p

1 0

D = p x + p

3 2

C = p x + p

5 4

B = p x + p

7 6

G = B * A + C

A = x * x

F = A * A H = D * A + E

P

7

(x) = G * F + H

END

AND

AND

AND

Figure 13.2: CONCURRENT EXECUTION GRAPHS FOR POLYNOMIAL EVALUATION: a) CONCURRENT; AND b) GROUP-

SEQUENTIAL.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

6

ALGORITHM CONVERSION

CONCURRENT INTO SEQUENTIAL

BEGIN

E = p x + p

1 0

D = p x + p

3 2

C = p x + p

5 4

B = p x + p

7 6

G = B * A + C

A = x * x

F = A * A H = D * A + E

P

7

(x)

= G * F + H

END

Figure 13.3: TRANSFORMATION OF A CONCURRENT EXECUTION GRAPH INTO A SEQUENTIAL ONE.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

7

ORGANIZATION OF SYSTEMS

TWO FUNCTIONS:

DATA TRANSFORMATIONS FUNCTIONAL UNITS (operators)

CONTROL OF DATA TRANSFORMATIONS

AND THEIR SEQUENCING CONTROL UNITS

TYPES OF SYSTEMS WITH RESPECT TO FUNCTIONAL UNITS:

NONSHARING SYSTEM

SHARING SYSTEM

UNIMODULE SYSTEM

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

8

TYPES OF CONTROL

CENTRALIZED CONTROL

DECENTRALIZED CONTROL

SEMICENTRALIZED CONTROL

D

A

T

A

C

O

M

M

U

N

I

C

A

T

I

O

N MODULE 1

MODULE 2

MODULE 3

Data

C

O

N

T

R

O

L

Control

signals

Conditions

(a)

D

A

T

A

C

O

M

M

U

N

I

C

A

T

I

O

N MODULE 1

MODULE 2

MODULE 3

Data

(b)

Sequencing

control

signals

D

A

T

A

C

O

M

M

U

N

I

C

A

T

I

O

N MODULE 1

MODULE 2

MODULE 3

Data

C

O

N

T

R

O

L

Control

signals

Conditions

(c)

Module

control

Figure 13.4: CONTROL STRUCTURES: a) CENTRALIZED; b) DECENTRALIZED; c) SEMICENTRALIZED.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

9

ADD

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

ADD

C

O

N

T

R

O

L

ADD

C

O

N

T

R

O

L

ADD

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

ADD

C

O

N

T

R

O

L

ADD

C

O

N

T

R

O

L

MULT

C

O

N

T

R

O

L

ADD

C

O

N

T

R

O

L

control data

* for clarity not all

control lines are shown

** MULT and ADD

include required storage

**

*

**

x

p

7

p

5

p

3

p

1

p

6

p

4

p

2

p

0

P

7

(x)

B

C

D E

G H

F

A

start

done

Figure 13.5: NON-SHARING DATA/DECENTRALIZED CONTROL IMPLEMENTATION FOR P

7

(x).

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

10

SHARING DATA SUBSYSTEM AND CENTRALIZED CONTROL

MODULE OPERATIONS:

if c1 = 1 then O

1

= I

11

I

12

+ I

13

if c2 = 1 then O

2

= I

21

I

22

+ I

23

I

ij

corresponds to the i-th input of set j

O

1

O

2

I

21

I

22

I

23

I

11

I

12

I

13

O

1

O

2

I

21

I

22

I

23

I

11

I

12

I

13

O

1

O

2

I

21

I

22

I

23

I

11

I

12

I

13

O

1

O

2

I

21

I

22

I

23

I

11

I

12

I

13

O

1

O

2

I

21

I

22

I

23

I

11

I

12

I

13

B

C G A F

D H E

p

7

p

6

x

p

5

p

4

x

0

0

x

p

3

p

2

x

p

1

p

0

x

P

7

(x)

Step 1: A, B, C, D, E

Step 2: F, G, H

Step 3: P

7

(x)

Computation steps:

Step 3

Step 2

Step 1

CONTROL

c

1

c

2

Figure 13.6: SHARING DATA SUBSYSTEM FOR P

7

(x).

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

11

write

address 1

address 2

address 3

REGISTER

ARRAY

R

CONTROL

OPERATOR

ab+c

a b c

z

DISTRIBUTOR

register

M

control of

module M

Figure 13.7: UNIMODULE DATA SUBSYSTEM FOR P

7

(x).

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

12

UNIMODULE DATA SUBSYSTEM

A POSSIBLE MAPPING:

1: a p

7

, b x

2: c p

6

3: z p

7

x + p

6

4: T z

5: a T, c p

5

6: z Tx + p

5

and so on.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

13

ORGANIZATION OF RTL SYSTEM

DATA SUBSYSTEM: implements data storage, data movement and data

transfers

CONTROL SUBSYSTEM: controls the operations in the data subsystem and

their sequencing

DATA

SUBSYSTEM

CONTROL

SUBSYSTEM

Control

signals

Conditions

Data inputs

Data outputs

Control outputs Control inputs

Figure 13.8: STRUCTURE OF A RTL SYSTEM.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

14

SPECIFICATION OF RTL SYSTEMS USING vhdl

Example 13.6

A SYSTEM WHICH PERFORMS THE FOLLOWING COMPUTATION WITH-

OUT USING A TWO-OPERAND ADDER:

INPUTS: x, y {128, . . . , 127}

OUTPUT: z {256, . . . , 508}

FUNCTION: z =

4(x + |y|)/2 if x < |y|

4x otherwise

RTL SEQUENCE FOR THIS COMPUTATION IS BASED ON

a = (x + |y|)/2 = x + (|y| x)/2

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

15

a<w

z = 4a

a=x; w = |y|

Input x, y

yes

no

a=a+1; w=w-1

Output z

(a)

-- This is a high-level description; it is not intended

-- for synthesis. (The WHILE statement might not be

-- supported by a synthesis tool)

PACKAGE inc_dec_pkg IS

SUBTYPE SignDataT IS INTEGER RANGE -128 TO 127;

SUBTYPE PosDataT IS INTEGER RANGE 0 TO 128;

SUBTYPE DataoutT IS INTEGER RANGE -256 TO 508;

END inc_dec_pkg;

USE WORK.inc_dec_pkg.ALL;

ENTITY inc_dec IS

PORT(x_in,y_in: IN SignDataT;

z_out : OUT DataoutT;

clk : IN BIT);

END inc_dec;

ARCHITECTURE high_level OF inc_dec IS

BEGIN

PROCESS (clk)

VARIABLE a : SignDataT;

VARIABLE w : PosDataT;

BEGIN

IF (clkEVENT AND clk = 1) THEN

a:= x_in; -- initialize variables

w:= ABS(y_in); -- compute abs(y_in)

WHILE (a < w) LOOP

a:= a+1; -- if x < y compute

w:= w-1; -- by incr. x and decr. y

END LOOP;

z_out <= (a * 4);

END IF;

END PROCESS;

END high_level;

(b)

Figure 13.9: SYSTEM IN EXAMPLE 13.6: a) EXECUTION GRAPH; b) HIGH-LEVEL DESCRIPTION.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

16

PROCEDURE TO OBTAIN SPECIFICATION

1. DRAW AN EXECUTION GRAPH FOR THE COMPUTATION

2. WRITE THE vhdl DESCRIPTION OF THE SYSTEM, BASED ON THE

EXECUTION GRAPH

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

17

Example 13.7

NEWTON-RAPHSON RECURRENCE FOR COMPUTING APPROXIMA-

TION z TO RECIPROCAL OF 1/2 x < 1

RTL SEQUENCE DERIVED FROM

z

i+1

= z

i

(2 xz

i

), z

0

= 1

TERMINATES WHEN x z

k

1 < 0.5

QUADRATIC CONVERGENCE

|xz

k

1| = (xz

k1

1)

2

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

18

|w-1| < eps/2

w=x*z

Input x, eps, z=1

yes

no

z=(2-w)z

Output z

(a)

-- This is a high-level description; it is not intended

-- for synthesis. (The WHILE statement and REAL TYPE might

-- not be supported by a synthesis tool)

PACKAGE recip_pkg IS

SUBTYPE DatainT IS REAL RANGE 0.5 TO 1.0;

SUBTYPE DataoutT IS REAL RANGE 1.0 TO 2.0;

SUBTYPE EpsT IS REAL RANGE 0.0 TO 0.1;

END recip_pkg;

USE WORK.recip_pkg.ALL;

ENTITY reciprocal IS

PORT(x_in : IN DatainT ;

eps_in: IN EpsT ;

z_out : OUT DataoutT;

clk : IN BIT );

END reciprocal;

ARCHITECTURE high_level OF reciprocal IS

BEGIN

PROCESS (clk)

VARIABLE x,w: DatainT ;

VARIABLE z : DataoutT;

BEGIN

IF (clkEVENT AND clk = 1) THEN

z := 1.0; x := x_in;

w := x * z;

WHILE (ABS(w - 1.0) > eps_in/2.0) LOOP

z := (2.0 - w) * z;

w := x * z;

END LOOP;

z_out <= z;

END IF;

END PROCESS;

END high_level;

(b)

Figure 13.10: SYSTEM IN EXAMPLE 13.7: a) EXECUTION GRAPH; b) HIGH-LEVEL SPECIFICATION.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

19

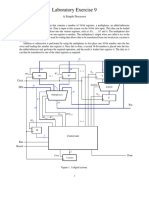

IMPLEMENTATION OF RTL SYSTEMS

MUX2

0 1

cmpl_y

LD

R_X

X

s_mux2

ld_Y

clk

LD

R_Y

Y

(0..0)

Control

signals

Operator

CMPL_X

Operator

CMPL_Y

Control

points

c_0

Operator

ADD

ld_Z

LD

R_Z

Z

n

n

n

Control

Subsystem

Data

Subsystem

ld_X

n

n

cmpl_x

n

n

n

n

clk

clk

clk

Conditions

c_in

- state

- state

transition

- control

functions

Register

Control inputs

Control outputs

Data inputs

Data outputs

MUX1

0 1

s_mux1

n

n

n

n

w

c_out

Figure 13.11: RTL SYSTEM.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

20

ARCHITECTURE behavioral OF data_sub IS

SIGNAL R_X,R_Y,R_Z: BIT_VECTOR(n-1 DOWNTO 0);

BEGIN

PROCESS (clk)

VARIABLE zero_n: BIT_VECTOR(n-1 DOWNTO 0):= (OTHERS => 0);

VARIABLE w : BIT_VECTOR(n-1 DOWNTO 0);

VARIABLE selec : BIT_VECTOR( 2 DOWNTO 0);

BEGIN

selec:= cmpl_x & cmpl_y & smux_2;

CASE selec IS

WHEN "000" => w := add(R_X,zero_n,c_0);

WHEN "001" => w := add(R_X,R_Y,c_0) ;

WHEN "010" => w := add(R_X,zero_n,c_0);

WHEN "011" => w := add(R_X,cmpl(R_Y),c_0) ;

WHEN "100" => w := add(cmpl(R_X),zero_n,c_0);

WHEN "101" => w := add(cmpl(R_X),R_Y,c_0) ;

WHEN "110" => w := add(cmpl(R_X),zero_n,c_0);

WHEN "111" => w := add(cmpl(R_X),cmpl(R_Y),c_0);

END CASE;

IF (clkEVENT AND clk = 1) THEN

IF (ld_X = 1) THEN R_X <= X; END IF; -- R_X

IF (ld_Z = 1) THEN R_Z <= w; END IF; -- R_Z

IF (ld_Y = 1) THEN

IF (smux_1 = 0) THEN R_Y <= Y; -- R_Y

ELSE R_Y <= w;

END IF;

END IF;

END IF;

END PROCESS;

END behavioral;

Figure 13.12: Register transfers in Figure 13.11

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

21

ANALYSIS OF RTL SYSTEMS

ENTITY rtl_system IS

GENERIC (n: NATURAL:=8); -- bit-vectors width

PORT(data_in : IN BIT_VECTOR ; -- input data

data_out: OUT BIT_VECTOR ; -- output data

ctrl_in : IN BIT_VECTOR ; -- input controls

ctrl_out: OUT BIT_VECTOR ; -- output controls

clk : IN BIT);

END rtl_system;

ARCHITECTURE general OF rtl_system IS

TYPE stateT IS (S0,S1,...,Sk);

SIGNAL state: stateT:= S0; -- state register

SIGNAL reg_A,...: BIT_VECTOR(n-1 DOWNTO 0); -- data registers

CONSTANT c1: NATURAL:= ...; --length of controls bit-vector

CONSTANT c2: NATURAL:= ...; --length of conds. bit-vector

SIGNAL data_ctrls : BIT_VECTOR(c1-1 DOWNTO 0); -- controls

SIGNAL data_conds : BIT_VECTOR(c2-1 DOWNTO 0); -- conds.

BEGIN

PROCESS(clk) -- data subsystem -----------------+

BEGIN -- |

IF (clk = 1) THEN -- |

CASE data_ctrls IS -- |

WHEN ... => ...; -- register transfer group 0 |

WHEN ... => ...; -- |

WHEN ... => ...; -- register transfer group k |

WHEN OTHERS => NULL; -- |

END CASE; -- |

END IF; -- |

END PROCESS; -- ---------------------------------+

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

22

ANALYSIS OF RTL SYSTEM (cont.)

PROCESS (clk) -- control subsystem, --------------+

BEGIN -- transition function |

IF (clk = 1) THEN -- transitions might depend on |

CASE state IS -- data conditions, described by |

WHEN S0 => state <= ...; -- IF statements in each state |

WHEN .... ; -- |

WHEN Sk => state <= ...; -- |

END CASE; -- |

END IF; -- |

END PROCESS; -- |

-- |

PROCESS (state,ctrl_in) -- control subsystem, |

BEGIN -- output function |

CASE state IS -- |

WHEN S0 => data_ctrls <= ...; ctrl_out <= ...; |

WHEN .... -- |

WHEN Sk => data_ctrls <= ...; ctrl_out <= ...; |

END CASE; -- |

END PROCESS; -- ---------------------------------+

END general;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

23

EXAMPLE 13.9: DATA OPERATORS

MULTF(m, rec) = mrec

SUB2F(w) = 2 w

SUB1F(w) = 1 w

COMP(b, eps) =

1 if b > eps

0 otherwise

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

24

EXAMPLE 13.9: RTL SYSTEM

CONTROL

SUBSYSTEM

arg rec

eps

MUX_M

MULTF

w

SUB2F

y

SUB1F

COMP

MUX_R

p

011...11

ld_y

ld_w

k

ld_eps

ld_rec

ld_arg

selM

selR

arg_in

eps_in

rec_out

clk

clk clk

clk

clk

DATA SUBSYSTEM

v

m

r

0 1

0 1

b

a

DMUX

0 1

DMUX

1 0

S0

S1

S2

S3

S4

k

start

D

Q

clk

D

Q

clk

D

Q

clk

D

Q

clk

clear

set

D

Q

clk

done

ld_arg, ld_eps, ld_rec

selM, ld_w,

ld_y

selR, ld_rec

n

n+1

n

n+1

n+1

n+1

n+1

n

n

n

n

n+1

n+1

n+1

Figure 13.14: RTL SYSTEM FOR Example 13.9.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

25

Example 13.9 (cont.)

ENTITY example IS

GENERIC(n: NATURAL:= 16); -- bit-vectors length

PORT(start : IN BIT ;

arg_in,eps_in: IN UNSIGNED(n-1 DOWNTO 0);

rec_out : OUT UNSIGNED(n DOWNTO 0) ;

done : OUT BIT ;

clk : IN BIT );

END example;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

26

Example 13.9 (cont.)

ARCHITECTURE direct OF example IS

TYPE stateT is (s0, s1, s2, s3, s4);

SIGNAL state : stateT:= s0;

SIGNAL arg,eps,w: UNSIGNED(n-1 DOWNTO 0); -- n-bit registers

SIGNAL rec,y : UNSIGNED(n DOWNTO 0) ; -- n+1 bit register

SIGNAL k : BIT ; -- condition

SIGNAL ld_arg,ld_rec,ld_eps,ld_w,ld_y,selR,selM: BIT; -- controls

BEGIN

PROCESS (clk) -- data subsystem ---------+

VARIABLE b: UNSIGNED(n-1 DOWNTO 0); -- internal data elements |

VARIABLE r,m,p,v: UNSIGNED(n DOWNTO 0); -- |

BEGIN -- combinational modules |

IF (selR = 0) THEN r:= (OTHERS => 1);r(n):=0; |

ELSE r:= p; END IF; --|

IF (selM = 0) THEN m:= y; ELSE m:= 0 & arg; END IF; --|

p:= multf(m,rec); b:= sub1f(w); v:= sub2f(w); k <= compf(eps,b); --|

IF (clk = 1) THEN -- register modules |

IF (ld_arg = 1) THEN arg <= arg_in; END IF; --|

IF (ld_rec = 1) THEN rec <= r ; END IF; --|

IF (ld_eps = 1) THEN eps <= eps_in; END IF; --|

IF (ld_w = 1) THEN w <= p(n-1 DOWNTO 0); END IF; --|

IF (ld_y = 1) THEN y <= v ; END IF; --|

END IF; --|

rec_out <= rec; --|

END PROCESS; -- ------------------------+

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

27

-- control subsystem ------+

PROCESS (clk) -- transition function |

BEGIN |

IF (clk = 1) THEN |

CASE state IS |

WHEN s0 => IF (start = 1) THEN state <= s1; --|

ELSE state <= s0; END IF; --|

WHEN s1 => state <= s2; --|

WHEN s2 => state <= s3; --|

WHEN s3 => state <= s4; --|

WHEN s4 => IF (k = 1) THEN state <= s2; |

ELSE state <= s0; END IF; --|

END CASE; --|

END IF; --|

END PROCESS; -- ------------------------+

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

28

PROCESS (state) -- output function --|

BEGIN --|

CASE state IS --|

WHEN s0 => done <= 1; ld_rec <= 0; --|

WHEN s1 => ld_arg <= 1; ld_eps <= 1; --|

selR <= 0; ld_rec <= 1; done <= 0; --|

WHEN s2 => selM <= 1; ld_w <= 1; --|

ld_arg <= 0; ld_eps <= 0; ld_rec <= 0; --|

WHEN s3 => ld_y <= 1; ld_w <= 0; --|

WHEN s4 => selM <= 0; selR <= 1; ld_rec <= 1; --|

WHEN others => NULL; --|

END CASE; --|

END PROCESS; -- ------------------------+

END direct;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

29

STATE DIAGRAM

S0

S1

S2

S3

S4

start

start

k

k

Outputs (Control Signals)

done selM selR ld_arg ld_eps ld_rec ld_y ld_w

1 0 0 0 0 0 0 0

0 0 0 1 1 1 0 0

0 1 0 0 0 0 0 1

0 0 0 0 0 0 1 0

0 0 1 0 0 1 0 0

Figure 13.17: STATE DIAGRAM OF SYSTEM IN EXAMPLE 13.9.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

30

Example 13.9 (cont.)

S0: done <= 1;

S1: done <= 0; arg <= arg_in; rec <= "01...1";

eps <= eps_in;

S2: w <= MULTF(arg,rec);

S3: y <= SUB2F(w)

S4: rec <= MULTF(y,rec);

k <= COMP(eps,SUB1F(w));

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

31

Example 13.9 (cont.)

ARCHITECTURE behavioral OF example IS

TYPE stateT IS (S0,S1,S2,S3,S4);

SIGNAL state : stateT:= S0;

SIGNAL arg,eps,w : UNSIGNED(n-1 DOWNTO 0);

SIGNAL rec,y : UNSIGNED(n DOWNTO 0) ;

BEGIN

PROCESS (clk)

BEGIN

IF (clkEVENT AND clk = 1) THEN

CASE state IS

WHEN S0 => done <= 1;

IF (start = 1) THEN state <= S1;

ELSE state <= S0; END IF;

WHEN S1 => arg <= arg_in;

rec <= (OTHERS => 1); rec(n) <= 0;

eps <= eps_in; done <= 0;

state <= S2;

WHEN S2 => w <= arg * rec;

state <= S3 ;

WHEN S3 => y <= 2 - w;

state <= S4 ;

WHEN S4 => rec <= y * rec;

IF (1-w > eps) THEN state <= S2;

ELSE state <= S0; END IF;

END CASE; END IF; END PROCESS; END behavioral;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

32

FUNCTION OF THE SYSTEM

WHILE (1-arg * rec > eps) LOOP

rec := (2-arg * rec) * rec;

END WHILE;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

33

Example 13.9: POSSIBLE REGISTER TRANSFERS

IF (ld_arg = 1) THEN arg <= arg_in; END IF;

IF (ld_eps = 1) THEN eps <= eps_in; END IF;

IF (ld_w = 1) AND (selM = 0) THEN w <= MULTF(y,rec);

END IF;

IF (ld_w = 1) AND (selM = 1) THEN w <= MULTF(arg,rec);

END IF;

IF (ld_y = 1) THEN y <= SUB2F(w); END IF;

IF (ld_rec = 1) AND (selR = 0) THEN rec <= 1 ; END IF;

IF (ld_rec = 1) AND (selR = 1) AND (selM = 0) THEN

rec <= MULTF(y,rec); END IF;

IF (ld_rec = 1) AND (selR = 1) AND (selM = 1) THEN

rec <= MULTF(y,arg); END IF;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

34

DESIGN OF RTL SYSTEMS

DESIGN OF DATA SUBSYSTEM:

1. DETERMINE THE OPERATORS (functional units)

Two operations can be assigned to the same functional unit if they form

part of dierent groups

2. DETERMINE THE REGISTERS REQUIRED TO STORE OPERANDS, RE-

SULTS, AND INTERMEDIATE VARIABLES

Two variables can be assigned to the same register if they are active in

disjoint time intervals

3. CONNECT THE COMPONENTS BY DATAPATHS (wires and multiplexers)

as required by the transfers in the sequence

4. DETERMINE THE CONTROL SIGNALS AND CONDITIONS required by

the sequence

5. DESCRIBE THE STRUCTURE OF THE DATA SECTION by a logic diagram,

a net list, or a vhdl structural description

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

35

GENERALIZED BEHAVIORAL DESCRIPTION

ARCHITECTURE generalized OF

data_subsystem IS

BEGIN

PROCESS (clk)

SIGNAL reg_A,reg_B: BIT_VECTOR;

BEGIN

IF (clk = 1) THEN

IF (ctl0 = 1) THEN ... END IF;

IF (ctl1 = 1) THEN ... END IF;

.....

IF (ctlj = 1) THEN ... END IF;

END IF;

END PROCESS;

END generalized;

ARCHITECTURE generalized OF

control_subsystem IS

BEGIN

PROCESS (clk)

TYPE stateT is (s0, s1, sk);

SIGNAL state: stateT:= s0;

BEGIN

IF (clk = 1) THEN

CASE state IS

WHEN s0 => ....;

WHEN s1 => ....;

WHEN sk => ....;

END CASE;

END IF;

END PROCESS;

END generalized;

(a) (b)

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

36

INTERFACE BETWEEN DATA AND CONTROL SUBSYSTEMS

ENTITY group_seq_system IS

PORT (data_in : IN BIT_VECTOR; -- input data

data_out: OUT BIT_VECTOR; -- output data

ctrl_in : IN BIT_VECTOR; -- input conditions

ctrl_out: OUT BIT_VECTOR; -- output conditions

clk : IN BIT );

END group_seq_system;

ARCHITECTURE generalized OF group_seq_system IS

SIGNAL controls : BIT_VECTOR; -- control signals

-- to data subsystem

SIGNAL conds : BIT_VECTOR; -- condition signals

-- from data subsystem

BEGIN

U1: ENTITY data_subsystem

PORT MAP (data_in,data_out,controls,conds,clk);

U2: ENTITY control_subsystem

PORT MAP (ctrl_in,ctrl_out,conds,controls,clk);

END generalized;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

37

DESIGN OF CONTROL SUBSYSTEM

1. DETERMINE THE REGISTER-TRANSFER SEQUENCE

2. ASSIGN ONE STATE TO EACH RT-group

3. DETERMINE STATE-TRANSITION AND OUTPUT FUNCTIONS

4. IMPLEMENT THE CORRESPONDING SEQUENTIAL SYSTEM

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

38

DESIGN EXAMPLE: MULTIPLIER

INPUTS: x, y {0, 1, . . . , 2

n

1}

OUTPUT: z {0, 1, . . . , 2

2n

2

n+1

+ 1}

FUNCTION: z = x y

RECURRENCE:

z[i + 1] =

1

2

(z[i] + (x 2

n

) y

i

)

z[0] = 0 z = z[n]

OPERATIONS IN ONE ITERATION OF THE RECURRENCE:

Multiplication of x by 2

n

.

Multiplication of (x 2

n

) by y

i

, the i-th bit of y (value 0 or x 2

n

)

Addition of z[i] and (x 2

n

) y

i

.

Multiplication of the sum by

1

2

(one-bit right shift)

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

39

EXECUTION GRAPH OF MULTiPlIER

z=0; i=0

Input x, y

start

start

i=i+1

i = n-1

idle

n

i = n-1

z = (1/2) (z + (x * 2 ) y )

i

Figure 13.22: EXECUTION GRAPH OF SERIAL-PARALLEL MULTIPLIER.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

40

Example 13.10

x = 188 , x = 10111100

y = 203 , y = 11001011

z = z[8] = 1001010100010100 = 38164

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

41

z[0] = 00000000 00000000

(x 2

8

) y

0

= 10111100 00000000

z[0] + (x 2

8

) y

0

= 010111100 00000000

z[1] = 01011110 00000000

(x 2

8

) y

1

= 10111100 00000000

z[1] + (x 2

8

) y

1

= 100011010 00000000

z[2] = 10001101 00000000

(x 2

8

) y

2

= 00000000 00000000

z[2] + (x 2

8

) y

2

= 010001101 00000000

z[3] = 01000110 10000000

(x 2

8

) y

3

= 10111100 00000000

z[3] + (x 2

8

) y

3

= 100000010 10000000

z[4] = 10000001 01000000

(x 2

8

) y

4

= 00000000 00000000

z[4] + (x 2

8

) y

4

= 010000001 01000000

z[5] = 01000000 10100000

(x 2

8

) y

5

= 00000000 00000000

z[5] + (x 2

8

) y

5

= 001000000 10100000

z[6] = 00100000 01010000

(x 2

8

) y

6

= 10111100 00000000

z[6] + (x 2

8

) y

6

= 011011100 01010000

z[7] = 01101110 00101000

(x 2

8

) y

7

= 10111100 00000000

z[7] + (x 2

8

) y

7

= 100101010 00101000

z[8] = 10010101 00010100

z = z[8] = 1001010100010100 = 38164

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

42

VHDL SPECIFICATION

Multiplier

xin

yin

start

clk

zout

Figure 13.23: BLOCK DIAGRAM

ENTITY multiplier IS

GENERIC(n : NATURAL:= 16); -- number of bits in operands

PORT (start : IN BIT ;

xin,yin: IN UNSIGNED(n-1 DOWNTO 0);

clk : IN BIT ;

zout : OUT UNSIGNED(2*n-1 DOWNTO 0);

done : OUT BIT);

END multiplier;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

43

ARCHITECTURE behavioral OF multiplier IS

TYPE stateT IS (idle,setup,active) ;

SIGNAL state : stateT := idle ;

SIGNAL x,y : BIT_VECTOR(n-1 DOWNTO 0); -- operand registers

SIGNAL z : BIT_VECTOR(2*n-1 DOWNTO 0);

SIGNAL count : NATURAL RANGE 0 TO n-1 ;

BEGIN

PROCESS (clk)

VARIABLE zero_2n : UNSIGNED(2*n-1 DOWNTO 0); -- constant zero

VARIABLE scale : UNSIGNED(n-1 DOWNTO 0) ; -- aligning vector

VARIABLE add_out : UNSIGNED(2*n DOWNTO 0) ;

BEGIN

zero_2n:= (OTHERS => 0);

scale := (OTHERS => 0);

IF (clkEVENT AND clk = 1) THEN

CASE state IS

WHEN idle => done <= 1;

IF (start = 1) THEN state <= setup;

ELSE state <= idle;

END IF;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

44

WHEN setup => x <= xin; y <= yin; z <= zero_2n;

count <= 0;

zout <= zero_2n; done <= 0;

state <= active;

WHEN active => IF (y(count)) = 0) THEN

add_out :=0 & z;

ELSE

add_out := (0 & z) + (0 & x & scale);

END IF

z <= add_out(2*n DOWNTO 1);

zout <= add_out(2*n DOWNTO 1);

IF (count /= (n-1)) THEN

state <= active;

count <= count+1;

ELSE

state <= idle;

done <= 1 ;

END IF;

END CASE;

END IF;

END PROCESS;

END behavioral;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

45

IMPLEMENTATION - DATA SUBSYSTEM

n-bit register x to store x and a 2n-bit register z to store z

n-bit register y to store y

A module to generate x 2

n

A module to generate (x 2

n

) y

i

A module to perform addition

(x 2

8

) y

i

x x x x x x x x 0 0 0 0 0 0 0 0

z[i] z z z z z z z z z z z z z z z z

A module to perform multiplication by 1/2 and load the result in z

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

46

DATA SUBSYSTEM: CONTROL SIGNALS

ldX,ldY,ldZ for loading x,y,z, respectively

shY for right-shifting y

clrZ for loading 0 into z

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

47

DATA SUBSYSTEM: BEHAVIORAL DESCRIPTION

ENTITY multdata_bhv IS

GENERIC(n : NATURAL := 16); -- number of bits

PORT (xin,yin : IN UNSIGNED(n-1 DOWNTO 0); -- data inputs

ldX,ldY,ldZ : IN BIT; -- control signals

shY,clrZ : IN BIT; -- control signals

zout : OUT UNSIGNED(2*n-1 DOWNTO 0); -- data output

clk : IN BIT);

END multdata_bhv;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

48

ARCHITECTURE behavioral OF multdata_bhv IS

SIGNAL x,y : UNSIGNED(n-1 DOWNTO 0) ; -- registers

SIGNAL z : UNSIGNED(2*n-1 DOWNTO 0);

BEGIN

PROCESS(clk)

VARIABLE zero_2n : UNSIGNED(2*n-1 DOWNTO 0); -- vector constant 0

VARIABLE scale : UNSIGNED(n-1 DOWNTO 0);

VARIABLE add_out : UNSIGNED(2*n DOWNTO 0);

BEGIN

zero_2n:= (OTHERS =>0);

scale := (OTHERS =>0);

IF (clkEVENT AND clk = 1) THEN

IF (ldX = 1) THEN x <= xin; END IF;

IF (ldY = 1) THEN y <= yin; END IF;

IF (y(0) =0) THEN

add_out := 0 & z;

ELSE

add_out := (0 & z) + (0 & x & scale);

END IF;

IF (ldZ = 1) THEN

z <= add_out(2*n DOWNTO 1);

zout <= add_out(2*n DOWNTO 1);

END IF;

IF (clrZ= 1) THEN z <= zero_2n; END IF;

IF (shY = 1) THEN y <= 0 & y(n-1 DOWNTO 1); END IF;

END IF; END PROCESS; END behavioral;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

49

DATA SUBSYSTEM: STRUCTURAL DESCRIPTION

ldX

ldZ

clrZ

xin yin

Shift register

ldY

shY

y_0

Register

Register

AND gates

n

n

n

n

n

Adder

c_out add_out

n-1

X Y

Z

(clock not shown)

0

zreg_out

2n

2n

n

zreg_in

xreg_out

and_out

VAND

ADD

2n

zout

Figure 13.25: DATA SUBSYSTEM

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

50

ENTITY multdata_str IS

GENERIC(n : NATURAL := 16); -- number of bits

PORT (xin,yin : IN UNSIGNED(n-1 DOWNTO 0); -- data inputs

ldX,ldY,ldZ : IN BIT; -- control signals

shY,clrZ : IN BIT; -- control signals

zout : OUT UNSIGNED(2*n-1 DOWNTO 0); -- data output

clk : IN BIT);

END multdata_str;

ARCHITECTURE structural OF multdata_str IS

SIGNAL add_out, xreg_out, and_out: BIT_VECTOR(n-1 DOWNTO 0);

SIGNAL c_out, y_0 : BIT;

SIGNAL zreg_out : BIT_VECTOR(2*n-1 DOWNTO 0);

SIGNAL zreg_in : BIT_VECTOR(2*n-1 DOWNTO 0);

SIGNAL clr : BIT;

BEGIN

zreg_in <= c_out & add_out & zreg_out(n-1 DOWNTO 1);

X : ENTITY reg PORT MAP (xin,ldX,xreg_out,clk);

Y : ENTITY shiftreg PORT MAP (yin,ldY,shY,y_0,clk);

Z : ENTITY regclr PORT MAP (zreg_in,ldZ,clrZ,zreg_out,clk);

VAND: ENTITY vectorand PORT MAP (xreg_out,y_0,and_out);

ADD: ENTITY adder_pos PORT MAP (zreg_out(2*n-1 DOWNTO n),

and_out,0,add_out,c_out);

END structural;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

51

STRUCTURAL DESCRIPTION OF MULTIPLIER

Data

subsystem

Control

subsystem

xin

yin

start

zout

done clk

n

n

2n

ldX

ldY

ldZ

shY

clrZ

clk

Figure 13.26: MULTIPLIER SCHEME

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

52

ENTITY multiplier IS

GENERIC(n : NATURAL:= 16); -- number of bits in operands

PORT (start : IN BIT ;

xin,yin: IN UNSIGNED(n-1 DOWNTO 0);

clk : IN BIT ;

zout : OUT UNSIGNED(2*n-1 DOWNTO 0);

done : OUT bit);

END multiplier;

ARCHITECTURE structural OF multiplier IS

SIGNAL ldX,ldY,ldZ,clrZ,shY: BIT;

BEGIN

U1: ENTITY multdata_bhv

PORT MAP (xin,yin,ldX,ldY,ldZ,shY,clrZ,zout,clk);

U2: ENTITY multctrl

PORT MAP (start,ldX,ldY,ldZ,shY,clrZ,done,clk);

END structural;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

53

CONTROL SUBSYSTEM

idle

setup

start=0

done = 1

controls = 00000

active,

count=0

active,

count=1

active,

count=n-1

done = 0

controls = 11001

controls = 00110 controls = 00110 controls = 00110

controls =(ldX,ldY,ldZ,shY,clrZ)

start=1

Figure 13.27: STATE DIAGRAM FOR MULTIPLIER CONTROL SUBSYSTEM.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

54

CONTROL SUBSYSTEM: BEHAVIORAL DESCRIPTION

ENTITY multctrl IS

GENERIC(n: NATURAL := 16); -- number of bits

PORT (start : IN BIT; -- control input

ldX,ldY,ldZ: OUT BIT; -- control signals

shY, clrZ : OUT BIT; -- control signals

done : OUT BIT; -- control output

clk : IN BIT);

END multctrl;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

55

ARCHITECTURE behavioral OF multctrl IS

TYPE stateT IS (idle,setup,active);

SIGNAL state : stateT:= idle;

SIGNAL count : NATURAL RANGE 0 TO n-1;

BEGIN

PROCESS (clk) -- transition function

BEGIN

IF (clkEVENT AND clk = 1) THEN

CASE state IS

WHEN idle => IF (start = 1) THEN state <= setup;

ELSE state <= idle ;

END IF;

WHEN setup => state <= active; count <= 0;

WHEN active => IF (count = (n-1)) THEN

count <= 0; state <= idle ;

ELSE

count <= count+1; state <= active;

END IF;

END CASE;

END IF;

END PROCESS;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

56

PROCESS (state,count) -- output function

VARIABLE controls: BitVector(5 DOWNTO 0);

-- code = (ldX,ldY,ldZ,shY,clrZ)

BEGIN

CASE state IS

WHEN idle => controls := "100000";

WHEN setup => controls := "011001";

WHEN active => controls := "000110";

END CASE;

done <= controls(5);

ldX <= controls(4); ldY <= controls(3); ldZ <= controls(2);

shY <= controls(1); clrZ<= controls(0);

END PROCESS;

END behavioral;

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

57

CYCLE TIME AND MULTIPLICATION TIME

CYCLE TIME

t

r

: the delay of the registers to produce stable outputs. This

includes the setup delay and the propagation delay.

t

buf

: the delay of the buer required by the load on y

0

.

t

and

: the delay of the and gates.

t

add

: the delay of the adder.

EXECUTION TIME: n + 2 cycles:

one cycle in the idle state,

one cycle in the setup state,

n cycles for the iterations.

Introduction to Digital Systems 13 Register-transfer Level (RTL) Systems

You might also like

- Control Tutorials For MATLAB and Simulink - Introduction - PID Controller DesignDocument15 pagesControl Tutorials For MATLAB and Simulink - Introduction - PID Controller DesignSengottu VelusamyNo ratings yet

- Control Logic DesignDocument40 pagesControl Logic Designrameshaarya9980% (5)

- VHDL 4 RTL ModelsDocument33 pagesVHDL 4 RTL ModelsNguyễn Minh NghĩaNo ratings yet

- Digital PID Controllers: Different Forms of PIDDocument11 pagesDigital PID Controllers: Different Forms of PIDสหายดิว ลูกพระอาทิตย์No ratings yet

- Experiment No 14 2018 BatchDocument14 pagesExperiment No 14 2018 BatchHafeez AliNo ratings yet

- Control System Toolbox For Matlab: IntroDocument12 pagesControl System Toolbox For Matlab: IntroMikaNo ratings yet

- Custom Single Purpose Processor DesignDocument24 pagesCustom Single Purpose Processor DesignAar Kay GautamNo ratings yet

- To Show Using MATLAB: Root Locus and PID Controller ElaborationDocument6 pagesTo Show Using MATLAB: Root Locus and PID Controller ElaborationAbdul HaseebNo ratings yet

- Write The VHDL Code That Describe: Bit CountDocument31 pagesWrite The VHDL Code That Describe: Bit CountMad Hatter MercuryNo ratings yet

- Lab Report 4 PDFDocument15 pagesLab Report 4 PDF20pwmct0739No ratings yet

- An Integer Square Root Algorithm: Example 24Document10 pagesAn Integer Square Root Algorithm: Example 24psomasalNo ratings yet

- MATLAB and Its Control ToolboxDocument41 pagesMATLAB and Its Control ToolboxzkqasimNo ratings yet

- Clase Diseño Por Medio Del LGR Usando MatlabDocument42 pagesClase Diseño Por Medio Del LGR Usando MatlabJesus Tapia GallardoNo ratings yet

- L11 RTL SystemsDocument35 pagesL11 RTL SystemsusitggsipuNo ratings yet

- Lab - Manual - Soft - Computing - PDFDocument39 pagesLab - Manual - Soft - Computing - PDFpradeep mahateNo ratings yet

- DSD PPT Usr and CN and Odd DividerDocument22 pagesDSD PPT Usr and CN and Odd Dividerece19637ec003No ratings yet

- Atienza Lab3Document18 pagesAtienza Lab3Marvin AtienzaNo ratings yet

- Lab 4 ReportDocument16 pagesLab 4 Report20pwmct0739No ratings yet

- Intro Vhdl1Document30 pagesIntro Vhdl1pandaros000No ratings yet

- Ds First LatestDocument31 pagesDs First LatestZohaib KhanNo ratings yet

- Lab 06Document7 pagesLab 06Andy MeyerNo ratings yet

- Design of A PPM Modulator With VHDLDocument10 pagesDesign of A PPM Modulator With VHDLMarcos Guerra MedinaNo ratings yet

- Systemverilog - Lecture 1Document62 pagesSystemverilog - Lecture 1Shilpa ReddyNo ratings yet

- ACS PracticalFile IshaVerma PDFDocument23 pagesACS PracticalFile IshaVerma PDFDibyendu KarmakarNo ratings yet

- Control ReportDocument15 pagesControl ReportKenshow Large50% (2)

- Program 1: Write A Program Using MATLAB To Plot Pole Zero Map While Transfer Function Is GivenDocument21 pagesProgram 1: Write A Program Using MATLAB To Plot Pole Zero Map While Transfer Function Is GivenShruti BhatnagarNo ratings yet

- Soc11 07 CodesignDocument50 pagesSoc11 07 Codesignswapna revuriNo ratings yet

- Machine Problem 4Document12 pagesMachine Problem 4JERUELNo ratings yet

- VHDL Processes: Cwru Eecs 318Document24 pagesVHDL Processes: Cwru Eecs 318KarThikNo ratings yet

- Ovation Advanced Control Algorithms: PredictorDocument10 pagesOvation Advanced Control Algorithms: PredictorMuhammad UsmanNo ratings yet

- Presented By: K.Praveen V.Sathish Kumar A.Yasar Arafath R.VenkateshwaranDocument32 pagesPresented By: K.Praveen V.Sathish Kumar A.Yasar Arafath R.Venkateshwaranprkg870% (1)

- EEE 70 Advanced Topics in Logic Design: Read Before ClassDocument30 pagesEEE 70 Advanced Topics in Logic Design: Read Before ClassPraveen MeduriNo ratings yet

- Sequential Circuit Design Using PLDsDocument8 pagesSequential Circuit Design Using PLDsJacob ChakoNo ratings yet

- Experiment No.1: Introduction To Lti Representation and Transfer Function ModelDocument7 pagesExperiment No.1: Introduction To Lti Representation and Transfer Function ModelIra CervoNo ratings yet

- Addition / Subtraction: Parts Chapters IDocument103 pagesAddition / Subtraction: Parts Chapters ITooba Sami ArifeenNo ratings yet

- ET2063 Mechatronics-ReportDocument28 pagesET2063 Mechatronics-Reportmahsanorion247No ratings yet

- EE208: Level II Control Systems Defining Transfer Functions in MatlabDocument7 pagesEE208: Level II Control Systems Defining Transfer Functions in Matlabanyany111111No ratings yet

- Acs Pract File 1Document27 pagesAcs Pract File 1deepanshumehalawat07No ratings yet

- Experiment No.1 Time Response of First Order System: 1.matlab ProgramDocument5 pagesExperiment No.1 Time Response of First Order System: 1.matlab ProgramDarshan DeepuNo ratings yet

- NI Tutorial 6463 enDocument6 pagesNI Tutorial 6463 enAmaury BarronNo ratings yet

- sc554 2014 Lecture09Document34 pagessc554 2014 Lecture09tharindu12No ratings yet

- Experiment 26 Shift Registers: ObjectivesDocument6 pagesExperiment 26 Shift Registers: ObjectivesPieyka ShafikaNo ratings yet

- Control Systems Design ToolsDocument9 pagesControl Systems Design ToolsTeguh SantosoNo ratings yet

- Note - 13 - Intro To Digital Control SystemDocument7 pagesNote - 13 - Intro To Digital Control SystemVimal Raj DNo ratings yet

- Unit 3Document24 pagesUnit 3Raja BenitaNo ratings yet

- Control System 1 PDFDocument72 pagesControl System 1 PDFElangoNo ratings yet

- Digital Filters in VHDL LabDocument5 pagesDigital Filters in VHDL LabAli AhmadNo ratings yet

- CSD Experiment No 8Document9 pagesCSD Experiment No 8Gourav PalNo ratings yet

- Combinational and Sequential Circuits DesignDocument25 pagesCombinational and Sequential Circuits DesignJadesh ChandaNo ratings yet

- VHDL Lab ProgramsDocument51 pagesVHDL Lab ProgramsvenkiNo ratings yet

- Chap6 PDFDocument24 pagesChap6 PDFSrinivas CherukuNo ratings yet

- ps3 (1) From MAE 4780Document5 pagesps3 (1) From MAE 4780fooz10No ratings yet

- Repetitive ControlDocument22 pagesRepetitive ControlShri KulkarniNo ratings yet

- Lab9 VHDLDocument8 pagesLab9 VHDLFasli CoolNo ratings yet

- Project Based Learning IcsDocument14 pagesProject Based Learning IcsAvinash YadavNo ratings yet

- Digital Logic DesignDocument106 pagesDigital Logic DesignSuraj KumarNo ratings yet

- Nonlinear Control Feedback Linearization Sliding Mode ControlFrom EverandNonlinear Control Feedback Linearization Sliding Mode ControlNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.From EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.No ratings yet