Professional Documents

Culture Documents

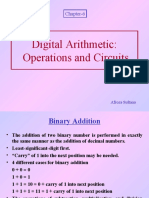

Operation Carry in A B 00 01 Result 10 Adder

Operation Carry in A B 00 01 Result 10 Adder

Uploaded by

Shuvra SahaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Operation Carry in A B 00 01 Result 10 Adder

Operation Carry in A B 00 01 Result 10 Adder

Uploaded by

Shuvra SahaCopyright:

Available Formats

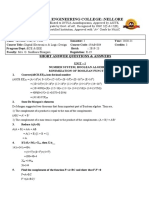

A 1-bit ALU

operation Carry in A B 00 01 Adder 10 Result

Carry out

Understand how this circuit works. Then look at the diagram of the 32-bit ALU in p.235.

Need to add one more input to the mux to implement slt

Converting an adder into a subtractor

A-B = =

(here - means arithmetic subtraction)

A + 2s complement of B A + 1s complement of B + 1

operation Carry in A B 00 01 0 1 Adder 10 Result

11 B invert Carry out

1-bit adder/subtractor

For subtraction, B invert = 1 and Carry in = 1

1-bit ALU for MIPS Assume that it has the instructions add, sub, and, or, slt.

operation Carry in A B 00 01 0 1 Less B invert add 10 Result

11 Set Carry out

Less will be used to detect if the 32-bit number A is less than the 32-bit number B. See the next page.

If A < B then Set = 1 else Set = 0

A 32-bit ALU for MIPS

B invert A0 B0 Less

C in

ALU

Cout

operation

C in A1 B1 0

ALU

Cout

.. ..

A31 B31 0

ALU

Cout

Result 31 Set overflow

Fast Carry Propagation

During addition, the carry can trigger a ripple from the LSB to the MSB. This slows down the speed of addition.

01111111111111111111 00000000000000001

How to overcome this? Consider the following:

c1

= = =

a0.b0 + a0.c0 + b0.c0 a0.b0 + (a0 + b0).c0 g0 + p0.c0 (where g0 = a0.b0, p0 = a0+b0)

c2

= = =

a1.b1 + (a1 + b1).c1 g1 + p1.(g0 + p0.c0) g1 + p1.g0 + p1.p0.c0

c4

g3 + p3.g2 + p3.p2.g1 + p3.p2.p1.g0 + p3.p2.p1.p0.c0

c32 = ?

It will be complex. But you can use a two-level circuit to generate c4. This will expedite addition. But it is impractical due to the complexity.

Practical circuits use a two-phase approach. See the example of the 16-bit adder, designed from four 4-bit adders in p.246. Let

G0 = g3 + p3.g2 + p3.p2.g1 + p3.p2.p1.g0 G1 = g7 + p7.g6 + p7.p6.g5 + p7.p6.p5.g4 G2 = g11 + p11.g10 + p11.p10.g9 + p11.p10.p9.g8 G3 = g15 + p15.g14 + p15.p14.g13 + p15.p14.p13.g12

P0 = p3.p2.p1.p0 P1 = p7.p6.p5.p4 P2 = p11.p10.p9.p8 P3 = p15.p14.p13.p12

Then

C1 = G0 + P0.c0 C2 = G1 + P1.G0 + P1.P0.c0 C3 = G2 + P2.G1 + P2.P1.G0 + P2.P1.P0.c0 C4 = G3 + P3.G2 + P3.P2.G1 + P3.P2.P1.G0 + P3.P2.P1.P0.c0

This is implemented in the carry look-ahead adder.

See the figure in p. 246 of your textbook.

How much faster is the carry look-ahead adder?

Multiplication

Be familiar with shift operations first

0 1 1 1 0 1 0 0 1 0 1 0 0 0 1 1

Shift right

0 0 1 1 1 0 1 0

shift left

0 1 0 0 0 1 1 1

1 0 0 1 0 1 0 1 1 0 0 1 0 0 0 0 1 0 1 1 0 1

(multiplicand) (multiplier)

0 1 0 0 0 0 0 1 0

See the diagrams in page 254 and 255 of your textbook, and learn how a multiplier works.

Floating point representation

A scheme for representing a number very small to very large. It is widely used in the scientific world. Consider, the floating point number

Exponent E +/- x x x x

significand F y y y y y y y y y y y y (+/-) 1. yyyyyyyyyyyy x 10xxxx (+/-) 1. yyyyyyyyyyyy x 2xxxx

In decimal it means In binary, it means (The 1 is implied)

IEEE 754 representation

s xxxxxxxx yyyyyyyyyyyyyyyyyyyyyyy

Single precision

23 bits

+127 128

Largest = 1.111 x 2

2 x 10 +38

Smallest = 1.000 x 2

1 x 10 -38

These can be positive and negative, depending on s.

IEEE 754 double precision (64 bits)

S 1

exponent 11 bits

significand 52 bits 1.111 x 2

+1023 1024

Largest = Smallest =

1.000 X 2

What do you mean by overflow and underflow in FP?

An overflow occurs when the number if too large to fit in the frame. An underflow occurs when the number is too small to fit in the given frame.

Biased Representation

Exponent = 11111111 Exponent = 00000000

2 1 20

awkward for sorting

However, to facilitate sorting, IEEE 754 treats 000 as the most negative, and 1,11..1 as the most positive exponent. This amounts to using a bias of 127.

00000000 (=-127)

11111111 (=+128)

bias +127 smallest largest

So, value = (1) x (1+significand) x 2

(exponent bias)

Practice simple conversions from fraction to FP.

Floating Point Addition

Example using decimal

A = 9.999 x 10 1, B = 1.610 x 10 1, A+B =?

Step 1. Align the smaller exponent with the larger one. B = 0.0161 x 101 = 0.016 x 101 (round off) Step 2. Add significands 9.999 + 0.016 = 10.015, so A+B = 10.015 x 101 Step 3. Normalize A+B = 1.0015 x 102 Step 4. Round off A+B = 1.002 x 102

Now, try to add 0.5 and 0.4375 in binary.

Floating Point Multiplication

Example using decimal A = 1.110 x 1010, B = 9.200 x 10-5 A x B =?

Step 1. Exponent of A x B = 10 + (-5) = -5 Step 2. Multiply significands 1.110 x 9.200 = 10.212000 Step 3. Normalize the product 10.212 x 10-5 = 1.0212 x 10-5 Step 4. Round off A x B = 1.021 x 10-5 Step 5. Decide the sign of A x B (+ x + = +)

So, A x B = + 1.021 x 10-5

Now try to multiply 0.5 with 0.4375 in binary. Use IEEE 754 format.

You might also like

- User Manual BX V293Document82 pagesUser Manual BX V293sesturlodNo ratings yet

- Adva - Training - FSP 150CC-GE20x R4.x Course - 2 - AdministrationDocument37 pagesAdva - Training - FSP 150CC-GE20x R4.x Course - 2 - Administrationgerritrensink100% (2)

- QNX Neutrino ArchitectureDocument342 pagesQNX Neutrino Architecturecbhanukiranneo100% (1)

- 2.5.5 Packet Tracer - Configure Initial Switch SettingsDocument5 pages2.5.5 Packet Tracer - Configure Initial Switch SettingsHeriyanto TanNo ratings yet

- Firewall - pfBlockerNG - Top 20 PDFDocument3 pagesFirewall - pfBlockerNG - Top 20 PDFAnonymous oQGQn7eSNo ratings yet

- CSC340 - HW3Document28 pagesCSC340 - HW3Daniel sNo ratings yet

- KmapDocument38 pagesKmapPECMURUGANNo ratings yet

- Unit 2Document38 pagesUnit 2toshgangwarNo ratings yet

- ICS SolutionDocument7 pagesICS SolutionAnonymous ubAhWPIVjNo ratings yet

- ARITHMETIC and LOGIC UNIT - in This Lecture, We Will Examine HowDocument12 pagesARITHMETIC and LOGIC UNIT - in This Lecture, We Will Examine HowbokadashNo ratings yet

- Tutorial 7 SolutionsDocument6 pagesTutorial 7 Solutionssama abd elgelilNo ratings yet

- DELD - Short Answer Questions and AnswersDocument23 pagesDELD - Short Answer Questions and AnswersPasupuleti Venkata RamanaNo ratings yet

- Arithmetic For Computers: Chapter-4Document67 pagesArithmetic For Computers: Chapter-4Jahangir AlamNo ratings yet

- Chapter 04Document33 pagesChapter 04Iqbal Ashfaq Joiya100% (1)

- Combinational CircuitsDocument68 pagesCombinational Circuitsavita207No ratings yet

- Arithmetic Logic Unit (ALU) MiniprojectDocument3 pagesArithmetic Logic Unit (ALU) MiniprojectLuis AuquillaNo ratings yet

- Review - Canonical Forms: Sum of Products Product of SumsDocument15 pagesReview - Canonical Forms: Sum of Products Product of SumsMuhammad AtifNo ratings yet

- Ddco Unit-5 NotesDocument14 pagesDdco Unit-5 NotesNIKHIL NIKHINo ratings yet

- Ee188 Final Batu PlazaDocument16 pagesEe188 Final Batu Plazameytz102No ratings yet

- CS M151B / EE M116C: Computer Systems ArchitectureDocument33 pagesCS M151B / EE M116C: Computer Systems ArchitecturetinhtrilacNo ratings yet

- Computer ArithmeticsDocument78 pagesComputer ArithmeticsBleron MorinaNo ratings yet

- Cominational and Sequential CircuitsDocument28 pagesCominational and Sequential CircuitsKennedy MutaiNo ratings yet

- Comb CircDocument63 pagesComb Circm.sangeethjaNo ratings yet

- P05-Digital Systems - Lecture - 17-20Document46 pagesP05-Digital Systems - Lecture - 17-20JAINo ratings yet

- Subtract SubtractorDocument3 pagesSubtract SubtractorJannel SalvaNo ratings yet

- Introduction To Digital Design: Chapter 2: Combinational Logic CircuitsDocument20 pagesIntroduction To Digital Design: Chapter 2: Combinational Logic CircuitsRawan F HamadNo ratings yet

- 2marks With AnswerDocument46 pages2marks With AnswerhariNo ratings yet

- Floating Point AluDocument11 pagesFloating Point Aluthuan phamNo ratings yet

- 03 Numeric BasicsDocument68 pages03 Numeric BasicsGîrju AndradaNo ratings yet

- Arth CirDocument105 pagesArth Cirnoor_dcetNo ratings yet

- Digital Design LaboratoryDocument10 pagesDigital Design Laboratorykarths22No ratings yet

- 09-Addition MultiplicationDocument27 pages09-Addition MultiplicationJbanfulNo ratings yet

- As 00001030Document32 pagesAs 00001030Akshat soniNo ratings yet

- Sol 5Document13 pagesSol 5ee206023No ratings yet

- ArithmeticDocument43 pagesArithmeticzatharoxNo ratings yet

- Chapter 03Document17 pagesChapter 03Talha YasinNo ratings yet

- Digital Arithmetic: Operations and Circuits: Chapter-6Document44 pagesDigital Arithmetic: Operations and Circuits: Chapter-6Samina TohfaNo ratings yet

- PorjDocument4 pagesPorjTaimenTaiNo ratings yet

- Cpe626 MultipliersDocument37 pagesCpe626 Multipliersmdzakir_hussainNo ratings yet

- Digital Logic Design 230201 (Dc-1) : PPTS: Unit - 1Document50 pagesDigital Logic Design 230201 (Dc-1) : PPTS: Unit - 1Girraj DohareNo ratings yet

- CS205 Assignment1 SolutionDocument7 pagesCS205 Assignment1 SolutionjohnnybyzhangNo ratings yet

- Note5 DigitalDocument63 pagesNote5 DigitalChintala Thrinadh 21BEE1006No ratings yet

- Practice Problems 12Document32 pagesPractice Problems 12suduku007No ratings yet

- Binary Numbers and ArithmeticDocument50 pagesBinary Numbers and ArithmeticRohit MaheshwariNo ratings yet

- DD Notes Section1Document23 pagesDD Notes Section1mabuhzaimaNo ratings yet

- Sistem Bilangan: Oleh: Moch Nur PurnamaDocument36 pagesSistem Bilangan: Oleh: Moch Nur PurnamaSmartcomputer SanggauNo ratings yet

- CC 2 Unit 2Document10 pagesCC 2 Unit 2SandipNo ratings yet

- C++ Bitwise OperatorsDocument19 pagesC++ Bitwise OperatorsÄbûýé SêñdèkúNo ratings yet

- Carry-Propagate AdderDocument6 pagesCarry-Propagate AddersaurabhNo ratings yet

- Lecture 5Document21 pagesLecture 5kmohey101No ratings yet

- ALUDocument7 pagesALUmonsour888No ratings yet

- EC3352_DSD_UNIT_IDocument13 pagesEC3352_DSD_UNIT_IPranav ShuklaNo ratings yet

- Chapter 4Document45 pagesChapter 4Mohammad Ahmed ChoudhryNo ratings yet

- Pooja VashisthDocument51 pagesPooja VashisthApurva SinghNo ratings yet

- Simple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialDocument3 pagesSimple Shift-Add Multiplier: ELE 4550 ASIC Technologies Project TutorialramyarakiNo ratings yet

- ALU (3) - Division Algorithms: Humboldt-Universität Zu BerlinDocument29 pagesALU (3) - Division Algorithms: Humboldt-Universität Zu BerlinRajarshi PoddarNo ratings yet

- Arithmetic For ComputersDocument48 pagesArithmetic For ComputersAdip ChyNo ratings yet

- Computer ArchitectureDocument27 pagesComputer ArchitectureMd. Atikur RahmanNo ratings yet

- Logic Circuits PDFDocument81 pagesLogic Circuits PDFÄlî VàráNo ratings yet

- Domains and RangeDocument15 pagesDomains and RangeIda BerlianNo ratings yet

- Let's Practise: Maths Workbook Coursebook 7From EverandLet's Practise: Maths Workbook Coursebook 7No ratings yet

- XCH - Exchange - AVR AssemblerDocument1 pageXCH - Exchange - AVR AssemblerRegard'sDexterZacheusNo ratings yet

- Ccmsetup CcmevalDocument5 pagesCcmsetup Ccmevalr_kruijerNo ratings yet

- Acer Aspire 5 A515 - Built-In SSD Not Found - Acer CommunityDocument8 pagesAcer Aspire 5 A515 - Built-In SSD Not Found - Acer CommunitymtomescuNo ratings yet

- TNPM Bulk CollectorDocument9 pagesTNPM Bulk CollectorKristopher SandersNo ratings yet

- Office Deployment ToolDocument5 pagesOffice Deployment Toolsam2976No ratings yet

- Us 21 The Unbelievable Insecurity of The Big Data Stack An Offensive Approach To Analyzing Huge and Complex Big Data InfrastructuresDocument48 pagesUs 21 The Unbelievable Insecurity of The Big Data Stack An Offensive Approach To Analyzing Huge and Complex Big Data InfrastructuresIgnacio Tlaxqueño GuerreroNo ratings yet

- Siemens S7-200 PPI: HMI SettingDocument7 pagesSiemens S7-200 PPI: HMI SettingAbdullahNo ratings yet

- CF-53mk3 Win7 English 64bit DriverInstallationGuideDocument3 pagesCF-53mk3 Win7 English 64bit DriverInstallationGuideAndrey PolupanNo ratings yet

- Winsock ProgrammingDocument12 pagesWinsock Programmingvivekkumars100% (1)

- HUB, Switch, Router PDFDocument11 pagesHUB, Switch, Router PDFDiana Larisa ArdeleanuNo ratings yet

- Flow Document DMDocument34 pagesFlow Document DMPSKNo ratings yet

- CSC 101 - Operating System-Week1Document10 pagesCSC 101 - Operating System-Week1shadowbee 47No ratings yet

- ECM-5410 5th Manual PDFDocument147 pagesECM-5410 5th Manual PDFEduard Barrios G.No ratings yet

- 2.4.1.2 Packet Tracer - Skills Integration Challenge - ILMDocument3 pages2.4.1.2 Packet Tracer - Skills Integration Challenge - ILMAva BarramedaNo ratings yet

- Cisco Firepower Management CenterDocument16 pagesCisco Firepower Management CenterAhmad BayhakiNo ratings yet

- CHAPTER 04 (Network)Document40 pagesCHAPTER 04 (Network)Mihirete BantegegnNo ratings yet

- NGÂN HÀ BTEC-CO1 - LUẬN VĂNDocument23 pagesNGÂN HÀ BTEC-CO1 - LUẬN VĂNNgân HàNo ratings yet

- Canon Ir2018 Ir2030 Ir2018i Ir2022i Ir2025i Ir2030i BrochureDocument5 pagesCanon Ir2018 Ir2030 Ir2018i Ir2022i Ir2025i Ir2030i BrochureciphardNo ratings yet

- Mcafee Endpoint Encryption For Files and FoldersDocument2 pagesMcafee Endpoint Encryption For Files and FoldersEcho SanakyNo ratings yet

- SHCDocument2 pagesSHCMuhammad Afran TitoNo ratings yet

- PythonPackagesandData AccesssDocument4 pagesPythonPackagesandData Accesssroy.scar2196No ratings yet

- Epson RC PL 70 Users Guide-Rc700a Rc90 T 257 365Document109 pagesEpson RC PL 70 Users Guide-Rc700a Rc90 T 257 365Nguyen TiNo ratings yet

- Tomcat Performance TuningDocument35 pagesTomcat Performance Tuningarunds1984100% (1)

- Mini Link 6600Document2 pagesMini Link 6600amr_karimm67% (9)

- Blue Coat K9 Web ProtectionDocument3 pagesBlue Coat K9 Web Protectionpacometal8No ratings yet