Professional Documents

Culture Documents

IC 4052 Datasheet

IC 4052 Datasheet

Uploaded by

Ganjar KurniawanCopyright:

Available Formats

You might also like

- 4052 UnisonicTechnologiesDocument6 pages4052 UnisonicTechnologiessigit raharjoNo ratings yet

- ANALOG MULTIPLEXERS/ DEMULTIPLEXERS - Part Number: UTC4053Document6 pagesANALOG MULTIPLEXERS/ DEMULTIPLEXERS - Part Number: UTC4053shawnleegabriel100% (1)

- Datasheet 4051Document6 pagesDatasheet 4051Jui KulkarniNo ratings yet

- TC75S102F_datasheet_en_20200605Document7 pagesTC75S102F_datasheet_en_20200605parsastar2010No ratings yet

- CD4029BC Presettable Binary/Decade Up/Down Counter: General Description FeaturesDocument9 pagesCD4029BC Presettable Binary/Decade Up/Down Counter: General Description FeaturesSantiago SerranoNo ratings yet

- CD4069Document5 pagesCD4069abdullahNo ratings yet

- CD4069 PDFDocument5 pagesCD4069 PDFPedro IsmaelNo ratings yet

- TC4538BP/TC4538BF Dual Precision Retriggerable/Resettable Monostable MultivibratorDocument9 pagesTC4538BP/TC4538BF Dual Precision Retriggerable/Resettable Monostable MultivibratorAmirNo ratings yet

- HCF4053M013TRDocument11 pagesHCF4053M013TRVasyaNo ratings yet

- HCF4053M013TRDocument11 pagesHCF4053M013TRVasyaNo ratings yet

- TC4521BP 24-Stage Frequency DividerDocument9 pagesTC4521BP 24-Stage Frequency DividerAmirNo ratings yet

- Rohm ML8511 00FCZ05B Datasheet PDFDocument8 pagesRohm ML8511 00FCZ05B Datasheet PDFarijit_ghosh_18No ratings yet

- TC4066BF Datasheet en 20170718 PDFDocument10 pagesTC4066BF Datasheet en 20170718 PDFricardo augustoNo ratings yet

- CD4069 DatasheetDocument7 pagesCD4069 DatasheetАна СтојковиќNo ratings yet

- TC4538BP Datasheet en 20140301Document9 pagesTC4538BP Datasheet en 20140301Strati YovchevNo ratings yet

- TC4081BF Datasheet en 20140301Document7 pagesTC4081BF Datasheet en 20140301YaKoviToNo ratings yet

- TC4584BP, TC4584BF, TC4584BFN: TC4584B Hex Schmitt TriggerDocument8 pagesTC4584BP, TC4584BF, TC4584BFN: TC4584B Hex Schmitt TriggerAmirNo ratings yet

- CD4016Document8 pagesCD4016api-3708997100% (1)

- Nte 4053Document4 pagesNte 4053Codinasound CaNo ratings yet

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocument6 pagesCD40106BC Hex Schmitt Trigger: General Description FeaturesHABUMUGISHA DieudonneNo ratings yet

- TC5565Document9 pagesTC5565MiniLabNo ratings yet

- N2576SG 5Document5 pagesN2576SG 5elnegritoheberNo ratings yet

- TC4093BP, TC4093BF: TC4093B Quad 2-Input NAND Schmitt TriggersDocument7 pagesTC4093BP, TC4093BF: TC4093B Quad 2-Input NAND Schmitt TriggersMohammed Al gobariNo ratings yet

- TC4520BP, TC4520BF: TC4520B Dual Binary Up CounterDocument10 pagesTC4520BP, TC4520BF: TC4520B Dual Binary Up CounterChaba Leyva HernándezNo ratings yet

- TC4081BP, TC4081BF, TC4081BFN: TC4081B Quad 2-Input AND GateDocument8 pagesTC4081BP, TC4081BF, TC4081BFN: TC4081B Quad 2-Input AND GateAmirNo ratings yet

- Is Now Part ofDocument10 pagesIs Now Part ofMatias GonzalezNo ratings yet

- Unisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersDocument7 pagesUnisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersNaresh KsNo ratings yet

- TC4013BP, TC4013BF: TC4013B Dual D-Type Flip FlopDocument8 pagesTC4013BP, TC4013BF: TC4013B Dual D-Type Flip Flopal nakheel electronicsNo ratings yet

- TC4066BP, TC4066BF, TC4066BFN, TC4066BFT: TC4066B Quad Bilateral SwitchDocument11 pagesTC4066BP, TC4066BF, TC4066BFN, TC4066BFT: TC4066B Quad Bilateral SwitchCandelaria CortesNo ratings yet

- Ds Ah 00614087Document20 pagesDs Ah 00614087P Chaayesha Naik 1No ratings yet

- CD4069UBC Inverter Circuits: General Description FeaturesDocument7 pagesCD4069UBC Inverter Circuits: General Description FeaturesvaleriojesusNo ratings yet

- TC4013BP, TC4013BF, TC4013BFN: TC4013B Dual D-Type Flip FlopDocument9 pagesTC4013BP, TC4013BF, TC4013BFN: TC4013B Dual D-Type Flip FlopvanmarteNo ratings yet

- Dual Low Power Operational AmplifierDocument5 pagesDual Low Power Operational Amplifieralex castroNo ratings yet

- TC4011BP, TC4011BF, TC4011BFN, TC4011BFT: TC4011B Quad 2 Input NAND GateDocument10 pagesTC4011BP, TC4011BF, TC4011BFN, TC4011BFT: TC4011B Quad 2 Input NAND GateAlireza RahimiNo ratings yet

- Ic Audio 8002 (2.0W)Document6 pagesIc Audio 8002 (2.0W)napoleon_velasc3617100% (1)

- TC4030BP, TC4030BF, TC4030BFN: TC4030B Quad Exclusive-OR GateDocument8 pagesTC4030BP, TC4030BF, TC4030BFN: TC4030B Quad Exclusive-OR GateAmirNo ratings yet

- TC75S103F Datasheet en 20200922-1927942Document9 pagesTC75S103F Datasheet en 20200922-1927942amin adimiNo ratings yet

- lmr1802g LB eDocument22 pageslmr1802g LB ecarlosibaNo ratings yet

- CD4024BC 7-Stage Ripple Carry Binary Counter: General Description FeaturesDocument6 pagesCD4024BC 7-Stage Ripple Carry Binary Counter: General Description FeaturesGoodLookingPirateNo ratings yet

- Specification For Release: TVS Diode Array WE-TVS SOT143-4LDocument5 pagesSpecification For Release: TVS Diode Array WE-TVS SOT143-4LkapakdoonNo ratings yet

- P14NF12FP - 120V, 14aDocument9 pagesP14NF12FP - 120V, 14aRenatoMaiaNo ratings yet

- TC4040BP, TC4040BF: TC4040B 12 Stage Ripple-Carry Binary Counter/DividersDocument8 pagesTC4040BP, TC4040BF: TC4040B 12 Stage Ripple-Carry Binary Counter/DividersMohammed Al gobariNo ratings yet

- TC4040Document8 pagesTC4040Edgar DauzonNo ratings yet

- Ena 1723Document7 pagesEna 1723Anddo BabbabNo ratings yet

- CD4030M/CD4030C Quad EXCLUSIVE-OR Gate: General Description ApplicationsDocument4 pagesCD4030M/CD4030C Quad EXCLUSIVE-OR Gate: General Description ApplicationsSuper WhippedNo ratings yet

- Datasheet TN6Q04 PDFDocument4 pagesDatasheet TN6Q04 PDFDaniel AvecillaNo ratings yet

- Specification For Release: TVS Diode Array WE-TVS SOT23-6LDocument5 pagesSpecification For Release: TVS Diode Array WE-TVS SOT23-6LAlex LuzNo ratings yet

- TC4069UBP, TC4069UBF, TC4069UBFN, TC4069UBFT: TC4069UB Hex InverterDocument9 pagesTC4069UBP, TC4069UBF, TC4069UBFN, TC4069UBFT: TC4069UB Hex InverterMohammed Al gobariNo ratings yet

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocument6 pagesCD40106BC Hex Schmitt Trigger: General Description FeaturesWellison RodriguesNo ratings yet

- 2SD300C17A4CDocument7 pages2SD300C17A4Csajad hejaziNo ratings yet

- Low Noise, Low Power Op Amp: Features DescriptionDocument28 pagesLow Noise, Low Power Op Amp: Features DescriptionSwapnil BangarNo ratings yet

- Isolated and Regulated 10 WATT Modular DC/DC Converters: SeriesDocument3 pagesIsolated and Regulated 10 WATT Modular DC/DC Converters: SeriesagusnellNo ratings yet

- Features Applications: IN OUT Xout OUT XoutDocument8 pagesFeatures Applications: IN OUT Xout OUT XoutEnéas BaroneNo ratings yet

- Dual Operational Amplifier-Yd4558: Youda Integrated CircuitDocument3 pagesDual Operational Amplifier-Yd4558: Youda Integrated CircuitJúnior Da Silva SantanaNo ratings yet

- HCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsDocument9 pagesHCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsEngin UzunNo ratings yet

- HCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsDocument10 pagesHCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsPendawa SeribuNo ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

IC 4052 Datasheet

IC 4052 Datasheet

Uploaded by

Ganjar KurniawanOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

IC 4052 Datasheet

IC 4052 Datasheet

Uploaded by

Ganjar KurniawanCopyright:

Available Formats

UTC 4052 CMOS

ANALOG MULTIPLEXERS

/DEMULTIPLEXERS

DESCRIPTION

The UTC 4052 analog multiplexers is digitally

–controlled analog switch. The device feature low ON

impedance and very low OFF leakage current. Control

of analog signals up to the complete supply voltage

range can be achieved.

SOP-16

FEATURES

*Triple Diode Protection on Control Inputs

*Switch Function is Break Before Make

*Supply Voltage Range=3.0 Vdc to 18 Vdc

*Analog Voltage Range(VDD-VEE)=3.0 to 18V

*Note:VEE must be≤Vss

*Linearized Transfer Characterisstics

*Low-noise-12nV/√Cycle ,f≥1.0kHz Typical

DIP-16

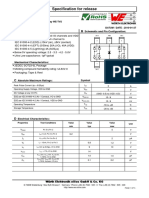

ABSOLUTE MAXIMUM RATINGS*1

PARAMETER SYMBOL RATING UNIT

DC Supply Voltage (Referenced to VEE,Vss≥VEE) VDD -0.5 ~ +18.0 V

Input or Output Voltage (DC or Transient) (Referenced to Vin,Vout -0.5 ~ VDD+0.5

V

Vss for Control Inputs and VEE for switch I/O)

Input Current (DC or Transient) per Control Pin Iin ±10 mA

Switch Through Current ISW ±25 mA

Power Dissipation *2

DIP-16 PD 700 mW

SOP-16 500

Ambient Temperature Range TA -55 ~ +125 °C

Storage Temperature Range Tstg -65 ~ +150 °C

Lead Temperature (8-Second Soldering) TLEAD 260 °C

*1. Maximum Ratings are those values beyond which damage to the device may occur.

*2. Temperature Derating : 7.0 mW/℃ From 65℃ ~ 125℃

UTC UNISONIC TECHNOLOGIES CO., LTD. 1

QW-R502-013,A

UTC 4052 CMOS

Dual 4-Channel Analog

PIN ASSIGMENT

Multiplexer/Demultiplexer

6 INHIBIT

Y0 1 16 VDD

CONTROLS 10 A

X 13

9 B

Y2 2 15 X2

12 X0

14 X1 COMMONS Y 3 14 X1

15 X2 OUT/IN

11 X3

SWITCHES Y3 4 13 X

IN/OUT 1 Y0

Y 9

5 Y1

Y1 5 12 X0

2 Y2

4 Y3

INH 6 11 X3

VDD=PIN16, VSS=PIN8, VEE=PIN7 VEE 7 10 A

Note: Control Inputs referenced to Vss.

Analog Inputs and Outputs reference to VEE. Vss 8 9 B

VEE must be <Vss.

ELECTRICAL CHARACTERISTICS

-55°C 25°C 125°C

PARAMETER SYMBOL TEST CONDITIONS UNIT

MIN MAX MIN TYP*3 MAX MIN MAX

SUPPLY REQUIREMENTS (Voltages Referenced to VEE)

Power Current Per VDD VDD-3.0≥Vss≥VEE 3.0 18 3.0 18 3.0 18 V

Range

Quiescent Current IDDControl Inputs:

Per Package Vin=Vss or VDD,Switch

I/O : VEE≤VI/O≤≤VDD,

and△Vswitch≤500mV *4 µA

VDD=5.0V 5.0 0.005 5.0 150

VDD=10V 10 0.010 10 300

20 0.015 20 600

VDD=15V

Total Supply Current ID(AV) TA=25℃only (The

(Dynamic Plus channel component,

Quiescent, Per (Vin-Vout) /Ron, is not

Package included.) µA

VDD=5.0V (0.07µA/kHz)f+IDD

VDD=10V Typical (0.20µA/kHz)f+IDD

VDD=15V (0.36µA/kHz)f+IDD

CONTROL INPUTS-INHIBIT, A, B, C (Voltages Referenced to Vss)

Low-Level Input VIL Ron=per spec,

Voltage Ioff=per spec

VDD=5.0V 1.5 2.25 1.5 1.5 V

VDD=10V 3.0 4.50 3.0 3.0

VDD=15V 4.0 6.75 4.0 4.0

High-Level Input VIH Ron=per spec,

Voltage Ioff=per spec

VDD=5.0V 3.5 3.5 2.75 3.5 - V

VDD=10V 7.0 7.0 5.50 7.0 -

VDD=15V 11 11 8.25 11 -

UTC UNISONIC TECHNOLOGIES CO., LTD. 2

QW-R502-013,A

UTC 4052 CMOS

-55°C 25°C 125°C

PARAMETER SYMBOL TEST CONDITIONS UNIT

MIN MAX MIN TYP*3 MAX MIN MAX

Input Leakage Iin VDD=15V ,Vin=0 or VDD ±0.1 ±10-5 ±0.1 1.0 µA

Current

Input Capacitance Cin 5.0 7.5 pF

SWITCHES IN/OUT AND COMMONS OUT/IN –X,Y,Z(Voltages Referenced to VEE)

Recommended VI/O Channel On or Off 0 VDD 0 VDD 0 VDD Vpp

Peak-to-Peak

Voltage Into or Out of

the Switch

Recommended Static △Vswitch Channel On 0 600 0 600 0 300 mV

or Dynamic Voltage

Across the Switch *4

(Figure 3)

Output Offset Voo Vin=0V,No Load 10 µV

Voltage

4

ON Resistance Ron △Vswitch≤500mV *

Vin=VIL or VIH (Control),

and Vin=0 to VDD(Switch)

800 250 1050 1200 Ω

VDD=5.0V

VDD=10V 400 120 500 520

VDD=15V 220 80 280 300

△ON Resistance △Ron VDD=5.0V 70 25 70 135

Between Any Two VDD=10V 50 10 50 95

Ω

Channels in the VDD=15V 45 10 45 65

Same Package

Off-Channel Leakage Ioff VDD=15V ,Vin=VIL or VIH ±100 ±0.05 ±100 ±1000

Current(Figure 8) (Control) Channel to

Channel or Any One nA

Channel

Capacitance, CI/O Inhibit=VDD 10 pF

Switch I/O

Capacitance, CO/I Inhibit=VDD 32 pF

Common O/I

Capacitance, CI/O Pins Not Adjacent 0.15 pF

Feedthrough Pins Adjacent 0.47

(Channel Off)

*3. Data labeled “Typ” is not to be used for design purposes, but is intended as an indication of the IC’s potential

*performance.

*4. For voltage drops across the switch (△Vswitch) > 600 mV ( > 300 mV at high temperature), excessive VDD

*current may be drawn, i.e. the current out of the switch may contain both VDD and switch input components. The

*reliability of the device will be unaffected unless the Maximum Ratings are exceeded. (See first page of this data

*sheet.)

UTC UNISONIC TECHNOLOGIES CO., LTD. 3

QW-R502-013,A

UTC 4052 CMOS

ELECTRICAL CHARACTERISTICS *5 (CL = 50 pF, TA = 25℃) (VEE ≤VSS unless otherwise indicated)

*6

PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNIT

Propagation Delay tPLH,tPHL RL=10kΩ

Times(Figure 4) VDD-VEE= 5.0, tPLH,tPHL=(0.17 ns/pF) CL+21.5 ns 30 75

Switch Input to Switch 12 30 ns

VDD-VEE=10, tPLH,tPHL=(0.08 ns/pF) CL+8.0 ns

Output VDD-VEE=15, tPLH,tPHL=(0.06 ns/pF) CL+7.0 ns 10 25

Propagation Delay tPHZ,tPLZ RL=10kΩ,VEE=Vss

Times(Figure 4) tPZH,tPZL Output”1” or “0” to High Impedance, or

Inhibit to Output High Impedance to”1” or “0” Level

300 600 ns

VDD-VEE= 5.0

VDD-VEE=10 155 310

VDD-VEE=15 125 250

Propagation Delay tPLN,tPHL RL=10kΩ,VEE=Vss

Times(Figure 4) VDD-VEE= 5.0 325 650

Control Input to Output 130 260 ns

VDD-VEE=10

VDD-VEE=15 90 180

Second Harmonic RL=10kΩ, f=1kHz, Vin=5Vpp, VDD-VEE=10 0.07 %

Distortion

Bandwidth (Figure 5) BW RL=1kΩ, Vin=1/2(VDD-VEE)p-p, CL=50pF, 17

MHz

20 Log (Vout/Vin)=-3dB, VDD-VEE=10

Off Channel RL=1kΩ, Vin=1/2(VDD-VEE)p-p, Fin=30MHz, -50

Feedthrough Attenuation VDD-VEE=10 dB

(Figure 5)

Channel Separation RL=1kΩ, Vin=1/2(VDD-VEE)p-p, fin=3.0MHz, -50

(Figure 6) dB

VDD-VEE=10

Crosstalk ,Control Input R1=1kΩ, RL=10kΩ, 75

to Common O/I (Figure Control tTLH=tTHL=20ns ,Inhibit=Vss), VDD-VEE=10 mV

7)

*5. The formulas given are for the typical characteristics only at 25 ℃.

*6. Data labelled “Typ” is not lo be used for design purposes but In intended as an indication of the IC’s potential

*performance.

UTC UNISONIC TECHNOLOGIES CO., LTD. 4

QW-R502-013,A

UTC 4052 CMOS

VDD VDD

VDD

IN/OUT OUT/IN

VEE

VDD

LEVEL

CONVERTED

CONTROL IN/OUT OUT/IN

VEE CONTROL

Figure 1.Switch Circuit Schematic

16 VDD

INH 6 BINARY TO 1-OF-4

LEVEL

TRUTH TABLE A 10 DECODER WITH

CONVERTER

B 9 INHIBIT

Control Inputs

Select ON Switches 8 Vss 7 VEE

Inhibit B A X0 12

0 0 0 Y0 X0

0 0 1 Y1 X1 X1 14

0 1 0 Y2 X2 13 X

0 1 1 Y3 X3 X2 15

1 X X None

X3 11

* X=Don't Care

Y0 1

Y1 5

3 Y

Y2 2

Y3 4

Figure 2. Functional Diagram

TEST CIRCUITS

UTC UNISONIC TECHNOLOGIES CO., LTD. 5

QW-R502-013,A

UTC 4052 CMOS

ON SWITCH A

PULSE

GENERATOR B

CONTROL

SECTION C

OF IC

LOAD Vout

V INH RL CL

SOURCE

VDD VEE VEE VDD

Figure 3.→△V Across Switch Figure 4. Propagation Delay Times, Control and Inhibit to Output

A,B,and C inputs used to tum ON or OFF

the switch under tes.

RL

A A

B B ON

C C

Vout OFF Vout

INH RL CL=50pF INH

Vss RL CL=50pF

Vin

Vin

VDD VEE VDD VEE

2 2

Figure 6. Channel Separation

Figure 5. Bandwidth and Off-Channe Feedthrough Attenuation

(Adjacent Channels Used For Setup)

UTC UNISONIC TECHNOLOGIES CO., LTD. 6

QW-R502-013,A

UTC 4052 CMOS

OFF CHANNEL UNDER TEST

A VDD

B VEE

C CONTROL OTHER

SECTION CHANNEL(S)

Vout OF IC VEE

INH RL CL=50pF VDD

R1

COMMON

VEE

VDD

Figure 7. Crosstalk,Control Input to Common O/I Figure 8. Off Channel Leakage

VDD

KEITHLEY 160

DIGITAL

MULTIMETER

10K

1kΩ

RANGE X-Y

VDD

PLOTTER

VEE=VSS

Figure 9. Channel Resistance(RON) Test Circuit

TYPICAL RESISTANCE CHARACTERISTIS

350 350

RON,"ON" RESISTANCE (OHMS)

RON,"ON" RESISTANCE (OHMS)

300 300

250 250

200 200

TA=125℃

150 TA=125℃ 150

100 100 25℃

25℃

-55℃

50 -55℃ 50

0 0

-10 -8.0 -6.0 -4.0 -2.0 0 0.2 4.0 6.0 8.0 10 -10 -8.0 -6.0 -4.0 -2.0 0 0.2 4.0 6.0 8.0 10

Vin,INPUT VOLTAGE (VOLTS) Vin,INPUT VOLTAGE (VOLTS)

Figure10.VDD=7.5V,VEE=-7.5V Figure11.VDD=5.0V,VEE=-5.0V

UTC UNISONIC TECHNOLOGIES CO., LTD. 7

QW-R502-013,A

UTC 4052 CMOS

700 350

TA=25℃

600 300

RON,"ON" RESISTANCE (OHMS)

RON,"ON" RESISTANCE (OHMS)

500 250

VDD=2.5V

400 200

300 150

TA=125℃ 5.0V

200 100

7.5V

25℃

100 -55℃ 50

0 0

-10 -8.0 -6.0 -4.0 -2.0 0 0.2 4.0 6.0 8.0 10 -10 -8.0 -6.0 -4.0 -2.0 0 0.2 4.0 6.0 8.0 10

Vin,INPUT VOLTAGE (VOLTS) Vin, INPUT VOLTAGE (VOLTS)

Figure12.VDD=2.5V,VEE=-2.5V Figure13 Comparison at 25℃,VDD=-VEE

Figure A illustrates use of the on–chip level converter detailed in Figures 2. The 0 ~ 5 V Digital Control

signal is used to directly control a 9 Vp–p analog signal.

The digital control logic levels are determined by VDD and VSS. The VDD voltage is the logic high voltage; the VSS

voltage is logic low. For the example, VDD = + 5 V = logic high at the control inputs; VSS = GND = 0 V = logic low.

The maximum analog signal level is determined by VDD and VEE. The VDD voltage determines the maximum

recommended peak above VSS. The VEE voltage determines the maximum swing below VSS. For the example, VDD –

VSS = 5 V maximum swing above VSS; VSS – VEE = 5 V maximum swing below VSS. The example shows a ± 4.5 V

signal which allows a 1/2 volt margin at each peak. If voltage transients above VDD and/or below VEE are anticipated

on the analog channels, external diodes (Dx) are recommended as shown in Figure B. These diodes should be small

signal types able to absorb the maximum anticipated current surges during clipping.

The absolute maximum potential difference between VDD and VEE is 18.0 V. Most parameters are specified up to

15 V which is the recommended maximum difference between VDD and VEE.

Balanced supplies are not required. However, VSS must be greater than or equal to VEE. For example, VDD = + 10

V, VSS = + 5 V, and VEE – 3 V is acceptable. See the Table below.

+5V -5V

VDD Vss VEE

+4.5V

+5V

9 Vp-p SWITCH

ANALOG SIGNAL I/O COMMON 9 Vp-p

O/I GND

EXTERNAL 4052 ANALOG SIGNAL

CMOS

DIGITAL

0 ~ 5V DIGITAL -4.5V

CIRCUITRY INHIBIT,

A,B,C

CONTROL SIGNALS

Figure A. Application Example

UTC UNISONIC TECHNOLOGIES CO., LTD. 8

QW-R502-013,A

UTC 4052 CMOS

V DD V DD

Dx Dx

AN ALO G C O MMO N

I/O O /I

Dx Dx

VEE VEE

Figure B.External G ermanium or Schottky C lipping D iodes

POSSIBLE SUPPLY CONNECTIONS

CONTROL INPUTS MAXIMUM ANALOG

VDD VSS VEE

LOGIC HIGH/LOGIC LOW SIGNAL RANGE IN

IN VOLTS IN VOLTS IN VOITS

IN VOLTS VOLTS

+8 0 -8 +8/0 +8 ~ -8=16Vp-p

+5 0 -12 +5/0 +5 ~–12=17Vp-p

+5 0 0 +5/0 +5 ~ 0=5Vp-p

+5 0 -5 +5/0 +5 ~ -5=10Vp-p

+10 +5 -5 +10/+5 +10 ~ –5=15Vp-p

UTC UNISONIC TECHNOLOGIES CO., LTD. 9

QW-R502-013,A

You might also like

- 4052 UnisonicTechnologiesDocument6 pages4052 UnisonicTechnologiessigit raharjoNo ratings yet

- ANALOG MULTIPLEXERS/ DEMULTIPLEXERS - Part Number: UTC4053Document6 pagesANALOG MULTIPLEXERS/ DEMULTIPLEXERS - Part Number: UTC4053shawnleegabriel100% (1)

- Datasheet 4051Document6 pagesDatasheet 4051Jui KulkarniNo ratings yet

- TC75S102F_datasheet_en_20200605Document7 pagesTC75S102F_datasheet_en_20200605parsastar2010No ratings yet

- CD4029BC Presettable Binary/Decade Up/Down Counter: General Description FeaturesDocument9 pagesCD4029BC Presettable Binary/Decade Up/Down Counter: General Description FeaturesSantiago SerranoNo ratings yet

- CD4069Document5 pagesCD4069abdullahNo ratings yet

- CD4069 PDFDocument5 pagesCD4069 PDFPedro IsmaelNo ratings yet

- TC4538BP/TC4538BF Dual Precision Retriggerable/Resettable Monostable MultivibratorDocument9 pagesTC4538BP/TC4538BF Dual Precision Retriggerable/Resettable Monostable MultivibratorAmirNo ratings yet

- HCF4053M013TRDocument11 pagesHCF4053M013TRVasyaNo ratings yet

- HCF4053M013TRDocument11 pagesHCF4053M013TRVasyaNo ratings yet

- TC4521BP 24-Stage Frequency DividerDocument9 pagesTC4521BP 24-Stage Frequency DividerAmirNo ratings yet

- Rohm ML8511 00FCZ05B Datasheet PDFDocument8 pagesRohm ML8511 00FCZ05B Datasheet PDFarijit_ghosh_18No ratings yet

- TC4066BF Datasheet en 20170718 PDFDocument10 pagesTC4066BF Datasheet en 20170718 PDFricardo augustoNo ratings yet

- CD4069 DatasheetDocument7 pagesCD4069 DatasheetАна СтојковиќNo ratings yet

- TC4538BP Datasheet en 20140301Document9 pagesTC4538BP Datasheet en 20140301Strati YovchevNo ratings yet

- TC4081BF Datasheet en 20140301Document7 pagesTC4081BF Datasheet en 20140301YaKoviToNo ratings yet

- TC4584BP, TC4584BF, TC4584BFN: TC4584B Hex Schmitt TriggerDocument8 pagesTC4584BP, TC4584BF, TC4584BFN: TC4584B Hex Schmitt TriggerAmirNo ratings yet

- CD4016Document8 pagesCD4016api-3708997100% (1)

- Nte 4053Document4 pagesNte 4053Codinasound CaNo ratings yet

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocument6 pagesCD40106BC Hex Schmitt Trigger: General Description FeaturesHABUMUGISHA DieudonneNo ratings yet

- TC5565Document9 pagesTC5565MiniLabNo ratings yet

- N2576SG 5Document5 pagesN2576SG 5elnegritoheberNo ratings yet

- TC4093BP, TC4093BF: TC4093B Quad 2-Input NAND Schmitt TriggersDocument7 pagesTC4093BP, TC4093BF: TC4093B Quad 2-Input NAND Schmitt TriggersMohammed Al gobariNo ratings yet

- TC4520BP, TC4520BF: TC4520B Dual Binary Up CounterDocument10 pagesTC4520BP, TC4520BF: TC4520B Dual Binary Up CounterChaba Leyva HernándezNo ratings yet

- TC4081BP, TC4081BF, TC4081BFN: TC4081B Quad 2-Input AND GateDocument8 pagesTC4081BP, TC4081BF, TC4081BFN: TC4081B Quad 2-Input AND GateAmirNo ratings yet

- Is Now Part ofDocument10 pagesIs Now Part ofMatias GonzalezNo ratings yet

- Unisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersDocument7 pagesUnisonic Technologies Co., LTD: 8-Channel Analog Multiplexers/DemultiplexersNaresh KsNo ratings yet

- TC4013BP, TC4013BF: TC4013B Dual D-Type Flip FlopDocument8 pagesTC4013BP, TC4013BF: TC4013B Dual D-Type Flip Flopal nakheel electronicsNo ratings yet

- TC4066BP, TC4066BF, TC4066BFN, TC4066BFT: TC4066B Quad Bilateral SwitchDocument11 pagesTC4066BP, TC4066BF, TC4066BFN, TC4066BFT: TC4066B Quad Bilateral SwitchCandelaria CortesNo ratings yet

- Ds Ah 00614087Document20 pagesDs Ah 00614087P Chaayesha Naik 1No ratings yet

- CD4069UBC Inverter Circuits: General Description FeaturesDocument7 pagesCD4069UBC Inverter Circuits: General Description FeaturesvaleriojesusNo ratings yet

- TC4013BP, TC4013BF, TC4013BFN: TC4013B Dual D-Type Flip FlopDocument9 pagesTC4013BP, TC4013BF, TC4013BFN: TC4013B Dual D-Type Flip FlopvanmarteNo ratings yet

- Dual Low Power Operational AmplifierDocument5 pagesDual Low Power Operational Amplifieralex castroNo ratings yet

- TC4011BP, TC4011BF, TC4011BFN, TC4011BFT: TC4011B Quad 2 Input NAND GateDocument10 pagesTC4011BP, TC4011BF, TC4011BFN, TC4011BFT: TC4011B Quad 2 Input NAND GateAlireza RahimiNo ratings yet

- Ic Audio 8002 (2.0W)Document6 pagesIc Audio 8002 (2.0W)napoleon_velasc3617100% (1)

- TC4030BP, TC4030BF, TC4030BFN: TC4030B Quad Exclusive-OR GateDocument8 pagesTC4030BP, TC4030BF, TC4030BFN: TC4030B Quad Exclusive-OR GateAmirNo ratings yet

- TC75S103F Datasheet en 20200922-1927942Document9 pagesTC75S103F Datasheet en 20200922-1927942amin adimiNo ratings yet

- lmr1802g LB eDocument22 pageslmr1802g LB ecarlosibaNo ratings yet

- CD4024BC 7-Stage Ripple Carry Binary Counter: General Description FeaturesDocument6 pagesCD4024BC 7-Stage Ripple Carry Binary Counter: General Description FeaturesGoodLookingPirateNo ratings yet

- Specification For Release: TVS Diode Array WE-TVS SOT143-4LDocument5 pagesSpecification For Release: TVS Diode Array WE-TVS SOT143-4LkapakdoonNo ratings yet

- P14NF12FP - 120V, 14aDocument9 pagesP14NF12FP - 120V, 14aRenatoMaiaNo ratings yet

- TC4040BP, TC4040BF: TC4040B 12 Stage Ripple-Carry Binary Counter/DividersDocument8 pagesTC4040BP, TC4040BF: TC4040B 12 Stage Ripple-Carry Binary Counter/DividersMohammed Al gobariNo ratings yet

- TC4040Document8 pagesTC4040Edgar DauzonNo ratings yet

- Ena 1723Document7 pagesEna 1723Anddo BabbabNo ratings yet

- CD4030M/CD4030C Quad EXCLUSIVE-OR Gate: General Description ApplicationsDocument4 pagesCD4030M/CD4030C Quad EXCLUSIVE-OR Gate: General Description ApplicationsSuper WhippedNo ratings yet

- Datasheet TN6Q04 PDFDocument4 pagesDatasheet TN6Q04 PDFDaniel AvecillaNo ratings yet

- Specification For Release: TVS Diode Array WE-TVS SOT23-6LDocument5 pagesSpecification For Release: TVS Diode Array WE-TVS SOT23-6LAlex LuzNo ratings yet

- TC4069UBP, TC4069UBF, TC4069UBFN, TC4069UBFT: TC4069UB Hex InverterDocument9 pagesTC4069UBP, TC4069UBF, TC4069UBFN, TC4069UBFT: TC4069UB Hex InverterMohammed Al gobariNo ratings yet

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocument6 pagesCD40106BC Hex Schmitt Trigger: General Description FeaturesWellison RodriguesNo ratings yet

- 2SD300C17A4CDocument7 pages2SD300C17A4Csajad hejaziNo ratings yet

- Low Noise, Low Power Op Amp: Features DescriptionDocument28 pagesLow Noise, Low Power Op Amp: Features DescriptionSwapnil BangarNo ratings yet

- Isolated and Regulated 10 WATT Modular DC/DC Converters: SeriesDocument3 pagesIsolated and Regulated 10 WATT Modular DC/DC Converters: SeriesagusnellNo ratings yet

- Features Applications: IN OUT Xout OUT XoutDocument8 pagesFeatures Applications: IN OUT Xout OUT XoutEnéas BaroneNo ratings yet

- Dual Operational Amplifier-Yd4558: Youda Integrated CircuitDocument3 pagesDual Operational Amplifier-Yd4558: Youda Integrated CircuitJúnior Da Silva SantanaNo ratings yet

- HCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsDocument9 pagesHCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsEngin UzunNo ratings yet

- HCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsDocument10 pagesHCF4066B: Quad Bilateral Switch For Transmission or Multiplexing of Analog or Digital SignalsPendawa SeribuNo ratings yet

- Analog Dialogue Volume 46, Number 1: Analog Dialogue, #5From EverandAnalog Dialogue Volume 46, Number 1: Analog Dialogue, #5Rating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet