Professional Documents

Culture Documents

Exhibit A

Exhibit A

Uploaded by

sabatino123Original Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Exhibit A

Exhibit A

Uploaded by

sabatino123Copyright:

Available Formats

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page1 of 7

Exhibit A

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page2 of 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27

GREGORY P. STONE (SBN 078329) gregory.stone@mto.com KATHERINE K. HUANG (SBN 219798) katherine.huang@mto.com PETER E. GRATZINGER (SBN 228764) peter.gratzinger@mto.com KEITH R.D. HAMILTON (SBN 252115) keith.hamilton@mto.com DAVID H. PENNINGTON (SBN 272238) david.pennington@mto.com MUNGER, TOLLES & OLSON LLP 355 South Grand Avenue, 35th Floor Los Angeles, CA 90071-1560 Telephone: (213) 683-9100 Facsmile: (213) 687-3702 PETER A. DETRE (SBN 182619) peter.detre@mto.com MUNGER, TOLLES & OLSON LLP 560 Mission Street, 27th Floor San Francisco, CA 94105 Telephone: (415) 512-4000 Facsimile: (415) 512-4077 Attorneys for Plaintiff RAMBUS INC. UNITED STATES DISTRICT COURT NORTHERN DISTRICT OF CALIFORNIA SAN FRANCISCO DIVISION RAMBUS INC., Plaintiff, v. LSI CORPORATION, Defendant. RAMBUS INC., Plaintiff, v. STMICROELECTRONICS N.V.; STMICROELECTRONICS INC., Defendants. Case No. 3:10-cv-05446 RS [PROPOSED] RAMBUS INC.S RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF Date: Time: Judge: August 29, 2012 10:00 a.m. Hon. Richard Seeborg

Case No. 3:10-cv-05449 RS

28

18429230.2

RAMBUSS RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF CASE NOS. 3:10-CV-05446, 3:10-CV-05449

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page3 of 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

I.

INTRODUCTION In their sur-reply brief, Defendants seek to extend the Federal Circuits holding that a

memory device is not necessarily a single chip to terms at issue herecontroller/controller device, and synchronous DRAM devicethat the Federal Circuit did not address. As set forth below, these terms are properly construed as single chips, and the Federal Circuit opinion does not indicate otherwise. With respect to whether a memory device can include a controller, the court held that it cannot include a CPU or bus controller. In re Rambus, No. 2011-1247, slip op. at 15 (Fed. Cir. Aug. 15, 2012). Because a synchronous DRAM device is a particular type of memory device, the construction of this term should include the same limitation. II. CONTROLLER/CONTROLLER DEVICE Defendants concede that the terms controller and controller device were not considered by the Federal Circuit, but argue that the courts reasoning and analysis is relevant to the proper construction of those terms. Sur-reply at 2. Each term, however, should be construed on its own merits, and, in arriving at its conclusion that a memory device is not limited to a single chip, the Federal Circuit relied in part on considerations unique to that term. For example, the court considered claim differentiation arguments, slip op. at 11-12, unrelated to the terms controller or controller device. For the reasons stated in Rambuss opening and reply briefs, these terms should be construed as integrated circuit devices, i.e. single chips. III. SYNCHRONOUS DYNAMIC RANDOM ACCESS MEMORY DEVICE A. A Synchronous DRAM Device is a single chip

Defendants effort to stretch the Federal Circuits decision regarding memory device to require that synchronous dynamic random access memory device be construed as including multi-chip devices cannot succeed. The Federal Circuit did not consider whether the latter, narrower term could encompass more than a single chip, and there was no occasion for it to do so: while the PTO examiner, the Board of Patent Appeals and Interferences (BPAI), and the Director of the PTO in his brief to the Federal Circuit maintained that a memory device is not a term of art and not necessarily limited to a single chip, they all agreed with Rambus that a DRAM device is a term of art referring to a single chip. For example, among its claim differentiation

18429230.2

-1-

RAMBUSS RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF CASE NOS. 3:10-CV-05446, 3:10-CV-05449

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page4 of 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

arguments to the Federal Circuit, the Director pointed to claims of U.S. Patent No. 5,841,715. Brief for Appellee-Director of the U.S.P.T.O., Aug. 5, 2011 (attached hereto as Ex. 1), at 33. While claim 1 of the 715 patent recites a memory device, dependent claim 3 provides that the [memory] device comprises a dynamic random access memory (DRAM) device. Id. (quoting 715 patent). The Director argued that [t]he use of the open-ended term comprising in claim 3 . . . implies that the memory device could encompass more than just a single DRAM chip, thereby suggesting that a memory device is not limited to a single chip. Id. (emphasis added). Thus, in making his argument, the Director interpreted the dynamic random access memory (DRAM) device of claim 3 as a single DRAM chip. Accord BPAI Decision on Appeal, No. 2010011178 (attached as Ex. I to Detre Decl. in support of Rambuss Opening Claim Construction Brief), at 29 (making similar claim differentiation argument); id. at 24, n.7 (quoting Examiners acknowledge[ment] that the memory devices such as ROM, SRAM, and DRAM are defined as being a single integrated memory chip.) (emphasis added). Further, contrary to Defendants argument, Sur-reply at 2, not every device term is entitled to a broad construction. Cf. Rambus Inc. v. Infineon Technologies, 318 F.3d 1081, 1091 (Fed. Cir. 2003) (construing integrated circuit device as a single chip); BPAI Decision on Appeal, No. 2011-013706 (attached hereto as Ex. 2), at 8 (construing synchronous semiconductor memory device as a single chip). In their sur-reply, Defendants rely on U.S. Patent No. 5,638,334. Sur-reply at 3. Defendants note that the Federal Circuit, in the course of discussing claim differentiation arguments, found that claim 6 of the 334 patent, which restricted the memory device of claim 1 to being formed on a single semiconductor substrate, could be viewed as limiting the broader term memory device to a single chip. Id. The Defendants find it significant that the Federal Circuit did not then turn to claim 7 of the 334 patent, which provides that the memory device [of claim 1] is a dynamic random access memory device, and state that it too is limited to a single chip. But nothing can be read into the fact that the court did not address claim 7. In that portion of the opinion, the Federal Circuit was addressing the claim differentiation argument made by the PTO, not cataloguing all of Rambuss patent claims that are, in its view, limited to a single chip. Slip op. at 11-12. And there would have been no reason for the PTO to refer to

18429230.2

-2-

RAMBUSS RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF CASE NOS. 3:10-CV-05446, 3:10-CV-05449

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page5 of 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

claim 7, because that claim does not support the claim differentiation argument it was making. There are various types of single-chip memory devices, including ROM, SRAM, and DRAM devices. See, e.g., 916 patent, col. 1:53-55 (referring to the most widely used Dynamic Random Access Memory (DRAM), Static RAM (SRAM) and Read Only Memory (ROM) devices); id., Fig. 2 (illustrating DRAM and ROM chips). Thus, even though a DRAM device is a single chip, the fact that claim 7 restricts a memory device to a DRAM device does not imply that a memory device is broader than a single chip; rather, the term memory device could simply encompass all single-chip memory devices, while claim 7 specifies that the memory device is a DRAM device, rather than an SRAM, ROM, or other type of single-chip memory device. B. A Synchronous DRAM Device cannot include a bus controller

Defendants argue in their sur-reply that, because the Federal Circuit held that a memory device could include some control functionality, the Court should reject that part of Rambuss proposed construction of synchronous dynamic random access memory device that specifies that such a device does not include a memory controller. Sur-reply at 3-4. The Federal Circuit was clear, however, that the construction of memory device should specify that such a device does not include a CPU or bus controller. Slip op. at 15 ([W]e construe a memory device as a component of a memory subsystem, not limited to a single chip, where the device may have a controller that, at least provides the logic necessary to receive and output specific data, but does not perform the control function of a CPU or bus controller.) (emphasis added). A synchronous DRAM device is a particular type of memory device; it follows that synchronous DRAM device should likewise be construed as not including a CPU or bus controller. Moreover, the Federal Circuit opinion provides examples of bus controllers that cannot be included in a memory device. First, the Federal Circuit considered the bus interface unit (BIU) in the prior art Jackson patent and found that because Rambus exclude[d] the function of Jacksons BIU during prosecution this prevents the memory device from containing a global bus controller or CPU. Slip. op. at 14-15. The prosecution history of the 918 patent makes clear the functionality that Rambus excluded and that the Federal Circuit relied on in finding that a memory device could not include a bus controller. During prosecution, the examiner had

18429230.2

-3-

RAMBUSS RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF CASE NOS. 3:10-CV-05446, 3:10-CV-05449

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page6 of 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

rejected Rambuss pending claims on the ground that the BIU, combined with conventional memory chips, met Rambuss claim limitations with Jacksons data length transfer information corresponding to the block size information in Rambuss claims. Rambus distinguished Jackson, pointing out that it was the BIU, not the memory devices, in Jackson that received the data length transfer information and the clock signal. Amendment, Jul. 23, 1999, at 10-11 (attached hereto as Ex. 3). The functionality that Rambus identified as distinguishing the BIU from a memory device was that the BIU (1) receives and decodes [the data length transfer information from the microprocessor] and, based thereon, generates and applies the addresses and control signals (i.e., OE\, RAS\, CAS\) necessary to obtain the number of bytes of data defined by data length transfer information, and (2) fetches the data returned from the memory, buffers and aligns that data, and then transfers it to the microprocessor synchronously with respect to an external clock signal. Id. Second, the Federal Circuit also found that the memory stick described in the patent specification is not a memory device. Slip op. at 9. Such a memory stick consists of a number of memory chips on a primary bus unit attached to a transceiver device. 916 patent, col. 19:51 - 20:35 & Fig. 9. The transceiver device connects the memory stick to a transceiver bus and is quite simple in function: the transceiver device detects request packets (specifying, for example, a read or write request) that are sent by master devices on the transceiver bus and transmits them to the memory chips on the primary bus unit, and transmits all the data required for the transaction between the primary bus unit and the transceiver bus. Id. Because it found that such a memory stick is not a memory device, the Federal Circuit must have concluded that the transceiver device described in the specification is a bus controller. Thus the construction of synchronous DRAM device should specify that it cannot include a CPU or bus controller, where the category of bus controllers includes any device with the functionality of the BIU in Jackson as set forth in the prosecution history of the 918 patent, or of the transceiver device in a memory stick described in the patent specification. IV. CONCLUSION Rambus respectfully submits that the Court should adopt its proposed claim constructions.

18429230.2

-4-

RAMBUSS RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF CASE NOS. 3:10-CV-05446, 3:10-CV-05449

Case3:10-cv-05449-RS Document110-1 Filed08/27/12 Page7 of 7

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28

DATED: August 27, 2012

MUNGER, TOLLES & OLSON LLP By: /s/ Peter A. Detre Peter A. Detre Attorneys for Plaintiff RAMBUS INC.

18429230.2

-5-

RAMBUSS RESPONSE TO DEFENDANTS SUR-REPLY CLAIM CONSTRUCTION BRIEF CASE NOS. 3:10-CV-05446, 3:10-CV-05449

You might also like

- United States District Court Northern District of California San Francisco DivisionDocument19 pagesUnited States District Court Northern District of California San Francisco Divisionsabatino123No ratings yet

- Claim Construction Order: No. 10-05446 RS No. 10-05449 RS C C ODocument28 pagesClaim Construction Order: No. 10-05446 RS No. 10-05449 RS C C Osabatino123No ratings yet

- Exhibit ADocument10 pagesExhibit Asabatino123No ratings yet

- Corrected Amicus Brief 10 4 07Document16 pagesCorrected Amicus Brief 10 4 07antitrusthallNo ratings yet

- United States District Court Northern District of California San Francisco DivisionDocument29 pagesUnited States District Court Northern District of California San Francisco Divisionsabatino123No ratings yet

- U S C A: Nited Tates Ourt of PpealsDocument37 pagesU S C A: Nited Tates Ourt of Ppealssabatino123No ratings yet

- Fairchild Semiconductor Corp., Et Al. v. Power Integrations, Inc., C.A. No. 12-540-LPS (D. Del. Aug. 28, 2013) .Document32 pagesFairchild Semiconductor Corp., Et Al. v. Power Integrations, Inc., C.A. No. 12-540-LPS (D. Del. Aug. 28, 2013) .YCSTBlogNo ratings yet

- Case Brief: Facts: Rambus V. InfineonDocument7 pagesCase Brief: Facts: Rambus V. InfineonTripathi OjNo ratings yet

- Pragmatus Telecom, LLC v. Volkswagen Group of America, Inc., Et Al., Master Docket No. 12-1533-RGA (D. Del. Sept. 9, 2014) .Document14 pagesPragmatus Telecom, LLC v. Volkswagen Group of America, Inc., Et Al., Master Docket No. 12-1533-RGA (D. Del. Sept. 9, 2014) .YCSTBlogNo ratings yet

- 4251Document6 pages4251sabatino123No ratings yet

- Answer To Complaint: A C C N - C 10-04017-JSWDocument10 pagesAnswer To Complaint: A C C N - C 10-04017-JSWsabatino123No ratings yet

- United States Court of Appeals: No. 2012-1480 (Reexamination No. 95/001,166)Document36 pagesUnited States Court of Appeals: No. 2012-1480 (Reexamination No. 95/001,166)sabatino123No ratings yet

- Gerald P. Garrett v. C.C. Higgenbotham, JR., 800 F.2d 1537, 11th Cir. (1986)Document5 pagesGerald P. Garrett v. C.C. Higgenbotham, JR., 800 F.2d 1537, 11th Cir. (1986)Scribd Government DocsNo ratings yet

- 58Document61 pages58sabatino123No ratings yet

- 10HarvJLTech353 PDFDocument16 pages10HarvJLTech353 PDFMohamed RaaziqNo ratings yet

- United States Court of Appeals, Fourth CircuitDocument11 pagesUnited States Court of Appeals, Fourth CircuitScribd Government DocsNo ratings yet

- Openwave Systems, Inc. v. Apple Inc., Et Al., C.A. No. 11-765-RGA (D. Del. Feb. 19, 2014) .Document7 pagesOpenwave Systems, Inc. v. Apple Inc., Et Al., C.A. No. 11-765-RGA (D. Del. Feb. 19, 2014) .YCSTBlogNo ratings yet

- Tony Dickey and Paul Parmer, Et Al. v. Advanced Micro DevicesDocument36 pagesTony Dickey and Paul Parmer, Et Al. v. Advanced Micro DevicesnorcavataNo ratings yet

- Attorney List On Signature PageDocument10 pagesAttorney List On Signature Pagesabatino123No ratings yet

- Transport RoomDocument388 pagesTransport Roomsabatino123No ratings yet

- Depuy Synthes Products, LLC v. Globus Medical, Inc., C.A. No. 11-652-LPS (D. Del. May 7, 2013)Document40 pagesDepuy Synthes Products, LLC v. Globus Medical, Inc., C.A. No. 11-652-LPS (D. Del. May 7, 2013)YCSTBlogNo ratings yet

- United States District Court Northern District of California San Francisco DivisionDocument9 pagesUnited States District Court Northern District of California San Francisco Divisionsabatino123No ratings yet

- Rambus'S Reply To Oppositions by Hynix and Samsung To Rambus'S Motion To Compel The Depositions of Hynix and Samsung On Design-Around and Alternatives As To Gddr5 and Ddr4Document10 pagesRambus'S Reply To Oppositions by Hynix and Samsung To Rambus'S Motion To Compel The Depositions of Hynix and Samsung On Design-Around and Alternatives As To Gddr5 and Ddr4sabatino123No ratings yet

- DELCHI CARRIER SpA v. ROTOREX CORPORATION FindLawDocument7 pagesDELCHI CARRIER SpA v. ROTOREX CORPORATION FindLawBùi Long ViệtNo ratings yet

- Public VersionDocument21 pagesPublic Versionsabatino123No ratings yet

- Exhibit ADocument106 pagesExhibit Asabatino123No ratings yet

- United States District Court For The Northern District of California San Jose DivisionDocument7 pagesUnited States District Court For The Northern District of California San Jose Divisionsabatino123No ratings yet

- United States Court of Appeals, Tenth CircuitDocument9 pagesUnited States Court of Appeals, Tenth CircuitScribd Government DocsNo ratings yet

- The Dirty OpinionDocument12 pagesThe Dirty OpinionErin FuchsNo ratings yet

- Progressive Semiconductor MarkmanDocument16 pagesProgressive Semiconductor MarkmaniphawkNo ratings yet

- The Value of The StandardDocument89 pagesThe Value of The StandardAnonymous pmp6FvMNo ratings yet

- Motion For Summary Judgment, LegalForce RAPC v. Demassa (UPL, California, Before USPTO)Document29 pagesMotion For Summary Judgment, LegalForce RAPC v. Demassa (UPL, California, Before USPTO)Raj Abhyanker100% (1)

- US Copyright Office: Vhdpa-ReportDocument23 pagesUS Copyright Office: Vhdpa-ReportUSA_CopyrightOfficeNo ratings yet

- Exhibit 1Document11 pagesExhibit 1sabatino123No ratings yet

- 13-11-12 Qualcomm Brief Re. Appeal of Apple v. Motorola Wisconsin FRAND DismissalDocument29 pages13-11-12 Qualcomm Brief Re. Appeal of Apple v. Motorola Wisconsin FRAND DismissalFlorian MuellerNo ratings yet

- Execware, LLC v. BJ's Wholesale Club, Inc., Et Al., C.A. No. 14-223-LPS-CJB (D. Del. July 15, 2015) .Document41 pagesExecware, LLC v. BJ's Wholesale Club, Inc., Et Al., C.A. No. 14-223-LPS-CJB (D. Del. July 15, 2015) .YCSTBlogNo ratings yet

- Snap-On v. Harbor Freight - Order Denying PIDocument20 pagesSnap-On v. Harbor Freight - Order Denying PISarah BursteinNo ratings yet

- Rambus'S Trial Brief To Exclude Samsung Trial Exhibits 4438 and 4439 From EvidenceDocument6 pagesRambus'S Trial Brief To Exclude Samsung Trial Exhibits 4438 and 4439 From Evidencesabatino123No ratings yet

- Exhibit BDocument72 pagesExhibit Bsabatino123No ratings yet

- Google LetterDocument3 pagesGoogle LetteronthecoversongsNo ratings yet

- United States v. National Amusement, 380 F.3d 558, 1st Cir. (2004)Document21 pagesUnited States v. National Amusement, 380 F.3d 558, 1st Cir. (2004)Scribd Government DocsNo ratings yet

- Acctuate v. IBM-MTDDocument21 pagesAcctuate v. IBM-MTDnimrodaviadNo ratings yet

- Dresdner Bank AG v. M/V Olympia Voyager, 446 F.3d 1377, 11th Cir. (2006)Document8 pagesDresdner Bank AG v. M/V Olympia Voyager, 446 F.3d 1377, 11th Cir. (2006)Scribd Government DocsNo ratings yet

- Appendix B-1Document15 pagesAppendix B-1sabatino123No ratings yet

- Exhibit ADocument78 pagesExhibit Asabatino123No ratings yet

- Order Granting in Part and Denying in Part Stmicroelectonics, Inc.'S Motion For Leave To Amend Answer and CounterclaimsDocument11 pagesOrder Granting in Part and Denying in Part Stmicroelectonics, Inc.'S Motion For Leave To Amend Answer and Counterclaimssabatino123No ratings yet

- Cal CD - Klausner - MMDocument6 pagesCal CD - Klausner - MMJ DoeNo ratings yet

- DearDocument2 pagesDearsabatino123No ratings yet

- Supreme Court of The United States: Limelight Networks, Inc. V. Akamai Technologies, Inc.Document13 pagesSupreme Court of The United States: Limelight Networks, Inc. V. Akamai Technologies, Inc.Anonymous Feglbx5No ratings yet

- SAS Institute Inc. v. World Programming LimitedDocument16 pagesSAS Institute Inc. v. World Programming LimitedZachery EanesNo ratings yet

- Lexmark Int'l, Inc. v. Static Control Components, Inc., 134 S. Ct. 1377 (2014)Document25 pagesLexmark Int'l, Inc. v. Static Control Components, Inc., 134 S. Ct. 1377 (2014)Scribd Government DocsNo ratings yet

- Memorandum of Points and Authorities in Support of Rambus Inc.'S Motion To Compel Samsung To Produce Discovery Relating To (1) Sales of Accused Products and (2) Memory ControllersDocument17 pagesMemorandum of Points and Authorities in Support of Rambus Inc.'S Motion To Compel Samsung To Produce Discovery Relating To (1) Sales of Accused Products and (2) Memory Controllerssabatino123No ratings yet

- Shields v. Atlantic Coast Line R. Co., 350 U.S. 318 (1956)Document10 pagesShields v. Atlantic Coast Line R. Co., 350 U.S. 318 (1956)Scribd Government DocsNo ratings yet

- CNG Ruling at Dallas Fort Worth International AirportDocument9 pagesCNG Ruling at Dallas Fort Worth International AirportRobert WilonskyNo ratings yet

- Worlds Markman ResultDocument40 pagesWorlds Markman ResultPatentplayNo ratings yet

- MaryDocument3 pagesMarysabatino123No ratings yet

- Re: Docket No. 366: RLF1 8090668v.1Document11 pagesRe: Docket No. 366: RLF1 8090668v.1sabatino123No ratings yet

- Petition for Certiorari Denied Without Opinion: Patent Case 98-1972.From EverandPetition for Certiorari Denied Without Opinion: Patent Case 98-1972.No ratings yet

- Encyclopaedia of International Aviation Law: Volume 3 English and French Version Version Englaise Et Française 2013 EditionFrom EverandEncyclopaedia of International Aviation Law: Volume 3 English and French Version Version Englaise Et Française 2013 EditionNo ratings yet

- Show Temp PDFDocument1 pageShow Temp PDFsabatino123No ratings yet

- United States District Court Eastern District of Texas Marshall DivisionDocument4 pagesUnited States District Court Eastern District of Texas Marshall Divisionsabatino123No ratings yet

- United States District Court Eastern District of Texas Marshall DivisionDocument4 pagesUnited States District Court Eastern District of Texas Marshall Divisionsabatino123No ratings yet

- Innovative Markman OrderDocument58 pagesInnovative Markman OrderiphawkNo ratings yet

- Innovative Microsft SettlementDocument2 pagesInnovative Microsft SettlementiphawkNo ratings yet

- Innovative Acer DismissalDocument1 pageInnovative Acer DismissaliphawkNo ratings yet

- In The United States District Court Eastern District of Texas Marshall DivisionDocument2 pagesIn The United States District Court Eastern District of Texas Marshall Divisionsabatino123No ratings yet

- Innovative Display Technologies, LLC v. ZTE Corporation, Et Al.Document2 pagesInnovative Display Technologies, LLC v. ZTE Corporation, Et Al.sabatino123No ratings yet

- AtDocument1 pageAtsabatino123No ratings yet

- Joint Motion To Dismiss: Arnan Orris Ichols RSHT UnnellDocument2 pagesJoint Motion To Dismiss: Arnan Orris Ichols RSHT Unnellsabatino123No ratings yet

- United States District Court For The Eastern District of Texas Marshall DivisionDocument2 pagesUnited States District Court For The Eastern District of Texas Marshall Divisionsabatino123No ratings yet

- IAM Magazine Issue 67 - Hands-On CounselDocument5 pagesIAM Magazine Issue 67 - Hands-On Counselsabatino123No ratings yet

- Innovative Blackberry DismissalDocument2 pagesInnovative Blackberry DismissaliphawkNo ratings yet

- Innovative Blackberry DismissalDocument2 pagesInnovative Blackberry DismissaliphawkNo ratings yet

- Innovative Apple DismissalDocument1 pageInnovative Apple DismissaliphawkNo ratings yet

- Innovative Canon DismissalDocument2 pagesInnovative Canon DismissaliphawkNo ratings yet

- PlaintiffDocument3 pagesPlaintiffsabatino123No ratings yet

- Defendants.: LITIOC/2100839v3/101022-0107Document4 pagesDefendants.: LITIOC/2100839v3/101022-0107sabatino123No ratings yet

- In The United States District Court For The Eastern District of Texas Marshall DivisionDocument33 pagesIn The United States District Court For The Eastern District of Texas Marshall Divisionsabatino123No ratings yet

- Defendants.: LITIOC/2100839v3/101022-0107Document4 pagesDefendants.: LITIOC/2100839v3/101022-0107sabatino123No ratings yet

- 6Document21 pages6sabatino123No ratings yet

- Innovative Display Technologies LLCDocument4 pagesInnovative Display Technologies LLCsabatino123No ratings yet

- Jarkom Naskah Publikasi Azhar Munif Upload 39 46Document8 pagesJarkom Naskah Publikasi Azhar Munif Upload 39 46Alda AzhariNo ratings yet

- Design and Implementation of Dual-Stacked Identical Yagi Antenna For UHF ApplicationsDocument4 pagesDesign and Implementation of Dual-Stacked Identical Yagi Antenna For UHF ApplicationsEditor IJTSRDNo ratings yet

- Installation Manual Gps Navigator GP-150: ModelDocument40 pagesInstallation Manual Gps Navigator GP-150: ModelJosko PrnjakNo ratings yet

- Triangle Esprit 40TH Antal Golden Oak Datasheets enDocument1 pageTriangle Esprit 40TH Antal Golden Oak Datasheets enMarko PetrovNo ratings yet

- Long Range Spy Robot With Night Vision: Block DiagramDocument5 pagesLong Range Spy Robot With Night Vision: Block DiagramHassan AliNo ratings yet

- Samuel Afoakwa PDFDocument113 pagesSamuel Afoakwa PDFDiego LombardoNo ratings yet

- Katalog PDFDocument20 pagesKatalog PDFIL Lo Gar100% (1)

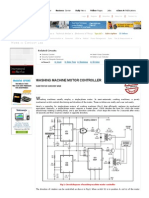

- Washing Machine Motor ControllerDocument3 pagesWashing Machine Motor ControllerprabhyodhNo ratings yet

- 32PFL3515D-F7 pl10 - 3 - Phil - SM - Aen - 120110Document108 pages32PFL3515D-F7 pl10 - 3 - Phil - SM - Aen - 120110london335No ratings yet

- Computer Notes For Class 9th 10thDocument33 pagesComputer Notes For Class 9th 10thPrince HaiderNo ratings yet

- NFC AbstractDocument21 pagesNFC AbstractSaqib AmeenNo ratings yet

- How To Use Hall Effect Sensor With Arduino?: OutlineDocument13 pagesHow To Use Hall Effect Sensor With Arduino?: OutlineRAMESH P (PC2013005013009)No ratings yet

- Final Report Iec-10Document10 pagesFinal Report Iec-10protikbiswas2088No ratings yet

- Module Unit: LaunchingDocument128 pagesModule Unit: LaunchingGreeshma DeepakNo ratings yet

- FPBA-01 PROFIBUS DP Adapter Module: User's ManualDocument174 pagesFPBA-01 PROFIBUS DP Adapter Module: User's ManualAngel DimariaNo ratings yet

- Group 3: Capalaran, Joshua Espuerta, Erjohn Limba, David Orhalo, Felix Jr. Tradio, BernadetteDocument14 pagesGroup 3: Capalaran, Joshua Espuerta, Erjohn Limba, David Orhalo, Felix Jr. Tradio, BernadetteANNAMARSNo ratings yet

- EXtreme Power Supply CalculatorDocument2 pagesEXtreme Power Supply CalculatorBartek KaczmarskiNo ratings yet

- Microsoft PowerPoint - Slide-Argus1,2,7,8, Mit (Compatibility M PDFDocument47 pagesMicrosoft PowerPoint - Slide-Argus1,2,7,8, Mit (Compatibility M PDFmaheshNo ratings yet

- BMS 40a 3S - SGTDocument2 pagesBMS 40a 3S - SGTMarcelo Mannett0% (1)

- FM - CG - Drones (17) 18 - Dutch Study About Interference Risks From Drones PDFDocument70 pagesFM - CG - Drones (17) 18 - Dutch Study About Interference Risks From Drones PDFPete AirNo ratings yet

- Small Signal Transistors TO-39 CaseDocument1 pageSmall Signal Transistors TO-39 CasePetr ggaNo ratings yet

- RTC Interfacing With 8051 Microcontroller and ProgrammingDocument16 pagesRTC Interfacing With 8051 Microcontroller and ProgrammingJoshua ButhelloNo ratings yet

- Teledyne Odom Hydrotrac IIDocument2 pagesTeledyne Odom Hydrotrac IIRamdan YassinNo ratings yet

- RIOT Board User Manual v1.1Document53 pagesRIOT Board User Manual v1.1Leon ConstantinNo ratings yet

- Field Service Engineer or Field Service Technician or ElectronicDocument2 pagesField Service Engineer or Field Service Technician or Electronicapi-121403242No ratings yet

- SIRIUS Innovations Selection Guide - Pwsa-A880m-0411 - Switching - Devicesr PDFDocument4 pagesSIRIUS Innovations Selection Guide - Pwsa-A880m-0411 - Switching - Devicesr PDFEscape ExistNo ratings yet

- Component Shelf Life 8a GEDocument35 pagesComponent Shelf Life 8a GEpapplionNo ratings yet

- Bluetooth HC-06 DatasheetDocument17 pagesBluetooth HC-06 DatasheetjuampicNo ratings yet

- MCQ in Wire and Wireless Communications System Part 6 ECE BoardDocument20 pagesMCQ in Wire and Wireless Communications System Part 6 ECE BoardIan John MontalboNo ratings yet

- Performance Comparison of 3D-Mesh and 3D-Torus Network-on-ChipDocument5 pagesPerformance Comparison of 3D-Mesh and 3D-Torus Network-on-ChipJournal of ComputingNo ratings yet