Professional Documents

Culture Documents

Sequential Circuits: March 28, 2006 1

Sequential Circuits: March 28, 2006 1

Uploaded by

Lakshmikanth MeduriOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Sequential Circuits: March 28, 2006 1

Sequential Circuits: March 28, 2006 1

Uploaded by

Lakshmikanth MeduriCopyright:

Available Formats

Sequential Circuits

x w

Combinational

v0 v1 clock

Storage elements

v0+ v1+

A combinational circuit and storage elements are interconnected to form a sequencial circuit. The information stored at any time defines the state of the circuit at that time. The next state of the storage elements is a function of the inputs and the present state. Synchronous sequential circuit can be defined from the knowledge of its signals at discrete instants.

March 28, 2006 1

Huffman Model

Sequential Circuit Design

1- Obtain either the state diagram or state table from the problem specs. 2- If we dont have one already, obtain the state table from the state diagram. 3- Assign binary codes to the states. 4- Derive the FF input equations from the next state entries of the state table. 5- Derive the output equations from the output entries of the state table.

March 28, 2006

Sequential Circuit Design

Design a sequence detector for the string 1101. The output must be 1 when the input matches this string

x clock

Sequence detector

March 28, 2006

Sequential Circuit Design

Mealy state machine (remember that in this state machine the output is dependent on input changes and states)

0/0 A 0/0 0/0 1/0 1/0 B 1/0 0/0

C 1/1

Assign binary values to each state. Example: A = 00, B = 01, C = 11, D = 10

March 28, 2006 4

Sequential Circuit Design

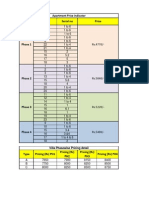

Make Table FROM present state & input TO next state & output, and FF inputs. J K Q(t+1) Operation

0 0 1 1 0 1 0 1 Q(t) 0 1 Q(t) No change Reset Set Complement

A B C D

March 28, 2006

Sequential Circuit Design

K-maps of the states & the outputs

Q1 Q0 I

0 1

Output = IQ1Q0

00 0 0 01 0 0 11 0 0 10 0 1

Q1 Q0 I

0 1 00 0 0

J1 = IQ0

01 0 1 11 X X 10 X X

Q1 Q0 I

00 0 1 X X

K1 = Q0

01 X X 11 0 0 10 1 1

Q1 Q0 I

0 1 00 0 1

J0 = I

01 X X 11 X X 10 0 1

Q1 Q0 I

K0 = I

00 X X 01 1 0 11 1 0 10 X X

6

0 1

March 28, 2006

Sequential Circuit Design

Layout Diagram

J1 = IQ0 K1 = Q0 J0 = I K0 = I Output = IQ1Q0

March 28, 2006

Sequential Circuit Design Moore State Machine

Associate output with states only. This means that the output is also synchronous with the clock

x clock Sequence detector

clock x w

March 28, 2006

Sequential Circuit Design

Moore State Machine for the sequence detector 110

0 A/0 0 0 1 1 B/0 1 0

C/0 1

D/1

clock x w

March 28, 2006

state

Sequential Circuit Design

VHDL implementation for the Moore sequence detector 110

ARCHITECTURE seq_det_arch of seq_det is BEGIN process1: PROCESS(CLK)

VARIABLE STATE : STD_LOGIC_VECTOR(1 DOWNTO 0):= "00";

ENTITY seq_det IS PORT ( CLK : IN STD_LOGIC; X : IN STD_LOGIC; W : OUT STD_LOGIC ); END seq_det;

March 28, 2006

BEGIN IF (CLK = 1) THEN CASE STATE IS WHEN "00" => IF (X = '0') THEN STATE := "00"; W <= '0'; ELSE STATE := "01"; W <= '0'; END IF; WHEN "01" => IF (X = '1') THEN STATE := "10"; W <= '0'; ELSE STATE := "00"; W <= '0'; END IF;

-- State A

-- State B

10

Continued

Sequential Circuit Design

VHDL implementation for the Moore sequence detector 110

WHEN "10" => IF (X = '1') THEN STATE := "10"; W <= '0'; ELSE STATE := "11"; W <= '1'; END IF; WHEN OTHERS => IF (X = '1') THEN STATE := "01"; W <= '0'; ELSE STATE := "00"; W <= '0'; END IF; END CASE; END IF; END PROCESS; END seq_det_arch; March 28, 2006

-- State C

-- State D

11

Sequential Circuit Design

VHDL implementation for the Moore sequence detector 110

Simulation waveform

March 28, 2006

12

You might also like

- Sequential Circuits: March 28, 2006 1Document12 pagesSequential Circuits: March 28, 2006 1Sunil Kumar DasariNo ratings yet

- Analysis and Design of Sequential Logic CircuitsDocument115 pagesAnalysis and Design of Sequential Logic CircuitsQuoc Khanh PhamNo ratings yet

- Finite State Machines: Moore MachineDocument4 pagesFinite State Machines: Moore Machineborakas_borakasNo ratings yet

- 6.1 Introduction of Sequential Logic CircuitsDocument71 pages6.1 Introduction of Sequential Logic CircuitsZhichaoWangNo ratings yet

- Digital Design ExamplesDocument29 pagesDigital Design ExampleshumnaharoonNo ratings yet

- Sequential Circuit Design Sequence RecognizerDocument4 pagesSequential Circuit Design Sequence RecognizerKhurram SamiNo ratings yet

- Sequential CircuitDocument51 pagesSequential CircuitDamodar Telu100% (1)

- Sequential Circuit AnalysisDocument15 pagesSequential Circuit AnalysisJeth Gato VestalNo ratings yet

- 15 Hw03 DigitalSystems IDocument3 pages15 Hw03 DigitalSystems IWilliam ZhuangNo ratings yet

- Sequential Circuit DesignDocument28 pagesSequential Circuit DesignNiranda PereraNo ratings yet

- Chapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State UniversityDocument6 pagesChapter 3: Sequential Logic Some Definitions: Dr. Tim Mcguire Sam Houston State Universitydemos2011No ratings yet

- 10 SequentialCircuitDesignDocument51 pages10 SequentialCircuitDesignTony Kawai KanNo ratings yet

- ITBP205 Digital Design and Computer OrganizationDocument21 pagesITBP205 Digital Design and Computer OrganizationReem Ashraf0% (1)

- Notes 326 Set11Document16 pagesNotes 326 Set11Dhanu ChettyNo ratings yet

- Finite State MachinesDocument55 pagesFinite State Machinesdeepanilsaxena100% (2)

- Switching Circuits & Logic Design: 14 Derivation of State Graphs and TablesDocument17 pagesSwitching Circuits & Logic Design: 14 Derivation of State Graphs and TablesAshish AgarwalNo ratings yet

- Ec 1201digital ElectronicsDocument17 pagesEc 1201digital ElectronicsSubathra Devi MourouganeNo ratings yet

- Sequential CircuitsDocument11 pagesSequential CircuitsUday DesirajNo ratings yet

- ELE2120 Digital Circuits and Systems: Tutorial Note 9Document25 pagesELE2120 Digital Circuits and Systems: Tutorial Note 9Nelson Ubaldo Quispe MNo ratings yet

- Fr6 FSM PassDocument67 pagesFr6 FSM PassMitroi ȘtefanNo ratings yet

- ITBP205 Digital Design and Computer OrganizationDocument12 pagesITBP205 Digital Design and Computer OrganizationReem AshrafNo ratings yet

- FSM 1Document145 pagesFSM 1Sriharsha EnjapuriNo ratings yet

- Clocked Sequential CircuitDocument33 pagesClocked Sequential CircuitMarco Antonio BussanichNo ratings yet

- Sequential Circuit Analysis Review: Flip-Flop VariationsDocument5 pagesSequential Circuit Analysis Review: Flip-Flop VariationsAlfi Muhammad Akbar BariaNo ratings yet

- Capstone ResearchProject Moore Mealy MachineDocument9 pagesCapstone ResearchProject Moore Mealy MachineAnish ChatterjeeNo ratings yet

- Finite State MachineDocument57 pagesFinite State MachinedoomachaleyNo ratings yet

- Sequential Circuit Analysis: State Tables State DiagramsDocument17 pagesSequential Circuit Analysis: State Tables State DiagramsAhmed Saad100% (1)

- Chapter 6 - Introduction To Sequential DevicesDocument62 pagesChapter 6 - Introduction To Sequential DevicesSarath Chandra SNo ratings yet

- Finite State Machine DesignDocument64 pagesFinite State Machine Designivanf15No ratings yet

- Chapter #8: Finite State Machine DesignDocument57 pagesChapter #8: Finite State Machine DesignAli AhmadNo ratings yet

- Esc201A: Introduction To Electronics: Sequential Circuit Design 2 Sequential Circuit Design - 2Document17 pagesEsc201A: Introduction To Electronics: Sequential Circuit Design 2 Sequential Circuit Design - 2Abhinay KumarNo ratings yet

- LogicDesign CHPT 10Document31 pagesLogicDesign CHPT 10john juanNo ratings yet

- Lab05 Flip FlopsDocument8 pagesLab05 Flip Flopskhanjamil12No ratings yet

- Experiment 9 Sequential Circuits Introduction To CountersDocument3 pagesExperiment 9 Sequential Circuits Introduction To CountersSai SaurabNo ratings yet

- ECE380 Digital Logic: Synchronous Sequential Circuits: Implementations Using D-Type, T-Type and JK-type Flip-FlopsDocument9 pagesECE380 Digital Logic: Synchronous Sequential Circuits: Implementations Using D-Type, T-Type and JK-type Flip-FlopsMoHsin KhNo ratings yet

- Lecture7 Chapter5 - Design of Clocked Sequential CircuitsDocument26 pagesLecture7 Chapter5 - Design of Clocked Sequential CircuitsHamza RiazNo ratings yet

- Question Bank Unit 4-1Document3 pagesQuestion Bank Unit 4-1birajkushwaha1996No ratings yet

- Digital Electonics DONEDocument19 pagesDigital Electonics DONEkassaroxzNo ratings yet

- LECTURE #16: Moore & Mealy Machines: EEL 3701: Digital Logic and Computer SystemsDocument8 pagesLECTURE #16: Moore & Mealy Machines: EEL 3701: Digital Logic and Computer SystemsNandlalYadavNo ratings yet

- Flip Flop Mealy and Moore ModelDocument25 pagesFlip Flop Mealy and Moore Modelsurajpb1989100% (1)

- Wint05 Exam2Document40 pagesWint05 Exam2Bruno SilvaNo ratings yet

- Sequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos TatasDocument22 pagesSequential Digital Circuits: Dr. Costas Kyriacou and Dr. Konstantinos Tatasvikramkolanu100% (2)

- EE200 Exp 11Document6 pagesEE200 Exp 11Tarunesh PandeyNo ratings yet

- De Unit4 NotesDocument127 pagesDe Unit4 NotesAravind RaoNo ratings yet

- Chapter 5 Synchronous Sequential CircuitDocument32 pagesChapter 5 Synchronous Sequential CircuitSenthur PriyaNo ratings yet

- Sequential Circuit AnalysisDocument13 pagesSequential Circuit AnalysismankindaNo ratings yet

- 19 Async Analysis and Design v1Document35 pages19 Async Analysis and Design v1muralik_64No ratings yet

- Basic Sequential Design Steps: Flip-Flop Inputs Primary OutputsDocument10 pagesBasic Sequential Design Steps: Flip-Flop Inputs Primary OutputsAnkur SinghNo ratings yet

- Synchronous CounterDocument12 pagesSynchronous CounterRajasekar PichaimuthuNo ratings yet

- Sequential LogicDocument139 pagesSequential Logicmdhuq1100% (1)

- Design of Sequential CircuitsDocument14 pagesDesign of Sequential CircuitsRaj RoyNo ratings yet

- Lect28 6Document3 pagesLect28 6Sumendra PandeyNo ratings yet

- Module - 6Document68 pagesModule - 6Shivanshu TripathiNo ratings yet

- Question Bank M Tech 2ND Sem Batch 2018Document31 pagesQuestion Bank M Tech 2ND Sem Batch 2018king khanNo ratings yet

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsFrom EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsRating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Price Indicator 21st OctDocument1 pagePrice Indicator 21st OctLakshmikanth MeduriNo ratings yet

- DDR ControllerDocument30 pagesDDR ControllerLakshmikanth MeduriNo ratings yet

- DFT SomeDocument79 pagesDFT SomeBhai BaiNo ratings yet

- Review of Electrical Sensors and ActuatorsDocument21 pagesReview of Electrical Sensors and ActuatorsManjula Udayanga HemapalaNo ratings yet

- Irp Test-1 (07!12!17) (Solution) (Jee Mains) Code-AbDocument20 pagesIrp Test-1 (07!12!17) (Solution) (Jee Mains) Code-Abvejoshi21699No ratings yet

- University of Cambridge International Examinations General CertificateDocument8 pagesUniversity of Cambridge International Examinations General CertificateHubbak KhanNo ratings yet

- Updated Resume - Kaushik SenguptaDocument3 pagesUpdated Resume - Kaushik SenguptaKaushik SenguptaNo ratings yet

- Nature of Urban Interventions in Changing The OldDocument10 pagesNature of Urban Interventions in Changing The OldAneesha MuthurajNo ratings yet

- Zapanta Vs PeopleDocument7 pagesZapanta Vs PeopleEricson Sarmiento Dela CruzNo ratings yet

- Effect of Reciprocal Teaching and Motivation On Reading Comprehension2016Document5 pagesEffect of Reciprocal Teaching and Motivation On Reading Comprehension2016Aqila HafeezNo ratings yet

- Experiment # 15: LABORATORY MANUAL For ENGR2860U-Fluid MechanicsDocument10 pagesExperiment # 15: LABORATORY MANUAL For ENGR2860U-Fluid MechanicsAbdullah Alshihri100% (1)

- Service Manual: DSC-F505VDocument34 pagesService Manual: DSC-F505VAnonymous Lfgk6vygNo ratings yet

- Iit Jee (Links)Document5 pagesIit Jee (Links)Tarun MankadNo ratings yet

- Special EducationDocument13 pagesSpecial EducationJanelle CandidatoNo ratings yet

- Surah Al Asr (Explanation)Document4 pagesSurah Al Asr (Explanation)Adil KhatriNo ratings yet

- EmphysemaDocument10 pagesEmphysemaNader Smadi100% (4)

- D Dy DT Q K DyDocument20 pagesD Dy DT Q K DyMohammed Al-OdatNo ratings yet

- 1 Year Bachillerato VERB TENSES REVIEWDocument4 pages1 Year Bachillerato VERB TENSES REVIEWLucía CatalinaNo ratings yet

- Field Manual: System 1010Dvn Nema Clamp-On Multi-Function FlowmeterDocument182 pagesField Manual: System 1010Dvn Nema Clamp-On Multi-Function FlowmeterRicardo souzaNo ratings yet

- Anime and MangaDocument14 pagesAnime and Mangapuspo agungNo ratings yet

- Body Repairs General Body RepairsDocument87 pagesBody Repairs General Body RepairsergdegNo ratings yet

- Rfa Ar04Document5 pagesRfa Ar04cuanicochorielynjuviNo ratings yet

- Op AmpDocument36 pagesOp AmpLord Nafaryus100% (1)

- MegaAudio ECatalougeDocument54 pagesMegaAudio ECatalougevicky9871No ratings yet

- Flexible Assessment Activities and Flexible Learning StrategiesDocument5 pagesFlexible Assessment Activities and Flexible Learning StrategiesAisa EdzaNo ratings yet

- Short Keys f1-f12Document2 pagesShort Keys f1-f12Farhan Khan NiaZiNo ratings yet

- BR Buyer Journey Assets enDocument1 pageBR Buyer Journey Assets enwfrancaassisNo ratings yet

- 19bch023 - 19bch002 (PC Term Paper)Document23 pages19bch023 - 19bch002 (PC Term Paper)Aditya JaniNo ratings yet

- Master Degree InformationDocument3 pagesMaster Degree InformationBivash NiroulaNo ratings yet

- Quiz Application: ISSN 2347-3983Document4 pagesQuiz Application: ISSN 2347-3983Syeda MidhatNo ratings yet

- 4 Ways To Change Your Life in 2023 PDFDocument24 pages4 Ways To Change Your Life in 2023 PDFHadjer ToumiNo ratings yet

- Selection Guide Specialty Carbon Blacks For PlasticsDocument8 pagesSelection Guide Specialty Carbon Blacks For Plasticsrahul_2005No ratings yet

- HOPE 12 Budget of WorkDocument2 pagesHOPE 12 Budget of WorkRonald Francis Sanchez VirayNo ratings yet

- Bonding QuizDocument7 pagesBonding Quiz卜一斐No ratings yet