Professional Documents

Culture Documents

Switched-Capacitor-Cell-Based Voltage Multipliers and DC-AC Inverters

Switched-Capacitor-Cell-Based Voltage Multipliers and DC-AC Inverters

Uploaded by

vinay kumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Switched-Capacitor-Cell-Based Voltage Multipliers and DC-AC Inverters

Switched-Capacitor-Cell-Based Voltage Multipliers and DC-AC Inverters

Uploaded by

vinay kumarCopyright:

Available Formats

1598 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 48, NO.

5, SEPTEMBER/OCTOBER 2012

Switched-Capacitor-Cell-Based Voltage

Multipliers and DCAC Inverters

Ke Zou, Student Member, IEEE, Mark J. Scott, Student Member, IEEE, and Jin Wang, Member, IEEE

AbstractIn this paper, several modular converter topologies

based on a switched-capacitor-cell concept are introduced for

high-power applications. Two types of switched-capacitor cells,

including the full cell and the half-cell, are discussed. The full

cell can be used for dcac inversion, and the half-cell is utilized

in both dcdc and dcac applications. A rotational charging

scheme is adopted for the half-cell-based dcdc voltage multiplier

to eliminate the large output capacitor that exists in many tra-

ditional switched-capacitor topologies. A soft-switching scheme,

which does not require extra components, is adopted to reduce

the switching loss and electromagnetic interference. A variable

switching frequency control scheme is proposed to realize soft

switching for dcac inverters. The experimental results on a 2-kW

prototype are presented to verify the proposed topologies.

Index TermsSoft switching, switched-capacitor converters,

variable frequency control.

I. INTRODUCTION

S

WITCHED-CAPACITOR converters contain only capac-

itors and switching devices. The absence of magnetic

components helps to shrink the system volume and cost. For

this reason, they have been extensively used in low-power

applications. Various topologies and control methods have

been proposed and applied [1][5]. However, many classical

switched-capacitor topologies, such as the traditional charge-

pump circuit, require either large voltage stress on components

or huge input/output capacitors. Moreover, the traditionally

uncontrolled capacitor charging current generates large current

stress on semiconductor switches, reduces the efciency of the

converter, and introduces a large amount of EMI noise, which

makes most classical switched-capacitor topologies and control

methods unsuitable for higher power applications.

Several topologies have been developed in recent years to

solve the aforementioned problems. For dcdc conversion, a

switched-capacitor dcdc converter based on the generalized

multilevel converter topology was presented in [6]. The 1-kW

prototype introduced in this paper can realize bidirectional

power conversion between a 42-V battery and 14-V or 42-V

Manuscript received June 18, 2011; revised November 9, 2011; accepted

February 9, 2012. Date of publication July 19, 2012; date of current version

September 14, 2012. Paper 2011-IPCC-357.R1, presented at the 2011 IEEE

Applied Power Electronics Conference and Exposition, Fort Worth, TX, March

611, and approved for publication in the IEEE TRANSACTIONS ON INDUSTRY

APPLICATIONS by the Industrial Power Converter Committee of the IEEE In-

dustry Applications Society. This work was supported by the National Science

Foundation under Project 1054479.

The authors are with the Department of Electrical and Computer En-

gineering, The Ohio State University, Columbus, OH 43210 USA (e-mail:

zou.35@buckeyemail.osu.edu; scott.585@osu.edu; wang@ece.osu.edu).

Color versions of one or more of the gures in this paper are available online

at http://ieeexplore.ieee.org.

Digital Object Identier 10.1109/TIA.2012.2209620

loads. In [7], a 3X (i.e., the output voltage is three times of

the input voltage) dcdc multiplier/divider was proposed, and

a 55-kW prototype for hybrid electric vehicles was built. In

[8], a multilevel modular capacitor-clamped dcdc converter

(MMCCC) topology was proposed with many benets, includ-

ing its modular structure, low current, and voltage stress of the

switches and its bidirectional operation capability. However, the

aforementioned topologies all require a large number of capac-

itors, which can signicantly increase the physical size and the

cost of the converter. Moreover, normally, only one xed output

voltage can be achieved for these topologies. Although special

control methods [7] can be adopted to realize several output

voltages, the controller complexity will be increased, and the

time response of the output voltage will be affected.

Charging current regulation is important for improving the

efciency of switched-capacitor converters. Several methods

have been proposed to regulate the charging current by us-

ing soft-switching methods. In [9][11], the quasi-resonant

switched-capacitor converters are investigated, where an extra

inductor is added to form an oscillation loop with the capacitors

to achieve soft switching. In [12], a soft-switching scheme that

does not require extra inductive components is proposed. Since

the charging current can be controlled by using soft-switching

methods, both the conduction loss and switching loss can be

largely reduced. This soft-switching method has been success-

fully applied to the MMCCC switched-capacitor topology [13].

Peak efciency of over 97% for a 630-W prototype has been

reported by further adopting an interleaving scheme [14].

For the dcac inversion, in [15], a Marx inverter was pro-

posed, which is based on the Marx generator concept in high-

voltage engineering. A Marx cell structure was generalized

from the Marx generator. By connecting several Marx cells in

series, multiple output voltage levels can be achieved. A similar

structure with the benets of common input and output grounds

was presented in [16]. The benets of Marx-cell-based inverters

include its multiple output voltage capability, the small number

of required capacitors, and its equal voltage stress on the

switches and capacitors. In [17] and [18], two other topologies

are provided that can realize multiple output voltage and can be

used for dc/ac inversion. However, since the capacitor charging

time in an inverter changes from cycle to cycle, the soft-

switching method aforementioned cannot be utilized. There-

fore, the capacitor charging current in a switched-capacitor

inverter has anextremelylarge peak value, which generates large

power losses as well as electromagnetic interference (EMI).

To solve the aforementioned problems, this paper extends the

Marx cell concept and proposes two different cell structures

the half-cell and the full cell. It can be seen that the Marx cell

0093-9994/$31.00 2012 IEEE

ZOU et al.: SWITCHED-CAPACITOR-CELL-BASED VOLTAGE MULTIPLIERS AND DCAC INVERTERS 1599

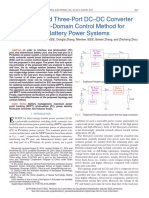

Fig. 1. Structure of switched-capacitor cells. (a) Full cell. (b) Half-cell.

(c) Series connection of switched-capacitor cells.

is equivalent to the half-cell. The half-cell-based dcdc multi-

plier adopts a rotational charging scheme and a soft-switching

scheme. As a result, the large output capacitor can be elimi-

nated, and the efciency can be increased. For dcac conver-

sion, both the half-cell-based and the full-cell-based inverters

are presented. To realize soft switching over the entire operation

range of the inverter and reduce the peak charging current, a

variable switching frequency control scheme is proposed.

The rest of this paper is organized as follows. in Section II,

the proposed half-cell and full-cell topologies are introduced.

The half-cell-based dcdc multiplier, including its structure and

control scheme, is presented in Section III. Section IV shows

the half-cell-based and full-cell-based dcac inverter topolo-

gies. The multicarrier pulsewidth modulation (PWM) control

method and the variable frequency control method are also

presented. Finally, the experimental results on a 2-kW modular

converter prototype are presented in Section V.

II. BASIC SWITCHING CELLS

A. Cell Structure

The full switched-capacitor cell is shown in Fig. 1(a). It is a

four-port system consisting of four switches and one capacitor.

The half-cell (Marx cell) is shown in Fig. 1(b), with only

three switches and one capacitor. The nal converter is a series

connection of these cells, as shown in Fig. 1(c). Each cell is

charged by the cell of the previous stage and discharges to the

cell of the next stage. Here, the voltage source is placed before

the rst cell, whereas an alternative method is to put the voltage

source in the middle of the series so that the current stress of

central cells can be reduced.

Fig. 2 shows the switching states of one full cell. In this

gure, C

1

is the capacitor from the previous stage and has a

voltage of V

C

. Port 2 is assumed to have a voltage potential

of V

2

. Among the four switches in Fig. 2(a), S

1

and S

2

form

one group and are switched together. S

3

and S

4

are independent

switches and cannot be turned on along with any other switches.

As a result, there are three switching states.

i) S

1

and S

2

are on [see Fig. 2(b)]. The two capacitors are

connected in parallel. Port 4 has the same potential as port

2. The potential of ports 1 and 3 is V

2

+V

C

.

Fig. 2. Operation states of a full cell. (a) Full switched-capacitor cell.

(b) State I. (c) State II. (d) State III.

ii) S

3

is on [see Fig. 2(c)]. Ports 1 and 4 have the potential of

V

2

+V

C

, and port 3 has a potential of V

2

+ 2V

C

.

iii) S

4

is on [see Fig. 2(d)]. Port 3 has a potential of V

2

. The

potentials of ports 1 and 4 are V

2

+V

C

and V

2

V

C

,

respectively.

In switching state I, two capacitors are connected in parallel,

and the one with higher voltage charges the other. In states II

and III, the two capacitors are connected in series; therefore,

various voltage levels can be achieved. For one single full

switching cell, there are three achievable voltage levels for

port 4: V

2

, V

2

+V

C

, and V

2

V

C

. Port 3 also has three

achievable voltage levels: V

2

, V

2

+V

C

, and V

2

+ 2V

C

.

By connecting N switching cells in series, there are 2N + 1

achievable levels between port 3 or port 4 of the last stage and

port 2 of the rst stage. If port 2 of the rst stage has zero

voltage potential, then for port 4 of the last stage, the achievable

voltage levels are i V

C

, where i is an integer between N

and N. Since both positive and negative voltage levels can be

generated in a symmetric manner, the full switched-capacitor

cell is suitable for dcac inverting applications.

For the half switched-capacitor cell, there are only two

switching states: State I, where S

1

and S

2

are on, and state II,

where S

3

is on (see Fig. 2(b) and (c), respectively). The number

of achievable voltage levels for port 3 or port 4 in a converter

with N stages of half switched-capacitor cell is N + 1. If port 2

of the rst stage has zero voltage potential, then for port 3 of the

last stage, the achievable voltage levels are (i + 1) V

C

, where

i is an integer between 0 and N. The dcdc voltage multiplier

can be realized by connecting the load to port 2 of the rst stage

and port 3 of the last stage.

For the half-cell, negative voltage can also be achieved by

connecting the previous stage between ports 3 and 4. This

way, the dcac inverting operation can be achieved by employ-

ing half-cells, which is the Marx inverter topology presented

in [15].

B. Component Selection of Proposed Cells

For a half-cell, the diagonal switch S

3

only conducts

forward current and blocks forward voltage. For the other

two switches S

1

and S

2

, however, in order to prevent the

1600 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 48, NO. 5, SEPTEMBER/OCTOBER 2012

Fig. 3. Realization of switching cells using MOSFETs. (a) Half-cell circuit.

(b) Full-cell circuit.

shoot-through when S

3

is closed, one switch has to block the

forward voltage and another has to block the reversed voltage.

As such, there are two forward-current-conductingforward-

voltage-blocking switches such as an insulated gate bipolar

transistor (IGBT) or a MOSFET and one forward-current-

conductingreversed-voltage-blocking switch such as a diode.

To achieve bidirectional power ow capability of the converter,

all switches can be realized by MOSFETs, and some MOSFETs

operate in the third quadrant.

For a full cell, when it operates in state II [see Fig. 2(c)], the

diagonal switch S

4

needs to block a voltage that equals to two

times the capacitors voltage V

C

. Similarly, the diagonal switch

S

3

needs to block 2V

C

in state III. The other two switches need

to block both positive and negative voltages during states II and

III. As a result, the two diagonal switches S

3

and S

4

can be

realized by MOSFETs or IGBTs with a voltage rating of 2V

c

and a parallel free-wheeling diode, whereas each of the other

two switches, i.e., S

1

and S

2

, requires two MOSFETs or IGBTs,

with a voltage rating of V

C

. The realizations of the half-cell and

the full cell using MOSFETs are shown in Fig. 3(a) and (b),

respectively.

III. HALF-CELL-BASED DCDC MULTIPLIER

A. Structure

For half-cell-based dcdc multipliers, port 3 of the last stage

and port 2 of the rst stage are used as output ports to achieve

the largest voltage transfer ratio. Although N + 1 voltage levels

can be achieved between these two ports in an N-stage half-

cell multiplier, it is not possible to have (N + 1):1 voltage

transfer ratio since there is only one switching state to achieve

(N + 1) V

C

, and the capacitors in this state are all in the

discharging mode. As a result, the output voltage cannot be

maintained.

With this modular switching cell structure, a rotationally

charging scheme can be adopted to reduce the requirements

of the output capacitor. This is achieved by adding one extra

half-cell to the multiplier. By doing this, the multiplier has

N + 1 stages, and two switching states are available to achieve

an output of (N + 1) V

C

. This extra available state makes

it possible to generate a stable output voltage by charging the

capacitors rotationally. At any time, except the dead time, there

will be one capacitor in the charging state, and other capacitors

are discharging to the load in series. The output voltage is

Fig. 4. DCDC voltage doubler based on half-cells.

Fig. 5. Equivalent circuit when C

1

is being charged.

stable, and only a small output capacitor is needed to lter

out the voltage ripple during the dead time. Another benet of

the proposed topology is that multiple output voltages can be

achieved. For example, a three-stage multiplier with an input

voltage of V

in

can output V

in

, 2 V

in

, and 3 V

in

. This rotationally

charging scheme and multiple output voltage capability can

also be found in previous studies such as [17] and [18].

B. Soft-Switching Principle

One major problem of a switched-capacitor circuit is the

unregulated charging current during the capacitor charging

process, which generates large in-rush current and EMI noise.

In [12], a soft-switching scheme is proposed by utilizing the

stray inductance in the circuit to resonate with the main ca-

pacitors. This paper employs the same idea; however, due to

the particular structure of the proposed multiplier, the soft-

switching scheme has some unique features.

Fig. 4 shows a voltage doubler that consists of two half-cells.

The dc source is placed in the middle so that the switches of

the both cells experience the same charging current. In this

structure, when S

4

and S

5

are closed, the charging current of C

2

ows from the source to the drain of S

4

, instead of the normal

drain-to-source conduction mode. Therefore, S

4

operates in the

third quadrant. S

2

on the other cell has the same third-quadrant

operation mode. Other MOSFETs in the circuit operate in

the rst quadrant. The stray inductance values, expressed as

L

s1

L

s5

, mainly come from the stray inductance of cables,

the package inductance of the MOSFETs, and the equivalent

series inductance (ESL) of the capacitors. If the layout of each

cell is the same, the stray inductance difference among different

cells can be considered small; therefore, a single resonant

switching frequency works for both cells.

The equivalent circuits in the two switching states are shown

in Figs. 5 and 6. To simplify the analysis, the load current is

ZOU et al.: SWITCHED-CAPACITOR-CELL-BASED VOLTAGE MULTIPLIERS AND DCAC INVERTERS 1601

Fig. 6. Equivalent circuit when C

2

is being charged.

Fig. 7. Equivalent circuit during the dead time.

assumed to be constant as I

d

. The capacitor charging currents

are named as I

C1

and I

C2

, which ow from the voltage source

to C

1

and C

2

, respectively. It can be seen that S

1

and S

5

, which

operate in the rst quadrant, carry only the capacitor charging

current. On the other hand, S

2

and S

4

, which operate in the third

quadrant, carry both the capacitor charging current and the load

current I

d

.

The proposed soft-switching scheme involves choosing a

switching frequency such that the charging current drops to zero

at the time when S

1

or S

5

are turning off. As a result, zero-

current switching is realized for S

1

and S

5

. For S

2

and S

4

, at

the moment when they are turning off, the remaining current is

I

d

. Due to the third-quadrant operation, their body diodes D

2

and D

4

will immediately take over the current. As a result, the

soft switching of S

2

and S

4

is achieved. After the dead time,

the current is shifting from diode D

2

or D

4

to the diagonal

MOSFETs S

3

or S

6

; therefore, there will be reverse recovery

loss of diodes. However, if SiC diodes is used to replace D

2

and D

4

, this reverse recovery loss can be minimized.

During the dead time, the load current ows through the body

diodes D

1

, D

2

, D

4

, and D

5

. Assuming that the two half-cells

are made the same and that the dead time is long enough for any

oscillation transients to decay, the load current will be equally

split into two parts, as shown in Fig. 7. The only voltage across

these diodes is the diode forward voltage; therefore, when their

corresponding MOSFETs are turning on after the dead time,

they will experience a minimum voltage. Therefore, the zero-

voltage turn-on can be achieved for S

1

, S

2

, S

4

, and S

5

.

It should be noted that this soft-switching scheme only ap-

plies to the MOSFETs that are used to charge the capacitors. For

the other two MOSFETs (S

3

and S

6

), soft switching cannot be

achieved using this scheme. However, since the main purpose

of utilizing soft switching is to reduce the associated power loss

and EMI noise due to unregulated charging current, this soft-

Fig. 8. Charging current of capacitor C

1

.

switching scheme can still help the proposed topology in large-

power applications.

If the equivalent resistance in the charging loop can be

neglected, the impedance of the capacitor charging loop can be

represented by a simple LC circuit. Under this assumption, the

capacitor charging current has a sinusoidal shape. The current

prole of I

C1

is shown in Fig. 8. The initial current I

0

is

due to the load current conduction during the dead time before

S

1

and S

2

are turned on. Therefore, the charging current has

a negative initial angle

0

. The current reaches zero again at

the angle , which is the soft-switching point. This means that

the charging process needs to be nished in more than half an

oscillation cycle to achieve soft switching.

After the charging process, the capacitor discharges to the

load with the load current I

d

. Therefore, the capacitor current

can be written as

i

C1

(t) =

_

I

peak

sin(

osc

t

0

), 0 < t < DT

S

I

d

, DT

S

< t < T

S

(1)

where D is the duty ratio of S

1

and S

2

, and T

S

is the switching

cycle. I

peak

and

osc

are the amplitude and angular frequency

of the sinusoidal part of the charging current, respectively.

The relationship between

osc

and angular switching frequency

sw

is

osc

=

+

0

2D

sw

. (2)

Assuming that, during the dead time, the free-wheeling load

current is evenly distributed into two branches, then the initial

value of the capacitor charging current I

0

is

I

0

= i

c1

(0) =

1

2

I

d

(3)

and

0

can be found from the following relationship:

I

d

2

= I

peak

sin

0

. (4)

On the other hand, due to the current balance of the capacitor

in one switching cycle

DT

S

+

0

0

(I

peak

sin )d = I

d

(1 D)T

S

. (5)

Solving (5),

1 + cos

0

sin

0

= 2( +

0

)

_

D

1 D

_

. (6)

1602 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 48, NO. 5, SEPTEMBER/OCTOBER 2012

Fig. 9. Current proles for the switches in the left cell.

Equation (6) gives the relationship between

0

and the duty

ratio D. For the dcdc voltage doubler, since D = 0.5,

0

can

be calculated to be 0.29

or 16.6

.

From (4), the peak value of the capacitor charging current

I

peak

can be calculated as

I

peak

=

I

d

2 sin(

0

)

= 1.75I

d

. (7)

The capacitor charging time T

ch

can be calculated using

T

ch

=

+

0

2

T

osc

(8)

where T

osc

is the oscillation cycle of the charging current.

The soft-switching frequency f

sw

can be calculated as

follows:

f

sw

=

2D

( +

0

)T

osc

. (9)

For the switched-capacitor voltage doubler, D is 0.5. Thus,

f

sw

=

( +

0

)T

osc

. (10)

C. Power Loss Analysis on the Proposed Voltage Doubler

The switching losses on switches S

1

, S

2

, S

4

, and S

5

of the

proposed voltage doubler can be neglected due to their soft-

switching operation. The switching loss analysis on the other

two switches (S

3

and S

6

) is similar to the analysis in traditional

boost converters, which is not elaborated here.

There are three types of conduction losses: the conduction

loss on the switches, on two main capacitors, and on the input

capacitor. The conduction loss can be calculated from the RMS

value of their corresponding current.

RMS Current of Switches: Fig. 9 shows the current proles

of the three switches in the left cell (i.e., S

1

, S

2

, and S

3

). S

1

and

S

2

only conduct in the rst half cycle, and S

3

only conducts

in the second half cycle. S

1

carries the capacitor charging

current; therefore, it shares the same current as the charging

current of C

1

. The third-quadrant-operated switched S

2

carries

the capacitor charging current and the load current. The switch

S

3

carries only the load current during the second half cycle.

The three current can be written as

I

S1

=

_

1.75I

d

sin

_

2(+

0

)

T

S

t

0

_

, 0<t <T

S

/2

0, T

S

/2<t <T

S

(11)

I

S2

=

_

1.75I

d

sin

_

2(+

0

)

T

S

t

0

_

+I

d

, 0<t <T

S

/2

0, T

S

/2<t <T

S

(12)

I

S3

=

_

0, 0<t <T

S

/2

I

d

, T

S

/2<t <T

S

.

(13)

The RMS value of the three currents can be calculated as

I

S1_RMS

=

_

1

T

T/2

_

0

_

1.75I

d

sin

_

2(+

0

)

T

S

t

0

__

2

dt

=0.833I

d

(14)

I

S2_RMS

=

_

1

T

T/2

_

0

_

1.75I

d

sin

_

2(+

0

)

T

S

t

0

_

+I

d

_

2

dt

=1.447I

d

(15)

I

S3_RMS

=

_

1

T

T/2

_

0

I

2

d

dt = 0.707I

d

. (16)

Due to the symmetric structure of this doubler, the three

switches in the right cell have the same current prole and RMS

values as the corresponding switches in the left cell.

RMS Current of the Two Main Capacitors: The two main

capacitors experience the same current, as the current shown in

Fig. 8 when D is 0.5. The RMS value of the current on the two

capacitors can be calculated as

I

C1_RMS

=

_

1

T

T/2

_

0

_

1.75I

d

sin

_

2( +

0

)

T

S

t

0

__

2

dt+

1

2

I

2

d

= 1.093I

d

. (17)

RMS Current of the Input Capacitor: The input current is

the sum of I

S2

and I

S4

. It has an average value of 2I

d

and

an ac ripple. The ac part of the input current ows into the

input capacitor and generates loss. The RMS value of the input

current ripple is

I

Cin_RMS

=

_

1

+

0

0

(1.75I

d

sin +I

d

2I

d

)

2

d

=0.387I

d

. (18)

Table I provides the RMS current and the conduction loss of

different components in the proposed voltage doubler. R

S

, R

C

,

and R

C_in

represent the ON-state resistance of the switch, the

ZOU et al.: SWITCHED-CAPACITOR-CELL-BASED VOLTAGE MULTIPLIERS AND DCAC INVERTERS 1603

TABLE I

RMS CURRENT AND CONDUCTION LOSS OF DIFFERENT

COMPONENTS IN THE PROPOSED VOLTAGE DOUBLER

TABLE II

LOSS COMPARISON BETWEEN THE PROPOSED VOLTAGE DOUBLER

AND THE TRADITIONAL VOLTAGE DOUBLER WITH

SOFT-SWITCHING CAPABILITY

equivalent series resistance (ESR) of the main capacitors, and

the ESR of the input capacitor, respectively.

Table II provides a comparison between the proposed voltage

doubler and the traditional switched-capacitor voltage dou-

bler with soft-switching capability [12]. P

loss_S

, P

loss_C

, and

P

loss_Cin

represent the total conduction loss on all of the

switches, on the two main capacitors, and on the input capaci-

tor, respectively. The proposed switched capacitor has a much

smaller input current ripple and conduction loss compared with

the traditional voltage doubler. This is because, in the proposed

topology, the voltage source is always connected in series with

one capacitor. Therefore, half of the power is directly sent to

the load.

D. Stability Analysis of the Proposed Voltage Doubler

The stability of the proposed voltage doubler is analyzed

using the state-space averaging method. The state vector for the

voltage doubler in Fig. 4 is

x(t) = [V

C

1

, V

C

2

, i

L

S1

, i

L

S2

, i

L

S4

, i

L

S5

]

T

. (19)

To simplify the analysis, it is assumed that C

1

= C

2

= C and

L

S1

= L

S2

= L

S4

= L

S5

= L. The doubler is modeled as

x(t) = Ax(t) +Bu(t) (20)

where A = A

1

d +A

2

(1 d) and B = B

1

d +B

2

(1 d).

In Fig. 4, the state equations can be written as

v

C

1

=

1

C

i

L

S1

v

C

2

=

1

C

(i

L

S1

i

L

S2

)

i

L

S1

=

1

L

((i

L

S2

i

L

S1

)R v

C

1

v

C

2

)

i

L

S2

=

1

L

(V

in

+v

C

2

(i

L

S2

i

L

S1

)R)

i

L

S4

= 0

i

L

S5

= 0.

(21)

Then, A

1

and A

2

can be obtained as

A

1

=

0 0

1

C

0 0 0

0 0

1

C

1

C

0 0

1

L

1

L

R

L

R

L

0 0

0

1

L

R

L

R

L

0 0

0 0 0 0 0 0

0 0 0 0 0 0

A

2

=

0 0 0 0

1

C

1

C

0 0 0 0 0

1

C

0 0 0 0 0 0

0 0 0 0 0 0

1

L

0 0 0

R

L

R

L

1

L

1

L

0 0

R

L

R

L

.

This voltage doubler operates with a duty ratio of 50%. Thus

A =0.5 A

1

+ 0.5 A

2

= 0.5 (A

1

+A

2

) (22)

A =

1

2

0 0

1

C

0

1

C

1

C

0 0

1

C

1

C

0

1

C

1

L

1

L

R

L

R

L

0 0

0

1

L

R

L

R

L

0 0

1

L

0 0 0

R

L

R

L

1

L

1

L

0 0

R

L

R

L

. (23)

The following characteristic polynomial can be obtained

from (23):

6

+

4R

5

L

+

(6L + 4R

2

C)

4

+ 14R

3

L

2

C

+

(5L + 4R

2

C)

2

+ 6R

L

3

C

2

+

R

2

L

4

C

2

= 0. (24)

Calculations have been performed on the six eigenvalues of

A to determine their variation with changes in load resistance.

In these calculations, L and C are set to be 58.8 nH and 47 F,

respectively, which is a value measured on the testing prototype.

Fig. 10 shows the locus of the six eigenvalues as R decreases

from20 to 1 . The real part of the eigenvalues stays on the left-

hand side of the imaginary axis, showing the voltage doubler is

stable in this load range.

IV. FULL-CELL-BASED AND HALF-CELL-BASED

DCAC INVERTERS

A. Full-Cell-Based Inverters

From the analysis in Section II, for an N-stage full-switched-

capacitor-cell-based converter, there are 2N + 1 achievable

voltage levels between port 2 of the rst stage and port 4 of

1604 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 48, NO. 5, SEPTEMBER/OCTOBER 2012

Fig. 10. Locus of eigenvalues with a resistance from 20 to 1 .

Fig. 11. Five-level full-cell switched-capacitor inverter.

the last stage. As a result, to realize a 2N + 1 level of inverter,

only N full cells are required.

Fig. 11 shows one ve-level dcac inverter consists of one

full cell and four extra switches S

5

S

8

. The extra switches are

always connected to the load and function as current bypass

routes. By adding these four switches, the total achievable

voltage levels can be increased by 2. Therefore, only N 1 full

cells are required to have a 2N + 1 inverter. In Fig. 11, one full

cell is enough to realize a ve-level inverter. It should be noted

here that this inverter has a good switching redundancy, which

can help to balance the capacitor voltage and improve the fault

tolerance capability of the circuit.

B. Half-Cell-Based Inverters

Due to the high switching component requirements for the

full-cell-based inverter, half-cell-based inverters can be the

alternative choice. To realize a 2N + 1-level inverter, 2N half-

cells are required. If four extra bypass switches are employed,

2N 2 half-cells are required to have a 2N + 1-level inverter.

The number of stages required for a half-cell-based inverter is

two times the requirement for a full-cell-based inverter. The

capacitor count is doubled, and more current stress is added to

central cells.

A half-cell-based ve-level inverter is shown in Fig. 12. This

topology was introduced in [15]. It consists of two half-cells

and four extra bypass switches S

7

S

10

.

Fig. 12. Five-level half-cell switched-capacitor inverter.

Fig. 13. Six sections for a ve-level switched-capacitor inverter.

C. Multicarrier PWM Control Method for a Five-Level

Switched-Capacitor Inverter

The design of a high-power switched-capacitor dcac in-

verter is more complex than the dcdc multiplier. The main

reason is that the duty ratio of the inverter changes from cycle

to cycle, similar with the capacitor charging time. Therefore,

the charging current cannot be well controlled. Two methods

are proposed to solve this problem: a multicarrier PWM control

method and a soft-switching scheme using variable frequency

control.

The multicarrier PWM control scheme is used to elimi-

nate unnecessary capacitor charging. The half-cell-based ve-

level inverter, as shown in Fig. 12, is used to illustrate this

method. Based on the capacitor charging characteristics, the

voltage modulation waveform for this inverter can be divided

into six sections, as shown in Fig. 13. The angle

1

in

Fig. 13 can be calculated by using the modulation index m

a

as follows:

1

= sin

1

_

1

2m

a

_

. (25)

Table III shows seven switching vectors used in this control

scheme. In order to minimize the capacitor charging loss, the

capacitor charging and discharging only occur in Sections II

and V, where positive or negative 2 V

in

is needed. In other

sections, where the inverter only output V

in

or zero voltage,

the capacitors are in the idle state, and there is no charging

activity. The source is directly connected to the load to output

V

in

(vector V

3

) or V

in

(vector V

5

), and it is bypassed when

zero voltage is needed (vector V

4

). In these regions, the inverter

functions as a normal H-bridge inverter.

ZOU et al.: SWITCHED-CAPACITOR-CELL-BASED VOLTAGE MULTIPLIERS AND DCAC INVERTERS 1605

TABLE III

SWITCHING VECTORS OF THE FIVE-LEVEL SWITCHED-CAPACITOR INVERTER

D. Soft-Switching Scheme for Switched-Capacitor Inverters

To realize soft switching at Sections II and V, a variable

frequency control scheme is proposed. In this scheme, the

switching frequency changes with the duty ratio to maintain a

constant capacitor charging time. Therefore, soft switching can

be realized for all cycles.

The relationship between the charging time and the instanta-

neous duty ratio is

T

ch

(t) = (1 D(t))

1

f

sw

(t)

. (26)

Note here the instantaneous duty ratio D(t) is dened as

D(t)=

_

2m

a

sin(t)1,

1

<t <

1

2m

a

sin(t)1, +

1

<t <2

1

.

(27)

The switching frequency can be calculated from (8) and (26)

as follows:

f

sw

(t) =

(1 D(t)) 2

+

0

(t)

1

T

osc

. (28)

Equation (28) provides a relationship between D(t) and the

switching frequency. Since

0

only depends on D(t), a lookup

table of

0

can be made for different duty ratios to expedite the

calculation of the switching frequency in real applications.

It should be noted that the switching frequency should have a

low limit. Otherwise, the capacitor will be overdischarged. The

capacitor voltage variation in one switching cycle is

V

C

=

1

C

I

d

(t)D(t)

1

f

sw

(t)

=

1

C

I

d

(t)T

osc

+

0

(t)

2

_

1

1 D(t)

1

_

. (29)

It is shown from (29) that the capacitor voltage ripple in-

creases with the load current I

d

(t) as well as D(t). The worst

scenario is at unity power factor, in which the load current I

d

(t)

and D(t) reach their peak value simultaneously. From (27),

D

max

(t) = 2m

a

1. Then, the peak capacitor voltage ripple is

V

C_max

=

1

C

I

d_peak

T

osc

+

0

(t)

2

_

2m

a

1

2 2m

a

_

. (30)

The initial angle

0

can be neglected at large duty ratio

conditions, due to the fact that

0

becomes negligible when the

peak current is large; then, V

C_max

can be estimated as

V

C_max

1

2C

I

d_peak

T

osc

_

2m

a

1

2 2m

a

_

. (31)

The peak capacitor charging current can be calculated as

follows:

(1 D(t))

0

I

ch_peak

sin()d = D(t)I

d

(t). (32)

Solve (32) as follows:

I

ch_peak

=

_

1

22m

a

sin()

1

_

(1+cos(

0

))

I

d

(t). (33)

Under the condition where the power factor is large, the peak

current occurs near the peak voltage point, and cos(

0

) 1;

then,

I

ch_peak

2

_

1

2 2m

a

1

_

I

d_peak

. (34)

Equation (34) gives the estimated maximum capacitor charg-

ing current of the proposed method. It can be seen that both

the modulation index and the load current affect the maximum

charging current.

The third-quadrant operated switches (S

1

and S

4

in Fig. 12),

which carry both the capacitor charging current and load cur-

rent, experience the highest current stress

I

S

1

_peak

_

4 4m

a

2

+ 1

_

I

d_peak

. (35)

Given the peak load current and maximum safety current of

the switching devices, the maximum modulation index can be

calculated from (35).

E. Simulation Results

A simulation on a 20-kVA switched-capacitor inverter has

been performed using PSIM to verify the control method pro-

posed in this paper. In this simulation, the dc input of this

1606 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 48, NO. 5, SEPTEMBER/OCTOBER 2012

Fig. 14. Simulation results of the inverter.

Fig. 15. Frequency spectrum of the output voltage.

inverter is 300 V, and the modulation index is 0.8. The load

is a constant RL load with resistance of 2 and inductance

of 3.5 mH. The power factor of this converter is 0.83. To

realize soft switching at around 20 kHz, the loop inductance

is selected to be 200 nH, and the capacitance of the capacitor

is 300 F.

Fig. 14 shows the output voltage, output current, the current

of S

2

, and the switching frequency. It can be seen that, the

switching frequency is kept constant at 20 kHz in Sections I,

III, IV, and VI. In Sections II and V, where capacitor charging

occurs, the switching frequency varies from 15 to 25 kHz. The

peak current of S

2

is about 426 A, whereas the peak load current

is 197 A. This ratio of peak charging current over peak load

current is 2.16, which is consistent with the estimated value of

2.36 from (34).

Fig. 15 shows the frequency spectrum of the output voltage.

Because of the variable frequency control, there is a band of

frequency components between 15 and 25 kHz.

V. EXPERIMENTAL RESULTS

A group of 1-kW half-cell prototypes has been built to verify

the ideas presented in this paper. The photograph of this cell

is shown in Fig. 16. Three MOSFETs (IRFI4410ZPbF) are

placed in parallel to form one switching device. To reduce the

Fig. 16. Photograph of the prototype cell.

Fig. 17. Input and output voltage waveform of the voltage doubler.

reverse recovery loss of the body diode, a power Schottky diode

(STPS30100ST) is used. Ten 100-V 4.7-F ceramic capacitors

(C5750X7R2A475K) are used together as the main capacitor.

The soft-switching frequency of a voltage doubler is measured

at an input voltage of 5 V and room temperature. When the

switching frequency is adjusted to 62.7 kHz, the zero-current

turn-off is achieved. With the assumption that the capacitance

of the capacitor under this test condition is 47 F, the total loop

stray inductance can be calculated as 117.6 nH.

A. DCDC Multiplier Test

A half-cell dcdc voltage doubler, which consists of two

prototype boards, is used to verify the soft-switching scheme

and the efciency. The circuit topology is shown in Fig. 4. The

dead time is set to be 200 ns. A small 10-F lm capacitor

is added to the output terminal to lter out the ripples during

the dead time. At an input voltage of 40 V, the zero-current

turn-off is achieved for S

1

and S

5

at a switching frequency of

75.9 kHz. Compared with the case when the input voltage is

5 V, the soft-switching frequency is increased, which is because

the capacitance of the ceramic capacitors decreases with the

increase in voltage.

Fig. 17 shows the input and output voltage together at a

load current of 10 A. Fig. 18 shows with the drainsource

voltage V

s1

and the drain current I

S1

of S

1

. It can be seen that

I

S1

drops to zero before the switching transient; therefore, the

ZOU et al.: SWITCHED-CAPACITOR-CELL-BASED VOLTAGE MULTIPLIERS AND DCAC INVERTERS 1607

Fig. 18. Current and turn-off voltage of S

1

.

Fig. 19. Efciency curve of the proposed dcdc multiplier.

zero-current turn-off is realized. The peak value of I

S1

is

17.2 A, which is consistent with (7).

Fig. 19 shows the efciency of the prototype from 200 to

2000 W with 40-V xed input voltage. It is measured with a

Yokogawa WT 3000 power meter and LEM IT 700-S high-

performance current transducer.

Fig. 20 shows the calculated power-loss breakdown among

different components at an input power of 1000 W. The cal-

culation on conduction losses is based on Table I. Since the

converter is built on a printed circuit board (PCB) with 2 OZ/ft

2

and a trace width of 300500 mils, the loss on PCB traces

contributes to a large portion (around 30%40%) of the total

loss. Therefore, in this power-loss breakdown, the resistance

values of the capacitor and switches are estimated together with

the ac resistance (at 70 kHz) of the PCB traces that they are

connected to. The switches have an average resistance of 8 m.

The resistance of the main capacitors and the input capacitor

is estimated to be 3.4 and 10 m, respectively. The switching

power loss of the two diagonal switches S

3

and S

6

is estimated

using the turn-on time and turn-off time of the MOSFETs from

the datasheet. The diode loss is the conduction loss of the four

Schottky diodes during the dead time. Other losses include

the conduction losses on the connection cables, the reverse

recovery loss of the diodes, the loss due to charging the body

capacitance of the MOSFETs during operation, and estimation

error.

Fig. 20. Breakdown of power loss at input power of 1000 W.

Fig. 21. Input and output voltage waveforms of the inverter.

The control power contributes to around 25% of the total

loss. The conduction loss of the switches and capacitors con-

sists of more than 45% of the total loss. The switching loss is

only 12% of the total loss, which proves the effectiveness of the

soft-switching method.

B. DCAC Inverter Test

A ve-level dcac inverter is built and tested using the

switching-cell prototypes. The circuit structure is shown in

Fig. 12. It is realized by four switched-capacitor prototype

boards. The modulation index is set to be 0.8. An adjustable

RL load with a constant power factor of 0.83 is used. In

the experiment, the switching frequency changes from 48.6 to

83.3 kHz to realize the soft switching for all capacitor charging

cycles.

Fig. 21 shows the waveforms of input voltage V

in

and output

voltage V

out

at a load condition of 17.4 mH and 9.4 . The

active power at this load condition is 272 W. The RMS value

of the fundamental output voltage and current is 58.74 V and

5.38 A, respectively. The RMS value of the total output voltage

is 62 V. According to IEEE Standard 519 [19], in which the total

harmonics distortion (THD) is calculated up to 40th order, the

voltage THD is 4.98%. The main reason for the harmonics is

1608 IEEE TRANSACTIONS ON INDUSTRY APPLICATIONS, VOL. 48, NO. 5, SEPTEMBER/OCTOBER 2012

Fig. 22. Waveforms of the output current I

d

and the charging current I

C1

.

Fig. 23. Zoomed-in capacitor charging current of the inverter.

the large stray inductance of the current paths when the inverter

functions as an H-bridge inverter. This occurs because four

identical prototype boards are connected using external cables

in this experiment, and unnecessary large inductance is present

even if the capacitor charging is not required. An integrated

inverter design can help to optimize the stray inductance dis-

tribution and solve this problem.

Fig. 22 shows the waveforms of load current I

d

and the

charging current of capacitor C

1

. The peak value of I

C1

is

21 A, whereas the peak value of I

d

is 9 A. The ratio between the

two peak values is 2.33, which is consistent with the estimation

result of (34).

Fig. 23 shows the zoomed-in view of the capacitor charging

current of C

1

. It can be seen that the zero-current switching is

realized for all cycles.

Fig. 24 shows the efciency curve of the proposed dcac

inverter with an input power from100 to 1000 W. The efciency

value is about 3% lower than the efciency of the voltage

doubler. The main reason is that four extra switching devices

are involved in the inverter topology, which introduce more

conduction loss and control power loss. In addition, the peak

value of the charging current of the inverter is higher than

that of the voltage doubler, which generates higher conduction

loss.

Fig. 24. Efciency curve of the proposed dcac inverter.

VI. CONCLUSION

This paper introduced two types of switched-capacitor cells:

the half-cell and the full cell. Both the dcdc multipliers and

the dcac inverters based on these cells are analyzed. For the

dcdc multiplier, a rotational charging scheme is proposed;

therefore, the large output capacitor required by traditional

switched-capacitor topologies can be eliminated. For the dcac

inversion, a multilevel inverter with voltage boost function can

be realized by using either the full cell or the half-cell. To

increase the efciency, a soft-switching scheme without adding

extra components is adopted, and a variable frequency control

for the inverter is proposed to realize full-range soft switching.

The proposed topologies and control methods can be used in

applications with a power range from subkilowatts to tens of

kilowatts.

REFERENCES

[1] A. Ioinovici, Switched-capacitor power electronics circuits, IEEE

Circuits Syst. Mag., vol. 1, no. 3, pp. 3742, Third Quarter, 2001.

[2] H. Chung, Design and analysis of a switched-capacitor-based step-up

dc/dc converter with continuous input current, IEEE Trans. Circuits Syst.

I, Fundam. Theory Appl., vol. 46, no. 6, pp. 722730, Jun. 1999.

[3] H. S. Chung, A. Ioinovici, and W. Cheung, Generalized structure of bidi-

rectional switched-capacitor DC/DC converters, IEEE Trans. Circuits

Syst. I, Fundam. Theory Appl., vol. 50, no. 6, pp. 743753, Jun. 2003.

[4] F. L. Luo and H. Ye, Positive output multiple-lift push-pull switched-

capacitor Luo-converters, IEEE Trans. Ind. Electron., vol. 51, no. 3,

pp. 594602, Jun. 2004.

[5] B. Arntzen and D. Maksimovic, Switched-capacitor DC/DC converters

with resonant gate drive, IEEE Trans. Power Electron., vol. 13, no. 5,

pp. 892902, Sep. 1998.

[6] F. Z. Peng, F. Zhang, and Z. Qian, A magnetic-less DC-DC converter for

dual-voltage automotive systems, IEEE Trans. Ind. Appl., vol. 39, no. 2,

pp. 511518, Mar./Apr. 2003.

[7] W. Qian, F. Z. Peng, and L. M. Tolbert, Development of a 55 kW 3X

DC-DC converter for HEV systems, in Proc. Veh. Power Propulsion

Conf., 2009, pp. 433439.

[8] F. H. Khan and L. M. Tolbert, A multilevel modular capacitor-clamped

DC-DC converter, IEEE Trans. Ind. Appl., vol. 43, no. 6, pp. 16281638,

Nov./Dec. 2007.

[9] K. K. Law, K. W. E. Cheng, and Y. P. B. Yeung, Design and analysis

of switched-capacitor-based step-up resonant converters, IEEE Trans.

Circuits Syst. I, Reg. Papers, vol. 52, no. 5, pp. 943948, May 2005.

[10] M. Shoyama, F. Deriha, and T. Ninomiya, Operation analysis and control

of resonant boost switched capacitor converter with high efciency, in

Proc. Power Electron. Spec. Conf., 2005, pp. 19661971.

[11] J. Kimball, P. Krein, and K. Cahill, Modeling of capacitor impedance in

switching converters, IEEE Power Electron. Lett., vol. 3, no. 4, pp. 136

140, Dec. 2005.

ZOU et al.: SWITCHED-CAPACITOR-CELL-BASED VOLTAGE MULTIPLIERS AND DCAC INVERTERS 1609

[12] D. Cao and F. Z. Peng, A family of zero current switching switched-

capacitor DC-DC converters, in Proc. 25th Annu. IEEE APEC,

Feb. 2125, 2010, pp. 13651372.

[13] D. Cao and F. Z. Peng, Zero-current-switching multilevel modular

switched-capacitor DC-DC converter, IEEE Trans. Ind. Appl., vol. 46,

no. 6, pp. 25362544, Nov./Dec. 2010.

[14] D. Cao and F. Z. Peng, Multiphase multilevel modular DC-DC converter

for high current high gain TEG application, in Proc. IEEE Energy Con-

vers. Congr. Expo., Atlanta, GA, 2010, pp. 42304237.

[15] J. I. Rodriguez and S. B. Leeb, A multilevel inverter topology for in-

ductively coupled power transfer, IEEE Trans. Power Electron., vol. 21,

no. 6, pp. 16071617, Nov. 2006.

[16] F. Zhang, S. Yang, F. Z. Peng, and Z. Qian, A zigzag cascaded multilevel

inverter topology with self voltage balancing, in Proc. IEEE APEC, Feb.

2008, pp. 16321635.

[17] O. Mak and A. Ioinovici, Switched-capacitor inverter with high power

density and enhanced regulation capability, IEEE Trans. Circuits Syst. I,

Fundam. Theory Appl., vol. 45, no. 4, pp. 336348, Jun. 1998.

[18] Y. Chang, Design and analysis of multistage multiphase switched-

capacitor boost DC-AC inverter, IEEE Trans. Circuits Syst. I, Reg.

Papers, vol. 58, no. 1, pp. 205218, Jan. 2011.

[19] IEEE Recommended Practice and Requirements for Harmonic Control in

Electric Power Systems, IEEE Std. 519-1992.

Ke Zou (S09) received the B.S. and M.S. degrees

from Xian Jiaotong University, Xian, China, in

2005 and 2008, respectively. He is currently working

toward the Ph.D. degree at The Ohio State Univer-

sity, Columbus.

His current research interests include switched-

capacitor dc/dc converters and dc/ac multilevel

inverters, battery models in high-frequency applica-

tions, and hardware-in-the-loop systems for power

electronics and power systems.

Mark J. Scott (S09) received the B.S. degree in

electrical and computer engineering from The Ohio

State University, Columbus, in 2005. He is currently

working toward the Ph.D. degree in electrical and

computer engineering at The Ohio State University.

He has worked as a Field Engineer installing

large industrial automated systems and as a Test

Engineer validating power electronics for automo-

tive applications. His research interests include uti-

lizing wide-band-gap devices in new and existing

power electronic topologies for renewable energy

applications.

Mr. Scott is the founding member of the IEEE Graduate Student Body at The

Ohio State University and a member of Tau Beta Pi.

Jin Wang (S02M05) received the B.S. degree

from Xian Jiaotong University, Xian, China, in

1998, the M.S. degree from Wuhan University,

Wuhan, China, in 2001, and the Ph.D. degree from

Michigan State University, East Lansing, MI, in

2005, all in electrical engineering.

From September 2005 to August 2007, he worked

at the Ford Motor Company as a Core Power Elec-

tronics Engineer and contributed to the traction drive

design of the Ford Fusion Hybrid. Since September

2007, he has been an Assistant Professor in the De-

partment of Electrical and Computer Engineering, The Ohio State University,

Columbus. His teaching position is cosponsored by American Electric Power,

Duke/Synergy, and FirstEnergy. He is the author of 40 peer-reviewed journal

and conference publications. His research interests include high-voltage and

high-power converter/inverters, integration of renewable energy sources, and

electrication of transportation.

Dr. Wang was the recipient of the IEEE Power Electronics Society Richard

M. Bass Young Engineer Award and the National Science Foundations

CAREER Award, both in 2011. Since March 2008, he has been an Associate

Editor for the IEEE TRANSACTIONS ON INDUSTRY APPLICATION.

You might also like

- Bluedart Express LTD - Tracking Details PDFDocument1 pageBluedart Express LTD - Tracking Details PDFvinay kumarNo ratings yet

- Nikon AssignmentDocument4 pagesNikon Assignmentfarah arshad100% (1)

- A Nonisolated Three-Port DC-DC Converter and Three-Domain Control Method For PV-Battery Power SystemsDocument11 pagesA Nonisolated Three-Port DC-DC Converter and Three-Domain Control Method For PV-Battery Power SystemsChristian EmenikeNo ratings yet

- 72-A Switched-Capacitor Three-Phase ACAC ConverterDocument11 pages72-A Switched-Capacitor Three-Phase ACAC ConverterJoão GimenesNo ratings yet

- AM28 A Single-Phase Photovoltaic Inverter Topology With A Series-Connected Energy BufferDocument9 pagesAM28 A Single-Phase Photovoltaic Inverter Topology With A Series-Connected Energy BufferReddy KvmNo ratings yet

- A Self-Balanced Step-Up Multilevel Inverter Based On Switched-Capacitor StructureDocument11 pagesA Self-Balanced Step-Up Multilevel Inverter Based On Switched-Capacitor StructurePrasanna Kumar EssampallyNo ratings yet

- Cascade Cockcroft-Walton Voltage MultiplierDocument15 pagesCascade Cockcroft-Walton Voltage MultiplierAnkush MukherjeeNo ratings yet

- Energies 08 09969Document23 pagesEnergies 08 09969Anonymous BoRFocNo ratings yet

- A Low Cost Flyback CCM Inverter For AC Module ApplicationDocument9 pagesA Low Cost Flyback CCM Inverter For AC Module Applicationvinay kumarNo ratings yet

- A Multilevel Converter With A Floating Bridge For Open-End Winding Motor Drive ApplicationsDocument10 pagesA Multilevel Converter With A Floating Bridge For Open-End Winding Motor Drive ApplicationsAbd DawaraNo ratings yet

- MVDC Voltage MultiplierDocument6 pagesMVDC Voltage Multiplierahmedallehyani5aNo ratings yet

- A Hybrid Ac-Dc Microgrid and Its ControlDocument9 pagesA Hybrid Ac-Dc Microgrid and Its ControlTouseef HussainNo ratings yet

- 14 IET Power Electronics - 2018 - SaeedianDocument12 pages14 IET Power Electronics - 2018 - SaeedianRanesh SubramaniNo ratings yet

- Charge Pump Design HVDocument16 pagesCharge Pump Design HVMohammed BelkheiriNo ratings yet

- Multi LVL DC DC BoostDocument9 pagesMulti LVL DC DC BoostDurga PrathibhaNo ratings yet

- DC-DC High-Voltage-Gain Converters With Low Count of Switches and Common GroundDocument22 pagesDC-DC High-Voltage-Gain Converters With Low Count of Switches and Common GroundSzymon FNo ratings yet

- A High Gain Multiport DC-DC Converter For Integrating Energy Storage Devices To DC MicrogridDocument12 pagesA High Gain Multiport DC-DC Converter For Integrating Energy Storage Devices To DC Microgridafroz mohdNo ratings yet

- SiC-MOSFET and Si-IGBT-Based DC-DC Interleaved ConDocument21 pagesSiC-MOSFET and Si-IGBT-Based DC-DC Interleaved Conprabhu rachutiNo ratings yet

- Soft Switched High Step-Up DC-DC Converter For Automotive ApplicationDocument4 pagesSoft Switched High Step-Up DC-DC Converter For Automotive Applicationkarthi.r.tNo ratings yet

- (SiC-En-2013-24) A High-Power-Density DC-DC Converter For Distributed PV ArchitecturesDocument8 pages(SiC-En-2013-24) A High-Power-Density DC-DC Converter For Distributed PV Architecturesnuaa_qhhNo ratings yet

- Asymmetrical Duty Cycle Control and Decoupled Power Flow Design of A Three-Port Bidirectional DC-DC Converter For Fuel Cell Vehicle ApplicationDocument14 pagesAsymmetrical Duty Cycle Control and Decoupled Power Flow Design of A Three-Port Bidirectional DC-DC Converter For Fuel Cell Vehicle ApplicationDaniel Oscar GarridoNo ratings yet

- Bbifbi Standalone Iet PeDocument10 pagesBbifbi Standalone Iet PeJeremy MeyerNo ratings yet

- The Application of The Cascaded Multilevel Photovoltaic: Converters in Grid Connected SystemsDocument6 pagesThe Application of The Cascaded Multilevel Photovoltaic: Converters in Grid Connected Systemssandeepbabu28No ratings yet

- 1 Megawatt, 20 KHZ, Isolated, Bidirectional 12Kv To 1.2Kv DC-DC Converter For Renewable Energy ApplicationsDocument8 pages1 Megawatt, 20 KHZ, Isolated, Bidirectional 12Kv To 1.2Kv DC-DC Converter For Renewable Energy ApplicationsJonxa BalenziagaNo ratings yet

- 2021 Chilecon Pinv15-584Document5 pages2021 Chilecon Pinv15-584EdgarNo ratings yet

- Research On A Cascaded Multilevel Inverter by Employing Three-Phase TransformersDocument10 pagesResearch On A Cascaded Multilevel Inverter by Employing Three-Phase TransformersManikanta SwamyNo ratings yet

- Three-Port Bidirectional Converter For Hybrid Fuel Cell SystemsDocument8 pagesThree-Port Bidirectional Converter For Hybrid Fuel Cell SystemsDaniel Oscar GarridoNo ratings yet

- A Tripole HVDC System Based On Modular Multilevel ConvertersDocument9 pagesA Tripole HVDC System Based On Modular Multilevel ConvertersvsasaankNo ratings yet

- Using Self-Driven AC-DC Synchronous Rectifier As A Direct Replacement For Traditional Power Diode RectifierDocument10 pagesUsing Self-Driven AC-DC Synchronous Rectifier As A Direct Replacement For Traditional Power Diode RectifierdabalejoNo ratings yet

- CH-43 Electric TractionDocument75 pagesCH-43 Electric TractionPunitNo ratings yet

- Bipolar AC-ACDocument15 pagesBipolar AC-ACBui DaiNo ratings yet

- Lawler Trans Pe Jan 2004 PDFDocument12 pagesLawler Trans Pe Jan 2004 PDFAshok KumarNo ratings yet

- Paper SaraDocument9 pagesPaper SaraSara ElbadaouiNo ratings yet

- New Multilevel Inverter Topology With Reduced Number of SwitchesDocument6 pagesNew Multilevel Inverter Topology With Reduced Number of SwitchesVikram PrasadNo ratings yet

- Control of Three-Phase Inverter For AC Motor Drive With Small DC-Link Capacitor Fed by Single-Phase AC SourceDocument8 pagesControl of Three-Phase Inverter For AC Motor Drive With Small DC-Link Capacitor Fed by Single-Phase AC SourceAnand KumarNo ratings yet

- Electronics 07 00062Document19 pagesElectronics 07 00062sanafayaz12No ratings yet

- Three Port DC-DC Converter For Storage Integration in MicrogridDocument6 pagesThree Port DC-DC Converter For Storage Integration in Microgridafroz mohdNo ratings yet

- A New Single-Phase Single-Stage Three-LevelDocument12 pagesA New Single-Phase Single-Stage Three-LevelGururaj BandaNo ratings yet

- Super High Gain DC DC Converter EpiphanyDocument31 pagesSuper High Gain DC DC Converter EpiphanyForbeniusNo ratings yet

- Batch 10Document68 pagesBatch 10Pidikiti Surendra BabuNo ratings yet

- New Efficient Submodule For A Modular Multilevel Converter in Multiterminal HVDC NetworksDocument21 pagesNew Efficient Submodule For A Modular Multilevel Converter in Multiterminal HVDC NetworksSudip MondalNo ratings yet

- Soft Switching Buck Converter For Battery Charging With MPPTDocument7 pagesSoft Switching Buck Converter For Battery Charging With MPPTVenkanna BodigeNo ratings yet

- Survey of CascadeDocument10 pagesSurvey of Cascadesumiths32No ratings yet

- Analysis, Modelling and Simulation of A Multiphase Interleaved Buck DC/DC Converter For PV ApplicationsDocument7 pagesAnalysis, Modelling and Simulation of A Multiphase Interleaved Buck DC/DC Converter For PV ApplicationsInnovative Research PublicationsNo ratings yet

- Multiport DC-DC Converters For Renewable Energy: An Overview With ContributionsDocument22 pagesMultiport DC-DC Converters For Renewable Energy: An Overview With ContributionsRa muNo ratings yet

- Transformer-Less Converter ConceptDocument8 pagesTransformer-Less Converter ConceptC_hakan_CNo ratings yet

- Two-Stage Micro-Grid Inverter With High PDFDocument10 pagesTwo-Stage Micro-Grid Inverter With High PDFacostaricciNo ratings yet

- An Electromagnetic Transient Simulation Model ForDocument4 pagesAn Electromagnetic Transient Simulation Model ForMohit Kumar ChowdaryNo ratings yet

- DC DC ConvertorDocument11 pagesDC DC ConvertorJyothiNo ratings yet

- Presentation Paper On DGDocument5 pagesPresentation Paper On DGAlok Bikash SadangiNo ratings yet

- 5 Jpe 09101 PDFDocument7 pages5 Jpe 09101 PDFIfan Seven SeasNo ratings yet

- A New Topology For Multilevel Current Source ConvertersDocument11 pagesA New Topology For Multilevel Current Source Converterskrishnareddy_ch3130No ratings yet

- Control of Energy Storage Interface With Abidirectional Converter For Photovoltaic SystemsDocument6 pagesControl of Energy Storage Interface With Abidirectional Converter For Photovoltaic SystemsLanstein Joe E PNo ratings yet

- Improved and Hybrid PVDocument6 pagesImproved and Hybrid PVMariGaneshNo ratings yet

- Multiphase Bidirectional Flyback Converter PDFDocument7 pagesMultiphase Bidirectional Flyback Converter PDFArceu CamposNo ratings yet

- Design and Analysis of Pulse-WidthDocument13 pagesDesign and Analysis of Pulse-WidthVisu TamilNo ratings yet

- High-Efficiency Bidirectional DC - DC Converter With High-Voltage GainDocument12 pagesHigh-Efficiency Bidirectional DC - DC Converter With High-Voltage GainghiocelNo ratings yet

- A New Single-Phase Single-Stage Three-Level Power Factor Correction AC-DC ConverterDocument12 pagesA New Single-Phase Single-Stage Three-Level Power Factor Correction AC-DC Convertersurya_v988No ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Methods for Increasing the Quality and Reliability of Power System Using FACTS DevicesFrom EverandMethods for Increasing the Quality and Reliability of Power System Using FACTS DevicesNo ratings yet

- Power Electronics and Energy Conversion Systems, Fundamentals and Hard-switching ConvertersFrom EverandPower Electronics and Energy Conversion Systems, Fundamentals and Hard-switching ConvertersNo ratings yet

- VSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsFrom EverandVSC-FACTS-HVDC: Analysis, Modelling and Simulation in Power GridsNo ratings yet

- Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid ConnectionDocument7 pagesSingle-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connectionvinay kumarNo ratings yet

- Uu (Oi (PioDocument1 pageUu (Oi (Piovinay kumarNo ratings yet

- TCSC and SSRDocument6 pagesTCSC and SSRTiger FlyNo ratings yet

- 106Document6 pages106vinay kumarNo ratings yet

- Grid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTDocument6 pagesGrid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTvinay kumarNo ratings yet

- 87Document5 pages87vinay kumarNo ratings yet

- Design and Simulation of Single Phase Z-Source Buck Boost Matrix ConverterDocument7 pagesDesign and Simulation of Single Phase Z-Source Buck Boost Matrix Convertervinay kumarNo ratings yet

- Indirect Control For Cascaded H-Bridge Rectifiers With Unequal LoadsDocument6 pagesIndirect Control For Cascaded H-Bridge Rectifiers With Unequal Loadsvinay kumarNo ratings yet

- DC Motor Speed Control For Electric Locomotive Equipped by Multi-Level DC-DC ConverterDocument7 pagesDC Motor Speed Control For Electric Locomotive Equipped by Multi-Level DC-DC Convertervinay kumarNo ratings yet

- New Method To Achieve AC Harmonic Elimination and Energy Storage Integration For 12-Pulse Diode RectifiersDocument8 pagesNew Method To Achieve AC Harmonic Elimination and Energy Storage Integration For 12-Pulse Diode Rectifiersvinay kumarNo ratings yet

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDocument6 pagesSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNo ratings yet

- Pioneer pdp-r06g r06c Media Receiver SMDocument90 pagesPioneer pdp-r06g r06c Media Receiver SMCarlos GuerconNo ratings yet

- Boq Sialkot Pak Army Panel B 1Document18 pagesBoq Sialkot Pak Army Panel B 1naqvikhizerNo ratings yet

- Product Catalogue 2009: Welding and Cutting EquipmentDocument52 pagesProduct Catalogue 2009: Welding and Cutting EquipmentMohit TyagiNo ratings yet

- Busbar Protection Intro - Sales Training May 08Document23 pagesBusbar Protection Intro - Sales Training May 08yuva rajNo ratings yet

- FR7xx2 BrochureDocument4 pagesFR7xx2 BrochuredotatchuongNo ratings yet

- CECL08D Datasheet Mp3-PlayerDocument1 pageCECL08D Datasheet Mp3-PlayerGlauber CostaNo ratings yet

- Software Quality Assurance (SQA) PlanDocument11 pagesSoftware Quality Assurance (SQA) PlanMuhammad OsamaNo ratings yet

- SM3GZ47, SM3JZ47: Ac Power Control ApplicationsDocument5 pagesSM3GZ47, SM3JZ47: Ac Power Control ApplicationsSergio BarbozaNo ratings yet

- 2537 VD4G-50 Vacuum Circuit-Breaker GBDocument4 pages2537 VD4G-50 Vacuum Circuit-Breaker GBburvanov0% (1)

- What Is A Lecher AntennaDocument4 pagesWhat Is A Lecher AntennaPt AkaashNo ratings yet

- Wireless PowerDocument31 pagesWireless Poweral_1989No ratings yet

- Prack Pr300: User ManualDocument98 pagesPrack Pr300: User ManualBầu Trời TrongNo ratings yet

- QR CodesDocument18 pagesQR CodesLavlesh JaiswalNo ratings yet

- CL-5000 Series Service and Calibration - TocDocument5 pagesCL-5000 Series Service and Calibration - TocTestNo ratings yet

- 10 Rules For ADHD Proof ProductivityDocument1 page10 Rules For ADHD Proof ProductivityKristeen Funk100% (1)

- 3M QS 2000E: Medium Voltage JointDocument3 pages3M QS 2000E: Medium Voltage Jointdavid mauricioNo ratings yet

- PLC ProgramDocument5 pagesPLC ProgramMOUSIN PASHANo ratings yet

- NetatmoDocument48 pagesNetatmoJuli SánchezNo ratings yet

- Microchannel Heat Exchanger: Prepared byDocument18 pagesMicrochannel Heat Exchanger: Prepared byPritam GoleNo ratings yet

- E.G. Per Set/group of StudentDocument4 pagesE.G. Per Set/group of StudentKiritoNo ratings yet

- Buck Converter Basics & Selection of ComponentsDocument22 pagesBuck Converter Basics & Selection of ComponentsSateesh TalisettyNo ratings yet

- D77005 enDocument46 pagesD77005 enzliangNo ratings yet

- Schumacher Xc103 ChargerDocument29 pagesSchumacher Xc103 ChargerKimberly Zahn ThibodeauxNo ratings yet

- TEC3000 Series On/Off or Floating Fan Coil and Individual Zone Thermostat Controllers With Dehumidification CapabilityDocument48 pagesTEC3000 Series On/Off or Floating Fan Coil and Individual Zone Thermostat Controllers With Dehumidification CapabilityIvar Denicia DelgadilloNo ratings yet

- UM-2D User ManualDocument31 pagesUM-2D User Manualwahyu wibowoNo ratings yet

- Samsung Ps43e450a1w Ps51e450a1wDocument49 pagesSamsung Ps43e450a1w Ps51e450a1wdann222No ratings yet

- 6 5 Cylin Atten - Prigusivac BukeDocument12 pages6 5 Cylin Atten - Prigusivac BukezigicsasaNo ratings yet

- RD7000 Brochure V2 en PDFDocument12 pagesRD7000 Brochure V2 en PDFbogdy00733054No ratings yet

- 2SC2073 PDFDocument3 pages2SC2073 PDFVenu Gopal Rao AggressNo ratings yet