Professional Documents

Culture Documents

91

91

Uploaded by

vinay kumar0 ratings0% found this document useful (0 votes)

33 views7 pagesCopyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

0 ratings0% found this document useful (0 votes)

33 views7 pages91

91

Uploaded by

vinay kumarCopyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PDF, TXT or read online from Scribd

Download as pdf or txt

You are on page 1of 7

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

Bipolar Tapezoidal Amalagated Rectangular Reference function for

improved performance PWM Multilevel Inverter

Bensraj R.

Assistant Professor, Depament of Electrical Engineering, Anamalai University

Annamalainaga, Chidmbaa, Tamilnadu, India

bensraL au@redifail.com

Natarajan S.P.

Professor and Head, Deparment of Instruentation Engineering, Anamalai Univesity,

Annamalainaga, Chidmbaam, Tamlnadu, India

spn _ annmalai@redifail.com

Shanthi B.

Associate Professor, Centalised Instrumentation and Service Laboratory, Annamalai Unversity,

Emil: au_shan@yahoo.com

Abstact: In many research papers modulation techniques have

been carried out with dif erent technique but this paper reveals

a new idea to enhance the perorance of MultiLevel Inverter

(MU. I trapezoidal a a reference in that case 3rd haronics

prouces signicant spectrum haronic energ, the impact of

that the difcult arises for flter design. An amalgamated

rectanglar references is developed to improve the perorances

of a fve level Cacaded MultiLevel Inverer (CMU. To validate

the improvement a MATLAB-SIMLK based simulation to

biploar amalgamated rectangular reference function is simulated

for ca"ier diposition techiques Phase Shi techique , Carier

Overlapping technique and Variable Frequenc techniques are

carried out. FF analysi and perormance of evaluation hae

been carried out. T simulaton results validating the strateges

presented. Among the all stategie developed ca"ier

overlapping technique provides relatively higher DC bu

utiliaton and PS provides the lowest distortion for moderate mao

Ke words: CMU PW Total Haronic Distorion, PD , POD ,

APOD, PS, CO, VF

1. Introduction

A multilevel converter (DC-AC) is an

emerging area to power electronc system that

synthesizes a desired outut voltage fom several

levels of DC voltages as inputs. With an

increasing number of DC voltage sources, the

converter outut voltage waveform approaches a

nearly sinusoidal waveform while using a

fndamental fequency-switching scheme.

Compared with the traditional two-level voltage

converter, the primary advantage of multilevel

converters is their smaller outut voltage step,

which results in high power quality, lower

harmonic components, better electomagetic

compatibility and lower switching losses. The

pricipal motivation for multilevel topologies is

the increase of power, the reduction of voltage

stress on the switches, and the generation of high

quality outut voltages and sinusoidal currents.

CMUs use more tha one DC voltage source to

generate an AC outut voltage. Shanthi and

Nataajan made a detailed comparative study of

various unipolar multicarier PWM strategies for

single phase cascaded MU throug simulation

usig MATLAB-SIMVLI and dSPACEIRTI

based implementation [1]. They also simulated

and implemented carrier overlapping bipolar

PWM techiques for chosen single phase

cascaded fve level inverter in [2]. Ayob and

Salam proposed a modulation technique for the

cascaded multilevel inverter in [3].

Generalization of the pulsewidth modulation

subharmonic method to contol single phase or

thee phase multilevel voltage source inverters is

considered in [4]. A modifed carrier aproach

that closely approxates the performance of

hamonic elimination is introduced by Krein et

al [5]. Hamonic elimination, taditionally digital,

is to be achievable by comparison of a sine wave

with modifed triangle carrier proposed in [6]. A

fve level multilevel selective harmonic

elimination PWM strategy based on a equal

number of switching transitions when compaed

against the previously mentioned technique is

proposed by Agelidis et al [7]. A generalized

formulation for selective harmonic elimination

pulse-width modulation control suitable for high

978-1-4673-0210-4112/$31.00 2012 IEEE 325

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

voltage high power cascaded multilevel voltage

source converters with both equal ad nonequal

DC sources used in constant fequency utility

applications in [8]. A new approach to medium

voltage vaiable-fequency static AC motor

drives ofers iprovements in power quality in

[9]. A improved performance of PWM strategy

for controlling the harmonics of outut voltage

of chosen CMU employing Trapezoidal

Amalagated Rectanglar Reference fnction.

MATLAB based simulations are performed

using power sytem block set. Lower order

harmonic and its side bands haonic energy are

sigifcant less for chosen CMU.

2. Multilevel Inverter

The elementary concept of a multilevel

converter to achieve higher power is to use a

series of power semiconductor switches with

several lower voltage DC sources to perform the

power conversion by synthesizing a staircase

voltage waveform. Figure I shows the single

phase fve level cascaded inverter. The cascaded

inverter is an unique when compared to other

tyes of multilevel inverters in the sense that it

consists of several modules that require separate

DC sources.

The gate signals for chosen fve level

cascaded inverter are simulated using

MA TLAB-SIMUI. Figure 2 shows a

sample SIMUI model developed for APOD

technique. The simulation results are presented

ad evaluated.

3. Bipolar Modulation Strategies for CMLI

A number of modulation strategies are

used in multilevel power conversion

applications. Carrier based PW methods ad

space vector methods are ofen used but when

Fig.I. A single phase cascaded inverter

the number of outut levels is more than fve, the

space vector method will be very complicated

with the increase of switching states. So the

carier based PWM method is preferred in MUs

and hence this work focuses on car ier based

PWM techniques. Multicarrier PWM strategies

ca be categorized into the following goups:

(i) carrier disposition techiques where the

reference signal is sampled through a number of

carier signals displaced by increments of the

reference amplitde (ii) phase shif PWM

technique where multiple carriers ae phase

shifed accordingly (iii) combination of carrier

disposition and phase shif technique. This

paper focuses on bipolar Trapezoidal

Amalagated Rectangular (TAR) modulation

strategies which have been used in CMU.

R:t

Fig.2. Sample PWM generation logic using

SIMULIN model developed for APOD

technique

326

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

4. Carrier Disposition Techniques

The following sections briefy describe

the carrier disposition PWM techiques. This

paper presents four tyes of bipolar PWM

strategies. The reference is Trapezoidal

Amalagated Rectangular Reference fnction.

The reference waveform has amplitude Am and

fequency fm and it is centred about the zero

level.

4.1. Phase disposition technique

I phase disposition all the cariers are in

phase. Figure 3 shows the multicarrier

arrangement for phase disposition technique for

ma=0.8.

Fig. 3. Multicarrier arragement for PDPWM

technique

4.2. Phase opposition disposition technique

With the POD technique the carrier

waveforms above the zero reference value are in

phase. Figure 4 shows the multicarrier

arrangement for POD technique.

Fig. 4. Multicarrier aragement for PODPW

technique

4.3. Alternate phase opposition disposition

Technique

Ths techique requires each of the four carier

waves for a fve level inverter to be phase

displaced fom each other by 180 degrees

alernately. Figure 5 shows the multi car ier

arrangement for APOD techique.

Fig. 5. Multicarier arrangement for

APODPWM technique

5. Phase Shif Technique

The phase shif multicarrier PWM techique

uses four carrier signals of the same amplitude

and fequency which are shifed by 90 degrees to

one another to generate the fve level inverter

outut voltage. The gate signals for the cascaded

inverter can be derived directly fom the PWM

signals (comparison of the carrier with the

trapezoidal reference). There is a certain degee

of feedom in the allocation of the carriers to the

inverter switches. Figure 6 shows the

multicarrier arragement for PS technique.

327

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

Fig. 6. Multicarrier arragement for PSPW

technique

6. Carrier Overlapping PWM Technique

The COPWM technique utilizes the CFD of

vertical ofsets among cariers. The principle of

COPWM is to use several overlapping carriers

with single modulating signal. For an m-Ievel

inverter, m-l cariers with the same fequency fc

ad same peak-to-peak amplitude Ac are

disposed such that the bands they occupy

overlap each other. The overlapping vertical

distance between each carrier is Ac/2 in this

work. The reference wave has the amplitude Am

ad fequency fm and it is centered in the middle

of the carier signals. The amplitude modulation

index m =

A

m

. The vertical ofset of

(: )

A

c

carriers for chosen fve level inverter can be as

illustrated i Figure 6. It can be seen that the

four carriers are overlapped with other ad the

Trapezoidal Amalagated Rectangular Reference

fnction is placed at the middle of the four

carriers. Figure 7 shows the multicarrier

arrangement for COPWM technique.

Fig. 7. Multicarrier arrangement for COPWM

technique

7. Variable Frequency (F) PWM Technique

The number of switchings for upper and

lower devices of chosen MU is much more than

that of intermediate switches in SHPWM using

constant fequency carriers. In order to equalize

the number of switchings for all the switches,

Fig. 8. Multicarrier aragement for VFPWM

technique

vaiable fequency PWM strategy is used as

illustrated in Figure 8 i which the carier

fequency of the intermediate switches is

properly increased to balace the numbers of

switching for all the switches. Figure 8 shows

the multicarrier aragement for VFPWM

technique (lower ad upper switches).

8. Simulation Results

The cascaded fve level inverter is modelled by

MATLAB-SIMUINK. Switching signals for

CMU are developed using bipolar modulation

techniques discussed prevously. Simulations are

performed for different values of ra raging

fom 0.6 - 1. The coresponding % THD values

ae measured using the FFT block and they are

328

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

shown in Table 1. Next table displays the Vrms of

fndamental of inverter outut for same

modulation indices. Tables 3- 5 display

respectively the correspondig CF, DF and FF.

Figres 9-20 show the simulated outut voltage

of CMU ad corresponding FFT plots with

above strategies but for only one sample value of

ra = 0.8. Figure 15 shows the fve level outut

voltage generated by PS strategy and its FFT

plot is shown in Figure 16. From Figre 15, PS

strategy has signifcant amount of harmonic

energy present in 3

r

d

and 7

th

harmonics. Figure

13 shows the fve level outut of APOD strategy

where signifcant energy is present in the 3

rd

harmonic. Figure 11 displays the fve level

outut volage generated by POD strategy and its

FFT plot is shown in Figure 12. The FFT

spectrum of POD strategy shows signifcant 3

r

d

,

ad 7

th

haonic energy content in the inverter

outut. Figure 9 shows the fve level outut

voltage generated by PD strategy and its FFT

plot is shown in Figure 10. PD strategy produces

signifcant 3r

d

and 7th harmonic energy. The

following parameter values are used for

simulation: Voc =100V ad R(load) = 100 ohms.

Fig.9. Otut voltage generated by PD

technique

urcaeuta|0z,= 177.2 'u~3964

3J

25

!5

!u

Fig. 10. FFT plot for outut voltage of PD

technique

329

Fig.11 Outut voltage generated by POD

technique

adamcn:a|0|z)!73.7 . 1302

||mcn|ccce

Fig. 12. FFT plot for output voltage of POD

technique

Fig.13 Outut voltage generated by APOD

technique

uuoancutu| 3 I745 'L3950%

:

Fig. 14. FFT plot for outut voltage of APOD

technique

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

Fig.15 Outut voltage generated by PS

technique

undrrn|ol5Oz) IE 0JO.79%

IE

I4

Fig. 16. FFT plot for outut voltage of PS

technique

Fig.17 Outut voltage generated by CO

technique

|uaoamer:a|(30z)= !6 'L=3924%

JJ

Fig. 18. FFT plot for outut voltage of CO

technique

2

Fig.19 Outut volage generated

by V technique

Fundiment . 1 3z= 178.3, THO= 38.19"

Fig.20 FFT plot for outut voltage of VF

Technique

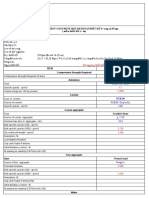

Table 1 % THD for different modulation

indices

Mg PD POD APOD PS CO

1 22.18 22.03 22.33 22.02 28.14

0.9 30.01 30.73 32.32 31.34 33.57

0.8 39.64 37.02 39.80 38.79 39.24

0.7 43.49 40.33 44 43.02 44.07

0.6 43.95 40.50 45.13 42.79 47.90

VF

21.41

30.88

38.19

42.33

42.29

Table 2 VRS for different modulation indices

Mg PD POD APOD PS CO VF

1 157.0 156.9 157.0 156.9 160.1 157.1

0.9 141.1 140.9 140.3 142.5 149.7 141.6

0.8 125.3 125.0 123.5 128.1 139.0 126.1

0.7 109.5 109.0 106.8 112.1 128.5 109.9

0.6 93.8 94.47 91.56 96.8 117.5 94.14

9. Conclusion

It is observed fom Table 1 that PD technique

provides outut with the THD. Among the all

strategies developed, CO provides DC bus

utilization (Table 2). 3

rd

ad

7th

order harmonics

ae reduced in APOD techniques (Table 3).

330

2012 Interational Conference on Computing, Electronics and Electrical Technologies [ICCEET]

References

1. l.B.Shanthi and S.P.Nataajan 'Compaative study on

vaious unipolar PWM stategies for sinle phase fve

level cascaded inverter', Interational Joural of

Power Electonics (IJPELEC), Special issue on: Powe

Converters: Modelin, Siuation Aalyis,

Topologies, secondar issues a applications, Inder

Science Pubilication Switzerlan, 2009.

2. B.Shanhi a S.P.Nataajan, 'Carier overlapping

PWM technques for sinle phase cascaded fve level

inverter', International Joural of Science and

Technique of Automatic contol & comuter

engineering (IJ-STA, Tunisia), Special issue on Conrol

of Electrical Mahines, pp. 590-601, December 2008.

3. Ayob, S.M. and Salam, Z, 'A new PWM scheme for

cascaded multilevel inverter using multiple trapezoidal

moduation signls', Research report of Universit

Teknolog, Malaysia, pp.242-246, 2004.

4. Carara,G, Gadella, S., Marchesoni, M., Salutari, R.

and Sciutto,G, 'A new multilevel PWM techique: a

theoretical analysis', IEEE Trans.Power Electon.vo!.7,

pp. 497-505, 1992.

5. P. T Krei B. M. Nee, and J. R. Wells, 'Hamonic

eliination switchin through modulation', in

Poc . IEEE Workhop Comut.Power Electron. 2004,

pp. 123-126.

6. R. Wells, X. Gen, P. L. Chapman, P. T. Krein and B.

M. Nee, 'Modulation-based haronic elimntion',

IEEE Tran. Power Electon.,vol. 22, no. 1, pp. 336-

340, Jan. 2007.

7. V G Agelidis, A. Baloutsis, I. Baloutsis, and C.

Cossar, 'Five-level selective hamonic

eliination PWM stategies and muticarrier

phaseshifed sinusoidal PWM: A compaison', in Proc.

IEEE Power Electon.Specialit Conf, Recife,

Brazil, Jun. 2005, pp. 1685-1691.

8. M. S. A. Dahidah and V G Agelidis, ' Selective

harmonic elimination PWM control for cascaded

multilevel voltage souce converters: A generalized

formula', IEEE Tan. Power Electon., vol. 23, no. 4,

pp. 1620- 1630, Jul. 2008.

9. J. Rodrigez, J. Lai, and F Pen, 'Multilevel

inverters:Asuvey of topologies, controls and

application', IEEE Trans. Ind. Electon., vol. 49, no.

4,pp. 724-738, Aug. 2002.

331

APPENDIX % of Hamonic magnitudes for

several condition of even mf and its side bands

(I=O.8)

Harmonic Harmonic ampltude with TAR rference

order

APO PS CO

PD POD V

D

3 order 3.90 2.80 l.l8 6.55 6.08 4.47

5 order 11.54 11.6 11.2 11.7 9.75 11.64

7 order 4.45 3.54 l.l9 7.64 4.11 5.15

II order 4.76 4.34 1.43 8.03 4.08 4.95

13 order 0.72 2.34 4.56 3.05 0.36 0.03

m=22 30.52 0.07 0.13 0.12 30.56 20.37

(ll) 21 2.49 19.1 11.8 16.2 1.98 2.68

(ml) 23 0.63 20.3 12.8 13.5 0.09 0.34

(l2) 20 3.49 0.05 0.25 0.12 5.79 10.56

(m2) 24 2.78 0.06 0.14 0.12 5.52 10.48

(2mr) 44 0.21 0.08 0.13 0.06 0.46 9.40

(2ll) 43 5.68 5.60 6.93 4.74 7.93 5.67

(2ml) 45 7.10 6.77 7.92 6.21 9.52 6.64

(2l2) 42 0.56 0.03 0.10 0.07 0.08 7.01

(2m2) 46 0.40 0.02 0.07 0.13 0.12 6.92

(3mr ) 66 3.78 0.03 0.19 0.12 6.39 4.02

(3ll) 65 0.26 3.30 3.02 3.31 1.01 1.04

(3ml) 67 0.66 4.60 4.71 3.09 0.08 1.40

(3l2) 64 2.33 0.08 0.09 0.17 0.88 1.31

(3m2) 68 2.76 0.08 0.09 0.09 1.34 2.84

(4m) 88 0.34 0.05 0.31 0.08 0.46 0.72

(4ll) 87 5.0 6.32 4.50 5.52 0.61 4.64

(4ml) 89 4.95 4.00 6.26 3.59 1.43 4.39

(4l2) 86 l.l1 0.07 0.07 0.12 0.31 0.11

(4m2) 90 0.15 0.07 0.06 0.06 0.45 0.23

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5822)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- CIS016 2 Assignment One 2016 17Document7 pagesCIS016 2 Assignment One 2016 17ProiectulTauNo ratings yet

- Bluedart Express LTD - Tracking Details PDFDocument1 pageBluedart Express LTD - Tracking Details PDFvinay kumarNo ratings yet

- ACUHDocument13 pagesACUHrajarethinammNo ratings yet

- Uu (Oi (PioDocument1 pageUu (Oi (Piovinay kumarNo ratings yet

- TCSC and SSRDocument6 pagesTCSC and SSRTiger FlyNo ratings yet

- 106Document6 pages106vinay kumarNo ratings yet

- Grid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTDocument6 pagesGrid Interactive PV System With Harmonic and Reactive Power Compensation Features Using A Novel Fuzzy Logic Based MPPTvinay kumarNo ratings yet

- Single-Phase Five-Level Inverter With Less Number of Power Elements For Grid ConnectionDocument7 pagesSingle-Phase Five-Level Inverter With Less Number of Power Elements For Grid Connectionvinay kumarNo ratings yet

- 87Document5 pages87vinay kumarNo ratings yet

- Design and Simulation of Single Phase Z-Source Buck Boost Matrix ConverterDocument7 pagesDesign and Simulation of Single Phase Z-Source Buck Boost Matrix Convertervinay kumarNo ratings yet

- Indirect Control For Cascaded H-Bridge Rectifiers With Unequal LoadsDocument6 pagesIndirect Control For Cascaded H-Bridge Rectifiers With Unequal Loadsvinay kumarNo ratings yet

- DC Motor Speed Control For Electric Locomotive Equipped by Multi-Level DC-DC ConverterDocument7 pagesDC Motor Speed Control For Electric Locomotive Equipped by Multi-Level DC-DC Convertervinay kumarNo ratings yet

- New Method To Achieve AC Harmonic Elimination and Energy Storage Integration For 12-Pulse Diode RectifiersDocument8 pagesNew Method To Achieve AC Harmonic Elimination and Energy Storage Integration For 12-Pulse Diode Rectifiersvinay kumarNo ratings yet

- Switching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor DriveDocument6 pagesSwitching Pattern Selection Scheme Based Cascaded Multilevel Inverter Fed Induction Motor Drivevinay kumarNo ratings yet

- Thakur Institute of Aviation TechnologyDocument3 pagesThakur Institute of Aviation TechnologyAshwini ChaurasiaNo ratings yet

- Wipe TCL 11-6-17Document23 pagesWipe TCL 11-6-17anamika tripathiNo ratings yet

- MiscellanousDocument12 pagesMiscellanousJohn Lee PueyoNo ratings yet

- API For Acr120s Smart CardDocument0 pagesAPI For Acr120s Smart CardAldrin Jay MoralesNo ratings yet

- Laminar Flow Assignment No 3Document3 pagesLaminar Flow Assignment No 3Ayushi GuptaNo ratings yet

- Experiment 8: Determination of The Ratio of The Specific Heats of AIRDocument9 pagesExperiment 8: Determination of The Ratio of The Specific Heats of AIRwallace kitoNo ratings yet

- Agreed Site Measurement RecordDocument40 pagesAgreed Site Measurement Recordලහිරු විතානාච්චිNo ratings yet

- G.o.ms - No.119, Dt.28!03!2017 Including AmendmentsDocument271 pagesG.o.ms - No.119, Dt.28!03!2017 Including AmendmentsRaghu Ram72% (18)

- Topographic Map of FiskDocument1 pageTopographic Map of FiskHistoricalMapsNo ratings yet

- Tsbus2008 984Document47 pagesTsbus2008 984karlosc17No ratings yet

- Park-Hotel-Hyderabad ArchRecord PDFDocument4 pagesPark-Hotel-Hyderabad ArchRecord PDFAlexLionNo ratings yet

- Agent ApiDocument18 pagesAgent ApiMister MxyzptlkNo ratings yet

- Pre Feasibility Report For Welspun Iron & Steel Pvt. LimitedDocument25 pagesPre Feasibility Report For Welspun Iron & Steel Pvt. LimitedkalaiNo ratings yet

- E5118 Sre1-4Document4 pagesE5118 Sre1-4Ravi Kishore BNo ratings yet

- Abalioglu - Kullanım - Klavuzu - ING PDFDocument251 pagesAbalioglu - Kullanım - Klavuzu - ING PDFCan YEŞİLNo ratings yet

- Technical Data Sheet For Hilti HIT HY 200Document39 pagesTechnical Data Sheet For Hilti HIT HY 200ValeriuNo ratings yet

- 100/240 V Power Supply: Position: No. 0 (The Leftmost) PropertiesDocument2 pages100/240 V Power Supply: Position: No. 0 (The Leftmost) PropertieswulanluvspinkNo ratings yet

- Logiq Book User ManualDocument664 pagesLogiq Book User ManualLuisFer Garcia100% (2)

- CF Diagram Les Paul StandardDocument1 pageCF Diagram Les Paul Standardokr15No ratings yet

- Principles of Hydrostatic Pressure: CE 309 - Fluid Mechanics Prepared By: John Brix C. PronuncialDocument18 pagesPrinciples of Hydrostatic Pressure: CE 309 - Fluid Mechanics Prepared By: John Brix C. PronuncialWendell NiveraNo ratings yet

- dm3000 Dm1000-DatasheetDocument2 pagesdm3000 Dm1000-DatasheetRohitBhatNo ratings yet

- TK ACI BASF 8735 Co So OK LY THUYETDocument42 pagesTK ACI BASF 8735 Co So OK LY THUYETDao Phuc LamNo ratings yet

- Jeep 4.7 Motor 2Document1 pageJeep 4.7 Motor 2Agustin Borge GarciaNo ratings yet

- 3M Filter Requirement - 3064 MisfahDocument3 pages3M Filter Requirement - 3064 MisfahHari Hara SuthanNo ratings yet

- AQA Computing A2 Exam Style QsDocument40 pagesAQA Computing A2 Exam Style QsKonstantinos KastanasNo ratings yet

- BEHA M31. All ModelsDocument3 pagesBEHA M31. All ModelsDavison da Silva BarbosaNo ratings yet