Professional Documents

Culture Documents

KI Ế NTR Ú CM Á YT Í NH CE2010

KI Ế NTR Ú CM Á YT Í NH CE2010

Uploaded by

Thái Quang QuýCopyright:

Available Formats

You might also like

- Chapter 02 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionDocument93 pagesChapter 02 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionPriyanka Meena75% (4)

- Dokumen - Pub - Computer Systems An Integrated Approach To Architecture and Operating Systems 0321486137 9780321486134Document705 pagesDokumen - Pub - Computer Systems An Integrated Approach To Architecture and Operating Systems 0321486137 9780321486134Enrique González Carrillo100% (1)

- Computer Architecture Question PaperDocument14 pagesComputer Architecture Question Paperheaughfrds100% (1)

- XP SP2 Product KeyDocument2 pagesXP SP2 Product Keysurya06950% (6)

- Advanced Computer Architecture: Dr. Muhammad Bilal KadriDocument28 pagesAdvanced Computer Architecture: Dr. Muhammad Bilal KadriSana BilalNo ratings yet

- Chapter03 1MIPS ISA PDFDocument63 pagesChapter03 1MIPS ISA PDFHoang Thao NguyenNo ratings yet

- Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsDocument68 pagesComputer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsNapsterNo ratings yet

- Sap - 2Document135 pagesSap - 2Muh Nur FaiziNo ratings yet

- 2015Sp CS61C L05 Kavs M1Document36 pages2015Sp CS61C L05 Kavs M1MaiDungNo ratings yet

- CS6461 - Computer Architecture Fall 2016 Morris Lancaster: Lecture 3 - Instruction Set ArchitectureDocument40 pagesCS6461 - Computer Architecture Fall 2016 Morris Lancaster: Lecture 3 - Instruction Set Architecture闫麟阁No ratings yet

- COA Question Bank PDFDocument27 pagesCOA Question Bank PDFPoovarasanNo ratings yet

- CS122: Computer Architecture & Organization: Semester I, 2011Document27 pagesCS122: Computer Architecture & Organization: Semester I, 2011Tarunbir BangaNo ratings yet

- Sunu2 1Document28 pagesSunu2 1garamanli707No ratings yet

- Computer Architecture: Nguyễn Trí ThànhDocument70 pagesComputer Architecture: Nguyễn Trí Thànhhoang.van.tuanNo ratings yet

- 04 MIPSintro PDFDocument70 pages04 MIPSintro PDFMuhammad Zunair HussainNo ratings yet

- Ramesh .B ELEC 6200 Computer Architecture & Design Fall 2008Document17 pagesRamesh .B ELEC 6200 Computer Architecture & Design Fall 2008Amandeep Kaur JunejaNo ratings yet

- Lect#1 - IntroductionDocument47 pagesLect#1 - IntroductionSIYAB KhanNo ratings yet

- Ca 2 Marks & Big Ques PDFDocument96 pagesCa 2 Marks & Big Ques PDFsathya priyaNo ratings yet

- LECTURE2Document26 pagesLECTURE2Ahmed MahjoubNo ratings yet

- Instructions: Language of The ComputerDocument62 pagesInstructions: Language of The ComputerJoNo ratings yet

- Cpu RegistersDocument35 pagesCpu RegistersanandNo ratings yet

- Lecture 5 - CH 02Document12 pagesLecture 5 - CH 02aliNo ratings yet

- Internal Assignment: Name Sneha Sankhla Roll Number 2214505216 Program Master of Computer Applications (Mca) Semester 1Document13 pagesInternal Assignment: Name Sneha Sankhla Roll Number 2214505216 Program Master of Computer Applications (Mca) Semester 1Sneha SankhlaNo ratings yet

- Chapter1 AcaDocument26 pagesChapter1 AcaKusuma P ChandrashekharNo ratings yet

- Assignment1 4Document5 pagesAssignment1 4Munim DheemanNo ratings yet

- Chapter 2Document72 pagesChapter 2Phú Quốc PhạmNo ratings yet

- CSE 675.02: Introduction To Computer Architecture: Instructor: Roger CrawfisDocument37 pagesCSE 675.02: Introduction To Computer Architecture: Instructor: Roger CrawfisJamsher BhanbhroNo ratings yet

- Unit 3Document68 pagesUnit 3subithavNo ratings yet

- Performance of A ComputerDocument83 pagesPerformance of A ComputerPrakherGuptaNo ratings yet

- Mips Instruction FormatDocument41 pagesMips Instruction Formatvivek patelNo ratings yet

- ACA Chapter 1Document106 pagesACA Chapter 1vishal95100% (1)

- L1 IntroductionDocument26 pagesL1 IntroductionMuhammad sohaibNo ratings yet

- Chapter 3 MohammadDocument52 pagesChapter 3 MohammadAchiaa Osei-DonkorNo ratings yet

- Question Bank For Computer ArchitectureDocument23 pagesQuestion Bank For Computer ArchitecturesuryaNo ratings yet

- Lec4 ch2-1Document37 pagesLec4 ch2-1Hussam AtherNo ratings yet

- COA - Unit 1 An IntroductionDocument26 pagesCOA - Unit 1 An IntroductionDevika csbsNo ratings yet

- Programming in CDocument211 pagesProgramming in CSrilekha MaruthaiyanNo ratings yet

- Chapter 1 Measuring Understanding PerformanceDocument63 pagesChapter 1 Measuring Understanding Performancequejaukennoitrei-2168No ratings yet

- Chapter 2 Instructions Language of The ComputerDocument94 pagesChapter 2 Instructions Language of The Computerkrishnagovind33No ratings yet

- Ece4750 T01 Proc ScycleDocument24 pagesEce4750 T01 Proc ScyclekartimidNo ratings yet

- Advanced Advanced Computer Computer Architecture ArchitectureDocument34 pagesAdvanced Advanced Computer Computer Architecture ArchitectureSam Thui Sam ThuiNo ratings yet

- Mips PPT SlidesDocument35 pagesMips PPT SlidesHassanMalikNo ratings yet

- Lecture 2 - MIPS Architecture Part I - Instruction SetDocument53 pagesLecture 2 - MIPS Architecture Part I - Instruction SetLaurenceNo ratings yet

- Complex Instruction Set ComputerDocument17 pagesComplex Instruction Set ComputerkangkanpaulNo ratings yet

- DDCA Question Bank CO-3Document11 pagesDDCA Question Bank CO-3rutwika06No ratings yet

- COA Unit 3Document52 pagesCOA Unit 3guptakrishns23No ratings yet

- Unit 1 Module 1-MergedDocument118 pagesUnit 1 Module 1-Mergedmaneskin488No ratings yet

- Lecture 3: Performance/Power, MIPS InstructionsDocument22 pagesLecture 3: Performance/Power, MIPS InstructionsHariharan SNo ratings yet

- CA Project ReportDocument26 pagesCA Project ReportShivam SisodiaNo ratings yet

- Assembly Programming: Introduction To Computer OrganizationDocument39 pagesAssembly Programming: Introduction To Computer OrganizationSai SaurabNo ratings yet

- II - DDCA - CO-3 - Terminal QuestionsDocument7 pagesII - DDCA - CO-3 - Terminal Questionspavan karthikNo ratings yet

- CAMP - QBDocument10 pagesCAMP - QBAkshai AkshaiNo ratings yet

- Instructions: Language of The ComputerDocument92 pagesInstructions: Language of The Computerdelinquent_abhishekNo ratings yet

- COMP 303 Lecture 1 (CH 1)Document21 pagesCOMP 303 Lecture 1 (CH 1)Emre KargıcıoğluNo ratings yet

- cs1104 p2 01Document35 pagescs1104 p2 01hafzalmjNo ratings yet

- Instructions: Language of The Computer: Omputer Rganization and EsignDocument33 pagesInstructions: Language of The Computer: Omputer Rganization and EsignBody AbdoNo ratings yet

- Digital Assignment #1 Course Name: Computer Architecture and Date: 11/10/2020 Course Code: CSE2001 Submission DeadlineDocument2 pagesDigital Assignment #1 Course Name: Computer Architecture and Date: 11/10/2020 Course Code: CSE2001 Submission DeadlineVicky VNo ratings yet

- Instructions: Language of The Computer PDocument92 pagesInstructions: Language of The Computer PAdip ChyNo ratings yet

- BCS-011 Computer Basics and PC Software Solved Assignment 2019-2020Document11 pagesBCS-011 Computer Basics and PC Software Solved Assignment 2019-2020IGNOUAssignmentGuru80% (10)

- BCS 011 Computer Basics and PC Software SOLVED ASSIGNMENT For 2019 2020 Session Free BY ASSINGMENTGURU PDFDocument11 pagesBCS 011 Computer Basics and PC Software SOLVED ASSIGNMENT For 2019 2020 Session Free BY ASSINGMENTGURU PDFAJ SharmaNo ratings yet

- COMPUTER ORGANISATION (LONG ANSWERS 2 PM)Document5 pagesCOMPUTER ORGANISATION (LONG ANSWERS 2 PM)spacekiller98No ratings yet

- Computer Hardware and Maintenance AssignmentDocument8 pagesComputer Hardware and Maintenance AssignmentDawit HukaNo ratings yet

- On Variables and OperatorsDocument14 pagesOn Variables and Operatorsgopi chand mallelaNo ratings yet

- Data Ontap 8.2: Storage Management Guide For 7-ModeDocument397 pagesData Ontap 8.2: Storage Management Guide For 7-ModeAdhye KurniadhyeNo ratings yet

- Computer Systems: CS553 Homework #2Document2 pagesComputer Systems: CS553 Homework #2Hariharan ShankarNo ratings yet

- Find Serial Number of Computer in Windows 10Document2 pagesFind Serial Number of Computer in Windows 10GabbarNo ratings yet

- Inventory of Equipment, Gadgets, Fixtures A. Laboratory 1 A.1 IT Equipment-HardwareDocument1 pageInventory of Equipment, Gadgets, Fixtures A. Laboratory 1 A.1 IT Equipment-HardwareJo Fel GarciaNo ratings yet

- Deploying Jupyter Notebooks For Students and ResearchersDocument35 pagesDeploying Jupyter Notebooks For Students and Researchersميلاد نوروزي رهبرNo ratings yet

- New The World of The Internet HandoutsDocument17 pagesNew The World of The Internet HandoutsZee AmanuelNo ratings yet

- Deployment StepsDocument3 pagesDeployment Stepsmahesh84psgNo ratings yet

- Modicon M340 Automation Platform BMXNOE0100Document3 pagesModicon M340 Automation Platform BMXNOE0100KuncoroNuryantoNo ratings yet

- Assignment 2 AssemblyDocument3 pagesAssignment 2 AssemblySyed WahabNo ratings yet

- Linux Device Driver DevelopmentDocument647 pagesLinux Device Driver Developmentobsey jackson100% (1)

- HPC - PyqDocument2 pagesHPC - Pyqtanay.bhor3No ratings yet

- Adobe AIR - Installing Adobe AIRDocument1 pageAdobe AIR - Installing Adobe AIRAriant PanjoolateNo ratings yet

- DX DiagDocument34 pagesDX Diagjeremyrondon97No ratings yet

- Computer Network - Layers of OSI ModelDocument6 pagesComputer Network - Layers of OSI ModelAbdul RehmanNo ratings yet

- CSC130CEx6S PDFDocument4 pagesCSC130CEx6S PDFmohammedNo ratings yet

- VME BioDrive - Biometric Flash Storage DeviceDocument1 pageVME BioDrive - Biometric Flash Storage DeviceMeganet CorporationNo ratings yet

- Design and Development of Android Based Attendance Management SystemDocument8 pagesDesign and Development of Android Based Attendance Management SystemTolorunleke FakiyesiNo ratings yet

- Lexmark E-Guide 2011 MajDocument302 pagesLexmark E-Guide 2011 MajIvana SmoljanNo ratings yet

- Lab 1: Kali Linux (Tiger Box) : ObjectivesDocument16 pagesLab 1: Kali Linux (Tiger Box) : ObjectivessalwaNo ratings yet

- SS ZG656Document13 pagesSS ZG656Mahesh H MNo ratings yet

- 004 - Hadoop Daemons (HDFS Only)Document3 pages004 - Hadoop Daemons (HDFS Only)Srinivas ReddyNo ratings yet

- DocumentDocument2 pagesDocumentAddieNo ratings yet

- Aadil Final FrontDocument6 pagesAadil Final FrontRaghu RamNo ratings yet

- Install Ubuntu Dual WindowDocument5 pagesInstall Ubuntu Dual WindowThành CôngNo ratings yet

- Error Detection and CorrectionDocument54 pagesError Detection and Correction209X1A2855 MEKALA VARUN YADAVNo ratings yet

- NdiswrapperDocument2 pagesNdiswrapperVentas PremiumsrlNo ratings yet

KI Ế NTR Ú CM Á YT Í NH CE2010

KI Ế NTR Ú CM Á YT Í NH CE2010

Uploaded by

Thái Quang QuýOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

KI Ế NTR Ú CM Á YT Í NH CE2010

KI Ế NTR Ú CM Á YT Í NH CE2010

Uploaded by

Thái Quang QuýCopyright:

Available Formats

dce

2010

KIN TRC MY TNH CE2010

BK

TP.HCM

Khoa Khoa hc v K thut My tnh BM K thut My tnh inh c Anh V http://www.cse.hcmut.edu.vn/~anhvu

2010, Dr. Dinh Duc Anh Vu

dce

2010

Instructions: Language of the Computer

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

dce

2010

Computer Architecture Is

the attributes of a [computing] system as seen by the programmer, i.e., the conceptual structure and functional behavior, as distinct from the organization of the data flows and controls the logic design, and the physical implementation. Amdahl, Blaaw, and Brooks, 1964

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

dce

2010

CAs Changing Definition

1950s to 1960s: Computer Architecture Course = Computer Arithmetic 1970s to mid 1980s: Computer Architecture Course = Instruction Set Design, especially ISA appropriate for compilers 1990s: Computer Architecture Course = Design of CPU, memory system, I/O system, Multiprocessors

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 4

dce

2010

The Instruction Set Architecture (ISA)

software

instruction set architecture

hardware

The interface description separating the software and hardware

Computer Architecture, Chapter 1 2010, Dr. Dinh Duc Anh Vu 5

dce

2010

Evolution of Instruction Sets

Single Accumulator (EDSAC 1950) Accumulator + Index Registers (Manchester Mark I, IBM 700 series 1953) Separation of Programming Model from Implementation

High-level Language Based (B5000 1963)

Concept of a Family (IBM 360 1964)

General Purpose Register Machines Complex Instruction Sets (Vax, Intel 432 1977-80) Load/Store Architecture (CDC 6600, Cray 1 1963-76) RISC (Mips,Sparc,HP-PA,IBM RS6000,PowerPC . . .1987) LIW/EPIC?

Computer Architecture, Chapter 2

(IA-64. . .1999)

6

2010, Dr. Dinh Duc Anh Vu

dce

2010

Evolution of Instruction Sets

Computer Architecture, Chapter 2

dce

2010

Evolution of Instruction Sets

Example: C := A + B

add C, A, B

Accumulator

load A add B store C #accum = M[A]; #accum += M[B]; #M[C] = accum; #M[C] = M[A] + M[B]; #R1 = M[A]; #R1 = R1 + M[B]; #M[C] = R1; #R1 = M[A]; #R2 = M[B]; #R3 = R1 + R2; #M[C] = R3;

Memory Memory

add C,A, B

Memory Register

load R1, A add R1,B store C,R1

Register Register

load R1,A load R2,B add R3,R1,R2 store C,R3

Computer Architecture, Chapter 2

dce

2010

Evolution of Instruction Sets

Major advances in computer architecture are typically associated with landmark instruction set designs

Ex: Stack vs GPR (System 360)

Design decisions must take into account:

technology machine organization programming languages compiler technology operating systems applications

And they in turn influence these

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 9

dce

2010

RISC Reduced Instruction Set Computer

RISC philosophy

fixed instruction lengths load-store instruction sets limited number of addressing modes limited number of operations

MIPS, Sun SPARC, HP PA-RISC, IBM PowerPC Instruction sets are measured by how well compilers use them as opposed to how well assembly language programmers use them CISC (C for complex), e.g., Intel x86

Design goals: speed, cost (design, fabrication, test, packaging), size, power consumption, reliability, memory space (embedded systems)

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 10

dce

2010

Instruction Set

The repertoire of instructions of a computer Different computers have different instruction sets

But with many aspects in common

Early computers had very simple instruction sets

Simplified implementation

Many modern computers also have simple instruction sets

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

11

dce

2010

The MIPS Instruction Set

Used as the example throughout the course Stanford MIPS commercialized by MIPS Technologies (www.mips.com) Large share of embedded core market

Applications in consumer electronics, network/storage equipment, cameras, printers,

Typical of many modern ISAs

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

12

dce

2010

The MIPS ISA

Instruction Categories

Load/Store Computational Jump and Branch Floating Point

coprocessor

Registers R0 - R31

Memory Management Special

OP OP OP

Computer Architecture, Chapter 2

PC HI LO

3 Instruction Formats: all 32 bits wide

rs rs rt rt jump target

2010, Dr. Dinh Duc Anh Vu 13

rd

shamt immediate

funct

dce

2010

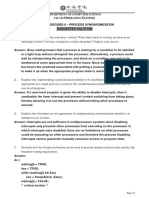

MIPS (RISC) Design Principles

Simplicity favors regularity

fixed size instructions small number of instruction formats opcode always the first 6 bits

Smaller is faster

limited instruction set limited number of registers in register file limited number of addressing modes

Make the common case fast

arithmetic operands from the register file (load-store machine) allow instructions to contain immediate operands

Good design demands good compromises

Same instruction length Single instruction format => 3 instruction formats

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 14

dce

2010

MIPS Instruction Classes Distribution

Frequency of MIPS instruction classes for SPEC2006

Instruction Class Integer Arithmetic Data transfer Logical Cond. Branch Jump 16% 35% 12% 34% 2% Frequency Ft. Pt. 48% 36% 4% 8% 0%

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

15

dce

2010

MIPS Arithmetic Instructions

MIPS assembly language arithmetic statement add $t0, $s1, $s2 sub $t0, $s1, $s2 Each arithmetic instruction performs one operation Each specifies exactly three operands that are all contained in the datapaths register file ($t0,$s1,$s2)

destination source1 op source2

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

16

dce

2010

MIPS Register File

Holds 32 32-bit registers

Two read ports and One write port

Registers are

Faster than main memory

But register files with more locations are slower (e.g., a 64 word file could be as much as 50% slower than a 32 word file) Read/write port increase impacts speed quadratically

Easier for a compiler to use

e.g., (A*B) (C*D) (E*F) can do multiplies in any order vs. stack

Can hold variables so that

code density improves (since register are named with fewer bits than a memory location)

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 17

dce

2010

Aside: MIPS Register Convention

Name $zero $at $v0 - $v1 $a0 - $a3 $t0 - $t7 $s0 - $s7 $t8 - $t9 $k0 - $k1 $gp $sp $fp $ra Register Number 0 1 2-3 4-7 8-15 16-23 24-25 26-27 28 29 30 31 Usage constant 0 (hardware) reserved for assembler returned values arguments temporaries saved values temporaries reserved for operating system global pointer stack pointer frame pointer return addr (hardware) Preserve on call? n.a. n.a. no yes no yes no n.a yes yes yes yes

18

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

dce

2010

Registers vs. Memory

Arithmetic instructions operands must be in registers

Processor Control Datapath

Memory

Devices Network Input Output

Compiler associates variables with registers What about programs with lots of variables?

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 19

dce

2010

Processor Memory Interconnections

Memory is a large, single-dimensional array An address acts as the index into the memory array

Memory read addr/ write addr Processor read data write data

10 101 1 8 4 0

? locations

32 bits

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 20

dce

2010

Accessing Memory

MIPS has two basic data transfer instructions for accessing memory (assume $s3 holds 2410)

lw sw $t0, 4($s3) $t0, 8($s3) #load word from memory #store word to memory

The data transfer instruction must specify

where in memory to read from (load) or write to (store) memory address where in the register file to write to (load) or read from (store) register destination (source)

The memory address is formed by summing the constant portion of the instruction and the contents of the second register

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 21

dce

2010

MIPS Memory Addressing

The memory address is formed by summing the constant portion of the instruction and the contents of the second (base) register

$s3 holds 8

Memory ...0110 ...0101 ...1100 ...0001 ...0010 ...1000 ...0100 32 bit Data lw sw $t0, 4($s3) $t0, 8($s3) 24 20 16 12 8 4 0 Word Address

#what? is loaded into $t0 #$t0 is stored where?

2010, Dr. Dinh Duc Anh Vu 22

Computer Architecture, Chapter 2

dce

2010

Compiling with Loads and Stores

Assuming variable b is stored in $s2 and that the base address of array A is in $s3, what is the MIPS assembly code for the C statement A[8] = A[2] - b

... A[3] A[2] A[1] A[0] ... $s3+12 $s3+8 $s3+4 $s3

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

23

dce

2010

Compiling with a Variable Array Index

Assuming that the base address of array A is in register $s4, and variables b, c, and i are in $s1, $s2, and $s3, respectively, what is the MIPS assembly code for the C statement ... ... c = A[i] - b

A[3] A[2] A[1] A[0] add add $s4+12 $s4+8 $s4+4 $s4 $t1, $s3, $s3 $t1, $t1, $t1 #array index i is in $s3 #temp reg $t1 holds 4*i

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

24

dce

2010

Dealing with Constants

Small constants are used quite frequently (50% of operands in many common programs)

e.g., A = A + 5; B = B + 1; C = C - 18;

Solutions? Why not?

Put typical constants in memory and load them Create hard-wired registers (like $zero) for constants like 1, 2, 4, 10,

How do we make this work?

How do we Make the common case fast !

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 25

dce

2010

Constant (or Immediate) Operands

Include constants inside arithmetic instructions

Much faster than if they have to be loaded from memory (they come in from memory with the instruction itself)

MIPS immediate instructions

addi $s3, $s3, 4 #$s3 = $s3 + 4

There is no subi instruction, can you guess why not?

Computer Architecture, Chapter 2 2010, Dr. Dinh Duc Anh Vu 26

dce

2010

MIPS Instructions, so far

Category Instr Example Meaning

add Arithmetic subtract add immediate Data transfer load word store word

add sub

$s1, $s2, $s3 $s1, $s2, $s3

$s1 = $s2 + $s3 $s1 = $s2 - $s3 $s1 = $s2 + 4 $s1 = Memory($s2+32) Memory($s2+32) = $s1

addi $s1, $s2, 4 lw sw $s1, 32($s2) $s1, 32($s2)

Computer Architecture, Chapter 2

2010, Dr. Dinh Duc Anh Vu

27

You might also like

- Chapter 02 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionDocument93 pagesChapter 02 Computer Organization and Design, Fifth Edition: The Hardware/Software Interface (The Morgan Kaufmann Series in Computer Architecture and Design) 5th EditionPriyanka Meena75% (4)

- Dokumen - Pub - Computer Systems An Integrated Approach To Architecture and Operating Systems 0321486137 9780321486134Document705 pagesDokumen - Pub - Computer Systems An Integrated Approach To Architecture and Operating Systems 0321486137 9780321486134Enrique González Carrillo100% (1)

- Computer Architecture Question PaperDocument14 pagesComputer Architecture Question Paperheaughfrds100% (1)

- XP SP2 Product KeyDocument2 pagesXP SP2 Product Keysurya06950% (6)

- Advanced Computer Architecture: Dr. Muhammad Bilal KadriDocument28 pagesAdvanced Computer Architecture: Dr. Muhammad Bilal KadriSana BilalNo ratings yet

- Chapter03 1MIPS ISA PDFDocument63 pagesChapter03 1MIPS ISA PDFHoang Thao NguyenNo ratings yet

- Computer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsDocument68 pagesComputer Architecture Lecture Notes Spring 2005 Dr. Michael P. Frank Competency Area 3: Programming and Coding MethodsNapsterNo ratings yet

- Sap - 2Document135 pagesSap - 2Muh Nur FaiziNo ratings yet

- 2015Sp CS61C L05 Kavs M1Document36 pages2015Sp CS61C L05 Kavs M1MaiDungNo ratings yet

- CS6461 - Computer Architecture Fall 2016 Morris Lancaster: Lecture 3 - Instruction Set ArchitectureDocument40 pagesCS6461 - Computer Architecture Fall 2016 Morris Lancaster: Lecture 3 - Instruction Set Architecture闫麟阁No ratings yet

- COA Question Bank PDFDocument27 pagesCOA Question Bank PDFPoovarasanNo ratings yet

- CS122: Computer Architecture & Organization: Semester I, 2011Document27 pagesCS122: Computer Architecture & Organization: Semester I, 2011Tarunbir BangaNo ratings yet

- Sunu2 1Document28 pagesSunu2 1garamanli707No ratings yet

- Computer Architecture: Nguyễn Trí ThànhDocument70 pagesComputer Architecture: Nguyễn Trí Thànhhoang.van.tuanNo ratings yet

- 04 MIPSintro PDFDocument70 pages04 MIPSintro PDFMuhammad Zunair HussainNo ratings yet

- Ramesh .B ELEC 6200 Computer Architecture & Design Fall 2008Document17 pagesRamesh .B ELEC 6200 Computer Architecture & Design Fall 2008Amandeep Kaur JunejaNo ratings yet

- Lect#1 - IntroductionDocument47 pagesLect#1 - IntroductionSIYAB KhanNo ratings yet

- Ca 2 Marks & Big Ques PDFDocument96 pagesCa 2 Marks & Big Ques PDFsathya priyaNo ratings yet

- LECTURE2Document26 pagesLECTURE2Ahmed MahjoubNo ratings yet

- Instructions: Language of The ComputerDocument62 pagesInstructions: Language of The ComputerJoNo ratings yet

- Cpu RegistersDocument35 pagesCpu RegistersanandNo ratings yet

- Lecture 5 - CH 02Document12 pagesLecture 5 - CH 02aliNo ratings yet

- Internal Assignment: Name Sneha Sankhla Roll Number 2214505216 Program Master of Computer Applications (Mca) Semester 1Document13 pagesInternal Assignment: Name Sneha Sankhla Roll Number 2214505216 Program Master of Computer Applications (Mca) Semester 1Sneha SankhlaNo ratings yet

- Chapter1 AcaDocument26 pagesChapter1 AcaKusuma P ChandrashekharNo ratings yet

- Assignment1 4Document5 pagesAssignment1 4Munim DheemanNo ratings yet

- Chapter 2Document72 pagesChapter 2Phú Quốc PhạmNo ratings yet

- CSE 675.02: Introduction To Computer Architecture: Instructor: Roger CrawfisDocument37 pagesCSE 675.02: Introduction To Computer Architecture: Instructor: Roger CrawfisJamsher BhanbhroNo ratings yet

- Unit 3Document68 pagesUnit 3subithavNo ratings yet

- Performance of A ComputerDocument83 pagesPerformance of A ComputerPrakherGuptaNo ratings yet

- Mips Instruction FormatDocument41 pagesMips Instruction Formatvivek patelNo ratings yet

- ACA Chapter 1Document106 pagesACA Chapter 1vishal95100% (1)

- L1 IntroductionDocument26 pagesL1 IntroductionMuhammad sohaibNo ratings yet

- Chapter 3 MohammadDocument52 pagesChapter 3 MohammadAchiaa Osei-DonkorNo ratings yet

- Question Bank For Computer ArchitectureDocument23 pagesQuestion Bank For Computer ArchitecturesuryaNo ratings yet

- Lec4 ch2-1Document37 pagesLec4 ch2-1Hussam AtherNo ratings yet

- COA - Unit 1 An IntroductionDocument26 pagesCOA - Unit 1 An IntroductionDevika csbsNo ratings yet

- Programming in CDocument211 pagesProgramming in CSrilekha MaruthaiyanNo ratings yet

- Chapter 1 Measuring Understanding PerformanceDocument63 pagesChapter 1 Measuring Understanding Performancequejaukennoitrei-2168No ratings yet

- Chapter 2 Instructions Language of The ComputerDocument94 pagesChapter 2 Instructions Language of The Computerkrishnagovind33No ratings yet

- Ece4750 T01 Proc ScycleDocument24 pagesEce4750 T01 Proc ScyclekartimidNo ratings yet

- Advanced Advanced Computer Computer Architecture ArchitectureDocument34 pagesAdvanced Advanced Computer Computer Architecture ArchitectureSam Thui Sam ThuiNo ratings yet

- Mips PPT SlidesDocument35 pagesMips PPT SlidesHassanMalikNo ratings yet

- Lecture 2 - MIPS Architecture Part I - Instruction SetDocument53 pagesLecture 2 - MIPS Architecture Part I - Instruction SetLaurenceNo ratings yet

- Complex Instruction Set ComputerDocument17 pagesComplex Instruction Set ComputerkangkanpaulNo ratings yet

- DDCA Question Bank CO-3Document11 pagesDDCA Question Bank CO-3rutwika06No ratings yet

- COA Unit 3Document52 pagesCOA Unit 3guptakrishns23No ratings yet

- Unit 1 Module 1-MergedDocument118 pagesUnit 1 Module 1-Mergedmaneskin488No ratings yet

- Lecture 3: Performance/Power, MIPS InstructionsDocument22 pagesLecture 3: Performance/Power, MIPS InstructionsHariharan SNo ratings yet

- CA Project ReportDocument26 pagesCA Project ReportShivam SisodiaNo ratings yet

- Assembly Programming: Introduction To Computer OrganizationDocument39 pagesAssembly Programming: Introduction To Computer OrganizationSai SaurabNo ratings yet

- II - DDCA - CO-3 - Terminal QuestionsDocument7 pagesII - DDCA - CO-3 - Terminal Questionspavan karthikNo ratings yet

- CAMP - QBDocument10 pagesCAMP - QBAkshai AkshaiNo ratings yet

- Instructions: Language of The ComputerDocument92 pagesInstructions: Language of The Computerdelinquent_abhishekNo ratings yet

- COMP 303 Lecture 1 (CH 1)Document21 pagesCOMP 303 Lecture 1 (CH 1)Emre KargıcıoğluNo ratings yet

- cs1104 p2 01Document35 pagescs1104 p2 01hafzalmjNo ratings yet

- Instructions: Language of The Computer: Omputer Rganization and EsignDocument33 pagesInstructions: Language of The Computer: Omputer Rganization and EsignBody AbdoNo ratings yet

- Digital Assignment #1 Course Name: Computer Architecture and Date: 11/10/2020 Course Code: CSE2001 Submission DeadlineDocument2 pagesDigital Assignment #1 Course Name: Computer Architecture and Date: 11/10/2020 Course Code: CSE2001 Submission DeadlineVicky VNo ratings yet

- Instructions: Language of The Computer PDocument92 pagesInstructions: Language of The Computer PAdip ChyNo ratings yet

- BCS-011 Computer Basics and PC Software Solved Assignment 2019-2020Document11 pagesBCS-011 Computer Basics and PC Software Solved Assignment 2019-2020IGNOUAssignmentGuru80% (10)

- BCS 011 Computer Basics and PC Software SOLVED ASSIGNMENT For 2019 2020 Session Free BY ASSINGMENTGURU PDFDocument11 pagesBCS 011 Computer Basics and PC Software SOLVED ASSIGNMENT For 2019 2020 Session Free BY ASSINGMENTGURU PDFAJ SharmaNo ratings yet

- COMPUTER ORGANISATION (LONG ANSWERS 2 PM)Document5 pagesCOMPUTER ORGANISATION (LONG ANSWERS 2 PM)spacekiller98No ratings yet

- Computer Hardware and Maintenance AssignmentDocument8 pagesComputer Hardware and Maintenance AssignmentDawit HukaNo ratings yet

- On Variables and OperatorsDocument14 pagesOn Variables and Operatorsgopi chand mallelaNo ratings yet

- Data Ontap 8.2: Storage Management Guide For 7-ModeDocument397 pagesData Ontap 8.2: Storage Management Guide For 7-ModeAdhye KurniadhyeNo ratings yet

- Computer Systems: CS553 Homework #2Document2 pagesComputer Systems: CS553 Homework #2Hariharan ShankarNo ratings yet

- Find Serial Number of Computer in Windows 10Document2 pagesFind Serial Number of Computer in Windows 10GabbarNo ratings yet

- Inventory of Equipment, Gadgets, Fixtures A. Laboratory 1 A.1 IT Equipment-HardwareDocument1 pageInventory of Equipment, Gadgets, Fixtures A. Laboratory 1 A.1 IT Equipment-HardwareJo Fel GarciaNo ratings yet

- Deploying Jupyter Notebooks For Students and ResearchersDocument35 pagesDeploying Jupyter Notebooks For Students and Researchersميلاد نوروزي رهبرNo ratings yet

- New The World of The Internet HandoutsDocument17 pagesNew The World of The Internet HandoutsZee AmanuelNo ratings yet

- Deployment StepsDocument3 pagesDeployment Stepsmahesh84psgNo ratings yet

- Modicon M340 Automation Platform BMXNOE0100Document3 pagesModicon M340 Automation Platform BMXNOE0100KuncoroNuryantoNo ratings yet

- Assignment 2 AssemblyDocument3 pagesAssignment 2 AssemblySyed WahabNo ratings yet

- Linux Device Driver DevelopmentDocument647 pagesLinux Device Driver Developmentobsey jackson100% (1)

- HPC - PyqDocument2 pagesHPC - Pyqtanay.bhor3No ratings yet

- Adobe AIR - Installing Adobe AIRDocument1 pageAdobe AIR - Installing Adobe AIRAriant PanjoolateNo ratings yet

- DX DiagDocument34 pagesDX Diagjeremyrondon97No ratings yet

- Computer Network - Layers of OSI ModelDocument6 pagesComputer Network - Layers of OSI ModelAbdul RehmanNo ratings yet

- CSC130CEx6S PDFDocument4 pagesCSC130CEx6S PDFmohammedNo ratings yet

- VME BioDrive - Biometric Flash Storage DeviceDocument1 pageVME BioDrive - Biometric Flash Storage DeviceMeganet CorporationNo ratings yet

- Design and Development of Android Based Attendance Management SystemDocument8 pagesDesign and Development of Android Based Attendance Management SystemTolorunleke FakiyesiNo ratings yet

- Lexmark E-Guide 2011 MajDocument302 pagesLexmark E-Guide 2011 MajIvana SmoljanNo ratings yet

- Lab 1: Kali Linux (Tiger Box) : ObjectivesDocument16 pagesLab 1: Kali Linux (Tiger Box) : ObjectivessalwaNo ratings yet

- SS ZG656Document13 pagesSS ZG656Mahesh H MNo ratings yet

- 004 - Hadoop Daemons (HDFS Only)Document3 pages004 - Hadoop Daemons (HDFS Only)Srinivas ReddyNo ratings yet

- DocumentDocument2 pagesDocumentAddieNo ratings yet

- Aadil Final FrontDocument6 pagesAadil Final FrontRaghu RamNo ratings yet

- Install Ubuntu Dual WindowDocument5 pagesInstall Ubuntu Dual WindowThành CôngNo ratings yet

- Error Detection and CorrectionDocument54 pagesError Detection and Correction209X1A2855 MEKALA VARUN YADAVNo ratings yet

- NdiswrapperDocument2 pagesNdiswrapperVentas PremiumsrlNo ratings yet