Professional Documents

Culture Documents

(IIT Guwahati) VLSI Design Verification and Test

(IIT Guwahati) VLSI Design Verification and Test

Uploaded by

jitu_4Copyright:

Available Formats

You might also like

- 523-0775579-003117 3ed Collins - 85C - EFIS - ManualDocument161 pages523-0775579-003117 3ed Collins - 85C - EFIS - Manualfiskit100% (5)

- Heathkit Schematic and Manual Archive InDICE PDFDocument30 pagesHeathkit Schematic and Manual Archive InDICE PDFGautam Balhara33% (6)

- DSP QuestionsDocument46 pagesDSP QuestionsAnonymous tLOxgFkyNo ratings yet

- A-Law and U-Law CompandingDocument4 pagesA-Law and U-Law CompandingAchyut Dev50% (2)

- Chapter 3 Part 1 Sensor and TransducersDocument48 pagesChapter 3 Part 1 Sensor and TransducersFikadu Eshetu100% (1)

- ECE 027 - Module 1 - Introduction About Semiconductor DiodesDocument54 pagesECE 027 - Module 1 - Introduction About Semiconductor DiodesMiyuki NakiriNo ratings yet

- Embedded System LESSONPLANDocument7 pagesEmbedded System LESSONPLANgallantprakashNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- WDC Question Bank 2018Document8 pagesWDC Question Bank 2018Aadharsh HariharanNo ratings yet

- Ofdm ProblemsDocument3 pagesOfdm ProblemsmohanshapuramNo ratings yet

- Chapter 12 Wireless Sensor Networks: From Reference Book: Adhoc Wireless Networks By: B.S. ManojDocument42 pagesChapter 12 Wireless Sensor Networks: From Reference Book: Adhoc Wireless Networks By: B.S. ManojMounisha g bNo ratings yet

- Unit 3 - WSN - MACDocument22 pagesUnit 3 - WSN - MACRmkumarsNo ratings yet

- Experiment No. 5 Darlington Pair Connection: (CITATION Ele /L 1033)Document4 pagesExperiment No. 5 Darlington Pair Connection: (CITATION Ele /L 1033)Dan BautistaNo ratings yet

- MPMC Lab ManualDocument157 pagesMPMC Lab ManualSanmuga SundaramNo ratings yet

- Chapter 1 Introduction To Robotics PDFDocument10 pagesChapter 1 Introduction To Robotics PDFOmar AL JabaiNo ratings yet

- Microprocessors & Interfacing Techniques Assignment No. 2Document2 pagesMicroprocessors & Interfacing Techniques Assignment No. 2Abdullah Nasir100% (4)

- EC8701-Antenna and Microwave EngineeringDocument12 pagesEC8701-Antenna and Microwave EngineeringsureshvkumarNo ratings yet

- Cyclotron Angular Frequency, Problems On Magnetron: Microwave Crossed-Field Tubes: 03/12/2020 & 10:00 AM-11:00 AMDocument18 pagesCyclotron Angular Frequency, Problems On Magnetron: Microwave Crossed-Field Tubes: 03/12/2020 & 10:00 AM-11:00 AMravi kiranNo ratings yet

- Assignment Digital CommunicationDocument8 pagesAssignment Digital CommunicationAkash SharmaNo ratings yet

- Laser MetrologyDocument41 pagesLaser MetrologyjennybunnyomgNo ratings yet

- Dcom Mod4Document4 pagesDcom Mod4Vidit shahNo ratings yet

- Value Added CourseDocument4 pagesValue Added CourseSuresh VaruvelNo ratings yet

- CU7008-Ultra Wideband CommunicationDocument16 pagesCU7008-Ultra Wideband CommunicationSaad100% (2)

- Ece-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentDocument9 pagesEce-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentMuhammadMansoorGohar100% (1)

- Bluetooth Based Smart Sensor NetworksDocument17 pagesBluetooth Based Smart Sensor NetworksEmjay ParkerNo ratings yet

- Cec355 - SDR Model QN Set IiDocument2 pagesCec355 - SDR Model QN Set Iivenki08No ratings yet

- Adaptive Signal ProcessingDocument24 pagesAdaptive Signal Processinganilshaw27No ratings yet

- Timer and CounterDocument30 pagesTimer and Countercleopatra2121No ratings yet

- Signals & Systems QBDocument18 pagesSignals & Systems QBAnonymous Ndsvh2soNo ratings yet

- Heart Attack Detection and Heart Rate Monitoring Using Iot: - Guided by - Presented byDocument6 pagesHeart Attack Detection and Heart Rate Monitoring Using Iot: - Guided by - Presented byBrightworld ProjectsNo ratings yet

- CU5191-Advanced Radiation SystemsDocument15 pagesCU5191-Advanced Radiation SystemsSaad0% (1)

- Rectangular WaveguideDocument5 pagesRectangular WaveguideSarveenaNo ratings yet

- Electronic Devices Lab MANUALDocument24 pagesElectronic Devices Lab MANUALna_hariprsadNo ratings yet

- Satellite Communication Unit 4Document16 pagesSatellite Communication Unit 4deepthiNo ratings yet

- Course Notes Advanced DSPDocument122 pagesCourse Notes Advanced DSPAnonymous hDKqasfNo ratings yet

- FeedCon (Unit 1)Document10 pagesFeedCon (Unit 1)Melissa LindayagNo ratings yet

- BAN U-1Document18 pagesBAN U-1kathiresanaembhithi100% (1)

- Aeronautical CommunicationsDocument18 pagesAeronautical CommunicationsBibinMathewNo ratings yet

- Diversity Techniques in Wireless Communication SystemsDocument30 pagesDiversity Techniques in Wireless Communication SystemsGurleen Singh RuprahNo ratings yet

- Module 4 PDFDocument33 pagesModule 4 PDFRachnaNo ratings yet

- 18Csc203J:Computer Organization and ArchitectureDocument56 pages18Csc203J:Computer Organization and ArchitectureSENTHIL RNo ratings yet

- Attendance Monitoring Intelligent ClassroomDocument4 pagesAttendance Monitoring Intelligent ClassroompochasrinuvasNo ratings yet

- Final Module 2Document32 pagesFinal Module 2RachnaNo ratings yet

- MTSODocument23 pagesMTSOShreya ShekarNo ratings yet

- Wireless Sensor Networks SyllabusDocument1 pageWireless Sensor Networks Syllabusshabnam.faridi36690% (1)

- Unit Ii: Digital ProtectionDocument55 pagesUnit Ii: Digital ProtectionViswanathanBalajiNo ratings yet

- Biomedical InstrumentationDocument23 pagesBiomedical InstrumentationAdithyaNo ratings yet

- IIR FiltersDocument36 pagesIIR FiltersHari Pillai100% (1)

- Unit-4 PPT. Embedded Systems by SuryaDocument34 pagesUnit-4 PPT. Embedded Systems by SuryaAnonymous 3yqNzCxtTz100% (1)

- OAN551-Sensors and TransducersDocument16 pagesOAN551-Sensors and TransducersPriya Venkadachalam50% (2)

- 4 Point DFT & IdftDocument2 pages4 Point DFT & IdftIshan KapoorNo ratings yet

- WWW - Vidyarthiplus.in: Department of Ece, Adhiparasakthi College of Engineering, KalavaiDocument18 pagesWWW - Vidyarthiplus.in: Department of Ece, Adhiparasakthi College of Engineering, Kalavaisharanyameen2704No ratings yet

- Signals and Systems Model - 1Document2 pagesSignals and Systems Model - 1sharanyameen2704No ratings yet

- Analog and Digital Communication SyllabusDocument3 pagesAnalog and Digital Communication SyllabusSrinivas SamalNo ratings yet

- Module 2 - PPT 4 - Miller Effect and Miller Capacitance and High Frequency Analysis PDFDocument11 pagesModule 2 - PPT 4 - Miller Effect and Miller Capacitance and High Frequency Analysis PDFGokulnath SNo ratings yet

- WSN Notes of Unit-04Document10 pagesWSN Notes of Unit-04akbarnagani13No ratings yet

- Virtual Instrumentation and Traditional InstrumentsDocument5 pagesVirtual Instrumentation and Traditional Instrumentsapi-37251390% (1)

- Digital Lab VIVA QuestionsDocument4 pagesDigital Lab VIVA QuestionsAnirudhan RaviNo ratings yet

- VLSI System Design SyllabusDocument2 pagesVLSI System Design SyllabusGaneshChandraNo ratings yet

- Proposed - BE E & TC 2019 - VLSI SyllabusDocument3 pagesProposed - BE E & TC 2019 - VLSI SyllabusRavindra DabhadeNo ratings yet

- Final Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System DesignDocument11 pagesFinal Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System Designarunbinay04No ratings yet

- Vishwakarma Institute of TechnologyDocument23 pagesVishwakarma Institute of TechnologyEr Shubham RaksheNo ratings yet

- Netherlands ISY HiringDocument4 pagesNetherlands ISY Hiringjitu_4No ratings yet

- 10 Mike BrinsonDocument63 pages10 Mike Brinsonjitu_4No ratings yet

- ANSYS 10nm Entry Into DesignDocument3 pagesANSYS 10nm Entry Into Designjitu_4No ratings yet

- KKKKDocument6 pagesKKKKjitu_4No ratings yet

- E-Admit Card 1001220262: Chinchore Jitendrakumar Balkrushna 13/12/1988Document1 pageE-Admit Card 1001220262: Chinchore Jitendrakumar Balkrushna 13/12/1988jitu_4No ratings yet

- EC ManualDocument3 pagesEC Manualjitu_4No ratings yet

- EC6401 Electronic Circuits II Anna University Question Papers Regulation 2013 Unit WiseDocument7 pagesEC6401 Electronic Circuits II Anna University Question Papers Regulation 2013 Unit WiseDharani KumarNo ratings yet

- Data Sheet - ZXESM R311 Lithium-Ion Battery V2.4 - ENDocument3 pagesData Sheet - ZXESM R311 Lithium-Ion Battery V2.4 - ENWandson LimaNo ratings yet

- Datasheet: AW3859-E-F AW3859-E-FDocument6 pagesDatasheet: AW3859-E-F AW3859-E-FdavidfloresrNo ratings yet

- Top 12 PCB Assembly House in AustriaDocument12 pagesTop 12 PCB Assembly House in AustriajackNo ratings yet

- 6 1Document76 pages6 1pravallikaNo ratings yet

- PCA 6143man PDFDocument102 pagesPCA 6143man PDFLuis Alberto Díaz OlmedoNo ratings yet

- 4003 5100 A-4003-DatasheetDocument2 pages4003 5100 A-4003-Datasheetmar mayoNo ratings yet

- Addis Ababa Ketema Astedader-2Document5 pagesAddis Ababa Ketema Astedader-2Nurye NigusNo ratings yet

- HardwarenotesDocument9 pagesHardwarenotesLakshmi NarayananNo ratings yet

- Digital STXe 60 500 Exciter Transmitter Brochure V1.2Document4 pagesDigital STXe 60 500 Exciter Transmitter Brochure V1.2Edgar MendezNo ratings yet

- APT3200 Manual PDFDocument46 pagesAPT3200 Manual PDFMehmetNo ratings yet

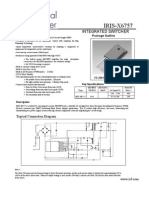

- IRIS-X6757: FeaturesDocument10 pagesIRIS-X6757: Featuresmiguel angel jaramilloNo ratings yet

- Immersionrc Laprf Interface Protocol: Version 1.2, Aug 2017Document2 pagesImmersionrc Laprf Interface Protocol: Version 1.2, Aug 2017dbsi batamNo ratings yet

- Glossary of TermsDocument6 pagesGlossary of TermstinguiblueNo ratings yet

- DHCT C3Document1 pageDHCT C3Mortis BeansNo ratings yet

- Answer KeyDocument2 pagesAnswer KeyLevi Lico PangilinanNo ratings yet

- Introduction To Information TechnologyDocument8 pagesIntroduction To Information TechnologyRegina xuanNo ratings yet

- TL-WR740N (EU) V7 UG 1474248366966cDocument87 pagesTL-WR740N (EU) V7 UG 1474248366966cAndressaIsrael BrittoCarvalhoNo ratings yet

- T5L 400 PR221DS-LS/I in 400 3p F FDocument3 pagesT5L 400 PR221DS-LS/I in 400 3p F FLê Xuân ĐịnhNo ratings yet

- Eaton 93PR 25-75 Datasheet ENDocument2 pagesEaton 93PR 25-75 Datasheet ENPhaniNo ratings yet

- A380 LEVEL III ATA 46 Network Server System Onboard Informati PDFDocument52 pagesA380 LEVEL III ATA 46 Network Server System Onboard Informati PDFDharmeshNo ratings yet

- Art 559Document24 pagesArt 559Ger JimenezNo ratings yet

- Analog Electronics Circuit: Unit 1 Single and Multistage AmplifiersDocument87 pagesAnalog Electronics Circuit: Unit 1 Single and Multistage AmplifiersTripti AgarwalNo ratings yet

- Skype Hacks - by Andrew SheppardDocument858 pagesSkype Hacks - by Andrew SheppardZoroark MichiuNo ratings yet

- Analog To Digital Convertor: PIC18f452Document13 pagesAnalog To Digital Convertor: PIC18f452ranaNo ratings yet

- Installation Procedure For Linux: $sudo LsusbDocument2 pagesInstallation Procedure For Linux: $sudo LsusbRai Kashif JahangirNo ratings yet

- Comparison Methods of Measurements: UNIT-3Document27 pagesComparison Methods of Measurements: UNIT-3jenitaNo ratings yet

- Bowthorpe EMP Remote Surge Monitoring SystemsDocument7 pagesBowthorpe EMP Remote Surge Monitoring Systemsminhbk83No ratings yet

(IIT Guwahati) VLSI Design Verification and Test

(IIT Guwahati) VLSI Design Verification and Test

Uploaded by

jitu_4Original Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

(IIT Guwahati) VLSI Design Verification and Test

(IIT Guwahati) VLSI Design Verification and Test

Uploaded by

jitu_4Copyright:

Available Formats

NPTEL Syllabus

VLSI Design Verification and Test - Web course

COURSE OUTLINE Digital VLSI Design flow comprises three basic phases: Design, Verification and Test. The web course would cover theoretical, implementation and CAD tools pertaining to these three phases. Although there can be individual full courses for each of these phases, the present course aims at covering the important problems/algorithms/tools so that students get a comprehensive idea of the whole digital VLSI design flow. VLSI Design: High level Synthesis, Verilog RTL Design, Combinational and Sequential Synthesis Logic Synthesis (for large circuits). Verification Techniques: Introduction to Hardware Verification and methodologies, Binary Decision Diagrams(BDDs) and algorithms over BDDs. Combinational equivalence checking, Temporal Logics, Modeling sequential systems and model checking, Symbolic model checking. VLSI Testing: Introduction, Fault models, Fault Simulation, Test generation for combinational circuits, Test generation algorithms for sequential circuits and Built in Self test. COURSE DETAIL

NPTEL

http://nptel.iitm.ac.in

Computer Science and Engineering

Pre-requisites: 1. Digital Design 2. Algorithm 3. Automata Theory (Basics) Coordinators: Dr. Santosh Biswas Department of Computer Science and EngineeringIIT Guwahati Prof. Jatindra Kumar Deka Department of Computer Science and EngineeringIIT Guwahati

Title

Sl.No.

Module/Lecture

Design

Introduction

Introduction to Digital VLSI Design Flow Specification, High level Synthesis, RTL Design, Logic Optimization, Verification and Test Planning

Design Representation

Hardware Specific Transformations

II

Scheduling, Allocation and Binding

Problem Specification: Scheduling, Allocation and Binding

Basic Scheduling Algorithms (Time constrained and Resource Constrained)

Allocation Steps: Unit Selection, Functional Unit Binding, Storage Binding, Interconnect Binding

Allocation Techniques: Clique Partitioning, Left-Edge Algorithm, Iterative Refinement.

III

Logic Optimization and Synthesis

Heuristic Minimization of Two-Level Circuits: Espresso

Finite State Machine Synthesis

Multi-Level Logic Synthesis

Multi-Level Minimization

Technology Mapping

Verification

IV

Binary Decision Diagram

Introduction and construction

Reduction rules and Algorithms, ROBDDs

Operation on BDDs and its Algorithms

Representation of Sequential Circuits

Temporal Logic

Introduction and Basic Operators

Syntax and Semantics of LTL, CTL and CLT*

Equivalence and Expressive Power

VI

Model Checking

Introduction to Verification

Specification and Modelling

Model Checking Algorithm

Symbolic Model Checking

Automata and its use in Verification

Automata Theoretic Model Checking

Practical Examples with SMV

Test

VII

Introduction to Digital Testing

Introduction, Test process and Test economics

Functional vs. Structural Testing Defects, Errors, Faults and Fault Modeling (mainly stuck at fault modeling)

Fault Equivalence, Fault Dominance, Fault Collapsing and Checkpoint Theorem

VIII

Fault Simulation and Testability Measures

1-2

Circuit Modeling and Algorithms for Fault Simulation Serial Fault Simulation Parallel Fault Simulation Deductive Fault Simulation Concurrent Fault Simulation

Combinational SCOAP Measures and Sequential SCOAP Measures

IX

Combinational Circuit Test Pattern Generation

Introduction to Automatic Test Pattern Generation (ATPG) and ATPG Algebras

Standard ATPG Algorithms D-Calculus and D-Algorithm Basics of PODEM and FAN

Sequential Circuit Testing and Scan Chains

ATPG for Single-Clock Synchronous Circuits Use of Nine-Valued Logic and Time-Frame Expansion Methods

Complexity of Sequential ATPG

2-3

Scan Chain based Sequential Circuit Testing Scan Cell Design Design variations of Scan Chains Sequential Testing based on Scan Chains Overheads of Scan Design Partial-Scan Design

XI

Built in Self test (BIST)

Introduction to BIST architecture BIST Test Pattern Generation, Response Compaction and Response Analysis

2-3

Memory BIST March Test BIST with MISR Neighborhood Pattern Sensitive Fault Test Transparent Memory BIST

References: 1. D. D. Gajski, N. D. Dutt, A.C.-H. Wu and S.Y.-L. Lin, High-Level Synthesis: Introduction to Chip and System Design, Springer, 1st edition, 1992. 2. S. Palnitkar, Verilog HDL: A Guide to Digital Design and Synthesis, Prentice Hall, 2nd edition, 2003. 3. G. De Micheli. Synthesis and optimization of digital circuits, 1st edition, 1994. 4. M. Huth and M. Ryan, Logic in Computer Science modeling and reasoning about systems, Cambridge University Press, 2nd Edition, 2004. 5. Bushnell and Agrawal, Essentials of Electronic Testing for Digital, Memory & Mixed-Signal Circuits, Kluwer Academic Publishers, 2000.

A joint venture by IISc and IITs, funded by MHRD, Govt of India http://nptel.iitm.ac.in

You might also like

- 523-0775579-003117 3ed Collins - 85C - EFIS - ManualDocument161 pages523-0775579-003117 3ed Collins - 85C - EFIS - Manualfiskit100% (5)

- Heathkit Schematic and Manual Archive InDICE PDFDocument30 pagesHeathkit Schematic and Manual Archive InDICE PDFGautam Balhara33% (6)

- DSP QuestionsDocument46 pagesDSP QuestionsAnonymous tLOxgFkyNo ratings yet

- A-Law and U-Law CompandingDocument4 pagesA-Law and U-Law CompandingAchyut Dev50% (2)

- Chapter 3 Part 1 Sensor and TransducersDocument48 pagesChapter 3 Part 1 Sensor and TransducersFikadu Eshetu100% (1)

- ECE 027 - Module 1 - Introduction About Semiconductor DiodesDocument54 pagesECE 027 - Module 1 - Introduction About Semiconductor DiodesMiyuki NakiriNo ratings yet

- Embedded System LESSONPLANDocument7 pagesEmbedded System LESSONPLANgallantprakashNo ratings yet

- Digital Integrated Circuits: A Design PerspectiveDocument78 pagesDigital Integrated Circuits: A Design Perspectiveapi-127299018No ratings yet

- WDC Question Bank 2018Document8 pagesWDC Question Bank 2018Aadharsh HariharanNo ratings yet

- Ofdm ProblemsDocument3 pagesOfdm ProblemsmohanshapuramNo ratings yet

- Chapter 12 Wireless Sensor Networks: From Reference Book: Adhoc Wireless Networks By: B.S. ManojDocument42 pagesChapter 12 Wireless Sensor Networks: From Reference Book: Adhoc Wireless Networks By: B.S. ManojMounisha g bNo ratings yet

- Unit 3 - WSN - MACDocument22 pagesUnit 3 - WSN - MACRmkumarsNo ratings yet

- Experiment No. 5 Darlington Pair Connection: (CITATION Ele /L 1033)Document4 pagesExperiment No. 5 Darlington Pair Connection: (CITATION Ele /L 1033)Dan BautistaNo ratings yet

- MPMC Lab ManualDocument157 pagesMPMC Lab ManualSanmuga SundaramNo ratings yet

- Chapter 1 Introduction To Robotics PDFDocument10 pagesChapter 1 Introduction To Robotics PDFOmar AL JabaiNo ratings yet

- Microprocessors & Interfacing Techniques Assignment No. 2Document2 pagesMicroprocessors & Interfacing Techniques Assignment No. 2Abdullah Nasir100% (4)

- EC8701-Antenna and Microwave EngineeringDocument12 pagesEC8701-Antenna and Microwave EngineeringsureshvkumarNo ratings yet

- Cyclotron Angular Frequency, Problems On Magnetron: Microwave Crossed-Field Tubes: 03/12/2020 & 10:00 AM-11:00 AMDocument18 pagesCyclotron Angular Frequency, Problems On Magnetron: Microwave Crossed-Field Tubes: 03/12/2020 & 10:00 AM-11:00 AMravi kiranNo ratings yet

- Assignment Digital CommunicationDocument8 pagesAssignment Digital CommunicationAkash SharmaNo ratings yet

- Laser MetrologyDocument41 pagesLaser MetrologyjennybunnyomgNo ratings yet

- Dcom Mod4Document4 pagesDcom Mod4Vidit shahNo ratings yet

- Value Added CourseDocument4 pagesValue Added CourseSuresh VaruvelNo ratings yet

- CU7008-Ultra Wideband CommunicationDocument16 pagesCU7008-Ultra Wideband CommunicationSaad100% (2)

- Ece-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentDocument9 pagesEce-Vii-dsp Algorithms & Architecture (10ec751) - AssignmentMuhammadMansoorGohar100% (1)

- Bluetooth Based Smart Sensor NetworksDocument17 pagesBluetooth Based Smart Sensor NetworksEmjay ParkerNo ratings yet

- Cec355 - SDR Model QN Set IiDocument2 pagesCec355 - SDR Model QN Set Iivenki08No ratings yet

- Adaptive Signal ProcessingDocument24 pagesAdaptive Signal Processinganilshaw27No ratings yet

- Timer and CounterDocument30 pagesTimer and Countercleopatra2121No ratings yet

- Signals & Systems QBDocument18 pagesSignals & Systems QBAnonymous Ndsvh2soNo ratings yet

- Heart Attack Detection and Heart Rate Monitoring Using Iot: - Guided by - Presented byDocument6 pagesHeart Attack Detection and Heart Rate Monitoring Using Iot: - Guided by - Presented byBrightworld ProjectsNo ratings yet

- CU5191-Advanced Radiation SystemsDocument15 pagesCU5191-Advanced Radiation SystemsSaad0% (1)

- Rectangular WaveguideDocument5 pagesRectangular WaveguideSarveenaNo ratings yet

- Electronic Devices Lab MANUALDocument24 pagesElectronic Devices Lab MANUALna_hariprsadNo ratings yet

- Satellite Communication Unit 4Document16 pagesSatellite Communication Unit 4deepthiNo ratings yet

- Course Notes Advanced DSPDocument122 pagesCourse Notes Advanced DSPAnonymous hDKqasfNo ratings yet

- FeedCon (Unit 1)Document10 pagesFeedCon (Unit 1)Melissa LindayagNo ratings yet

- BAN U-1Document18 pagesBAN U-1kathiresanaembhithi100% (1)

- Aeronautical CommunicationsDocument18 pagesAeronautical CommunicationsBibinMathewNo ratings yet

- Diversity Techniques in Wireless Communication SystemsDocument30 pagesDiversity Techniques in Wireless Communication SystemsGurleen Singh RuprahNo ratings yet

- Module 4 PDFDocument33 pagesModule 4 PDFRachnaNo ratings yet

- 18Csc203J:Computer Organization and ArchitectureDocument56 pages18Csc203J:Computer Organization and ArchitectureSENTHIL RNo ratings yet

- Attendance Monitoring Intelligent ClassroomDocument4 pagesAttendance Monitoring Intelligent ClassroompochasrinuvasNo ratings yet

- Final Module 2Document32 pagesFinal Module 2RachnaNo ratings yet

- MTSODocument23 pagesMTSOShreya ShekarNo ratings yet

- Wireless Sensor Networks SyllabusDocument1 pageWireless Sensor Networks Syllabusshabnam.faridi36690% (1)

- Unit Ii: Digital ProtectionDocument55 pagesUnit Ii: Digital ProtectionViswanathanBalajiNo ratings yet

- Biomedical InstrumentationDocument23 pagesBiomedical InstrumentationAdithyaNo ratings yet

- IIR FiltersDocument36 pagesIIR FiltersHari Pillai100% (1)

- Unit-4 PPT. Embedded Systems by SuryaDocument34 pagesUnit-4 PPT. Embedded Systems by SuryaAnonymous 3yqNzCxtTz100% (1)

- OAN551-Sensors and TransducersDocument16 pagesOAN551-Sensors and TransducersPriya Venkadachalam50% (2)

- 4 Point DFT & IdftDocument2 pages4 Point DFT & IdftIshan KapoorNo ratings yet

- WWW - Vidyarthiplus.in: Department of Ece, Adhiparasakthi College of Engineering, KalavaiDocument18 pagesWWW - Vidyarthiplus.in: Department of Ece, Adhiparasakthi College of Engineering, Kalavaisharanyameen2704No ratings yet

- Signals and Systems Model - 1Document2 pagesSignals and Systems Model - 1sharanyameen2704No ratings yet

- Analog and Digital Communication SyllabusDocument3 pagesAnalog and Digital Communication SyllabusSrinivas SamalNo ratings yet

- Module 2 - PPT 4 - Miller Effect and Miller Capacitance and High Frequency Analysis PDFDocument11 pagesModule 2 - PPT 4 - Miller Effect and Miller Capacitance and High Frequency Analysis PDFGokulnath SNo ratings yet

- WSN Notes of Unit-04Document10 pagesWSN Notes of Unit-04akbarnagani13No ratings yet

- Virtual Instrumentation and Traditional InstrumentsDocument5 pagesVirtual Instrumentation and Traditional Instrumentsapi-37251390% (1)

- Digital Lab VIVA QuestionsDocument4 pagesDigital Lab VIVA QuestionsAnirudhan RaviNo ratings yet

- VLSI System Design SyllabusDocument2 pagesVLSI System Design SyllabusGaneshChandraNo ratings yet

- Proposed - BE E & TC 2019 - VLSI SyllabusDocument3 pagesProposed - BE E & TC 2019 - VLSI SyllabusRavindra DabhadeNo ratings yet

- Final Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System DesignDocument11 pagesFinal Updated New Syllabus Mtech BPUT 2009-10 VLSI Embeded System Designarunbinay04No ratings yet

- Vishwakarma Institute of TechnologyDocument23 pagesVishwakarma Institute of TechnologyEr Shubham RaksheNo ratings yet

- Netherlands ISY HiringDocument4 pagesNetherlands ISY Hiringjitu_4No ratings yet

- 10 Mike BrinsonDocument63 pages10 Mike Brinsonjitu_4No ratings yet

- ANSYS 10nm Entry Into DesignDocument3 pagesANSYS 10nm Entry Into Designjitu_4No ratings yet

- KKKKDocument6 pagesKKKKjitu_4No ratings yet

- E-Admit Card 1001220262: Chinchore Jitendrakumar Balkrushna 13/12/1988Document1 pageE-Admit Card 1001220262: Chinchore Jitendrakumar Balkrushna 13/12/1988jitu_4No ratings yet

- EC ManualDocument3 pagesEC Manualjitu_4No ratings yet

- EC6401 Electronic Circuits II Anna University Question Papers Regulation 2013 Unit WiseDocument7 pagesEC6401 Electronic Circuits II Anna University Question Papers Regulation 2013 Unit WiseDharani KumarNo ratings yet

- Data Sheet - ZXESM R311 Lithium-Ion Battery V2.4 - ENDocument3 pagesData Sheet - ZXESM R311 Lithium-Ion Battery V2.4 - ENWandson LimaNo ratings yet

- Datasheet: AW3859-E-F AW3859-E-FDocument6 pagesDatasheet: AW3859-E-F AW3859-E-FdavidfloresrNo ratings yet

- Top 12 PCB Assembly House in AustriaDocument12 pagesTop 12 PCB Assembly House in AustriajackNo ratings yet

- 6 1Document76 pages6 1pravallikaNo ratings yet

- PCA 6143man PDFDocument102 pagesPCA 6143man PDFLuis Alberto Díaz OlmedoNo ratings yet

- 4003 5100 A-4003-DatasheetDocument2 pages4003 5100 A-4003-Datasheetmar mayoNo ratings yet

- Addis Ababa Ketema Astedader-2Document5 pagesAddis Ababa Ketema Astedader-2Nurye NigusNo ratings yet

- HardwarenotesDocument9 pagesHardwarenotesLakshmi NarayananNo ratings yet

- Digital STXe 60 500 Exciter Transmitter Brochure V1.2Document4 pagesDigital STXe 60 500 Exciter Transmitter Brochure V1.2Edgar MendezNo ratings yet

- APT3200 Manual PDFDocument46 pagesAPT3200 Manual PDFMehmetNo ratings yet

- IRIS-X6757: FeaturesDocument10 pagesIRIS-X6757: Featuresmiguel angel jaramilloNo ratings yet

- Immersionrc Laprf Interface Protocol: Version 1.2, Aug 2017Document2 pagesImmersionrc Laprf Interface Protocol: Version 1.2, Aug 2017dbsi batamNo ratings yet

- Glossary of TermsDocument6 pagesGlossary of TermstinguiblueNo ratings yet

- DHCT C3Document1 pageDHCT C3Mortis BeansNo ratings yet

- Answer KeyDocument2 pagesAnswer KeyLevi Lico PangilinanNo ratings yet

- Introduction To Information TechnologyDocument8 pagesIntroduction To Information TechnologyRegina xuanNo ratings yet

- TL-WR740N (EU) V7 UG 1474248366966cDocument87 pagesTL-WR740N (EU) V7 UG 1474248366966cAndressaIsrael BrittoCarvalhoNo ratings yet

- T5L 400 PR221DS-LS/I in 400 3p F FDocument3 pagesT5L 400 PR221DS-LS/I in 400 3p F FLê Xuân ĐịnhNo ratings yet

- Eaton 93PR 25-75 Datasheet ENDocument2 pagesEaton 93PR 25-75 Datasheet ENPhaniNo ratings yet

- A380 LEVEL III ATA 46 Network Server System Onboard Informati PDFDocument52 pagesA380 LEVEL III ATA 46 Network Server System Onboard Informati PDFDharmeshNo ratings yet

- Art 559Document24 pagesArt 559Ger JimenezNo ratings yet

- Analog Electronics Circuit: Unit 1 Single and Multistage AmplifiersDocument87 pagesAnalog Electronics Circuit: Unit 1 Single and Multistage AmplifiersTripti AgarwalNo ratings yet

- Skype Hacks - by Andrew SheppardDocument858 pagesSkype Hacks - by Andrew SheppardZoroark MichiuNo ratings yet

- Analog To Digital Convertor: PIC18f452Document13 pagesAnalog To Digital Convertor: PIC18f452ranaNo ratings yet

- Installation Procedure For Linux: $sudo LsusbDocument2 pagesInstallation Procedure For Linux: $sudo LsusbRai Kashif JahangirNo ratings yet

- Comparison Methods of Measurements: UNIT-3Document27 pagesComparison Methods of Measurements: UNIT-3jenitaNo ratings yet

- Bowthorpe EMP Remote Surge Monitoring SystemsDocument7 pagesBowthorpe EMP Remote Surge Monitoring Systemsminhbk83No ratings yet