Professional Documents

Culture Documents

Advanced Topics in Logic Design Final Exam

Advanced Topics in Logic Design Final Exam

Uploaded by

محسن محمد محروسCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Advanced Topics in Logic Design Final Exam

Advanced Topics in Logic Design Final Exam

Uploaded by

محسن محمد محروسCopyright:

Available Formats

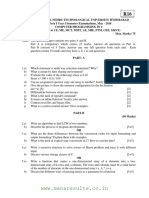

Cairo University Faculty of Engineering

Department of Electronics and Electrical Communications Engineering

Advanced Topics in Logic Design

Fourth Year 2012/2013 - Term 1 Final Exam January 2013 2 Hours

Attempt ALL Questions

Question 1 Boolean Function Decomposition & Boolean SAT a. [2 marks] Write the general expression for the Shannon Function Decomposition of a Boolean function f of n Boolean variables x1, x2, ., xn about the splitting variable xi, where 1 i n, in terms of its positive and negative cofactors with respect to xi. b. [2 marks] Show that the Boolean function given in part (a) is independent of xi if its positive and negative cofactors with respect to xi are logically equivalent. c. [3 marks] Show that the Boolean function given in part (a) is negative unate with respect to xi if all minterms in its positive cofactor with respect to xi are also minterms of its negative cofactor with respect to xi, and the positive and negative cofactors with respect to xi are not logically equivalent. d. [3 marks] If the universal quantification of the Boolean function given in part (a) with respect to xi is found to be unsatisfiable, can there exist a product term in any SOP of the function that does not contain either the positive or negative literal of xi? Explain the reason, and give an example to illustrate the answer. e. [5 marks] Use Davis-Logemann-Loveland Depth-First Search Algorithm to solve the following SAT problem: (x1 + x3) (x2 + x3) (x1 + x4) (x2 + x4) (x1 + x3 + x4) (x1 + x2 + x4). Question 2 Boolean Matching a. [3 marks] Write an expression for the total number of mappings that can be considered when attempting to find a possible matching for a pair of Boolean functions in terms of the number of Boolean variables of the functions n. Can a pair of Boolean functions be matched if they have different number of variables? What are the drawbacks of the Canonical Boolean Matching algorithms based on truth tables and table lookup? b. [4 marks] Compute the Unateness and the Size of the Onset signatures of the pair of Boolean functions f = x1 x3 + x2 + x1x3 and g = y1y2 y3 + y1 y2y3. c. [3 marks] Find a possible matching for the two functions given in part (b) if it exists.

Page 1 /3

Question 3 Logic Optimization a. [4 marks] Explain how to check whether cube C in cover F of the Boolean function f is either redundant or irredundant. Illustrate that by checking whether the cube C = x1 x3 in the following cover F = {x1 x2, x2 x4, x3 x4, x1 x3, x2 x3} is redundant or irredundant. b. [6 marks] Illustrate how the Quine-McClosky procedure is applied to generate all prime cubes of the Boolean function f whose on-set is given by the cover F = {x1 x2 x4, x2 x3 x4} and dont care set is given by the cover D = {x1 x2, x2 x4}. Write the covering table of the function and show how it is used to generate the minimum-size cover. c. [5 marks] Illustrate how the minimum column cover is used to generate the complement of the unate Boolean function f = x1 x3 + x2 x4 + x1 x4 + x2 x3.

Question 4 ROBDD a. [2 marks] Explain the tradeoff between using canonical data structures such as truth tables and binary decision diagrams and non-canonical data structures such as covers to represent Boolean functions. b. [4 marks] Explain how the if-then-else (ITE) operator is used to build a reduced-ordered binary decision diagram representation of a Boolean function f. Illustrate that by sketching the ROBDD representation of a 2-input NOR Boolean function. c. [4 marks] Show that the ROBDD representation of an n-input XOR Boolean function has n levels and (2n-1) nodes. Illustrate how the onset of the 4-input XOR Boolean function is generated from its ROBDD representation.

Question 5 AIG a. [2 mark] Use De Morgans law to design an AIG with the minimum number of levels for a 4 -input OR gate. b. [4 marks] Construct an AIG representation with the minimum number of level for a 42 encoder. c. [4 marks] Show how construct an AIG representation for a 5-input majority encoder.

Question 6 Logic Difference & Incremental Synthesis a. [4 marks] Describe the main phases of the DeltaSyn incremental synthesis techniques used to minimize the logic difference between an original design and the desired design modified by Engineering Change Orders CEO.

Page 2 /3

b. [6 marks] Illustrate how the DeltaSyn technique is applied to minimize the logic difference between the desired output y and the original model y* whose schematics are given in the following Figure.

Page 3 /3

You might also like

- MATH1005 Final Exam 2022Document17 pagesMATH1005 Final Exam 2022Spamy SpamNo ratings yet

- Calculus by Feliciano UyDocument83 pagesCalculus by Feliciano UyAndreana Amor76% (21)

- Multiply Whole Numbers: InvestigateDocument44 pagesMultiply Whole Numbers: InvestigateShahla Ali100% (1)

- WWW - Manaresults.Co - In: (Common To CSE, IT)Document2 pagesWWW - Manaresults.Co - In: (Common To CSE, IT)Sajjad KhanNo ratings yet

- Isc Specimen Paper Computer Science Paper 1 (Theory)Document7 pagesIsc Specimen Paper Computer Science Paper 1 (Theory)ShadowerNo ratings yet

- S.S.S. SAMITI's S.A.M. D. Higher Secondary School of ScienceDocument5 pagesS.S.S. SAMITI's S.A.M. D. Higher Secondary School of ScienceSUPRIYA BHAGATNo ratings yet

- EC2203 Digital Electronics Question BankDocument16 pagesEC2203 Digital Electronics Question BankSophiaKaviNo ratings yet

- Computer Science XII ISC Sample PaperDocument9 pagesComputer Science XII ISC Sample PaperAkshay PandeyNo ratings yet

- Fourth Semester B.E Degree Examination (Common To CS and IS) Model Question Paper I 06CS43 Analysis and Design of AlgorithmsDocument4 pagesFourth Semester B.E Degree Examination (Common To CS and IS) Model Question Paper I 06CS43 Analysis and Design of AlgorithmsMohnish RajuNo ratings yet

- WWW - Manaresults.Co - In: (Common To CSE, IT)Document2 pagesWWW - Manaresults.Co - In: (Common To CSE, IT)Suresh ThallapelliNo ratings yet

- Second Semester Examinations 2017/2018: Answer FOUR QuestionsDocument6 pagesSecond Semester Examinations 2017/2018: Answer FOUR Questionshussein hammoudNo ratings yet

- ISC Computer Science Question Paper 2016 Solved For Class 12 - A Plus Topper 3Document1 pageISC Computer Science Question Paper 2016 Solved For Class 12 - A Plus Topper 3samm guptaNo ratings yet

- Computer Archtecture&organisation Assignment-DegreeDocument3 pagesComputer Archtecture&organisation Assignment-DegreeJharon MMNo ratings yet

- Second Semester Examinations 2016/2017: Answer FOUR QuestionsDocument6 pagesSecond Semester Examinations 2016/2017: Answer FOUR Questionshussein hammoudNo ratings yet

- Logic Design June 2010 ESDocument2 pagesLogic Design June 2010 ESPrasad C MNo ratings yet

- 3SFE618 Formal Methods 2009Document18 pages3SFE618 Formal Methods 2009Hasini PereraNo ratings yet

- ISC 2005 Computer Science Paper 1 TheoryDocument6 pagesISC 2005 Computer Science Paper 1 TheoryShadowerNo ratings yet

- 3SFE618 Formal Methods 2007Document17 pages3SFE618 Formal Methods 2007Hasini PereraNo ratings yet

- L-2/T-Licse Date: 08/08/2017: - 'Ds (Jia)Document22 pagesL-2/T-Licse Date: 08/08/2017: - 'Ds (Jia)Na ThakaNo ratings yet

- Ds Solved 2021-22Document54 pagesDs Solved 2021-22avanitiwari048No ratings yet

- Sample Questions For Exam: Select Correct Answers. You Can Copy and Paste ' Beside The Answer You SelectDocument8 pagesSample Questions For Exam: Select Correct Answers. You Can Copy and Paste ' Beside The Answer You SelectKi KiNo ratings yet

- Ael Zg554 Ec-2r First Sem 2023-2024Document5 pagesAel Zg554 Ec-2r First Sem 2023-2024Charan EswarNo ratings yet

- EEC 605 VLSI CAD Final Exam 1436-1437 Term 1 Cairo UniversityDocument3 pagesEEC 605 VLSI CAD Final Exam 1436-1437 Term 1 Cairo UniversityMohsenMahroosNo ratings yet

- Design and Analysis of Algorithms - May-2013 PDFDocument4 pagesDesign and Analysis of Algorithms - May-2013 PDFNagababu PachhalaNo ratings yet

- MarchApril 2023Document2 pagesMarchApril 2023maamamun4000No ratings yet

- DPSDDocument16 pagesDPSDDhilip PrabakaranNo ratings yet

- Nov 11Document2 pagesNov 11ashwani_yadav85No ratings yet

- Master of Computer Applications (MCA) : Assignments JANUARY 2012Document14 pagesMaster of Computer Applications (MCA) : Assignments JANUARY 2012Subramanyam PillalamarriNo ratings yet

- Computer Science PaperDocument8 pagesComputer Science PaperAsh UrlopeNo ratings yet

- ISC Computer Science - Official Specimen Paper 2013Document9 pagesISC Computer Science - Official Specimen Paper 2013Guide For SchoolNo ratings yet

- 3 07 Paper IiiDocument5 pages3 07 Paper IiiKampa LavanyaNo ratings yet

- Compiler Design Final Question BankDocument5 pagesCompiler Design Final Question BanksravaniNo ratings yet

- Question Bank: B.Tech Iii Year - I Sem (R17) (2019-20)Document32 pagesQuestion Bank: B.Tech Iii Year - I Sem (R17) (2019-20)Banoth PavanNo ratings yet

- Model Question PaperDocument12 pagesModel Question PaperASHOKNo ratings yet

- Computer Science Tripos Part IDocument10 pagesComputer Science Tripos Part IHuxNo ratings yet

- CompreDocument2 pagesComprepranavjibhakateNo ratings yet

- 23 November 2010, 9:00 Am - 12 Noon: CS101 Computational Engineering Final ExamDocument8 pages23 November 2010, 9:00 Am - 12 Noon: CS101 Computational Engineering Final ExamKaustubh MallikNo ratings yet

- Final ExaminationDocument3 pagesFinal ExaminationLinah RoseNo ratings yet

- SEMESTER I, 20152016 MidtermDocument6 pagesSEMESTER I, 20152016 Midtermকফি ওয়ান টুNo ratings yet

- Design and Analysis of Algorithms (Cse-It) - May-2014Document5 pagesDesign and Analysis of Algorithms (Cse-It) - May-2014Nagababu PachhalaNo ratings yet

- BCA I I Digital SystemDocument4 pagesBCA I I Digital SystemAmory Sabri AsmaroNo ratings yet

- Department of EceDocument8 pagesDepartment of Ecerajendr_46No ratings yet

- ECS305 (OOS) 2nd SessionalDocument3 pagesECS305 (OOS) 2nd SessionalAshutosh SinghNo ratings yet

- DAA - SET 1 May 2016Document2 pagesDAA - SET 1 May 2016Anurag PatnaikuniNo ratings yet

- ProgrammingDocument10 pagesProgrammingAshvin GraceNo ratings yet

- Question Bank Iii Semester BtechDocument18 pagesQuestion Bank Iii Semester BtechHarold WilsonNo ratings yet

- CS467 ADocument3 pagesCS467 AE3 TechNo ratings yet

- 9A05403 Design & Analysis of AlgorithmsDocument4 pages9A05403 Design & Analysis of AlgorithmssivabharathamurthyNo ratings yet

- Answer All Questions, Each Carries 4 MarksDocument3 pagesAnswer All Questions, Each Carries 4 MarksKarthikaNo ratings yet

- 131 Ad 052018Document2 pages131 Ad 052018vrkoradaNo ratings yet

- Class 9 Computers MM-100Document3 pagesClass 9 Computers MM-100xagal74444No ratings yet

- 1-2 r13 Aug 2014 Q.PDocument96 pages1-2 r13 Aug 2014 Q.PGajula SureshNo ratings yet

- Question-Regular-Cs205 Data Structures (CS, It), December 2017Document2 pagesQuestion-Regular-Cs205 Data Structures (CS, It), December 2017For FunNo ratings yet

- The Bcs Professional Examinations BCS Level 5 Diploma in IT: The British Computer SocietyDocument4 pagesThe Bcs Professional Examinations BCS Level 5 Diploma in IT: The British Computer SocietyOzioma IhekwoabaNo ratings yet

- Graded Assignment 1 - Questions - StudentDocument4 pagesGraded Assignment 1 - Questions - StudentDane SinclairNo ratings yet

- IT 340-Programming Language Design Concepts7Document7 pagesIT 340-Programming Language Design Concepts7jathurshanm3No ratings yet

- Applied RVE Reconstruction and Homogenization of Heterogeneous MaterialsFrom EverandApplied RVE Reconstruction and Homogenization of Heterogeneous MaterialsNo ratings yet

- Multidisciplinary Design Optimization Supported by Knowledge Based EngineeringFrom EverandMultidisciplinary Design Optimization Supported by Knowledge Based EngineeringNo ratings yet

- 12.jee Main Sure Gtm-1 With Detailed Solutions-Pages-2-8Document7 pages12.jee Main Sure Gtm-1 With Detailed Solutions-Pages-2-8Kalyan ReddtNo ratings yet

- Section 1: Roots and Coefficients: Edexcel AS Further Maths Roots of PolynomialsDocument3 pagesSection 1: Roots and Coefficients: Edexcel AS Further Maths Roots of PolynomialsChung Man HoNo ratings yet

- State Observer (Estimator)Document18 pagesState Observer (Estimator)Shahrukh GillNo ratings yet

- Asna NotesDocument95 pagesAsna NotesHumbang PurbaNo ratings yet

- Stat Summative TestDocument8 pagesStat Summative Testbonifacio gianga jr100% (1)

- Mean and Random VariableDocument4 pagesMean and Random VariabledfgftjhfjsNo ratings yet

- Java Code Lab)Document3 pagesJava Code Lab)peace_edafeNo ratings yet

- Basic Maths New-EnglishDocument7 pagesBasic Maths New-EnglishchandimaNo ratings yet

- G11 Genmath Performance TaskDocument4 pagesG11 Genmath Performance TaskDennis AquinoNo ratings yet

- All About You AssignmentDocument3 pagesAll About You AssignmentPeter KimNo ratings yet

- Semi Detailed Lesson PlanDocument3 pagesSemi Detailed Lesson PlanRayne CruzNo ratings yet

- Factoring Polynomials GCF PDFDocument2 pagesFactoring Polynomials GCF PDFNamsangNo ratings yet

- Asset-V1 MITx+6.86x+3T2020+typeasset+blockslides Lecture6 CompressedDocument22 pagesAsset-V1 MITx+6.86x+3T2020+typeasset+blockslides Lecture6 CompressedRahul VasanthNo ratings yet

- Chapter 1 Number SystemDocument48 pagesChapter 1 Number SystemShaoor ParachaNo ratings yet

- Lambert W-Function Revisited - Applications in ScienceDocument12 pagesLambert W-Function Revisited - Applications in ScienceLuan OzelimNo ratings yet

- MR Lai Add Maths NotesDocument10 pagesMR Lai Add Maths Notesteng fsNo ratings yet

- Đề Sở Vĩnh Phúc + Đáp ÁnDocument6 pagesĐề Sở Vĩnh Phúc + Đáp ÁnChâu Bảo HânNo ratings yet

- A Matrix Is A Rectangular Array of Elements Arranged in Horizontal and Vertical ColumnsDocument83 pagesA Matrix Is A Rectangular Array of Elements Arranged in Horizontal and Vertical ColumnsvaibhavNo ratings yet

- DLL-Aug 1-5, 2016Document3 pagesDLL-Aug 1-5, 2016Hanna FerNo ratings yet

- Awers Af34125Document1 pageAwers Af34125kingofpaladinsNo ratings yet

- Uzawa - Walras's Existence Theorem and Brower's Fixed Point Theorem PaperDocument4 pagesUzawa - Walras's Existence Theorem and Brower's Fixed Point Theorem PaperMauro MLRNo ratings yet

- IMO 2015 ShorlistDocument7 pagesIMO 2015 ShorlistAxelNo ratings yet

- B.sc. MathematicsDocument72 pagesB.sc. MathematicsAthul Ks100% (2)

- GMM Var StataDocument27 pagesGMM Var StataChahine BergaouiNo ratings yet

- Ebook Dbm10063 Basic AlgebraDocument57 pagesEbook Dbm10063 Basic Algebrakancil orangeNo ratings yet

- Mat495 Chapter 5Document10 pagesMat495 Chapter 5MuhamadSadiqNo ratings yet

- CBSE Study Material For Class 10Document6 pagesCBSE Study Material For Class 10techt0n1c0% (1)