Professional Documents

Culture Documents

Digital Microelectronic Digital Microelectronic Circuits Circuits ( (

Digital Microelectronic Digital Microelectronic Circuits Circuits ( (

Uploaded by

Gowtham HariCopyright:

Available Formats

You might also like

- Cmos Inverter CharacteristicsDocument5 pagesCmos Inverter CharacteristicsRichu Jose CyriacNo ratings yet

- Group4 EECS511 Huang&SuDocument5 pagesGroup4 EECS511 Huang&SuDivya ReddyNo ratings yet

- Disjuntor Andeli AW45Document7 pagesDisjuntor Andeli AW45hudsonNo ratings yet

- Ricoh MP C300 SchematicsDocument18 pagesRicoh MP C300 Schematicsluissilvaleiria100% (1)

- Dasherkandi Sewage Treatment Plant Project, 500MLD: Cable StudyDocument16 pagesDasherkandi Sewage Treatment Plant Project, 500MLD: Cable StudyআসিফহাসানখানNo ratings yet

- Cad Lab ManualDocument15 pagesCad Lab ManualSougata Ghosh100% (2)

- Bicmos Logic GatesDocument25 pagesBicmos Logic GatesRavi Chandra KumarNo ratings yet

- EE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignDocument39 pagesEE5518 VLSI Digital Circuit Design VLSI Digital Circuit DesignBharat Kumar100% (1)

- 1.3 CMOS-Inverter-DC-CharacteristicsDocument34 pages1.3 CMOS-Inverter-DC-Characteristicssreemurarik756No ratings yet

- CMOS InverterDocument16 pagesCMOS Invertersreekanthreddy peramNo ratings yet

- EE4271 VLSI Design: The InverterDocument32 pagesEE4271 VLSI Design: The Inverterprakash_shrNo ratings yet

- Pass Gate Logic: Switch NetworkDocument34 pagesPass Gate Logic: Switch NetworkSunil SharmaNo ratings yet

- Vlsi l4 Static Cmos InvDocument26 pagesVlsi l4 Static Cmos InvSuriya SkariahNo ratings yet

- Lect12 InverterDocument17 pagesLect12 InverterVimala PriyaNo ratings yet

- Resonant&Buck ChopperDocument18 pagesResonant&Buck ChopperKata Naresh BabuNo ratings yet

- Materials and Methodology: IntrductionDocument15 pagesMaterials and Methodology: Intrductionmosub fudolNo ratings yet

- Calculation of Power Losses For MMC-based VSC HVDC StationsDocument10 pagesCalculation of Power Losses For MMC-based VSC HVDC StationshumudsaidNo ratings yet

- Sepic Converter Design and Operation: by Gregory SharpDocument21 pagesSepic Converter Design and Operation: by Gregory SharpSingam SridharNo ratings yet

- DPM 1as-BlDocument4 pagesDPM 1as-BlNarendra BholeNo ratings yet

- ECA-Labmanual BookDocument56 pagesECA-Labmanual BookL Hari Venkatesh100% (2)

- ECE124A F11 HW5 SolutionsDocument4 pagesECE124A F11 HW5 SolutionsPeter VerlangieriNo ratings yet

- CAD LAbDocument27 pagesCAD LAbSuraj KamyaNo ratings yet

- Reset Circuits Slave MicroDocument8 pagesReset Circuits Slave MicroAntonioNo ratings yet

- Lab10 2011Document5 pagesLab10 2011Venkat RamananNo ratings yet

- I. Instructional Objectives: D S G D GDocument4 pagesI. Instructional Objectives: D S G D Gcokelat_kNo ratings yet

- Combination Logic Design: Pradondet Nilagupta Pom@ku - Ac.th Department of Computer Engineering Kasetsart UniversityDocument78 pagesCombination Logic Design: Pradondet Nilagupta Pom@ku - Ac.th Department of Computer Engineering Kasetsart UniversitybhawnaNo ratings yet

- EE 2.3: Semiconductor Modelling in SPICE Course Homepage:: SPICE Diode and BJT ModelsDocument34 pagesEE 2.3: Semiconductor Modelling in SPICE Course Homepage:: SPICE Diode and BJT ModelsKathir ChandraboseNo ratings yet

- References: (Used For Creation of The Presentation Material)Document35 pagesReferences: (Used For Creation of The Presentation Material)Kumar BsnspNo ratings yet

- Oversampled Dead-Beat Current Controller for Voltage Source ConvertersDocument8 pagesOversampled Dead-Beat Current Controller for Voltage Source ConvertersirmascirubbettaNo ratings yet

- 3.design of Automated Smart Home For Smart CityDocument110 pages3.design of Automated Smart Home For Smart Citysyed nemath miyaNo ratings yet

- Dynamic Logic CircuitsDocument61 pagesDynamic Logic Circuitsbirla_sNo ratings yet

- A 270-Ma Self-Calibrating-Clocked Output-Capacitor-Free LDO With 0.151.15V Output Range and 0.183-fs FoMDocument12 pagesA 270-Ma Self-Calibrating-Clocked Output-Capacitor-Free LDO With 0.151.15V Output Range and 0.183-fs FoMVani YamaniNo ratings yet

- Digital Power-Conversion For The Analog EngineerDocument12 pagesDigital Power-Conversion For The Analog EngineerfjwoemcuNo ratings yet

- Design and Implementation of 1 GHZ Current Starved Voltage Controlled Oscillator (Vco) For PLL Using 90Nm Cmos TechnologyDocument6 pagesDesign and Implementation of 1 GHZ Current Starved Voltage Controlled Oscillator (Vco) For PLL Using 90Nm Cmos Technologyanon_7010885870% (1)

- Chap7 Cmos Inverter PrincipleDocument54 pagesChap7 Cmos Inverter PrinciplebhawnaNo ratings yet

- HW DesignDocument16 pagesHW DesignharshaNo ratings yet

- Csce 3303 - Fundamental MicroelectronicsDocument16 pagesCsce 3303 - Fundamental MicroelectronicsSameh SherifNo ratings yet

- Variador Maquina CaminadoraDocument23 pagesVariador Maquina CaminadoraHector Cabrera100% (1)

- Lecture - MOS & MOSFET-1Document21 pagesLecture - MOS & MOSFET-1Kartika MunirNo ratings yet

- Wakodikar 2020Document6 pagesWakodikar 2020mohamed redaNo ratings yet

- CH 06Document70 pagesCH 06M. Ahmad IjazNo ratings yet

- CMOS SubcircuitsDocument80 pagesCMOS SubcircuitsashishmanyanNo ratings yet

- Aic Lab Cadence 11 Folded v02Document9 pagesAic Lab Cadence 11 Folded v02Hagar IlbheryNo ratings yet

- Implementing A PID Controller in A Microsemi Fpga: Application Note AC303Document8 pagesImplementing A PID Controller in A Microsemi Fpga: Application Note AC303tjshelleyNo ratings yet

- Lecture9 - Digital CMOS LogicDocument27 pagesLecture9 - Digital CMOS LogicAliemre TeltikNo ratings yet

- DPM 1As-Bl: Product DescriptionDocument4 pagesDPM 1As-Bl: Product DescriptionFane PelinNo ratings yet

- AN240 Interfacing 3V and 5V Applications: Authors: Tinus Van de Wouw (Nijmegen) / Todd Andersen (Albuquerque)Document7 pagesAN240 Interfacing 3V and 5V Applications: Authors: Tinus Van de Wouw (Nijmegen) / Todd Andersen (Albuquerque)teo37No ratings yet

- EE42 100 Wb-Lecture19 080713-FDocument37 pagesEE42 100 Wb-Lecture19 080713-FozanistzNo ratings yet

- Electronics Projects - DC Motor Speed Control Using H-Bridge - EngineersGarageDocument1 pageElectronics Projects - DC Motor Speed Control Using H-Bridge - EngineersGarageMmeli NtwanaYebhoza DubeNo ratings yet

- CMOS Logic Gates: Gagandeep SinghDocument37 pagesCMOS Logic Gates: Gagandeep SinghGagandeep Singh Dhingra100% (1)

- OTA ComparatorsDocument41 pagesOTA ComparatorsPedro Aaron Saldaña100% (1)

- Sliding Mode Control of SMPS: Ms. A. Jonisha, Mrs. V. Devi MaheswaranDocument11 pagesSliding Mode Control of SMPS: Ms. A. Jonisha, Mrs. V. Devi MaheswaranInternational Organization of Scientific Research (IOSR)No ratings yet

- Analog Electronic and LICDocument202 pagesAnalog Electronic and LICshilpaNo ratings yet

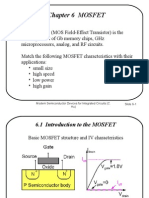

- Ch. 6 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsDocument70 pagesCh. 6 Lecture Slides For Chenming Hu Book: Modern Semiconductor Devices For ICsChenming Hu100% (2)

- DC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Document22 pagesDC-to-DC Power Converter by Rodney Yeu and Sudip Kundu ECE 345 Section H TA: Jon Wheeler 4/26/02 Project #34Harkishen SinghNo ratings yet

- 16 Design IdeasDocument7 pages16 Design Ideasmailnehru8955100% (2)

- Multilevel Inverters en PDFDocument34 pagesMultilevel Inverters en PDFbektasNo ratings yet

- A Doubly Grounded Boost Seven Level PV Inverter Topology With Model Predictive ControllerDocument6 pagesA Doubly Grounded Boost Seven Level PV Inverter Topology With Model Predictive ControllerRodovarNo ratings yet

- UNIT-II Shunt Compensation StatcomDocument35 pagesUNIT-II Shunt Compensation StatcomHarshJindalNo ratings yet

- Inside The Digital Gate: Reading: Chapter 6 of A&LDocument31 pagesInside The Digital Gate: Reading: Chapter 6 of A&LVenkata KrishnanNo ratings yet

- MMC Documentation EMTPDocument36 pagesMMC Documentation EMTPmancolmoNo ratings yet

- Current Mode Pi ControllerDocument19 pagesCurrent Mode Pi ControllersunitaNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- VLSI Questions Answers r3Document79 pagesVLSI Questions Answers r3Gowtham HariNo ratings yet

- EE/CE 6301: Advanced Digital Logic: Bill SwartzDocument140 pagesEE/CE 6301: Advanced Digital Logic: Bill SwartzGowtham HariNo ratings yet

- Scan Path DesignDocument54 pagesScan Path DesignGowtham HariNo ratings yet

- Aoi 22Document6 pagesAoi 22Bryan OrenseNo ratings yet

- Unix CommandsDocument4 pagesUnix CommandsAzmat NaseemNo ratings yet

- EEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniDocument44 pagesEEDG/CE 6301: Advanced Digital Logic: Mehrdad NouraniGowtham HariNo ratings yet

- Chapter 1. Overview of Digital Design With Verilog HDLDocument6 pagesChapter 1. Overview of Digital Design With Verilog HDLGowtham HariNo ratings yet

- HW 1Document1 pageHW 1Gowtham HariNo ratings yet

- Problem 3) Implementation of Problem1 Using Synopsys CodeDocument22 pagesProblem 3) Implementation of Problem1 Using Synopsys CodeGowtham HariNo ratings yet

- TRIACDocument1 pageTRIACGowtham HariNo ratings yet

- Final FileDocument54 pagesFinal FileGowtham HariNo ratings yet

- EE 6325 VLSI Design: Office HoursDocument5 pagesEE 6325 VLSI Design: Office HoursGowtham HariNo ratings yet

- Introduction To Analog Integrated Circuits DesignDocument20 pagesIntroduction To Analog Integrated Circuits DesignGowtham HariNo ratings yet

- Electronic Ding Dong Kit Parts: For Seeria OrderDocument12 pagesElectronic Ding Dong Kit Parts: For Seeria OrderAsghar AliNo ratings yet

- 4-Torch IO CardDocument25 pages4-Torch IO CardJose Luis LopezNo ratings yet

- GR00005200D 13a PDFDocument187 pagesGR00005200D 13a PDFbitadminaccNo ratings yet

- DCM PDFDocument2 pagesDCM PDFvasava dipakNo ratings yet

- Auto Changeover SchemeDocument14 pagesAuto Changeover SchemeSudipto MajumderNo ratings yet

- Model 4820 Series Truck Socket Wiring To Liberty (5-Wire) OBMDocument1 pageModel 4820 Series Truck Socket Wiring To Liberty (5-Wire) OBMJonyNo ratings yet

- OsiSense XC XCMN2102L1 DocumentDocument6 pagesOsiSense XC XCMN2102L1 DocumentRadoNo ratings yet

- Bq24753a Host-Controlled Li-Ion and Li-Polymer Battery Charger With Low I and System Power SelectorDocument46 pagesBq24753a Host-Controlled Li-Ion and Li-Polymer Battery Charger With Low I and System Power SelectorHeru susantoNo ratings yet

- Piezo Road Traffic Sensor (PVDF FILM)Document2 pagesPiezo Road Traffic Sensor (PVDF FILM)HeejongNo ratings yet

- FM Transmitter PDFDocument5 pagesFM Transmitter PDFAndrés HoyteNo ratings yet

- SIMATIC S5 Communication CableDocument8 pagesSIMATIC S5 Communication CableAlex GonzalezNo ratings yet

- Thyristor Controlled Power For Induction Motor 1 FrontDocument8 pagesThyristor Controlled Power For Induction Motor 1 Frontvidhya associateNo ratings yet

- FAC-008-1 FKE Facility Rating Methodology r5Document13 pagesFAC-008-1 FKE Facility Rating Methodology r5Dave SchlageterNo ratings yet

- 0947 Power Factor CorrectionDocument4 pages0947 Power Factor CorrectionاحمدرضاNo ratings yet

- A3910 DatasheetDocument7 pagesA3910 DatasheetLêĐìnhDanhNo ratings yet

- Unit 4Document102 pagesUnit 4Manjushree KumaravelNo ratings yet

- 2.5 Solid-State RelaysDocument4 pages2.5 Solid-State Relaysmuez zabenNo ratings yet

- RameshDocument12 pagesRameshKurapati Siddarth100% (1)

- Delta Fan/Pump Vector Control Drive CP2000 Series User ManualDocument868 pagesDelta Fan/Pump Vector Control Drive CP2000 Series User Manualotaku sekaiNo ratings yet

- WTB16P-24161120A00: Small Photoelectric SensorsDocument8 pagesWTB16P-24161120A00: Small Photoelectric SensorsValen TineNo ratings yet

- CH01 and 02Document64 pagesCH01 and 02hmltdt9221No ratings yet

- Downloaded From Manuals Search EngineDocument12 pagesDownloaded From Manuals Search Engineyoga_pntNo ratings yet

- Manual Book Inverter A-800Document862 pagesManual Book Inverter A-800Rizky AndreanNo ratings yet

- E8 Lab ReportDocument2 pagesE8 Lab ReportVin_Q26No ratings yet

- 1 Grounding and Bonding For Electrical SystemsDocument4 pages1 Grounding and Bonding For Electrical SystemsronniedakingpouNo ratings yet

- Olflex LappDocument2 pagesOlflex LappSanthosh V RaajendiranNo ratings yet

- MID 216 PSID 11 Brake Light Right SideDocument3 pagesMID 216 PSID 11 Brake Light Right SideTun Tun Win Kse100% (1)

Digital Microelectronic Digital Microelectronic Circuits Circuits ( (

Digital Microelectronic Digital Microelectronic Circuits Circuits ( (

Uploaded by

Gowtham HariOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Digital Microelectronic Digital Microelectronic Circuits Circuits ( (

Digital Microelectronic Digital Microelectronic Circuits Circuits ( (

Uploaded by

Gowtham HariCopyright:

Available Formats

Digital Microelectronic Digital Microelectronic

Circuits Circuits

((361 361--1 1--3021 3021 ))

Presented by: Dr. Alexander Fish

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 11

The CMOS The CMOS

Inverter Inverter

Lecture Lecture 77::

Motivation Motivation

The Inverter, or NOT gate, is truly the

nucleus of all digital designs.

We will analyze the inverter and find its

characterizing parameters.

Once its operation and properties are

clearly understood, designing and

In Out

0 1

1 0

In Out

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

clearly understood, designing and

analyzing more intricate structures, such

as NAND gates, adders, multipliers and

microprocessors is greatly simplified.

This lecture focuses on the static CMOS

inverter the most popular at present and

the basis for the CMOS digital logic family.

22

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.1 An Intuitive Explanation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 33

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

AN INTUITIVE EXPLANATION AN INTUITIVE EXPLANATION

As usual, well start with

44

+

-

V

An Intuitive Explanation An Intuitive Explanation

A Static CMOS Inverter is modeled on

the double switch model.

The basic assumption is that the

switches are Complementary, i.e.

when one is on, the other is off.

V0

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

When the top switch is on, the supply

voltage propagates to the output

node.

When the bottom switch is on, the

ground voltage is propagated out.

55

An Intuitive Explanation An Intuitive Explanation

Now we will replace the model switches

with real voltage controlled switches

MOS Transistors.

We will use complementary transistors

one nMOS and one pMOS, and hook

them up to the same input voltage.

V =V

+

-

V

V

out

=0

V =0

V

out

=V

in

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

them up to the same input voltage.

Now, when we set a high input voltage,

the nMOS is on and the pMOS off. The

ground voltage propagates.

When we put a low input voltage, the

pMOS is on and the nMOS is off. The

supply voltage propagates.

Weve built an inverter!

66

V

in

=V V

in

=0

V

out

=V

in

An Intuitive Explanation An Intuitive Explanation

The voltage connected to the Source of the pMOS is

known as the Supply Voltage or V

DD

.*

We mark the connection to V

DD

with a horizontal or

slanted bar.

Accordingly, V

DD

represents a logical 1 and GND

represents a logical 0.

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

represents a logical 0.

Inputting V

DD

to the CMOS inverter will present GND

at the output. Inputting GND will present V

DD

at the

output.

This characteristic is non-trivial and is one of the

advantages of CMOS design. It is known as Rail to

Rail Swing.**

77

* It can also be called V

CC

, regarding the Collector of BJT transistors.

** Rails are the supply voltages, i.e. V

DD

and GND. If a voltage is connected

to the nMOS Source instead of GND, we refer to this voltage as V

SS

.

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.2 Static Operation

7.1 An Intuitive Explanation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 88

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

STATIC OPERATION STATIC OPERATION

Now that we understand the principles,

well analyze

99

The Inverters VTC The Inverters VTC

To construct the VTC of the CMOS inverter,

we need to graphically superimpose the I-V

curves of the nMOS and pMOS onto a

common coordinate set.

We can see that: I

SDp

I I =

V

SGp V

SDp

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 10 10

I

DSn

SDp DSn

I I =

GSn in

V V =

SGp DD in

V V V =

DSn out

V V =

SDp DD out

V V V =

V

GSn

V

out

V

in

V

DD

V

DSn

The Inverters VTC The Inverters VTC

Since V

in

and V

out

are the input and output voltages of the

nMOS transistor, we will change the coordinates of the

pMOS.

V

SGp

=2.5

out DD SDp

V V V =

I

SDp

V =1.5

V

in

=0

I

DSn

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 11 11

V

SGp

=1

out DD SDp

V

SDp

V

in

=1.5

DSn SDp

I I =

V

out

in DD SGp

V V V =

For V

DD

=2.5V

The Inverters VTC The Inverters VTC

Now, we will superimpose the modified pMOS I-V curves on

the nMOS I-V graphs:

I

DSn

V

in

=0 V

in

=V

DD

The intersection of corresponding load lines shows the DC

operating points, where the currents of the nMOS and pMOS

are equal.

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 12 12

V

out

V

in

=0

V

in

=V

DD

/2 V

in

=V

DD

/2

V

in

=V

DD

The Inverters VTC The Inverters VTC

Putting all the intersection points on a graph with the

corresponding output voltage will give us the CMOS

inverters VTC:

V

out

V

DD

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 13 13

V

in

V

DD

/2

V

DD

/2

V

DD

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.2 Static Operation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 14 14

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Operating Regions Operating Regions

Lets figure out what region of operation each transistor is in

throughout the VTC curve.*

V

out

V

DD

* Considering Long Channel Transistors

With V

TH

<V

DD

/2

in TH

V V <

GSn in TH

V V V Cutoff = <

V

SGp V

SDp

V

out

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 15 15

V

in

V

DD

/2

V

DD

/2

V

DD V

TH

GSn in TH

V V V Cutoff = <

V

GSn

SGp DD in TH

SDp DD out TH SGp

V V V V

Linear

V V V V V

= >

`

= <

)

Operating Regions Operating Regions

So now, lets jump to the other side of the VTC.

V

out

V

DD

in DD TH

V V V >

SGp DD in TH

V V V V Cutoff = <

V

SGp

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 16 16

V

in

V

DD

/2

V

DD

/2

V

DD V

DD

-V

TH

V

GSn

GSn in DD TH TH

DSn out GSn TH

V V V V V

Linear

V V V V

= > >

`

= <

) V

DSn

V

out

Operating Regions Operating Regions

Now, back to the VTC regions. Lets see what happens

when we raise the input voltage slightly past V

TH

.

V

out

V

DD

in TH

V V >

GSn in TH

V V V = >

V

SGp V

SDp

V

out

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 17 17

V

in

V

DD V

TH

+V

GSn in TH

DSn out DD GSn TH

V V V

Sat

V V V V V

= >

`

= >

)

V

GSn

0

SGp DD in TH

SDp DD out SGp TH

V V V V

Linear

V V V V V

= >

`

= <

)

Operating Regions Operating Regions

The same when V

in

is a bit more than V

TH

lower than V

DD

.

V

out

V

DD

in DD TH

V V V V =

SGp DD in TH

V V V V = >

V

SGp V

SDp

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 18 18

V

in

V

DD V

DD

-V

TH

-V

SGp DD in TH

SDp DD out DD SGp TH

V V V V

Sat

V V V V V V

= >

`

= >

)

V

GSn

0

GSn in TH

DSn out GSn TH

V V V

Linear

V V V V

= >

`

= <

)

V

out

Operating Regions Operating Regions

Finally, we have the middle area, where:

V

out

V

DD

2

in DD

V V V =

2

2

SGp DD in DD TH

SDp DD out DD SGp TH

V V V V V

Sat

V V V V V V

= >

`

= >

)

V

SGp V

SDp

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 19 19

V

in

V

DD V

DD

/2

V

GSn

V

out

2

2

GSn in DD TH

DSn out DD GSn TH

V V V V

Sat

V V V V V

= >

`

= >

)

Operating Regions Operating Regions

To Sum it up:

V

out

V

DD

Towards the rails, one of the transistors

is cut off, and the other is resistive.

Once the cut off transistor starts

conducting, it immediately is saturated.

nMOS off

pMOS - res

nMOS sat

pMOS - res

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 20 20

V

in

V

DD

As we approach the middle input

voltages, both transistors are saturated.

The VTC slope is known as the Gain of

the gate.

pMOS - res

nMOS sat

pMOS - sat

nMOS res

pMOS - sat

nMOS res

pMOS - off

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.2 Static Operation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 21 21

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Switching Threshold Switching Threshold

The Switching Threshold, V

M

, is the point where V

in

=V

out

.

This can be calculated:

Graphically, at the intersection of the VTC with V

in

=V

out

V

out

V

DD

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Or analytically, by equating the nMOS and pMOS saturation currents

with V

in

=V

out

.

22 22

V

in

V

DD

V

M

Switching Threshold Switching Threshold

Lets analytically compute V

M

.

Remember, the saturation current for a MOSFET is given by:

Lets assume =0 and well equate the two currents:

( ) ( )

2

2

p

n

k

k

I V V V V = =

( ) ( )

2

1

2

DS GS TH DS

k

I V V V = +

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Now well substitute:

And well arrive at:

23 23

( ) ( )

2

2

2 2

p

n

D GSn Tn SGp Tp

k

k

I V V V V = =

GSn in M

V V V = =

SGp DD in DD M

V V V V V = =

( )

1

Tn DD Tp

M

V r V V

V

r

+

=

+

p

n

k

r

k

Switching Threshold Switching Threshold

A similar analytic evaluation for short channel devices with

a current of:

Will bring us to:

2

DSAT

DS DSAT GS TH

V

I kV V V

| |

=

|

\

V

V | |

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

And assuming V

Tn

=V

Tp

and V

DD

is much larger than V

TH

and

V

DSAT

, we can estimate:

24 24

2 2

1

DSATp

DSATn

Tn DD Tp

M

V

V

V r V V

V

r

| |

+ + + +

|

\

=

+

p DSATp

short

n DSATn

k V

r

k V

2 1 1

DSAT short DD short DD

M T

short short

V r V r V

V V

r r

= + +

+ +

Switching Threshold Switching Threshold

As we can see, r is an important factor in setting the

threshold voltage.

r is a design parameter, that is set by the drive strength

ratios of the nMOS and pMOS:

_

p

long channel

k

r

k

ox

W W

k k C

L L

=

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Using the current equations again, we can find the drive

strength ratio for a desired V

M

:

25 25

_ long channel

n

r

k

ox

k k C

L L

=

2

p

M Tn

n DD M Tp

k

V V

k V V V

| |

= |

|

\

Switching Threshold Switching Threshold

A symmetric VTC (V

M

=V

DD

/2) is often desired. In this case:

Generally, the same length (L) is taken for all transistors in

digital circuits, and so for a symmetric VTC:

n

p n p

W W

L L

| | | |

=

| |

\ \

( )

2 1

Tn DD Tp

DD

M

V r V V

V

V

r

+

= =

+

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

digital circuits, and so for a symmetric VTC:

26 26

2...4

p

n

n p

W

W

=

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 27 27

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Remember our definitions of Noise Margins from Lecture 3.

Noise Margins Noise Margins

V(y)

V

OHmin

Slope = -1

"1"

V

OHmin

V

IH

Undefined

Region

NM

H

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 28 28

V(x)

V

OLmax

V

IH

V

IL

Slope = -1

V

M

max

min

L IL OL

H OH IH

NM V V

NM V V

=

=

"0"

V

IL

V

OLmax

Region

NM

L

Noise Margins Noise Margins

One of the CMOS logic familys advantages is a Full Rail to

Rail Swing. In other words:

To calculate the Noise Margins, we will need to find V

IL

and

V

IH

. These are the points where the gain is -1.

max

min

OH DD

OL

V V

V GND

=

=

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

V

IH

. These are the points where the gain is -1.

To do this we will equate the

currents:

V

IL

nMOS sat, pMOS res

V

IH

nMOS res, pMOS sat

29 29

V

out

V

in

V

DD

V

DD

1

out

in

dV

dV

=

1

out

in

dV

dV

=

nMOS sat

pMOS - res

nMOS res

pMOS - sat

Noise Margins Noise Margins

Lets calculate V

IH

:

Assuming matching devices (k

n

=k

p

, V

Tn

=V

Tp

):

Differentiating and equating -1, we reach:

( ) ( ) ( ) ( )

2

2

2 2

p

DSn

DSn n GSn Tn DSn DSp GSp Tp

k

V

I res k V V V I sat V V

(

= = =

(

( ) ( )

2

2 1

2 2

out

IH TH out DD IH TH

V

V V V V V V =

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Differentiating and equating -1, we reach:

Doing the same for V

IL

or using symmetry, we reach:

Accordingly, for a matched long-channel device, and

assuming V

OHmin

V

OHmax

and V

OLmax

V

OLmin

in CMOS, we get:

30 30

( )

1

5 2

8

IH DD TH

V V V =

( )

1

3 2

8

IL DD TH

V V V = +

( )

1

0 3 2

8

H L DD IH IL DD TH

NM NM V V V V V = = = +

Noise Margins Noise Margins

A different approach is to use a piece-wise linear

approximation:

OH OL DD

IH IL

V V V

V V

g g

= =

V

out

V

DD

g

M

IH M

V

V V

g

=

DD M

IL M

V V

V V

g

= +

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 31 31

V

in

V

DD

V

IH

V

IL

g g

H DD IH L IL

NM V V NM V = =

With this approach, finding the inverters gain will show us

the noise margins with a very small error.

Noise Margins Noise Margins

We will find the gain at the mid-point (both transistors are

saturated) of a short-channel device:

Differentiating, we get:

( ) ( )

1 1

2 2

DSATp

DSATn

D n DSATn in Tn n out p DSATp DD in Tp p DD p out

V

V

I k V V V V k V V V V V V

| |

| |

= + = +

| |

\

\

( ) ( )

+ + +

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Ignoring some second order expressions and substituting

V

in

=V

M

, we arrive at:

32 32

( ) ( )

( ) ( )

1 1

/ 2 / 2

n DSATn n out p DSATp p DD p out

out

in n n DSATn in Tn DSATn p p DSATp DD in Tp DSATp

k V V k V V V

dV

dV k V V V V k V V V V V

+ + +

=

+

( ) ( )( )

1 1

/ 2

n DSATn p DSATp

D M n p M Tn DSATn n p

k V k V

r

g

I V V V V

+

+

=

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

DYNAMIC OPERATION DYNAMIC OPERATION

Now that we see how the inverter behaves in

steady state, we will analyze its transient:

33 33

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.2 Static Operation

7.3 Dynamic Operation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 34 34

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Parasitic Capacitances Parasitic Capacitances

Remember that our transistors have capacitance connected

to the output node.

Well calculate the capacitance values a bit later,

but for now, lets just use and equivalent

output capacitance.

When the input is low our pMOS is a

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

When the input is low our pMOS is a

non-linear resistor and our nMOS is

cut off, so we get a simple RC circuit.

Our capacitance is charged, bringing

the output voltage to V

DD

.

35 35

+

-

V

C

eq

V

DD

When the input is high, we essentially have closed the top

switch and opened the bottom one.

This creates a resistive path from the capacitor to GND, and

blocks the path from the supply to the output.

Again we have an RC network, though this time

we are just discharging the capacitance to GND.

Parasitic Capacitances Parasitic Capacitances

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

we are just discharging the capacitance to GND.

We end up with an output equal to GND.

36 36

C

eq

0

Parasitic Capacitances Parasitic Capacitances

So we saw that, a switching CMOS inverter charges and

discharges a parasitic output capacitance.

During the switching process, we can create a model that

will transform the circuit into a simple RC network.

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

In this way, we can easily derive a first order analysis of the

CMOS dynamic operation for propagation delay and power

consumption calculation.

Our first goal is to represent all the parasitic capacitances

by one output capacitance between the output node and

ground.

37 37

Lets remember the MOSFET capacitances that we learned

in Lecture 4:

Parasitic Capacitances Parasitic Capacitances

G

C

GD

C

GS

GS GCS GSO

C C C = +

GD GCD GDO

C C C = +

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 38 38

D

S

B

C

SB

C

DB

C

GB

GB GCB

C C =

SB Sdiff

C C =

DB Ddiff

C C =

Parasitic Capacitances Parasitic Capacitances

Well start with the obvious:

Taking the input step as ideal, the gate-to-source

and gate-to-body capacitances dont contribute

to the propagation delay.

The source-to-body capacitance is shorted to the

supply, so it doesnt switch.

C

GSP

+C

GBP

C

GDP

+C

GDN

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

What about the gate-to-drain capacitance?

While the gate voltage rises (V

in

), the drain

voltage drops (V

out

) and vice versa.

According to the Miller Effect, we can move this

capacitance relative to ground, doubling its

value.

39 39

C

GSN

+C

GBN

2(C

GDP

+C

GDN

)

Parasitic Capacitances Parasitic Capacitances

And last we have diffusion capacitances:

Both drain-to-body capacitances have a

terminal with a constant voltage and the

other connected to the output.

For a simple computation, we will replace

them with an equivalent capacitance to ground.

C

DBP

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

them with an equivalent capacitance to ground.

These capacitances are very non-linear and

we will not go into their calculation in this

course.

40 40

C

DBN

C

DBP

+C

DBN

Now, to annotate the parasitics during switching, we will

cascade another inverter after the first.

We first add the Wire Capacitance.

Then we add the gate capacitances of

the second inverter.

These are approximately the oxide

P1

P2

Parasitic Capacitances Parasitic Capacitances

C

GP2

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

These are approximately the oxide

capacitance times the area:

Again, we can just add the pMOS gate

capacitance to the general capacitance to

ground.

N1

P1

P2

N2

41 41

C

GN2

C

W

( )

2 2 2 2 2 2 GN GP OX N N P P

C C C W L W L + +

Parasitic Capacitances Parasitic Capacitances

Altogether, as a very general approximation, we get:

An even more general approximation

with N fan-out gates gives us:

P1

P2

C

GP2

C

DBP1

( ) ( )

1 1 1 1 2 2

2( )

load GDP GDN DBP DBN GP GN W

C C C C C C C C = + + + + + +

C C C N C = + +

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 42 42

N1

P1

P2

N2

C

GN2

C

DBN1

+C

W

C

GDP1

+C

GDN1

C

DBP1

load out wire in

C C C N C = + +

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.3 Dynamic Operation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 43 43

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Propagation Delay Propagation Delay

Now that we know the load capacitance of the CMOS

inverter, we can write:

Assuming an ideal step at the input, the propagation delay, t

( ) ( )

0

1

t

out

load

V t i t dt

C

=

( )

( )

2

1

v

load

pd

v

C v

t dv

i v

=

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Assuming an ideal step at the input, the propagation delay, t

pd

is the time it takes the output to (dis)charge 50% of its

voltage.

We will look at three ways to calculate the propagation

delay:

By solving the integral above.

By approximating the average current

By using equivalent resistance

44 44

Propagation Delay Propagation Delay Method Method 1 1

Well start with V

in

=0. Accordingly, P1 is

open and N1 is closed, causing the output

voltage to be held at V

out

=V

DD

At t=0, V

in

changes from 0 to V

DD

, closing

P1 and opening N1.

This causes the output to discharge

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

This causes the output to discharge

like a first order RC network.

45 45

V

DD

C

eq

t

V

in

t

V

out

t=0

V

DD

Propagation Delay Propagation Delay Method Method 1 1

At this point V

DSn

=V

DD

>V

GS

-V

TH

, so N1 is in saturation and

the discharge current is given by:

Assuming =0 and integrating until N1 enters the linear

( ) ( )

2

1

2

n

DSn In TH out

k

I V V V = +

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Assuming =0 and integrating until N1 enters the linear

region:

46 46

( )

( )

( )

1

2

2

DD TH

DD

V V

DD DD TH

load

p

V

n

D

DD TH

C V V V

C

t dv

k

i sat

V V

(

= =

t

V

out

V

DD

V

DD

/2

V

DD

-V

TH

t

p1

t

pHL

Propagation Delay Propagation Delay Method Method 1 1

Now V

DSn

<V

GS

-V

TH

and so N1 goes into linear operation

with:

Well write an expression for the change in voltage:

( ) ( )

2

2

out

DSn n in TH out

V

I res k V V V

(

=

(

( )

2

2

DSn n out

out in TH out

i k V

dV dt V V V

C C

(

= =

(

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

And arrive at the following integral:

47 47

2

load load

C C

(

( )

( )

1

2

2

2

1

2

pHL DD

DD TH

t V

load out

p

t V V

n DD TH

out out

DD TH

C dV

t dt

k V V

V V

V V

= =

t

V

out

V

DD

V

DD

/2

V

DD

-V

TH

t

p1

t

pHL

t

p2

Propagation Delay Propagation Delay Method Method 1 1

Using the equality:

We get:

2

1

ln 1

dx

ax x ax

| |

=

|

2

3 4

ln

load DD TH

p

C V V

t

| |

=

|

t

V

out

V

DD

V

DD

/2

V

DD

-V

TH

t t

t

p2

( )

( )

2

2

2

1

2

DD

DD TH

V

load out

p

V V

n DD TH

out out

DD TH

C dV

t

k V V

V V

V V

==

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

And putting together the two parts, we get:

For V

TH

=0.2V

DD

, we get:

48 48

2

ln

p

n DD

t

k V

=

|

\

( )

1 2

2 1 3 4

ln

2

load TH DD TH

pHL p p

n DD TH DD TH DD

C V V V

t t t

k V V V V V

( | |

= + = +

( |

\

1.6

load

pHL

n DD

C

t

k V

=

t

p1

t

pHL

Propagation Delay Propagation Delay Method Method 2 2

As mentioned earlier, using a different approach, we can

approximate this delay using average currents.

We will find the average current between t=0 and t=t

pHL

and

calculate:

( ) ( )

2

1

0

DD

load

load

pHL

V

C

C V

t

i

i i t

=

(

+

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Knowing that i

DSn

(0) is saturation current with V

DSn

=V

DD

and

i

DSn

(t

pHL

) is linear current with V

DSn

=0.5V

DD

, we get:

49 49

( ) ( )

1

0

2

DSn

avg

DSn DSn pHL

i

i i t

(

+

1.7

load

pHL

n DD

C

t

k V

Propagation Delay Propagation Delay Method Method 3 3

As seen above, the derivation of the propagation delay in a

direct and accurate way is quite complex.

A general and more intuitive option is to derive a linear

equivalent resistance for a transistor that gives a good

estimation that is much simpler to analyze.

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

estimation that is much simpler to analyze.

The primary approach to deriving such an equivalent

resistance is to calculate the transistors average resistance

throughout its operation (ON) period.

50 50

( ) ( ) ( )

( )

( )

( ) ( )

2 2

1 2

1 1

... 1 2

2 1 2 1

1 1 1

2

t t

DS

eq t t t on on on on

DS t t

V t

R average R t R t dt dt R t R t

t t t t I t

=

= = = + (

Propagation Delay Propagation Delay Method Method 3 3

Now, we will calculate the propagation delay of a short

channel inverter, by using the equivalent resistance to

discharge a capacitor from V

DD

to V

DD

/2.

Assuming V

DD

>>V

DSATn

, we can assume

that throughout the propagation delay,

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

that throughout the propagation delay,

the transistor is velocity saturated.

We can write:

51 51

( )

/ 2

1 3 7

1

/ 2 4 1 9

DD

DD

V

DD

eq DD

DD DSAT DSAT V

V V

R dV V

V I I V

| |

=

|

+

\

( )

2

2

DSAT

DSAT n DD TH DSAT

V

I k V V V

(

=

(

Propagation Delay Propagation Delay Method Method 3 3

Now that we know the equal resistance, we can use a first

order RC network with a step function input for annotation:

0

out out in

load

eq

dV V V

C

dt R

+ =

( )

( )

1

t

out DD

V t e V

=

R C

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

For propagation delay computation, we will use V

1

(t)=V

DD

and V

2

(t)=V

DD

/2 and we arrive at:

52 52

( )

( )

1

out DD

V t e V =

eq load

R C

ln(2) 0.69 0.69

pHL n n eqn load

t R C = = =

Propagation Delay Propagation Delay Method Method 3 3

Similarly for a Low to High transition, we arrive at:

The overall propagation delay is defined as the average of

the two:

0.69 0.69

pLH p eqp load

t R C = =

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

the two:

53 53

( )

0.69

2 2

load eqp eqn pLH pHL

pd

C R R t t

t

+ +

=

Propagation Delay Propagation Delay Method Method 3 3

To calculate and analyze the parameters that affect the

propagation delay, we will take =0 and get:

Accordingly, we can minimize the delay in the following

3

0.69 0.52

4

2

DD DD load

pHL load

DSAT DSATn

n DSATn DD Tn

V V C

t C

V I

k V V V

= =

| |

|

\

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Accordingly, we can minimize the delay in the following

ways:

Minimize C

load

.

Increase W/L

Increase V

DD

54 54

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 55 55

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Device Sizing Device Sizing --

Device Sizing is the Width to Length ratio (W/L) of the

transistor.

When discussing a CMOS logic gate, we relate to the the

pMOS/nMOS ratio ((W

p

/L

p

)/(W

n

/L

n

)). We will call this ratio .

To get a balanced inverter (i.e. V

m

=V

DD

/2) we usually will

need =3-3.5, mainly due to the mobility ratio of holes and

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

need =3-3.5, mainly due to the mobility ratio of holes and

electrons.

This generally equates the propagation delay of High-to-

Low and Low-to-High transitions.

However, this does not imply that this ratio yields the

minimum overall propagation delay.

56 56

Device Sizing Device Sizing --

How can this be?

To get a faster t

pLH

, we need to enlarge the pMOS width.

This increases the parasitic capacitance (C

load

), degrading t

pHL

.

We will now find the optimum ratio for sizing an inverter.

As usual, we will consider two identical cascaded CMOS

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

As usual, we will consider two identical cascaded CMOS

inverters. The load capacitance of the driving gate is:

Now we will mark the device size ratio as :

57 57

( ) ( )

1 2 1 1 2 2 load out in wire dp dn gp gn wire

C C C C C C C C C = + + = + + + +

( )( )

1 2

1

load dn gn wire

C C C C = + + +

( )

( )

p

n

WL

WL

Device Sizing Device Sizing --

Noting that we have reduced the equivalent resistance of

the pMOS by , we can write the first order RC propagation

delay:

( ) ( )( )

1 2

0.69

0.345 1

2

eqp

load

pd eqn eqp dn gn wire eqn

R

C

t R R C C C R

| |

(

= + = + + + +

|

\

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Now we just need to find the minimum:

A typical optimum for is usually around 2.

58 58

0

pd

dt

d

=

( ) 1 2

1 2

1

dn gn wire

eqp eqp

wire

opt

eqn dn gn eqn

C C C

R R

C

R C C R

+ >>

| |

= + |

|

+

\

Device Sizing Device Sizing --

Conclusions:

A balanced inverter isnt usually the fastest possible

inverter.

A typical optimal pMOS/nMOS ratio for performance is

given by:

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

given by:

59 59

2

eqp

opt

eqn

R

R

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 60 60

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Device Sizing Device Sizing -- SS

We saw how the ratio between the pMOS and nMOS can

be optimized to improve performance.

Now, we will take a balanced inverter and see how upsizing

affects the intrinsic or unloaded delay.

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

We will start by writing the delay as a function of the

intrinsic capacitance (diffusion and overlap) and the extrinsic

capacitances (fanout and wiring):

61 61

( ) ( )

load diff overlap fanout wire int ext

C C C C C C C = + + + +

( )

int

0.69 0.69

pd eq load eq ext

t R C R C C = = +

Device Sizing Device Sizing -- SS

Now, we will mark the minimal intrinsic delay as t

p0

. This is

the delay of a minimum sized balanced inverter only loaded

by its own intrinsic capacitance (C

ext

=0):

We will now mark the sizing factor, S. This is the relative

upsizing of the inverter, i.e. C

int

=SC

ref

and accordingly

0

0.69

p ref ref

t R C

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

upsizing of the inverter, i.e. C

int

=SC

ref

and accordingly

R

eq

=R

ref

/S.

Now we can write the delay of an upsized inverter:

62 62

( ) ( )

int 0

0.69 0.69 0.69 1 1

ref

ext ext

pd eq ext ref ext ref iref p

ref ref

R

C C

t R C C SC C R C t

S SC SC

| | | |

= + = + = + = + | |

| |

\ \

Device Sizing Device Sizing -- SS

Conclusions:

The intrinsic delay of an inverter (t

p0

) is independent of

the sizing of the gate and is purely determined by

technology. When no load is present, an increase in the

drive of the gate is totally offset by the increased

0

1

ext

pd p

ref

C

t t

SC

| |

= + |

|

\

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

drive of the gate is totally offset by the increased

capacitance.

To minimize a loaded inverters delay, S should be

enlarged, but at the expense of a substantial gain in

area.

63 63

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 64 64

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

Sizing a chain of inverters Sizing a chain of inverters

As with everything in life, inverter sizing presents a number

of trade-offs:

The larger the load, the slower the driving gate.

To make the driving gate faster, upsizing is needed.

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

The more the gate is upsized, the higher the intrinsic capacitance,

which slows the gate down and presents a larger load capacitance

to the preceding gate.

To optimize this problem, instead of using one big inverter,

we will analyze the effect of a gradually increasing chain of

inverters.

65 65

Sizing a chain of inverters Sizing a chain of inverters

To explore this problem, we must define a proportionality

factor, .

is a function of technology*, that describes the

relationship between a gates input gate capacitance (C

g

)

and its intrinsic output capacitance (C

int

):

int g

C C

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Now, we will write the delay as a function of , and the

effective fanout, f:

We can see that the delay for a certain technology is only a

function of the effective fanout!

66 66

* is close to 1 for most submicron processes!

0 0

1 1

ext

pd p p

g

C f

t t t

C

| |

| |

= + = + |

|

|

\

\

ext

g

C

f

C

Sizing a chain of inverters Sizing a chain of inverters

Now we will express the delay

of a chain of inverters:

Assuming a negligible wire capacitance, for the j-th stage,

we get:

( ) , 1

1 1

g j j

C

f

t t t

+

| |

| |

= + = + |

|

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

And we can write the total delay as:

67 67

( ) , 1

, 0 0

,

1 1

g j j

pd j p p

g j

t t t

C

+

| |

= + = + |

|

|

\

\

( ) , 1

, 0

1 1

,

1

N N

g j

pd pd j p

j j

g j

C

t t t

C

+

= =

| |

= = + |

|

\

Sizing a chain of inverters Sizing a chain of inverters

We have N-1 unknowns, so we will derive N-1 partial

derivatives:

We receive a set of constraints:

( ) , 1

0

1 ,

1

N

g j

pd p

j g j

C

t t

C

+

=

| |

= + |

|

\

,

0

pd

g j

t

C

( )

( ) ( )

, 1 , g j g j

C

C

C C C

+

= =

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

This means that:

Each inverter is sized up by the same factor, f.

Each inverter has the same effective fanout, f

j

=f.

Each inverter has the same delay, t

p0

(1+f/ ).

68 68

( )

( ) ( ) , , 1 , 1

, , 1

g j g j g j

g j g j

C C C

C C

+

= =

Sizing a chain of inverters Sizing a chain of inverters

We can now find the effective fanout, f:

( ) , 1 ,2 ,3 ,4 ,

1 1 , ,1 ,2 ,3 , 1 , ,1

N N

g j g g g g N N load load

j

j j g j g g g g N g N g

C

C C C C

C C

f f

C C C C C C C

+

= =

= = = =

,1

/

N

N

load g

f C C F = =

,1

load

g

C

F

C

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

We defined the overall effective fanout, F, between the input

and load capacitance of the circuit. Using this parameter,

we can express the total delay:

69 69

0

1

N

pd p

F

t N t

| |

= +

|

|

\

Sizing a chain of inverters Sizing a chain of inverters

Starting with a minimum sized inverter with C

g,min

, and

driving a given load, C

load

, we can see that:

With a small number of stages, we get a large delay due to the

effective fanout (f, F).

With a large number of stages, we get a large delay due to the

intrinsic delay (Nt

p0

)

0

1

N

pd p

F

t N t

| |

= +

|

|

\

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

To find the optimal number of stages, we will differentiate

and equate to zero.

70 70

0

pd

dt

dN

=

ln

0

N

N

F F

F

N

+ =

Sizing a chain of inverters Sizing a chain of inverters

This equation only has an analytical solution for the case of

=0. In this esoteric case we get:

If we take the typical case of =1, we can numerically solve

ln

0

N

N

F F

F

N

+ =

0

ln

opt

N F

=

=

0

2.718

opt

f e

=

= =

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

If we take the typical case of =1, we can numerically solve

the equation and arrive at:

71 71

1

3.6

opt

f

=

3.6

1

log

opt

N F

=

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

POWER CONSUMPTION POWER CONSUMPTION

And now that we fully understand the static and dynamic operation

of the CMOS Inverter, its time to take a look at

72 72

What will we learn today? What will we learn today?

7.1 An Intuitive Explanation

7.2 Static Operation

7.3 Dynamic Operation

7.2.1 The Inverters VTC

7.2.2 Operating Regions

7.2.3 Switching Threshold

7.2.4 Noise Margins

7.3.1 Parasitic Capacitances

7.3.2 Propagation Delay

7.3 Dynamic Operation

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter 73 73

7.4 Power Consumption

7.5 Summary

7.3.2 Propagation Delay

7.3.3 Device Sizing -

7.3.4 Device Sizing S

7.3.5 Sizing a Chain of Inverters

7.4.1 Dynamic Power

7.4.2 Short Circuit Power

7.4.3 Static Power

7.4.4 Total Power Consumption

7.4 Power Consumption

Dynamic Power Dynamic Power

Assuming an ideal step input, we can analyze

the energy consumed from the supply of the

equivalent circuit during a Low-to-High transition

is given by:

( )

2

0 0 0

DD

DD DD

V

out

V V DD DD load load DD out load DD

dV

E i t V dt V C dt C V dV C V

dt

= = = =

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

Now, looking at the energy stored in the load

capacitance, we get:

74 74

( )

0 0 0

DD DD

V V DD DD load load DD out load DD

dt

( )

2

0 0 0

2

DD

DD

V

out load DD

Charge V out load out load out out

dV C V

E i t V dt C V dt C V dV

dt

= = = =

Dynamic Power Dynamic Power

Analyzing these results, we see that the energy required to

charge the output capacitance is twice the energy stored on

the capacitor at the end of the transition.

2

DD

V load DD

E C V =

2

2

load DD

Charge

C V

E =

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

This is relatively surprising and very important.

It means that half of the energy was wasted on the pMOS

resistance independent of its size!

75 75

Dynamic Power Dynamic Power

Assuming the input changes now from zero to one, we now

get a High-to-Low transition.

Here, the supply is disconnected, and the charge stored on

the capacitance flows through the nMOS to the ground.

The energy dissipated is the total energy stored on the

output capacitance, as no charge is left:

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

output capacitance, as no charge is left:

The sum of the charge and discharge

energy is obviously equal to the energy

supplied:

76 76

( )

2

0

0 0

2

DD

out load DD

discharge DSn out load out load out out

V

dV C V

E i t V dt C V dt C V dV

dt

= = = =

2

DD

charge discharge V load DD

E E E C V + = =

Dynamic Power Dynamic Power

Conclusions:

Each charge and discharge cycle dissipates a fixed amount of

energy, independent of the size of the device.

The effective energy is the charge stored on the capacitance. The

rest of the energy is wasted as heat burned on the pMOS (charge)

and nMOS (discharge) resistance.

To compute the Power Dissipation, we calculate the total

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

To compute the Power Dissipation, we calculate the total

energy wasted per one second.

For a circuit that completes a Low-to-High transition f

0 1

times per second (and therefore a

High-to-Low transition as well),

the dynamic power consumption is:

77 77

2

0 1 dyn load DD

P C V f

=

Dynamic Power Dynamic Power

We said that the Power Dissipation is a factor of the

switching frequency of the gate.

But the gate only switches when its input changes. In other

words, the switching activity is smaller than the circuit

frequency.

We can rewrite the Dynamic Power expression using the

Digital Microelectronic Circuits Digital Microelectronic Circuits The VLSI Systems Center The VLSI Systems Center -- BGU BGU Lecture Lecture 77: The CMOS Inverter : The CMOS Inverter

We can rewrite the Dynamic Power expression using the