Professional Documents

Culture Documents

Midtermarch 2

Midtermarch 2

Uploaded by

Ghina BaassiriCopyright:

Available Formats

You might also like

- Solution Manual of Cmputer Organization and ArchitecturDocument29 pagesSolution Manual of Cmputer Organization and ArchitecturHossam Al-atawi44% (27)

- Exercise Questions Finals-2Document22 pagesExercise Questions Finals-2Faiza AliNo ratings yet

- Interview Questions for IBM Mainframe DevelopersFrom EverandInterview Questions for IBM Mainframe DevelopersRating: 1 out of 5 stars1/5 (1)

- Rms2dc Ltc1968 Demo Circuit-Dc427b A B CDocument4 pagesRms2dc Ltc1968 Demo Circuit-Dc427b A B CsastrakusumawijayaNo ratings yet

- ECE 452: Computer Organization and DesignDocument9 pagesECE 452: Computer Organization and Designdermeister1988No ratings yet

- Your Name:: Final ExamDocument9 pagesYour Name:: Final ExamDaniel EcheverriaNo ratings yet

- PH 4 QuizDocument119 pagesPH 4 Quizstudent1985100% (1)

- Assignment1 4Document5 pagesAssignment1 4Munim DheemanNo ratings yet

- BaiTap Chuong123Document19 pagesBaiTap Chuong123Nguyễn Ngọc TúNo ratings yet

- Practice Exam Computer ArchitectureDocument15 pagesPractice Exam Computer ArchitectureMuhammad UsmanNo ratings yet

- ELEC2300 Homework 1Document2 pagesELEC2300 Homework 1李卓倫No ratings yet

- CS433 hw1 Fall 07Document3 pagesCS433 hw1 Fall 0798140207No ratings yet

- Instructions: Csce 212: Final Exam Spring 2009Document5 pagesInstructions: Csce 212: Final Exam Spring 2009NapsterNo ratings yet

- CENG400 Midterm Fall 2015Document10 pagesCENG400 Midterm Fall 2015Mohamad IssaNo ratings yet

- Hardw S97Document10 pagesHardw S97Dinesh DevaracondaNo ratings yet

- PL01 GuiaoDocument3 pagesPL01 GuiaoJoão LourençoNo ratings yet

- Comparch Comparch-002 Exams Midterm A8Xj46NCRoDocument9 pagesComparch Comparch-002 Exams Midterm A8Xj46NCRoMattia LeNo ratings yet

- Eduqas A Computer Science Sams From 2015Document48 pagesEduqas A Computer Science Sams From 2015Mohsin Khubaib AhmedNo ratings yet

- Cse3666 MT1S F12Document5 pagesCse3666 MT1S F12dimpal_3221No ratings yet

- Cse4302a1 SolDocument4 pagesCse4302a1 SolRajesh TiwaryNo ratings yet

- 1HDocument8 pages1HSandipChowdhuryNo ratings yet

- Hw1 Sum2013Document8 pagesHw1 Sum2013Dylan EricksonNo ratings yet

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Document4 pagesThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonNo ratings yet

- CAMP - QBDocument10 pagesCAMP - QBAkshai AkshaiNo ratings yet

- Question Bank For Computer ArchitectureDocument23 pagesQuestion Bank For Computer ArchitecturesuryaNo ratings yet

- Time: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14Document3 pagesTime: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14PrateekMandiNo ratings yet

- Illinois Exam2 Practice Solfa08Document4 pagesIllinois Exam2 Practice Solfa08bittronicNo ratings yet

- Comp Architecture Sample QuestionsDocument9 pagesComp Architecture Sample QuestionsMohamaad SihatthNo ratings yet

- cs146 Fall2017 Midterm1xxDocument12 pagescs146 Fall2017 Midterm1xxgrizzyleoNo ratings yet

- Computer Architecture Sample MidtermDocument9 pagesComputer Architecture Sample Midtermkhayat_samirNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- Arch June 2020Document3 pagesArch June 2020A7a WtfNo ratings yet

- Master of Computer Applications (MCA) : MCA/ASSIGN/I/YEAR/2014Document17 pagesMaster of Computer Applications (MCA) : MCA/ASSIGN/I/YEAR/2014Krishna PatelNo ratings yet

- Attempt All of The Following QuestionsDocument5 pagesAttempt All of The Following Questionssoli0snakeNo ratings yet

- Architecture ComputerDocument3 pagesArchitecture Computerlillyren2808No ratings yet

- Bachelor of Computer Applications (Revised Syllabus) : Assignments (For July, 2014 and Jan., 2015 Sessions)Document9 pagesBachelor of Computer Applications (Revised Syllabus) : Assignments (For July, 2014 and Jan., 2015 Sessions)Ashis PradhanNo ratings yet

- Quiz 1Document12 pagesQuiz 1RexChandu100% (1)

- Computer Science Textbook Solutions - 13Document30 pagesComputer Science Textbook Solutions - 13acc-expertNo ratings yet

- Quiz For Chapter 1Document12 pagesQuiz For Chapter 1Alejandro Delgadillo DuranNo ratings yet

- High Performance Computer Architecture (CS60003)Document2 pagesHigh Performance Computer Architecture (CS60003)Venkata PranavNo ratings yet

- HW 05Document6 pagesHW 05samadNo ratings yet

- COMP1411 Final Exam Question BookDocument10 pagesCOMP1411 Final Exam Question Bookashtonsamuel2121No ratings yet

- EXAMDec2012 SolutionDocument8 pagesEXAMDec2012 Solutionخالد ناهض نايف نجمNo ratings yet

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Document4 pages21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RNo ratings yet

- Tutorial Sheet2014Document7 pagesTutorial Sheet2014Julia DanielNo ratings yet

- Computer Architecture Midterm1 CmuDocument30 pagesComputer Architecture Midterm1 CmuÖzgürCemBirlerNo ratings yet

- FinalDocument4 pagesFinalApinya SUTHISOPHAARPORNNo ratings yet

- GATE 2011 Computer Science Engineering Set - C: Q.1 - Q.25 Carry One Mark EachDocument20 pagesGATE 2011 Computer Science Engineering Set - C: Q.1 - Q.25 Carry One Mark EachKanchan AroraNo ratings yet

- Exercises 1 Assembly and Machine Languages: Number SystemsDocument3 pagesExercises 1 Assembly and Machine Languages: Number SystemsThomas WangNo ratings yet

- CSA 2022 Sess2Document2 pagesCSA 2022 Sess2ahmed khanNo ratings yet

- Ajaykumargargengineeringcollege, Ghaziabad: Department of CseDocument2 pagesAjaykumargargengineeringcollege, Ghaziabad: Department of CseAmardeep SinghNo ratings yet

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MNo ratings yet

- Exam2 Fa2014 SolutionDocument14 pagesExam2 Fa2014 Solutionrafeak rafeakNo ratings yet

- Wa0002 PDFDocument39 pagesWa0002 PDFSreenath SreeNo ratings yet

- Hsslive - In: Computer ApplicationsDocument79 pagesHsslive - In: Computer Applicationspirated wallahNo ratings yet

- AP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceFrom EverandAP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Practical Numerical C Programming: Finance, Engineering, and Physics ApplicationsFrom EverandPractical Numerical C Programming: Finance, Engineering, and Physics ApplicationsNo ratings yet

- Computer Knowledge Bit Bank for All Competitive ExamsFrom EverandComputer Knowledge Bit Bank for All Competitive ExamsRating: 4 out of 5 stars4/5 (4)

- Designing An FPGA-Based Reader - ArticuloDocument4 pagesDesigning An FPGA-Based Reader - ArticuloRaul Crespo SaucedoNo ratings yet

- Ugreen Hitune True Wireless Earbuds Ws100 User ManualDocument16 pagesUgreen Hitune True Wireless Earbuds Ws100 User Manualtheron25No ratings yet

- W 48 × H 48 MM Power ON Delay Analog Timers: ATE8 SeriesDocument3 pagesW 48 × H 48 MM Power ON Delay Analog Timers: ATE8 Seriesyanier martinezNo ratings yet

- 5 Emc Techniques For Heatsinks TasterDocument5 pages5 Emc Techniques For Heatsinks Tasterhugo parraNo ratings yet

- Advanced Light Streak TutorialDocument21 pagesAdvanced Light Streak Tutorialerne1813No ratings yet

- Intel® Desktop Compatibility Tool: More InformationDocument51 pagesIntel® Desktop Compatibility Tool: More InformationdrdivishNo ratings yet

- GoodWE Product Page - DNS - AllDocument2 pagesGoodWE Product Page - DNS - AllImtiaz NNo ratings yet

- Cse IIIDocument47 pagesCse IIIJagan NathanNo ratings yet

- Colt 5dr Acc Bro1Document14 pagesColt 5dr Acc Bro1Samyaza ShemyazazNo ratings yet

- RRU Hardware Maintenance Guide (04) (PDF) - enDocument22 pagesRRU Hardware Maintenance Guide (04) (PDF) - enKamalKhanNo ratings yet

- Bentone BG 400 Manual de InstalacionDocument44 pagesBentone BG 400 Manual de InstalacionCarlos Baeza100% (1)

- Current Transformers Installation QuizDocument12 pagesCurrent Transformers Installation QuizsamNo ratings yet

- TRM 104Document2 pagesTRM 104Dennis RimandoNo ratings yet

- Cummins GensetDocument4 pagesCummins GensetBenny S PutraNo ratings yet

- p320h 2 5 SSD Product Brief LoDocument2 pagesp320h 2 5 SSD Product Brief LoMark ReinhardtNo ratings yet

- Battery Charging Guide - 6 VoltDocument5 pagesBattery Charging Guide - 6 VoltKidus DawitNo ratings yet

- Untitled DiagramDocument1 pageUntitled DiagramirfanNo ratings yet

- High Speed Modified Booth's Multiplier For Signed and Unsigned NumbersDocument8 pagesHigh Speed Modified Booth's Multiplier For Signed and Unsigned NumbersInternational Journal of Science and Engineering InvestigationsNo ratings yet

- FTK 1115 B PDFDocument10 pagesFTK 1115 B PDFnorshazlinNo ratings yet

- Airmux-200: Broadband Wireless MultiplexerDocument8 pagesAirmux-200: Broadband Wireless MultiplexerAbu FadilahNo ratings yet

- FMIL Pianos and Benches RETAIL Prices MAY E-MailDocument8 pagesFMIL Pianos and Benches RETAIL Prices MAY E-MailPalanisamy BalasubramaniNo ratings yet

- A100D-CE-04 Product General DescriptionDocument5 pagesA100D-CE-04 Product General DescriptionSurta DevianaNo ratings yet

- Electronic Measurments Instrumentation Eec403Document1 pageElectronic Measurments Instrumentation Eec403Brahmanand SinghNo ratings yet

- Mason S Flow Graph Formula PDFDocument21 pagesMason S Flow Graph Formula PDFRUBIONo ratings yet

- XAudio2 High Performance Considerations USDocument32 pagesXAudio2 High Performance Considerations USJose QuillahuamanNo ratings yet

- EC 3150 Label Printer (Win7 32bit) - InstructionDocument39 pagesEC 3150 Label Printer (Win7 32bit) - InstructionMarcelino Navarrete EvaristoNo ratings yet

- GlobcomDocument96 pagesGlobcomvacuumNo ratings yet

- Mastering Linux Kernel DevelopmentDocument346 pagesMastering Linux Kernel Developmentatom tux100% (2)

- Option Details: Synchrotact 6Document1 pageOption Details: Synchrotact 6Žarko MočnikNo ratings yet

Midtermarch 2

Midtermarch 2

Uploaded by

Ghina BaassiriOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Midtermarch 2

Midtermarch 2

Uploaded by

Ghina BaassiriCopyright:

Available Formats

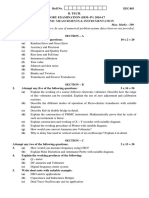

ECE 452: Computer Organization and Design Spring 2010 Midterm

Colorado State University 23 Mar 2010

Name: Student ID number:

___________________________________ ___________________________________

Instructions:

Write all answers on the white space provided below the question. In case you require more space, you can use the back of the sheet or extra sheets of paper. Only 1 sheet of hand written notes (both sides) on regular sized paper is allowed, along with a calculator. There are 9 regular questions for a total score of 100, and a 10th question for extra credit (10 points) You have 1 hour 30 minutes. Write legibly and give clear answers showing all your steps. Try to attempt all questions as partial points will be given for a correct approach. Make reasonable assumptions if there is ambiguity for any question. Not all questions are of equal difficulty. Please review the entire set of questions first and then budget your time carefully.

Q1. [10 points] Computer A has an overall CPI of 1.3 and can be run at a clock rate of 600MHz. Computer B has a CPI of 2.5 and can be run at a clock rate of 750 Mhz. We have a particular program we wish to run. When compiled for computer A, this program has exactly 100,000 instructions. How many instructions would the program need to have when compiled for Computer B, in order for the two computers to have exactly the same execution time for this program?

Q2. [10 points] Suppose that we can improve the floating point instruction performance of machine by a factor of 15 (the same floating point instructions run 15 times faster on this new machine). What percent of the instructions must be floating point to achieve a Speedup of at least 4?

Q3. [5 points] Prior to the early 1980s, machines were built with more and more complex instruction set. The MIPS is a RISC machine. Why has there been a move to RISC machines away from complex instruction machines?

Q4. [5 points] In the snippet of MIPS assembler code below, how many times is instruction memory accessed? How many times is data memory accessed? (Count only accesses to memory, not registers.) lw $v1, 0($a0) addi $v0, $v0, 1 sw $v1, 0($a1) addi $a0, $a0, 1

Q5. [20 points] In MIPS assembly, write an assembly language version of the following C code segment: int A[100], B[100]; for (i=1; i < 100; i++) { A[i] = A[i-1] + B[i]; } At the beginning of this code segment, the only values in registers are the base address of arrays A and B in registers $a0 and $a1. Avoid the use of multiplication instructionsthey are unnecessary.

Q6. [10 points] Structural, data and control hazards typically require a processor pipeline to stall. Listed below are a series of optimization techniques implemented in a compiler or a processor pipeline designed to reduce or eliminate stalls due to these hazards. For each of the following optimization techniques, state which pipeline hazards it addresses and (briefly) how it addresses it. Some optimization techniques may address more than one hazard, so be sure to include explanations for all addressed hazards.

(a) Branch Prediction

(b) Instruction Scheduling

(c) delay slots

(d) increasing availability of functional units (ALUs, adders etc)

(e) caches

Q7. [10 points] For the MIPS datapath shown below, several lines are marked with X.

(a) For each one, describe in words the negative consequence of cutting this line relative to the working unmodified processor.

(b) Provide a (minimum 2 instruction) snippet of MIPS assembly code that will fail

(c) Provide a (minimum 2 instruction) snippet of MIPS assembly code that will still work

Q8. [10 points] Consider a MIPS machine with a 5-stage pipeline with a cycle time of 10ns. Assume that you are executing a program where a fraction, f, of all instructions immediately follow a load upon which they are dependent. (a) With forwarding enabled what is the total execution time for N instructions, in terms of f ?

(b) Consider a scenario where the MEM stage, along with its pipeline registers, needs 12 ns. There are now two options: add another MEM stage so that there are MEM1 and MEM2 stages or increase the cycle time to 12ns so that the MEM stage fits within the new cycle time and the number of pipeline stages remain unaffected. For a program mix with the above characteristics, when is the first option better than the second. Your answer should be based on the value of f.

Q9. [20 points] Consider the following assembly language code: I0: ADD R4 = R1 + R0; I1: SUB R9 = R3 - R4; I2: ADD R4 = R5 + R6; I3: LDW R2 = MEM[R3 + 100]; I4: LDW R2 = MEM[R2 + 0]; I5: STW MEM[R4 + 100] = R2; I6: AND R2 = R2 & R1; I7: BEQ R9 == R1, Target; I8: AND R9 = R9 & R1; Consider a pipeline with forwarding, hazard detection, and 1 delay slot for branches. The pipeline is the typical 5stage IF, ID, EX, MEM, WB MIPS design. For the above code, complete the pipeline diagram below (instructions on the left, cycles on top) for the code. Insert the characters IF, ID, EX, MEM, WB for each instruction in the boxes. Assume that there two levels of bypassing, that the second half of the decode stage performs a read of source registers, and that the first half of the write-back stage writes to the register file. Label all data stalls (Draw an X in the box). Label all data forwards that the forwarding unit detects (arrow between the stages handing off the data and the stages receiving the data). What is the final execution time of the code?

Q10. [Extra credit question: 10 points] Prediction and Predication (a) Consider the following piece of code: for(i=0; i<1000000; i++){ a = random(100); if(a >= 50){ ... } } Assume that random(N) returns a random number uniformly distributed between 0 and N-1 inclusive. Consider the branch instruction associated with the if statement. Is there a type of branch predictor that predicts this branch well? Explain your answer.

(b) Predication can eliminate all forward conditional branches in a program. The backward branches in a program are, typically, associated with loops and hence are mostly taken. So it is possible to eliminate all forward branches and statically predict the backward branches as Taken and this would get rid of the complex branch predictors in a machine. But the Itanium processor which has hardware support for predication still retains a complex two level branch predictor. Explain why this is the case.

You might also like

- Solution Manual of Cmputer Organization and ArchitecturDocument29 pagesSolution Manual of Cmputer Organization and ArchitecturHossam Al-atawi44% (27)

- Exercise Questions Finals-2Document22 pagesExercise Questions Finals-2Faiza AliNo ratings yet

- Interview Questions for IBM Mainframe DevelopersFrom EverandInterview Questions for IBM Mainframe DevelopersRating: 1 out of 5 stars1/5 (1)

- Rms2dc Ltc1968 Demo Circuit-Dc427b A B CDocument4 pagesRms2dc Ltc1968 Demo Circuit-Dc427b A B CsastrakusumawijayaNo ratings yet

- ECE 452: Computer Organization and DesignDocument9 pagesECE 452: Computer Organization and Designdermeister1988No ratings yet

- Your Name:: Final ExamDocument9 pagesYour Name:: Final ExamDaniel EcheverriaNo ratings yet

- PH 4 QuizDocument119 pagesPH 4 Quizstudent1985100% (1)

- Assignment1 4Document5 pagesAssignment1 4Munim DheemanNo ratings yet

- BaiTap Chuong123Document19 pagesBaiTap Chuong123Nguyễn Ngọc TúNo ratings yet

- Practice Exam Computer ArchitectureDocument15 pagesPractice Exam Computer ArchitectureMuhammad UsmanNo ratings yet

- ELEC2300 Homework 1Document2 pagesELEC2300 Homework 1李卓倫No ratings yet

- CS433 hw1 Fall 07Document3 pagesCS433 hw1 Fall 0798140207No ratings yet

- Instructions: Csce 212: Final Exam Spring 2009Document5 pagesInstructions: Csce 212: Final Exam Spring 2009NapsterNo ratings yet

- CENG400 Midterm Fall 2015Document10 pagesCENG400 Midterm Fall 2015Mohamad IssaNo ratings yet

- Hardw S97Document10 pagesHardw S97Dinesh DevaracondaNo ratings yet

- PL01 GuiaoDocument3 pagesPL01 GuiaoJoão LourençoNo ratings yet

- Comparch Comparch-002 Exams Midterm A8Xj46NCRoDocument9 pagesComparch Comparch-002 Exams Midterm A8Xj46NCRoMattia LeNo ratings yet

- Eduqas A Computer Science Sams From 2015Document48 pagesEduqas A Computer Science Sams From 2015Mohsin Khubaib AhmedNo ratings yet

- Cse3666 MT1S F12Document5 pagesCse3666 MT1S F12dimpal_3221No ratings yet

- Cse4302a1 SolDocument4 pagesCse4302a1 SolRajesh TiwaryNo ratings yet

- 1HDocument8 pages1HSandipChowdhuryNo ratings yet

- Hw1 Sum2013Document8 pagesHw1 Sum2013Dylan EricksonNo ratings yet

- Thapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Document4 pagesThapar Institute of Engineering & Technology, Patiala: End Semester Examination (May 2019)Forza HorizonNo ratings yet

- CAMP - QBDocument10 pagesCAMP - QBAkshai AkshaiNo ratings yet

- Question Bank For Computer ArchitectureDocument23 pagesQuestion Bank For Computer ArchitecturesuryaNo ratings yet

- Time: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14Document3 pagesTime: 03 Hours Maximum Marks: 100: (Autonomous Institution Under VTU) VI Semester B. E. Examinations, May/Jun 14PrateekMandiNo ratings yet

- Illinois Exam2 Practice Solfa08Document4 pagesIllinois Exam2 Practice Solfa08bittronicNo ratings yet

- Comp Architecture Sample QuestionsDocument9 pagesComp Architecture Sample QuestionsMohamaad SihatthNo ratings yet

- cs146 Fall2017 Midterm1xxDocument12 pagescs146 Fall2017 Midterm1xxgrizzyleoNo ratings yet

- Computer Architecture Sample MidtermDocument9 pagesComputer Architecture Sample Midtermkhayat_samirNo ratings yet

- Indian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Document4 pagesIndian Institute of Technology, Kharagpur: Mid-Spring Semester 2021-22Utkarsh PatelNo ratings yet

- Arch June 2020Document3 pagesArch June 2020A7a WtfNo ratings yet

- Master of Computer Applications (MCA) : MCA/ASSIGN/I/YEAR/2014Document17 pagesMaster of Computer Applications (MCA) : MCA/ASSIGN/I/YEAR/2014Krishna PatelNo ratings yet

- Attempt All of The Following QuestionsDocument5 pagesAttempt All of The Following Questionssoli0snakeNo ratings yet

- Architecture ComputerDocument3 pagesArchitecture Computerlillyren2808No ratings yet

- Bachelor of Computer Applications (Revised Syllabus) : Assignments (For July, 2014 and Jan., 2015 Sessions)Document9 pagesBachelor of Computer Applications (Revised Syllabus) : Assignments (For July, 2014 and Jan., 2015 Sessions)Ashis PradhanNo ratings yet

- Quiz 1Document12 pagesQuiz 1RexChandu100% (1)

- Computer Science Textbook Solutions - 13Document30 pagesComputer Science Textbook Solutions - 13acc-expertNo ratings yet

- Quiz For Chapter 1Document12 pagesQuiz For Chapter 1Alejandro Delgadillo DuranNo ratings yet

- High Performance Computer Architecture (CS60003)Document2 pagesHigh Performance Computer Architecture (CS60003)Venkata PranavNo ratings yet

- HW 05Document6 pagesHW 05samadNo ratings yet

- COMP1411 Final Exam Question BookDocument10 pagesCOMP1411 Final Exam Question Bookashtonsamuel2121No ratings yet

- EXAMDec2012 SolutionDocument8 pagesEXAMDec2012 Solutionخالد ناهض نايف نجمNo ratings yet

- 21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Document4 pages21CS34 SIMP Questions - 21SCHEME: Module-1 (Study Any 5 Questions)Rohan RNo ratings yet

- Tutorial Sheet2014Document7 pagesTutorial Sheet2014Julia DanielNo ratings yet

- Computer Architecture Midterm1 CmuDocument30 pagesComputer Architecture Midterm1 CmuÖzgürCemBirlerNo ratings yet

- FinalDocument4 pagesFinalApinya SUTHISOPHAARPORNNo ratings yet

- GATE 2011 Computer Science Engineering Set - C: Q.1 - Q.25 Carry One Mark EachDocument20 pagesGATE 2011 Computer Science Engineering Set - C: Q.1 - Q.25 Carry One Mark EachKanchan AroraNo ratings yet

- Exercises 1 Assembly and Machine Languages: Number SystemsDocument3 pagesExercises 1 Assembly and Machine Languages: Number SystemsThomas WangNo ratings yet

- CSA 2022 Sess2Document2 pagesCSA 2022 Sess2ahmed khanNo ratings yet

- Ajaykumargargengineeringcollege, Ghaziabad: Department of CseDocument2 pagesAjaykumargargengineeringcollege, Ghaziabad: Department of CseAmardeep SinghNo ratings yet

- Computer Organization Jan 2010Document2 pagesComputer Organization Jan 2010Prasad C MNo ratings yet

- Exam2 Fa2014 SolutionDocument14 pagesExam2 Fa2014 Solutionrafeak rafeakNo ratings yet

- Wa0002 PDFDocument39 pagesWa0002 PDFSreenath SreeNo ratings yet

- Hsslive - In: Computer ApplicationsDocument79 pagesHsslive - In: Computer Applicationspirated wallahNo ratings yet

- AP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceFrom EverandAP Computer Science Principles: Student-Crafted Practice Tests For ExcellenceNo ratings yet

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemFrom EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Practical Numerical C Programming: Finance, Engineering, and Physics ApplicationsFrom EverandPractical Numerical C Programming: Finance, Engineering, and Physics ApplicationsNo ratings yet

- Computer Knowledge Bit Bank for All Competitive ExamsFrom EverandComputer Knowledge Bit Bank for All Competitive ExamsRating: 4 out of 5 stars4/5 (4)

- Designing An FPGA-Based Reader - ArticuloDocument4 pagesDesigning An FPGA-Based Reader - ArticuloRaul Crespo SaucedoNo ratings yet

- Ugreen Hitune True Wireless Earbuds Ws100 User ManualDocument16 pagesUgreen Hitune True Wireless Earbuds Ws100 User Manualtheron25No ratings yet

- W 48 × H 48 MM Power ON Delay Analog Timers: ATE8 SeriesDocument3 pagesW 48 × H 48 MM Power ON Delay Analog Timers: ATE8 Seriesyanier martinezNo ratings yet

- 5 Emc Techniques For Heatsinks TasterDocument5 pages5 Emc Techniques For Heatsinks Tasterhugo parraNo ratings yet

- Advanced Light Streak TutorialDocument21 pagesAdvanced Light Streak Tutorialerne1813No ratings yet

- Intel® Desktop Compatibility Tool: More InformationDocument51 pagesIntel® Desktop Compatibility Tool: More InformationdrdivishNo ratings yet

- GoodWE Product Page - DNS - AllDocument2 pagesGoodWE Product Page - DNS - AllImtiaz NNo ratings yet

- Cse IIIDocument47 pagesCse IIIJagan NathanNo ratings yet

- Colt 5dr Acc Bro1Document14 pagesColt 5dr Acc Bro1Samyaza ShemyazazNo ratings yet

- RRU Hardware Maintenance Guide (04) (PDF) - enDocument22 pagesRRU Hardware Maintenance Guide (04) (PDF) - enKamalKhanNo ratings yet

- Bentone BG 400 Manual de InstalacionDocument44 pagesBentone BG 400 Manual de InstalacionCarlos Baeza100% (1)

- Current Transformers Installation QuizDocument12 pagesCurrent Transformers Installation QuizsamNo ratings yet

- TRM 104Document2 pagesTRM 104Dennis RimandoNo ratings yet

- Cummins GensetDocument4 pagesCummins GensetBenny S PutraNo ratings yet

- p320h 2 5 SSD Product Brief LoDocument2 pagesp320h 2 5 SSD Product Brief LoMark ReinhardtNo ratings yet

- Battery Charging Guide - 6 VoltDocument5 pagesBattery Charging Guide - 6 VoltKidus DawitNo ratings yet

- Untitled DiagramDocument1 pageUntitled DiagramirfanNo ratings yet

- High Speed Modified Booth's Multiplier For Signed and Unsigned NumbersDocument8 pagesHigh Speed Modified Booth's Multiplier For Signed and Unsigned NumbersInternational Journal of Science and Engineering InvestigationsNo ratings yet

- FTK 1115 B PDFDocument10 pagesFTK 1115 B PDFnorshazlinNo ratings yet

- Airmux-200: Broadband Wireless MultiplexerDocument8 pagesAirmux-200: Broadband Wireless MultiplexerAbu FadilahNo ratings yet

- FMIL Pianos and Benches RETAIL Prices MAY E-MailDocument8 pagesFMIL Pianos and Benches RETAIL Prices MAY E-MailPalanisamy BalasubramaniNo ratings yet

- A100D-CE-04 Product General DescriptionDocument5 pagesA100D-CE-04 Product General DescriptionSurta DevianaNo ratings yet

- Electronic Measurments Instrumentation Eec403Document1 pageElectronic Measurments Instrumentation Eec403Brahmanand SinghNo ratings yet

- Mason S Flow Graph Formula PDFDocument21 pagesMason S Flow Graph Formula PDFRUBIONo ratings yet

- XAudio2 High Performance Considerations USDocument32 pagesXAudio2 High Performance Considerations USJose QuillahuamanNo ratings yet

- EC 3150 Label Printer (Win7 32bit) - InstructionDocument39 pagesEC 3150 Label Printer (Win7 32bit) - InstructionMarcelino Navarrete EvaristoNo ratings yet

- GlobcomDocument96 pagesGlobcomvacuumNo ratings yet

- Mastering Linux Kernel DevelopmentDocument346 pagesMastering Linux Kernel Developmentatom tux100% (2)

- Option Details: Synchrotact 6Document1 pageOption Details: Synchrotact 6Žarko MočnikNo ratings yet