Professional Documents

Culture Documents

PHB 55n03lta Logic Level Fet

PHB 55n03lta Logic Level Fet

Uploaded by

yusufwpOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

PHB 55n03lta Logic Level Fet

PHB 55n03lta Logic Level Fet

Uploaded by

yusufwpCopyright:

Available Formats

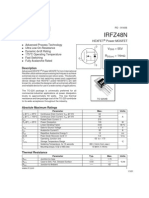

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

Rev. 04 4 September 2002 Product data

1. Description

N-channel logic level eld-effect power transistor in a plastic package using TrenchMOS technology. Product availability: PHP55N03LTA in a SOT78 (TO-220AB) PHB55N03LTA in a SOT404 (D2-PAK) PHD55N03LTA in a SOT428 (D-PAK).

2. Features

s Low on-state resistance s Fast switching.

3. Applications

s Computer motherboard high frequency DC to DC converters.

4. Pinning information

Table 1: Pinning - SOT78, SOT404, SOT428 simplied outlines and symbol Simplied outline

mb mb mb

Pin Description 1 2 3 mb gate (g) drain (d) source (s) mounting base, connected to drain (d)

[1]

Symbol

d

g s

2 2 1

MBK106

MBB076

1 3

MBK116

3

MBK091

Top view

1 2 3

SOT78 (TO-220AB)

[1]

SOT404 (D2-PAK)

SOT428 (D-PAK)

It is not possible to make connection to pin 2 of the SOT404 and SOT428 packages.

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

5. Quick reference data

Table 2: VDS ID Ptot Tj RDSon Quick reference data Conditions 25 C Tj 175 C Tmb = 25 C; VGS = 5 V Tmb = 25 C VGS = 10 V; ID = 25 A; Tj = 25 C VGS = 5 V; ID = 25 A; Tj = 25 C Typ 11 15 Max 25 55 85 175 14 18 Unit V A W C m m drain-source voltage (DC) drain current (DC) total power dissipation junction temperature drain-source on-state resistance Symbol Parameter

6. Limiting values

Table 3: Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Symbol Parameter VDS VDGR ID VGS IDM Ptot Tstg Tj IS ISM drain-source voltage (DC) drain-gate voltage (DC) drain current (DC) gate-source voltage peak drain current total power dissipation storage temperature junction temperature source (diode forward) current (DC) Tmb = 25 C peak source (diode forward) current Tmb = 25 C; pulsed; tp 10 s unclamped inductive load; ID = 25 A; tp = 0.1 ms; VDD = 15 V; RGS = 50 ; VGS = 5V; starting Tj = 25 C Tmb = 25 C; pulsed; tp 10 s; Figure 3 Tmb = 25 C; Figure 1 Conditions 25 C Tj 175 C 25 C Tj 175 C; RGS = 20 k Tmb = 25 C; VGS = 5 V; Figure 2 and 3 Tmb = 100 C; VGS = 5 V; Figure 2 Min 55 55 Max 25 25 55 38 20 220 85 +175 +175 55 220 60 Unit V V A A V A W C C A A mJ

Source-drain diode

Avalanche ruggedness EDS(AL)S non-repetitive drain-source avalanche energy

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

2 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

120 Pder (%) 80

03aa16

120 Ider (%) 80

03aa24

40

40

0 0 50 100 150 200 Tmb ( C)

0 0 50 100 150 200 Tmb ( C)

P tot P der = ---------------------- 100 % P

tot ( 25 C )

ID I der = ------------------ 100 % I

D ( 25 C )

Fig 1. Normalized total power dissipation as a function of mounting base temperature.

Fig 2. Normalized continuous drain current as a function of mounting base temperature.

103 ID (A)

03ae64

Limit RDSon = VDS / ID

tp = 10 s

102 100 s

10

DC

1 ms 10 ms 100 ms

1 1 10 VDS (V) 102

Tmb = 25 C; IDM is single pulse.

Fig 3. Safe operating area; continuous and peak drain currents as a function of drain-source voltage.

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

3 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

7. Thermal characteristics

Table 4: Rth(j-mb) Rth(j-a) Thermal characteristics Conditions Min Typ Max Unit 60 75 50 1.75 K/W K/W K/W K/W thermal resistance from junction to mounting base Figure 4 thermal resistance from junction to ambient SOT78 SOT428 SOT404 and SOT428 vertical in still air SOT428 minimum footprint; mounted on a PCB SOT404 minimum footprint; mounted on a PCB Symbol Parameter

7.1 Transient thermal impedance

10 Zth(j-mb) (K/W)

03ae63

= 0.5

0.2 0.1 10-1 0.05 0.02 P = tp T

single pulse 10-2 10-5

tp T 10-4 10-3 10-2 10-1

tp (s)

Fig 4. Transient thermal impedance from junction to mounting base as a function of pulse duration.

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

4 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

8. Characteristics

Table 5: Characteristics Tj = 25 C unless otherwise specied. Symbol Parameter Static characteristics V(BR)DSS drain-source breakdown voltage ID = 0.25 mA; VGS = 0 V Tj = 25 C Tj = 55 C VGS(th) gate-source threshold voltage ID = 1 mA; VDS = VGS; Figure 9 Tj = 25 C Tj = 175 C Tj = 55 C IDSS drain-source leakage current VDS = 25 V; VGS = 0 V Tj = 25 C Tj = 175 C IGSS RDSon gate-source leakage current drain-source on-state resistance VGS = 5 V; VDS = 0 V VGS = 5 V; ID = 25 A; Figure 7 and 8 Tj = 25 C Tj = 175 C VGS = 10 V; ID = 25 A Tj = 25 C Dynamic characteristics gfs Qg(tot) Qgs Qgd Ciss Coss Crss td(on) tr td(off) tf VSD forward transconductance total gate charge gate-source charge gate-drain (Miller) charge input capacitance output capacitance reverse transfer capacitance turn-on delay time rise time turn-off delay time fall time source-drain (diode forward) voltage IS = 25 A; VGS = 0 V; Figure 12 IS = 55 A; VGS = 0 V VDD = 15 V; ID = 55 A; VGS = 10 V; RG = 5 VGS = 0 V; VDS = 25 V; f = 1 MHz; Figure 11 VDS = 25 V; ID = 25 A ID = 55 A; VDD = 15 V; VGS = 5 V; Figure 13 32 20 8 7 950 340 230 8 45 45 40 0.95 1.2 15 80 80 60 1.2 S nC nC nC pF pF pF ns ns ns ns V V 11 14 m 15 25.5 18 30.6 m m 0.05 10 10 500 100 A A nA 1 0.5 1.5 2 2.3 V V V 25 22 V V Conditions Min Typ Max Unit

Source-drain diode

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

5 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

60 ID (A) Tj = 25 C 10 V 5 V 4.5 V

03ae65

60 ID (A) 40 VDS > ID x RDSon

03ae67

4V

40 3.5 V

Tj = 25 C

175 C

20 3V

20

VGS = 2.5 V 0 0 0.5 1 1.5 VDS (V) 2 0 0 1 2 3 4 5 VGS (V)

Tj = 25 C

Tj = 25 C and 175 C; VDS > ID x RDSon

Fig 5. Output characteristics: drain current as a function of drain-source voltage; typical values.

Fig 6. Transfer characteristics: drain current as a function of gate-source voltage; typical values.

0.03 RDSon () Tj = 25 C

03ae66

2 a 1.5

03ad57

VGS = 4 V

0.02

4.5 V 5V 1 10 V 0.5

0.01

0 0 20 40 ID (A) 60

0 -60 0 60 120 Tj (C) 180

Tj = 25 C

R DSon a = --------------------------R DSon ( 25 C )

Fig 7. Drain-source on-state resistance as a function of drain current; typical values.

Fig 8. Normalized drain-source on-state resistance factor as a function of junction temperature.

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

6 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

2.5 VGS(th) (V) 2 max

03aa33

10-1 ID (A) 10-2

03aa36

1.5

typ

10-3 min typ max

min

10-4

0.5

10-5

0 -60 0 60 120 Tj (C) 180

10-6 0 1 2 VGS (V) 3

ID = 1 mA; VDS = VGS

Tj = 25 C; VDS = 5 V

Fig 9. Gate-source threshold voltage as a function of junction temperature.

Fig 10. Sub-threshold drain current as a function of gate-source voltage.

104

03ae70

C (pF)

103

Ciss

Coss Crss 102 10-1

10

VDS (V)

102

VGS = 0 V; f = 1 MHz

Fig 11. Input, output and reverse transfer capacitances as a function of drain-source voltage; typical values.

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

7 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

60 IS (A) 40 VGS = 0 V

03ae69

10 VGS (V) 8 ID = 55 A Tj = 25 C VDD = 15 V 6

03ae71

4 20 175 C Tj = 25 C 2

0 0 0.3 0.6 0.9 VSD (V) 1.2

0 0 10 20 30 Q (nC) 40 G

Tj = 25 C and 175 C; VGS = 0 V

ID = 55 A; VDD = 15 V

Fig 12. Source (diode forward) current as a function of source-drain (diode forward) voltage; typical values.

Fig 13. Gate-source voltage as a function of gate charge; typical values.

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

8 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

9. Package outline

Plastic single-ended package; heatsink mounted; 1 mounting hole; 3-lead TO-220AB SOT78

E p

A A1 q

D1

mounting base

L1(1)

L2 Q

b1

3

b c

5 scale

10 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A 4.5 4.1 A1 1.39 1.27 b 0.9 0.7 b1 1.3 1.0 c 0.7 0.4 D 15.8 15.2 D1 6.4 5.9 E 10.3 9.7 e 2.54 L 15.0 13.5 L1(1) 3.30 2.79 L2 max. 3.0 p 3.8 3.6 q 3.0 2.7 Q 2.6 2.2

Note 1. Terminals in this zone are not tinned. OUTLINE VERSION SOT78 REFERENCES IEC JEDEC 3-lead TO-220AB EIAJ SC-46 EUROPEAN PROJECTION ISSUE DATE 00-09-07 01-02-16

Fig 14. SOT78 (TO-220AB).

9397 750 10143 Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

9 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

Plastic single-ended surface mounted package (Philips version of D2-PAK); 3 leads (one lead cropped)

SOT404

A E A1 mounting base

D1

HD

2

Lp

3

b c Q

2.5 scale

5 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A 4.50 4.10 A1 1.40 1.27 b 0.85 0.60 c 0.64 0.46 D max. 11 D1 1.60 1.20 E 10.30 9.70 e 2.54 Lp 2.90 2.10 HD 15.80 14.80 Q 2.60 2.20

OUTLINE VERSION SOT404

REFERENCES IEC JEDEC EIAJ

EUROPEAN PROJECTION

ISSUE DATE 99-06-25 01-02-12

Fig 15. SOT404 (D2-PAK)

9397 750 10143 Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

10 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

Plastic single-ended surface mounted package (Philips version of D-PAK); 3 leads (one lead cropped)

SOT428

seating plane y A E b2 A A1 mounting base A2 E1

D1 D HE L2

2

L L1

1

b1 e e1 b

3

w M A c

10 scale

20 mm

DIMENSIONS (mm are the original dimensions) UNIT mm A 2.38 2.22 A1(1) 0.65 0.45 A2 0.93 0.73 b 0.89 0.71 b1 1.1 0.9 b2 5.46 5.26 c 0.4 0.2 D 6.22 5.98 D1 min. 4.0 E 6.73 6.47 E1 e e1 HE 10.4 9.6 L 2.95 2.55 L1 min. 0.5 L2 0.9 0.5 w 0.2 y max. 0.2

4.81 2.285 4.57 4.45

Note 1. Measured from heatsink back to lead. OUTLINE VERSION SOT428 REFERENCES IEC JEDEC TO-252 JEITA SC-63 EUROPEAN PROJECTION ISSUE DATE 99-09-13 01-12-11

Fig 16. SOT428 (D-PAK)

9397 750 10143 Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

11 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

10. Revision history

Table 6: 04 Revision history CPCN Description Product data (9397 750 10143) Modications:

Rev Date 20020904

Changes to Table 3 Limiting values EDS(AL)S correction of typographical error in test conditions IDS(AL)S entry removed

03 02 01

20020221 20010801 20010330

Product data (9397 750 09288) Product data (9397 750 08642) Product data (9397 750 08149)

9397 750 10143

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

12 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

11. Data sheet status

Data sheet status[1] Objective data Preliminary data Product status[2] Development Qualication Denition This data sheet contains data from the objective specication for product development. Philips Semiconductors reserves the right to change the specication in any manner without notice. This data sheet contains data from the preliminary specication. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specication without notice, in order to improve the design and supply the best possible product. This data sheet contains data from the product specication. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Changes will be communicated according to the Customer Product/Process Change Notication (CPCN) procedure SNW-SQ-650A.

Product data

Production

[1] [2]

Please consult the most recently issued data sheet before initiating or completing a design. The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

12. Denitions

Short-form specication The data in a short-form specication is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook. Limiting values denition Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specication is not implied. Exposure to limiting values for extended periods may affect device reliability. Application information Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specied use without further testing or modication.

13. Disclaimers

Life support These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application. Right to make changes Philips Semiconductors reserves the right to make changes, without notice, in the products, including circuits, standard cells, and/or software, described or contained herein in order to improve design and/or performance. Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no licence or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specied.

14. Trademarks

TrenchMOS is a trademark of Koninklijke Philips Electronics N.V.

Contact information

For additional information, please visit http://www.semiconductors.philips.com. For sales ofce addresses, send e-mail to: sales.addresses@www.semiconductors.philips.com.

9397 750 10143

Fax: +31 40 27 24825

Koninklijke Philips Electronics N.V. 2002. All rights reserved.

Product data

Rev. 04 4 September 2002

13 of 14

Philips Semiconductors

PHP/PHB/PHD55N03LTA

TrenchMOS Logic Level FET

Contents

1 2 3 4 5 6 7 7.1 8 9 10 11 12 13 14 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 Pinning information . . . . . . . . . . . . . . . . . . . . . . 1 Quick reference data . . . . . . . . . . . . . . . . . . . . . 2 Limiting values . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Thermal characteristics. . . . . . . . . . . . . . . . . . . 4 Transient thermal impedance . . . . . . . . . . . . . . 4 Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . 5 Package outline . . . . . . . . . . . . . . . . . . . . . . . . . 9 Revision history . . . . . . . . . . . . . . . . . . . . . . . . 12 Data sheet status . . . . . . . . . . . . . . . . . . . . . . . 13 Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Disclaimers . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13 Trademarks. . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Koninklijke Philips Electronics N.V. 2002. Printed in The Netherlands

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights. Date of release: 4 September 2002 Document order number: 9397 750 10143

This datasheet has been downloaded from: www.DatasheetCatalog.com Datasheets for electronic components.

You might also like

- Switching Power Supply Design: A Concise Practical HandbookFrom EverandSwitching Power Supply Design: A Concise Practical HandbookNo ratings yet

- Atx Power Supply PFC SchematicDocument1 pageAtx Power Supply PFC SchematicBere Alonzo100% (2)

- Bombardier CRJ 200-Automatic Flight Control SystemDocument28 pagesBombardier CRJ 200-Automatic Flight Control SystemHarish Iyengar100% (1)

- PHD 98 N 03Document14 pagesPHD 98 N 03Kevin TateNo ratings yet

- BUK7511-55A BUK7611-55A: 1. DescriptionDocument15 pagesBUK7511-55A BUK7611-55A: 1. DescriptionziminautaNo ratings yet

- D13N03LTDocument12 pagesD13N03LTmarquitos550bNo ratings yet

- Pmv65Xp: 1. Product ProfileDocument12 pagesPmv65Xp: 1. Product Profilealoksharma20No ratings yet

- Buk9237 55aDocument13 pagesBuk9237 55aOlga PlohotnichenkoNo ratings yet

- Description: N-Channel Enhancement Mode Field-Effect TransistorDocument14 pagesDescription: N-Channel Enhancement Mode Field-Effect TransistorFernando Gonzales SanchezNo ratings yet

- BUK7508-55A: 1. Product ProfileDocument14 pagesBUK7508-55A: 1. Product Profilejalvarez_385073No ratings yet

- N-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DataDocument10 pagesN-Channel Trenchmos Transistor Irf540, Irf540S: Features Symbol Quick Reference DatathedrodNo ratings yet

- BUK951R6-30E: 1. Product ProfileDocument13 pagesBUK951R6-30E: 1. Product ProfileTom BeanNo ratings yet

- IRFZ48NDocument8 pagesIRFZ48NLuay IssaNo ratings yet

- Irl 1004Document9 pagesIrl 1004Luiz RvNo ratings yet

- Dual N-Channel Enhancement Mode Phn210T Trenchmos TransistorDocument8 pagesDual N-Channel Enhancement Mode Phn210T Trenchmos TransistorCristian ViolaNo ratings yet

- N-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference DataDocument9 pagesN-Channel Trenchmos Transistor Irf630, Irf630S: Features Symbol Quick Reference Datalord mace tyrellNo ratings yet

- Irlz 24 NDocument9 pagesIrlz 24 NRobson PontinNo ratings yet

- Irfz 48 VDocument8 pagesIrfz 48 VZoltán HalászNo ratings yet

- N-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataDocument9 pagesN-Channel Enhancement Mode Bsp100 Trenchmos Transistor: Features Symbol Quick Reference DataroozbehxoxNo ratings yet

- Fdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MDocument11 pagesFdd8896 / Fdu8896: N-Channel Powertrench Mosfet 30V, 94A, 5.7MKevin TateNo ratings yet

- 4,, Psmn4r8-100bseDocument13 pages4,, Psmn4r8-100bseWelly N HealtantoNo ratings yet

- N-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Document11 pagesN-Channel Powertrench Mosfet 30V, 58A, 9M: April 2008Kevin TateNo ratings yet

- CD22100 - DataSheetDocument10 pagesCD22100 - DataSheetHao ChungNo ratings yet

- BLF244Document16 pagesBLF244Luis AlfredoNo ratings yet

- FDP5N50U / FDPF5N50UT: Ultra FRFETDocument10 pagesFDP5N50U / FDPF5N50UT: Ultra FRFETtecnologo456No ratings yet

- Irfz46n PDFDocument9 pagesIrfz46n PDFYunier FernandezNo ratings yet

- IRF650B / IRFS650B: 200V N-Channel MOSFETDocument10 pagesIRF650B / IRFS650B: 200V N-Channel MOSFETbinoelNo ratings yet

- IRL540NDocument8 pagesIRL540Nmestek123No ratings yet

- P-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataDocument7 pagesP-Channel Enhancement Mode BSH205 MOS Transistor: Features Symbol Quick Reference DataKumar Amit VermaNo ratings yet

- K 3918Document8 pagesK 3918Anderson DuarteNo ratings yet

- Irfz 34 NLDocument10 pagesIrfz 34 NLguerrero_27No ratings yet

- Irfi 3205 Power MosfetDocument9 pagesIrfi 3205 Power MosfetAndy WilsonNo ratings yet

- N 308 ApDocument11 pagesN 308 Apdragon-red0816No ratings yet

- IRF3710Document8 pagesIRF3710Andrés MorochoNo ratings yet

- Irfp 260 NDocument9 pagesIrfp 260 NJolaine MojicaNo ratings yet

- Power Transistor: SPP17N80C3 SPA17N80C3 Cool MOS™Document13 pagesPower Transistor: SPP17N80C3 SPA17N80C3 Cool MOS™cmlcaldeira10No ratings yet

- B44P04Document7 pagesB44P04aldo_suviNo ratings yet

- Irfr3707Zpbf Irfu3707Zpbf: V R Max QGDocument11 pagesIrfr3707Zpbf Irfu3707Zpbf: V R Max QGJared RobisonNo ratings yet

- Irf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsDocument6 pagesIrf7811Avpbf Irf7811Avpbf: Absolute Maximum RatingsnewmailsNo ratings yet

- FQPF8N80CDocument11 pagesFQPF8N80CWsad WsadNo ratings yet

- IRFZ48 55V-64A 140W-N-channelenhancemenT PDFDocument8 pagesIRFZ48 55V-64A 140W-N-channelenhancemenT PDFZxdIaminxXzlovewithzxXzyouzxNo ratings yet

- 5305SDocument10 pages5305SHugo Camacho RamirezNo ratings yet

- Pmv65Xp: 1. General DescriptionDocument14 pagesPmv65Xp: 1. General DescriptionDustin JacksonNo ratings yet

- 01 Ufshsi 4 Pczuf 2 FKWKTC 7 PDG 1 PyDocument9 pages01 Ufshsi 4 Pczuf 2 FKWKTC 7 PDG 1 PyPuti Benny LakraNo ratings yet

- Irf740b PDFDocument10 pagesIrf740b PDFMed SamiNo ratings yet

- Mosfet 10NM60NDocument19 pagesMosfet 10NM60NRicardo Misael Torres0% (1)

- FQP13N50: N-Channel QFET MosfetDocument8 pagesFQP13N50: N-Channel QFET MosfetaldoNo ratings yet

- Irlr 7843Document12 pagesIrlr 7843Idris LMNo ratings yet

- B35N04Document7 pagesB35N04aldo_suviNo ratings yet

- IRF540NDocument7 pagesIRF540Nmichaelliu123456No ratings yet

- Irf7205pbf Datasheet MosfetDocument9 pagesIrf7205pbf Datasheet Mosfetnithinmundackal3623No ratings yet

- Advanced Power Electronics Corp.: AP85T03GH/JDocument6 pagesAdvanced Power Electronics Corp.: AP85T03GH/JfjlopeztecnicNo ratings yet

- Fdms0308Cs: N-Channel Powertrench SyncfetDocument8 pagesFdms0308Cs: N-Channel Powertrench Syncfetdreyes3773No ratings yet

- FQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETDocument9 pagesFQB30N06L / FQI30N06L: 60V LOGIC N-Channel MOSFETsoweloNo ratings yet

- Mos Field Effect Transistor: Switching N-Channel Power Mos FetDocument7 pagesMos Field Effect Transistor: Switching N-Channel Power Mos FetLuis Antonio Arévalo SifontesNo ratings yet

- Irfps 3810 PBFDocument8 pagesIrfps 3810 PBFCrisan Radu-HoreaNo ratings yet

- Coolmos Power Transistor: Features Product SummaryDocument10 pagesCoolmos Power Transistor: Features Product SummaryAnais Cullon BermejoNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to DisplaysNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- ZXLD1360: V GND LXDocument25 pagesZXLD1360: V GND LXyusufwpNo ratings yet

- AN-202 - An IC Amplifier User's Guide To Decoupling - Grounding - and Making Things Go Right For A ChangeDocument8 pagesAN-202 - An IC Amplifier User's Guide To Decoupling - Grounding - and Making Things Go Right For A ChangeyusufwpNo ratings yet

- IRFP460Document9 pagesIRFP460yusufwpNo ratings yet

- Tutorial para Usar El TL494Document32 pagesTutorial para Usar El TL494Marlon Isaac CortesNo ratings yet

- 2SK117Document5 pages2SK117yusufwpNo ratings yet

- AD7710 EvalBoard AppNoteDocument8 pagesAD7710 EvalBoard AppNoteyusufwpNo ratings yet

- AN556 - Implementing A Table ReadDocument5 pagesAN556 - Implementing A Table ReadyusufwpNo ratings yet

- MMA7455 3 Axis Accelerometer Documentation v1.1Document7 pagesMMA7455 3 Axis Accelerometer Documentation v1.1mamamedusaNo ratings yet

- Uc284xa Uc384xaDocument16 pagesUc284xa Uc384xayusufwpNo ratings yet

- LTC2440 PDFDocument28 pagesLTC2440 PDFyusufwpNo ratings yet

- CA3080Document12 pagesCA3080yusufwpNo ratings yet

- Eim AssessmentDocument7 pagesEim AssessmentMike Lyster Alvarez100% (1)

- SP791 Data SheetsDocument19 pagesSP791 Data SheetstarpinoNo ratings yet

- 2020 Model XDocument62 pages2020 Model XSimon Alvarez50% (2)

- Operational Amplifier 741 As Mono Stable Multi Vibrator 1Document5 pagesOperational Amplifier 741 As Mono Stable Multi Vibrator 1Gayan WijethilakaNo ratings yet

- EN - RGB Pilot - Ultrasonic Spec SheetDocument1 pageEN - RGB Pilot - Ultrasonic Spec Sheettito_matrixNo ratings yet

- Diodos Zener Bzx55c-SeriesDocument3 pagesDiodos Zener Bzx55c-SeriesLuis Enrique De los Santos FarfánNo ratings yet

- Bzx84 SeriesDocument11 pagesBzx84 SeriesonafetsNo ratings yet

- Controlador MCCDocument4 pagesControlador MCCJuan RiosNo ratings yet

- Unix Internals Unix Internals: Introduction To Kernel Introduction To KernelDocument71 pagesUnix Internals Unix Internals: Introduction To Kernel Introduction To Kernelkumar nNo ratings yet

- Lab - 3 - Multistage CE AmplifierDocument18 pagesLab - 3 - Multistage CE AmplifierANo ratings yet

- Nemo FSR1: For GSM and WCDMA Wireless NetworksDocument2 pagesNemo FSR1: For GSM and WCDMA Wireless Networksashu guptaNo ratings yet

- Fral FDNF44 ManualDocument8 pagesFral FDNF44 ManualmoisturecarevidsNo ratings yet

- Canon F1 ManualDocument64 pagesCanon F1 Manualvaldormarhauslendale0% (1)

- DCR-TRV240 - 340DCR-TRV240 - 340 L2-v1 L2-v1 (1) .3Document181 pagesDCR-TRV240 - 340DCR-TRV240 - 340 L2-v1 L2-v1 (1) .3domisoftNo ratings yet

- Field Visit ReportDocument5 pagesField Visit Reportpramod100% (1)

- Electrician IntroductionDocument33 pagesElectrician Introductionsnadeem07No ratings yet

- ELE291 Test 2 Q SEM MARCH - JULY 2022Document2 pagesELE291 Test 2 Q SEM MARCH - JULY 2022Hamzah أسَدُ أللَّهNo ratings yet

- Eurotherm Drives Product Catalog DC DrivesDocument6 pagesEurotherm Drives Product Catalog DC DrivesYahyaMoummouNo ratings yet

- Addition of Hydrohalogenic Acids To Alkenes in Aqueous-Organic, Two-Phase Systems in The Presence of Catalytic Amounts of Onium Salts PDFDocument3 pagesAddition of Hydrohalogenic Acids To Alkenes in Aqueous-Organic, Two-Phase Systems in The Presence of Catalytic Amounts of Onium Salts PDFatomoscoNo ratings yet

- 0 - Cover Page-Index (Section II A)Document3 pages0 - Cover Page-Index (Section II A)owngauravNo ratings yet

- X25 XXX 01 SP E-1Document15 pagesX25 XXX 01 SP E-1Richard ZerpaNo ratings yet

- Chapter 8 Bipolar Junction Transistors: Question: What Is The Meaning of "Bipolar" ?Document43 pagesChapter 8 Bipolar Junction Transistors: Question: What Is The Meaning of "Bipolar" ?廖學儒No ratings yet

- Double Stub and LC Matching CircuitDocument31 pagesDouble Stub and LC Matching CircuitVijay ReddyNo ratings yet

- Monitoring Port Noise Levels: To Reduce Community ImpactDocument4 pagesMonitoring Port Noise Levels: To Reduce Community ImpactmanuelNo ratings yet

- Lightning Arrester Lightningcontroller MC 125-B/Npe: Operation and Fields of ApplicationDocument2 pagesLightning Arrester Lightningcontroller MC 125-B/Npe: Operation and Fields of ApplicationAnas BasarahNo ratings yet

- GM0465RDocument18 pagesGM0465RautreraNo ratings yet

- Dzexams 4am Anglais t1 20161 101910 PDFDocument3 pagesDzexams 4am Anglais t1 20161 101910 PDFCybernet NetwebNo ratings yet

- ch01 PDFDocument52 pagesch01 PDF潘呈洋No ratings yet

- Course No: EEE-402: Bangladesh University of Engineering and TechnologyDocument3 pagesCourse No: EEE-402: Bangladesh University of Engineering and Technologyসেলিম সরকার মায়েলNo ratings yet