Professional Documents

Culture Documents

Dravhandling Moradi

Dravhandling Moradi

Uploaded by

Abhilash OSCopyright:

Available Formats

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5823)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1093)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (852)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (898)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (541)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (349)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (823)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (403)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Dark Demon - Christine FeehanDocument4 pagesDark Demon - Christine Feehantheresa1970No ratings yet

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- SpokenTutorialExpertise AnInsight PDFDocument2 pagesSpokenTutorialExpertise AnInsight PDFAbhilash OSNo ratings yet

- PSpice Part ListDocument678 pagesPSpice Part Listmac50% (4)

- Voltagemultiplier AMOSDocument3 pagesVoltagemultiplier AMOSAbhilash OSNo ratings yet

- Infra Red Detectors: M. Tech Credit Seminar Report, Electronic Systems Group, EE Dept, IIT Bombay Submitted Oct O4Document28 pagesInfra Red Detectors: M. Tech Credit Seminar Report, Electronic Systems Group, EE Dept, IIT Bombay Submitted Oct O4Tan HuynhNo ratings yet

- DSP Lab 2Document4 pagesDSP Lab 2Abhilash OSNo ratings yet

- AIC Ch12 PDFDocument44 pagesAIC Ch12 PDFAbhilash OSNo ratings yet

- Abhilash O.S: Career ObjectiveDocument4 pagesAbhilash O.S: Career ObjectiveAbhilash OSNo ratings yet

- Lecture 0Document23 pagesLecture 0Abhilash OSNo ratings yet

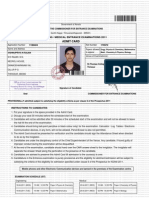

- Engineering / Medical Entrance Examinations 2011: Admit CardDocument1 pageEngineering / Medical Entrance Examinations 2011: Admit CardAbhilash OSNo ratings yet

- Election Dispute ResolutionDocument3 pagesElection Dispute ResolutionOly VerNo ratings yet

- Advanced Solo Encyclopedia Vol 1 PART 1 1 41 PDFDocument41 pagesAdvanced Solo Encyclopedia Vol 1 PART 1 1 41 PDFcolintb1100% (1)

- CH 6. Binomial Theorem (Math +1)Document26 pagesCH 6. Binomial Theorem (Math +1)Dinesh BabuNo ratings yet

- Violations of OLSDocument64 pagesViolations of OLSOisín Ó CionaoithNo ratings yet

- What Is Critical Pedagogy?: A Summary of The Work of Paulo Freire & His ContemporariesDocument38 pagesWhat Is Critical Pedagogy?: A Summary of The Work of Paulo Freire & His ContemporariesS. Ma. Elisabeth Ngewi,rvmNo ratings yet

- Middle School Lesson PlanDocument3 pagesMiddle School Lesson Planapi-339151467No ratings yet

- Microsoft Power Point - Organsiational Culture MSC Revised 1010Document6 pagesMicrosoft Power Point - Organsiational Culture MSC Revised 1010mattstewartis9589No ratings yet

- The Final Appeal To Mankind Nikolai LevashovDocument216 pagesThe Final Appeal To Mankind Nikolai LevashovvickieNo ratings yet

- Multi TextDocument10 pagesMulti Textkexley6900No ratings yet

- Life of PIDocument2 pagesLife of PIIulian UngureanuNo ratings yet

- Asm 324Document2 pagesAsm 324MaximbspChattisgarhNo ratings yet

- The Fraud Triangle TheoryDocument2 pagesThe Fraud Triangle Theoryjama jamsNo ratings yet

- Rule 112Document645 pagesRule 112Nemei SantiagoNo ratings yet

- Examen Parcial - Semana 4 INGLESDocument12 pagesExamen Parcial - Semana 4 INGLESClaudia MedinaNo ratings yet

- 3A GR Narrative Tenses KeyDocument2 pages3A GR Narrative Tenses KeyDaria ZialionayaNo ratings yet

- ChatGPT Lords PrayerDocument12 pagesChatGPT Lords PrayerLouis MelgarejoNo ratings yet

- Disco Inferno in CM en EbmDocument1 pageDisco Inferno in CM en EbmMichaelNo ratings yet

- 31 MySQL QuestionsDocument13 pages31 MySQL QuestionsAmit_mahajanNo ratings yet

- No Mind-Map: Map / Pic Pedalogical Strategies Skills / HOT / Kbat Teaching Aids Noble Values Thinking SkillsDocument2 pagesNo Mind-Map: Map / Pic Pedalogical Strategies Skills / HOT / Kbat Teaching Aids Noble Values Thinking Skillscyberbat2008No ratings yet

- STM32 SPI Flash MemDocument19 pagesSTM32 SPI Flash MemimioNo ratings yet

- Nils Persson 2018 Teacher ResumeDocument3 pagesNils Persson 2018 Teacher Resumeapi-379998608No ratings yet

- Educ4000 Curriculum Integration and Differentiation Semester 2 2018 Bentley Campus IntDocument20 pagesEduc4000 Curriculum Integration and Differentiation Semester 2 2018 Bentley Campus Intapi-314401095No ratings yet

- Towards Being A HumanDocument53 pagesTowards Being A HumanlarenNo ratings yet

- SSP 186 - The CAN Data BusDocument29 pagesSSP 186 - The CAN Data Busmas20012No ratings yet

- Word by Word Surah 55 Ar RahmanDocument5 pagesWord by Word Surah 55 Ar RahmanBriliant Dzikrillah littaqwaNo ratings yet

- Common Tropical Disease in ThailandDocument84 pagesCommon Tropical Disease in ThailandDr.Sathaporn KunnathumNo ratings yet

- Asd and SchizophreniaDocument8 pagesAsd and SchizophreniaCarregan AlvarezNo ratings yet

- UNITED PERFUMES - Distributor Price List Jan 12, 2024 - Web DownloadDocument88 pagesUNITED PERFUMES - Distributor Price List Jan 12, 2024 - Web DownloadMe Dicen RoiNo ratings yet

- Events of Disputes AnswersDocument7 pagesEvents of Disputes AnswersMohamed AliNo ratings yet

Dravhandling Moradi

Dravhandling Moradi

Uploaded by

Abhilash OSOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dravhandling Moradi

Dravhandling Moradi

Uploaded by

Abhilash OSCopyright:

Available Formats

University of Oslo

Department of Informatics

Ultra Low Power

Digital Circuit Design

for Wireless Sensor

Network Applications

PhD Thesis

Farshad Moradi

October 2011

Farshad Moradi, 2011

Series of dissertations submitted to the

Faculty of Mathematics and Natural Sciences, University of Oslo

No. 1121

ISSN 1501-7710

All rights reserved. No part of this publication may be

reproduced or transmitted, in any form or by any means, without permission.

Cover: Inger Sandved Anfinsen.

Printed in Norway: AIT Oslo AS.

Produced in co-operation with Unipub.

The thesis is produced by Unipub merely in connection with the

thesis defence. Kindly direct all inquiries regarding the thesis to the copyright

holder or the unit which grants the doctorate.

Ultra Low Power Digital Circuit

Design for Wireless Sensor

Network Applications

Farshad Moradi

Institute of Informatics

UNIVERSITETET I OSLO

October 2011

To my family

[i]

ABSTRACT

Farshad Moradi, PhD, University of Oslo, July 2011, Ultra Low Power Digital Circuit

Design for Wireless Sensor Network Applications, Major advisor: Prof. Dag T. Wisland,

Co-advisors: Prof. Snorre Aunet and Prof. Yngvar Berg

As the CMOS technology continues to scale down into the nano-scale regime, robustness

of the circuit with respect to process variation and soft error are becoming major obstacles

for circuit designers. Storage elements (SRAM, flip-flops) are particularly vulnerable to

process variation and soft errors. Thus, in this work, we have focused on storage elements

to improve the yield loss in SRAM due to process variations and to design a soft error

tolerant flip-flop. SRAMs are particularly vulnerable to failures due to process variation

resulting in reduced yield. The main problem with SRAM is the conflicting requirements

for read stability and writeability. In this work, we propose designs to overcome conflicting

trade-off between read and write stability. Furthermore, new SRAM cells, namely 11T-

SRAM, PMOS access transistor SRAM, are proposed with capability of working at near-

threshold voltages, properly. The effect of body-biasing on SRAM cell is explored to show

improvements from body-biasing in sub-threshold regions. Results show at least 30%

improvement in read noise margin for proposed SRAM cells while write margin is

improved. Furthermore, to overcome short channel effect, different candidate transistor

structures have been investigated to replace the bulk MOSFETs. Among them, FinFET is

considered to be a promising candidate for scaled CMOS devices in sub-22-nm technology

nodes. In this work, by introducing a new device, the read and write stability for SRAM is

improved by 20% and 9% respectively, while performance is improved by 56%compared

to conventional designs. we study the double-gate FinFET SRAM technology-circuit

design space to understand the interplay of device short-channel-effect (SCE), SRAM area,

access time, soft error immunity, stability under process variations and leakage. Several

Flip-Flop designs are designed to reduce power in DSP applications. Simulation results

show 40% improvement in total power saving for some DSP applications such as FIR

filters and other DSP applications. Design challenges in submicron CMOS technology are

investigated in details for sub-threshold designs for wireless sensor network applications.

In this work different CMOS model such as ST Microelectronic, TSMC and IBM models

are used for different application.

[ii]

Ultra Low power Digital Circuit Design for Wireless Sensor

Network Applications

Farshad Moradi, PhD, University of Oslo, July 2011

Hovedveileder: Frsteamanuensis Dag T. Wisland

Medveiledere: Professor Snorre Aunet og Professor Yngvar Berg

Ny forskning innenfor feltet trdlse sensornettverk pner for nye og innovative produkter og

lsninger. Biomedisinske anvendelser er blant omrdene med strst potensial og det investeres i dag

betydelige belp for bruke denne teknologien for gjre medisinsk diagnostikk mer effektiv

samtidig som man pner for fjerndiagnostikk basert p trdlse sensornoder integrert i et

helsenett. Mlet er forbedre tjenestekvalitet og redusere kostnader samtidig som brukerne skal

oppleve forbedret livskvalitet som flge av kt trygghet og mulighet for tilbringe mest mulig tid i

eget hjem og unng undvendige sykehusbesk og innleggelser.

For gjre dette til en realitet er man avhengige av sensorelektronikk som bruker minst mulig energi

slik at man oppnr tilstrekkelig batterilevetid selv med veldig sm batterier. I sin avhandling Ultra

Low power Digital Circuit Design for Wireless Sensor Network Applications har PhD-kandidat

Farshad Moradi fokusert p nye lsninger innenfor konstruksjon av energigjerrig digital

kretselektronikk. Avhandlingen presenterer nye lsninger bde innenfor aritmetiske og

kombinatoriske kretser, samtidig som den studerer nye statiske minneelementer (SRAM) og

alternative minnearkitekturer. Den ser ogs p utfordringene som oppstr nr silisiumteknologien

nedskaleres i takt med mikroprosessorutviklingen og foreslr lsninger som bidrar til gjre

kretslsninger mer robuste og skalerbare i forhold til denne utviklingen. De viktigste konklusjonene

av arbeidet er at man ved introdusere nye konstruksjonsteknikker bde er i stand til redusere

energiforbruket samtidig som robusthet og teknologiskalerbarhet ker. Forskningen har vrt utfrt i

samarbeid med Purdue University og vrt finansiert av Norges Forskningsrd gjennom FRINAT-

prosjektet Micropower Sensor Interface in Nanometer CMOS Technology.

[iv]

ACKNOWLEDGMENTS

I would like to take this opportunity to thank all the people without whom this dissertation

could not have been possible.

I sincerely like to thank my thesis advisor Prof. Dag Wisland, for mentoring me in this

research work. Observing his critical thinking, sound vision and great communication

skills has really helped me to improve professionally as well as personally.

I would also thank my advisor, at Purdue University, Prof. Kaushik Roy, for giving me

this opportunity to work in his Lab. His research visions and sharp insights were

instrumental in the completion of this work. He taught me how to transform a new idea

into a research accomplishment. My sincere thanks to him for giving advice and help.

I would like to thank my Co-advisors, Prof. Snorre Aunet and Prof. Yngvar Berg for

their guidance and suggestions during the research work.

I would like to thank Prof. Hamid Mahmoodi for his contiguous help and advice during

my research. My sincere thanks to him for providing me to work and learn from him. His

continuous encouragement and motivation during this research has enabled me to

study/explore various research areas. My sincere thanks to him for providing me the

opportunity to learn and work with him.

I would like to thank Nanoelectronic group at University of Oslo.

I would like to thank Nanoelectronic Research Lab (NRL) members at Purdue University.

I would like to thank research council for their support during the project.

Specially, I would like to thank Charles Augustine(Intel), Georgios Karakonstantis(EPFL),

Georgios Panagopoulos(Purdue), Sang Phill Park(Intel), Ashish Goel (Broadcom), Sumeet

Kumar Gupta(Purdue), Niladri Mojumder(Global Foundries), Sabal Mukhapadhyay

(Georgia Tech. University).

Last but not the least, my sincere thanks to my wife, Negin, my parents, and my family

members whose support and love made this work possible.

Contents

Abstract .................................................................................................................................. i

Acknowledgment .................................................................................................................. iii

Capter 1: Digital Circuit Design Challenges in Nano-Scale CMOS ........................................ 1

1.1. Thesis Organization .................................................................................................. 2

Chapter 2 Ultra Low Power Digital Circuit Block .................................................................. 7

2.1. Full adder topologies ................................................................................................ 8

2.2. Proposed Full Adders ............................................................................................. 16

2.3. Leakage-tolerant Logic circuit design ..................................................................... 20

2.4. Conclusion ............................................................................................................. 29

Chapter 3: . Flip-Flop Design for low power applications ..................................................... 31

3.1. Flip-Flop design ..................................................................................................... 32

3.1.1. Sense-Amplifier Flip-Flop .............................................................................. 33

3.1.2. Hybrid Latch Flip-Flop (HLFF) ...................................................................... 34

3.1.3. Transmission-Gate Flip-Flop .......................................................................... 35

3.2. Data-Dependant Sense-Amplifier Flip-Flop ............................................................ 36

3.2.1. Simulation Results .......................................................................................... 36

3.3. Pulsed-Flip-Flop ..................................................................................................... 39

3.4. Flip-Flops in DSP Applications .............................................................................. 45

3.4.1. DD-Counter design ........................................................................................ 46

3.4.2. FIR Filter Design ........................................................................................... 46

3.4.3. DCT design.................................................................................................... 47

3.5. Conclusion ............................................................................................................. 49

Chapter 4: Ultra Low power SRAM design ......................................................................... 51

4.1. Conventional SRAM Design .................................................................................. 54

4.2. Proposed Ultra low power SRAM cells................................................................... 56

4.2.1. Subthreshold 11T-SRAM............................................................................... 56

4.2.2. Subthreshold PMOS-Access transistor SRAM (PAT-SRAM) ........................ 60

4.3. SRAM Design, Architecture Level ......................................................................... 67

4.3.1. Wordline Drives for SRAM arrays ................................................................. 68

4.3.2. Proposed wordline driver ............................................................................... 70

4.3.3. Simulation Results ......................................................................................... 71

4.3.4. Dynamic Noise Margin Comparison .............................................................. 76

4.3.5. MLWD in other SRAM topologies ................................................................ 79

4.3.6. Implementation area ...................................................................................... 82

4.4. Conclusions ............................................................................................................ 82

Chapter 5: Nano-Scale CMOS Circuit Design Challenges for Ultra Low Power

Applications ......................................................................................................................... 84

5.1. DC Analysis for CMOS 65nm Technology ............................................................. 85

5.2. Stacking effect in 65nm Technology ....................................................................... 86

5.3. Body Biasing Technique ......................................................................................... 87

5.3.1. Body-Biasing in Scaled Technologies ............................................................ 89

5.3.2. Body-Biasing Simulation Results ................................................................... 91

5.3.3. Channel Length effect on Body-Biasing Technique........................................ 91

5.3.4. Efficacy of Body-Biasing Technique.............................................................. 93

5.4. Design Examples .................................................................................................... 94

5.4.1. Flip-Flops In Subthreshold ............................................................................. 94

5.4.2 Write Cycle Improved SRAM Design using body-biasing............................. 101

5.5. Conclusions .......................................................................................................... 102

Chapter 6: Asymmetrically-Doped Source/Drain FinFET (AD-FinFET) For SRAMs with

Improved Read/Write Noise Margin .................................................................................. 103

6.1.Asymmetric FinFET .............................................................................................. 106

6.2. FinFET SRAM Cell .............................................................................................. 111

6.3. Asymmetric-Doping FinFET SRAM .................................................................... 112

6.4.Conclusions ........................................................................................................... 115

Chapter 7: Future Research Trajectory .............................................................................. 117

7.1. Contribution of this work ...................................................................................... 117

7.2. Future Work ......................................................................................................... 119

References .............................................................................................................................. i

i

List of Figures:

Fig.1.1. Increasing power over technology generations

Fig.1.2 leakage power is becoming the dominant component of overall power consumption in

scaled technologies

Fig.1.3. Increasing power density with technology scaling

Fig.1.4. Basic sensor node block

Fig.2.1. CMOS standard 28T full adder

Fig.2.2. Different topologies for SERF full adder

Fig.2.3. Equivalent circuit in input vector ABC

in

=110

Fig.2.4. Equivalent circuit for related inputs (SUM)

Fig.2.5. SERF behavior

Fig.2.6. SERF behavior Analysis

Fig.2.7. MUX-based SERF adder

Fig.2.8 (a) GDI technique (b) XOR gate using GDI

Fig.2.9. GDI XOR-based (a,b), and XNOR-based Full adder (c,d)

Fig.2.10. Failure in GDI full adder

Fig.2.11. Proposed SERF full adder circuit

Fig.2.12. Modified SERF full adder (based on Fig.2.2 (d))

Fig.2.13. Proposed SERF full adder

Fig.2.14. Modified GDI full adder (GDI#1)

Fig.2.15. Output waveforms of GDI#1 and test bench

Fig.2.16. GDI #2 full adder circuit

Fig.2.17. The main sources of noise in domino logic circuit

Fig.2.18 Proposed domino logic circuit-1

Fig.2.19. Waveforms of proposed circuit-1

Fig.2.20. High speed proposed domino logic circuit-2

Fig.2.21. Proposed MUX-1

Fig.2.22. Proposed Comparator-1

Fig.2.23. Proposed Comparator-2

Fig.2.24. UNG vs. Delay for proposed MUXs

Fig.2.25. UNG versus Delay for proposed comparators

Fig.2.26. Proposed domino logic circuit

Fig.2.27. Waveforms of ASV circuit

Fig.2.28. 3-inputs OR-Gate topology

Fig.3.1. Sense-Amplifier Flip-Flop

Fig.3.2. Hybrid-Latch Flip-Flop

Fig.3.3. Modified Transmission-Gate Flip-Flop (MTGFF)

Fig.3.4. Data-Dependant FF (DD-SAFF) and Test-Bench

Fig.3.5. Power consumption improvement for DD-SAFF

Fig.3.6. Power consumption for different supply voltages

Fig.3.7. T

CLK-Q

delay for SAFF and DD-SAFF

Fig.3.8. Setup and hold time for SAFF and DD-SAFF

Fig.3.9. Monte-Carlo simulation for delay comparison

Fig.3.10. Layout of (a) SAFF (b) DDSAFF

Fig.3.11. Pulse generation technique

Fig.3.12. Output waveforms for CPG and TGPG designs

Fig.3.13. Transmission-Gate Pulse Generator (TGPG) output waves and scheme

Fig.3.14. PHLFF design

Fig.3.15. Delay and Energy comparison for HLFF and PHLFF

Fig.3.16. T

C-Q

versus T

D-CLK

Fig.3.17. Pulsed-SAFF

Fig.3.18. Shift register block

Fig.3.19. Energy and delay comparisons for SAFF and PSAFF

ii

Fig.3.20. PTGFF topology

Fig.3.21. Output waveforms of PTGFF

Fig.3.22. 8-bit counter

Fig.3.23. CSHM based Fir Filter of size M

Fig.3.24. 2D-DCT operation, areas of high energy-high switching activity outputs and low energy

outputs

Fig.3.25. Power consumption result of DCT for different FFs

Fig.4.1. IDS versus VDS for single NMOS transistor in 65nm

Fig.4.2. I

on

/I

off

ratio for different supply voltages

Fig.4.3. 6T SRAM cell

Fig.4.4. Output waveforms for 6T-SRAM cell

Fig.4.5. Write mode circuitry in 6T-SRAM cell

Fig.4.6. SNM for HOLD and READ in 6T-SRAM (V

DD

=0.4)

Fig.4.7. SNM vs. WM1/WM5 for different temperatures

Fig.4.8. Proposed 11T-SRAM cell

Fig.4.9. output waveforms during read a. 6T-SRAM b. 11T-SRAM

Fig.4.10. Modified 11T-SRAM (14T-SRAM)

Fig.4.11. Butterfly plot for 11T-SRAM

Fig.4.12. Butterfly plot for 11T-SRAM in different temperatures

Fig.4.13. read noise margin for 11T-SRAM

Fig.4.14. Configuration of modified write path in 6T-SRAM cell

Fig.4.15. Proposed SRAM circuit

Fig.4.16. Curves of proposed SRAM cell

Fig.4.17. Waveforms of proposed circuit (Write cycle)

Fig.4.18. Butterfly curves for 6T-SRAM cell

Fig.4.19. Write Margin calculation

Fig.4.20. Write SNM for different temperature (at different corners)

Fig.4.21. Circuit for sweeping WL

R

to get WSNM

Fig.4.22. Write SNM for proposed circuit

Fig.4.23. SNM versus V

DD

Fig.4.24. Monte Carlo simulation for read SNM for 6T-SRAM standard cell

Fig.4.25. SNM in read and HOLD mode for proposed SRAM cell

Fig.4.26. SNM in read and HOLD mode for proposed SRAM cell

Fig.4.27. read assist circuitry

Fig.4:28. RAT scheme

Fig.4.29. LPWD-SS

Fig.4.30. MLWD circuit topology

Fig.4.31. Output of MLVD during the write

Fig.4.32. MLWL outputs during READ

Fig.4.33. Simulation results for MLWD and CWD

Fig.4.34. Voltage Sense-Amplifier used in SRAM array design

Fig.4.36. Lowering the WL voltage effect on SNM and Read access time

Fig.4.35. Read-SNM for 6T-SRAM at different operating voltages

Fig.4.37. Current saving of MLWD during Read.

Fig.4.38. Current saving during Write and Read

Fig.4.39. Write delay for MLWD compared to CWD and LPWD

Fig.4.40. Level of MLWD at different operation voltage

Fig.4.41. Write Margin comparison

Fig.4.42. Process variations effect on WL voltage during the READ Fig.4.43. Effect of process

variations on WL voltage level during write

Fig.4.44. Simulation results for CWD and MLWD design

Fig.4.45. Simulations results for CWD and MLWD

Fig.4.46. Simulation results for MLWD at different levels of V

F

(WL)

Fig.4.47. Schematics of 8T-SRAM and ST-SRAM cells

iii

Fig.4.48. TGPT-SRAM cell

Fig.4.49. TGPT-SRAM cell wit separate BLs

Fig.4.50. Separate bitlines TGPT-SRAM cell

Fig.4.51. Thin-cell 6T-SRAM cell layout

Fig.4.52. Layout of (a) MLWD (b) CWD designs

Fig.4.53. Layout of 128KB SRAM array including MLWD and CWD layouts

Fig.5.1. (a) 2PMOS (b) 3PMOS (c) 2NMOS circuits

Fig.5.2. V

out

vs. V

in

(b) IDS current vs. gate voltage

Fig.5.3. (a) circuit1 (b) circuit2 schematics

Fig.5.4. transient analysis for (a) circuit2 (b) circuit1 (with minimum size for all transistors in 27

o

C,

TT model)

Fig.5.5. the effect of body biasing technique

Fig.5.6. ID vs. Body voltage for NMOS transistor

Fig.5.7. I

off

and I

bulk

vs. V

bulk

Fig.5.8. PMOS Drain current versus Body voltage

Fig.5.9. Optimal body bias vs. channel length for maximum ON current

Fig.5.10. ID (ON current) vs. channel length

Fig.5.11. The effect of FBB on long and short channel devices

Fig.5.12. HLFF waveforms in V

DD

=0.3V, T=27

o

C (TT)

Fig.5.13. Failure in HLFF circuit

Fig.5.14. Proposed Complementary Hybrid Latch Flip Flop (CHLFF)

Fig.5.15. Output of CHLFF (TT model, T=27,V

DD

=270mV)

Fig.5.16. Failure in SAFF

Fig.5.17. Schematic of CSAFF circuit

Fig.5.18. Proposed SRAM design

Fig.5.19. Supply voltage waveform

Fig.5.20. Comparison of the proposed technique with conventional 6T-SRAM cell during write

cycle

Fig.6.1. Asymmetric-Doping FinFET device

Fig.6.2. I

D

-V

DS

for AD-FinFET and Symmetric FinFET

Fig.6.3. AD-FinFET versus Symmetric FinFET Device

Fig.6.4. Igate vs. drain voltage

Fig.6.5. ID-VGS for AD-FinFET and symmetric FinFET

Fig.6.6. Effect of asymmetric FinFET on I

D

-V

G

characteristics by tuning the doping concentration

in the drain contact

Fig.6.7. Effect of asymmetric FinFET on I

D

-V

G

characteristics by tuning the doping concentration

in the source contact.

Fig.6.8. Conduction and valence bands for AD- and AS-FinFET: (a) V

GS

=0, V

DS

=0.9V and

(b)V

GS

=0.5V, V

DS

=0.9V.

Fig.6.9. (a) Capacitance components and (b) total capacitance for the different device

configurations when gate contact is set to zero V

G

=0V and the drain contact is swept.

Fig.6.10. (a) Capacitance components and (b) total capacitance for different device configurations

when gate contact is set to a constant voltage V

D

=0 V and the gate contact is swept.

Fig.6.11. (a) Capacitance components and (b) total capacitance for different device configurations

when gate contact is set to a constant voltage V

G

=0.9V and the drain contact is swept

Fig.6.12. (a) Total capacitance (b) Capacitance components for different device configurations

when drain contact is set to a constant voltage V

D

=0.9V and the gate contact is swept

Fig.6.13. 6T-FinFET SRAM cell, layout and schematic

Fig.6.14. AD-SRAM FinFET Design

Fig.6.15. Read SNM results for AD-FinFET and SD-FinFET SRAM cells

Fig.6.16. Variation in VREAD with DIBL

Fig.6.17. CV/I delay versus VG

Fig.6.18. Comparison of T

WL

delay for AD- and SD- FinFETs

Fig.7.1. Research vision and directions

Fig.7.2. Research plan in device level

iv

Design

Challenges in

Nano-Scale

Technology

Chapter 1

Cahpter1: Design Challenges In Nano-Scale Technology

1

Chapter 1

Design challenges in Nano-Scale

Technology

Introduction

CMOS devices have been scaled down aggressively in the last few decades resulting in

higher integration density and improved performance. However, due to short channel

effects, threshold voltage (V

th

) scaling, oxide thickness scaling and increased doping

density, the off current in the devices has increased drastically with technology scaling.

Hence, as we are approaching the end of the silicon roadmap, controlling leakage current is

becoming a major problem. Moreover, statistical variations in process parameters, such as

device structure (channel length, oxide thickness, width etc), location and number of

dopants in channel (random dopant fluctuation), is increasing with technology scaling. The

variation in process parameters results in large distribution in delay and leakage and

significantly reduces robustness of a circuit. Hence, large leakage current and increasing

process variations have emerged as two major obstacles for designing CMOS circuits

(logic and memory) at the end of silicon roadmap.

Smaller transistors are inherently faster and consume less dynamic power. However, when

millions of transistors are integrated together to create a complex VLSI system, we observe

several new challenges threatening the reliability of computation. Some of them are as

follows:

Leakage Power: With ever-increasing operating frequency and more transistors on a

single die, switching power has increased significantly (Fig.1.1). By scaling the devices to

sub-50nm regimes, controlling over the channel and second order effects such as short

channel effects, DIBL, narrow width effect etc., has become less. Furthermore, by

technology scaling, leakage components increase significantly. Fig.1.2 shows the leakage

power components and the percentage of leakage power for different technology nodes.

Both dynamic and leakage power consumption affect the reliability of the underlying

devices and reduce the battery lifetime of handheld devices. In another word, I

ON

/I

OFF

ratio

decreases with scaling technology. Especially, for ultra low voltage applications such as

Cahpter1: Design Challenges In Nano-Scale Technology

2

wireless sensor nodes, using techniques to reduce the leakage current is crucial due to a

very low I

ON

/I

OFF

ratio in near threshold or sub-threshold regions.

Fig.1.1. Increasing power over technology generations[Intel]

Fig.1.2 leakage power is becoming the dominant component of overall power consumption in

scaled technologies

Process Variation: Sub-wavelength lithography has led to large variation in transistor

geometries (L;W; TOX) and the flat-band voltage (VFB). Process variation effects are more

stringent in small size devices. Variations in channel length, channel width, oxide

thickness, threshold voltage, line-edge roughness, and random dopant fluctuations are the

sources of the inter-die and the intra-die variations in process parameters [the random

variations in the number and location of dopant atoms in the channel region of the device

resulting in the random variations in transistor threshold voltage (RDF)]. One of this inter

die effects is threshold voltage variations due to the changes of a single transistor (e.g.

threshold voltage increases if temperature is reduced). However, intra-die variations may

be different from one transistor to another (i.e. increase in V

th

for one device on the other

hand decrease in threshold voltage for another). An example of the systematic intra-die

variation can be the change in the channel length of different transistors of a die that are

spatially correlated. The RDF induced V

th

variation is a classic example of the random

intra-die variation. Such variations along with higher levels of integration can lead to large

spread in circuit delay, power, and robustness across different dies (Fig.1.2). Therefore, a

circuit designed to meet a target delay using nominal VTH transistors may not meet the

delay target, leading to parametric delay failures. Parameter variations have severe impact

(both in terms of errors as well as leakage) on minimum geometry circuits such as SRAM

cells. Inter-die parameter variations, coupled with the intrinsic on-die VTH variation can

result in stability failures in SRAM cells, degrading the memory yield. A cell failure can

Cahpter1: Design Challenges In Nano-Scale Technology

3

Fig.1.3. Increasing power density with technology scaling [Intel]

occur due to:(a) an increase in the cell access time (access failure), (b) unstable read/write

operations (read/write failure),or (c) failure in the data holding capability of the cell at a

lower supply voltage. Body-biasing has been used for mitigating the impact of inter-die

process variation and reducing the parametric failures [1]. However, it has been observed

that the effectiveness of body-biasing reduces with technology scaling [2]. Different

challenges in ultra low supply voltage, especially for storage circuits, are investigated in

this dissertation. Unfortunately, for lower supply voltages the effect of process variations

increases significantly. Therefore looking at process variations in different designs,

especially for very low voltages is interesting.

Power Density and Die-Temperature: Increasing power density due to faster clock,

power consumption (due to dynamic power and leakage) and high device integration is

becoming another issue. The increased power density translates into excessive heat while

the cooling capability of the package remains limited. Hence, it gives rise to elevation of

overall die temperature as well as localized heating at highly active regions of a chip

(called hot-spots", Fig.1.3). Traditionally, a circuit is designed to operate at worst-case

temperature which is inefficient given the fact that the circuit may experience the worst-

case condition only for short duration. Dynamic thermal management techniques like logic

shutdown, clock gating, frequency scaling, voltage-frequency throttling etc. have been

proposed in past [3] [4] [5]. Although these techniques are capable of bringing down power

density and temperature, they also degrade the performance considerably. Dynamic voltage

scaling can be an effective way to reduce temperature in the event of overheating because

it reduces both the switching as well as leakage power. However, if the clock frequency is

not scaled simultaneously, then increased path delays (due to lower voltage) may result

into wrong computation. Combined V-f control technique reduces leads to cubic benefit in

terms of power saving at the cost of complex control circuitry and pipeline stalls [5].

Nano-scale reliability: As dimensions of MOS devices have been scaled down, new

reliability problems are coming into effect. One of these emerging reliability issues is aging

effects that result in device performance degradation over time. NBTI (Negative biased

temperature instability) is a well-known aging phenomenon, which is a limiting factor for

future scaling of devices. NBTI results the generation of trapped charges, which cause

threshold voltage degradation of PMOS. Another reliability issues are PBTI, Hot carrier

injection (HCI), and TDDB that should be considered for ultra-scaled nano-scale devices.

Cahpter1: Design Challenges In Nano-Scale Technology

4

Due to higher electric field in ultra-thin body (UTB) devices, HCI is increased significantly

that should be considered for future technologies.

1.1. Thesis Organization:

In this thesis, we consider different challenges in ultra low power circuit design for

wireless sensor network applications, portable devices etc. We present several leakage-

tolerant, noise-immune, low power and high performance designs for different DSP

application. The main contribution of this thesis is to design ultra low power digital circuit

design for wireless sensor nodes at very low supply voltages (Near/Sub-threshold).

However, in this thesis we tried to consider other potentials for future low power and

reliable design by considering new devices such as double-gate MOSFETs. Therefore, the

main contributions of this work are as follows:

- High-Speed and leakage-tolerant design: In this part of our work, we propose several

low leakage logic circuits and basic blocks such as wide OR-gates, Full adder (FA)

design, XOR, Multiplexer (MUX), comparators etc. Chapter 2, covers designing basic

logic circuit blocks for high performance and low power targets.

- Flip-Flop design: Among the logic elements, latches and flip-flops (FF) are critical for

the performance of a digital system. Flip-flops, the characteristic building block of any

clocking or pipeline system, are the most important components in synchronous VLSI

designs. Unless they are carefully designed and characterized, the performance of FFs

has a critical effect on the system. Interestingly, the FFs often consumes the largest

share of the total system power (20%-50%) [6]. We propose several new flip-flops to

reduce the total power of DSP applications such as filters, and DCT. Results show at

least 27% total saving compared to using conventional FFs.

- SRAM Design: SRAM bit-cells utilizing minimum sized transistors are susceptible to

various random process variations. Hence reducing the memory operating supply

voltage (V

min

), while maintaining the yield is becoming extremely challenging in nano-

scale technologies. Chapter 4 focuses on developing novel circuit techniques for robust

memory operation with lower V

min

. In this chapter we propose different SRAM design

Fig.1.4. Basic sensor node block

Cahpter1: Design Challenges In Nano-Scale Technology

5

at bit-cell level and SRAM architecture level. Simulation results show significant

improvement in read and write robustness (2X) while lower leakage is achieved.

- Challenges in Sub-Threshold Design: challenges observed in 65nm technology for

circuits utilizing sub-threshold region operation are presented. Different circuits are

analyzed and simulated for ultra low supply voltages to find the best topology

for sub-threshold operation. The effect of body-biasing technique is investigated in

detail to find the optimal point to get the minimum power and maximum performance.

SRAM and Flip-Flop designs are re-designed using body-biasing technique and

stacking effect in chapter 5.

- Double-Gate Design: To overcome short channel effects (SCE), different

candidate transistor structures have been investigated to replace the bulk

MOSFETs. Among them, FinFETs is considered to be a promising candidate for

scaled CMOS devices in sub-22-nm technology nodes. This device shows increased

immunity to SCE due to improved channel control by the gate voltage.

Furthermore, threshold voltage (V

th

) can be easily controlled by engineering the

gate contact work function. Moreover, V

th

variations due to random dopant in the

channel region (RDF) are reduced due to almost intrinsic channel doping. In this

chapter, new FinFET device is introduced to improve the device characteristics.

Furthermore, a robust SRAM design is introduced to resolve the conflict between

read and write margins. Results show 10 times less leakage while DIBL and

subthreshold-slope are improved by three times and 20%, respectively.

Furthermore, the conflict between read and write is resolved.

In general, the main goal of the thesis is to consider low power design for wireless sensor

nodes. Fig.1.4 shows a typical wireless sensor node block that includes: Energy sources,

wireless communication interface, sensor interface, including analog/digital converter and

I/O parts, computational unit, that processes sensor reading and networking algorithms and

is able to store small amount of intermediate data, Memory that stores program code,

intermediate data, and queries and networking data, and finally debugging interface.

Therefore, we focused on designing the storage blocks such as memory and flip-flops, and

low power digital design for processing unit. At the same time, we explore the behavior of

nano-scale transistors at ultra low supply voltages.

Ultra Low Power

Digital Circuit

Blocks for

Wireless Sensor

Nodes

Chapter 2

Chapter 2: Ultra Low Power Digital Circuit Blocks

7

Chapter 2

Ultra Low Power Digital Circuit Blocks

for Wireless Sensor Nodes

Introduction

With the rapid development of portable digital applications, the demand for increasing

speed, compact implementation, and low power dissipation triggers numerous research

efforts [7]-[10]. The role of power dissipation in VLSI systems is pervasive. For high

performance design, power dissipation can be the limiting factor to clock speed and circuit

density because of the inability to get power to circuits or to remove the heat that they

generate. For portable information systems, power dissipation has a direct bearing on size,

weight, cost, and battery life. Consequently, power dissipation is becoming widely

recognized as a top-priority issue for VLSI circuit design. The challenge facing the VLSI

designer is to find and effectively apply circuit techniques that can balance the needs for

performance with those of power dissipation [11]. Therefore ultra low power circuits

design becomes the major candidate for portable applications such as wireless sensor

nodes. One common technique for reducing power is power supply scaling. For CMOS

circuits the cost of lower supply voltage is lower performance. Scaling the threshold

voltage can limit this performance loss somewhat but results in increased leakages [12].

Other techniques used in low power design include clock gating and dynamic

voltage/frequency scaling [13], [14].

Subthreshold circuit design involves scaling the supply voltage below the threshold

voltage, where load capacitances are charged/discharged by subthreshold leakage currents.

Leakage currents are orders of magnitude lower than drain currents in the strong inversion

regime, therefore there is a significant limit on the maximum performance of subthreshold

circuits. Therefore, traditionally, subthreshold circuits have been used for applications

which require ultra-low power dissipation, with low-to-moderate circuit performance [15].

In the first part of this chapter, different topologies for full-adders are presented along with

some circuit modifications to reduce the power consumption. Due to the importance of

leakage power consumption in digital CMOS circuits, new technique is proposed to reduce

2.1. Full Adder Topologies

8

the sub-threshold leakage current in high fan-in gates (e.g. OR gate) and basic blocks such

as comparators and multiplexers for high-performance applications. Two circuit techniques

are proposed to reduce the leakage current in nano-scale circuits as follows:

1. Leakage-tolerant circuit for domino logic

2. Adaptive supply voltage technique

Let us first look at different topologies for full-adders.

Fig.2.1. CMOS standard 28T full adder

2.1. Full Adder Topologies

One-Bit Full adder design is one of the most critical components of a processor that

determines its throughput, as it is used in ALU, the floating point unit, and address

generation in case of cache or memory accesses [15]. A variety of full adders have been

reported in [16]-[24]. However, in this chapter, we focus on the full adder topologies

specified for subthreshold design and wireless sensor networks. One of the most well

known full adders is the standard CMOS full adder that uses 28 transistors as shown in

Fig.2.1. In [16] the sense energy recovery full adder (SERF) is presented. The topology of

this circuit is shown in Fig.2.2 which requires only 10 transistors to implement a full adder.

Table.2.1 Truth table of SERF full adder design

Chapter 2: Ultra Low Power Digital Circuit Blocks

9

Several full adder topologies have been presented in [18] with a low number of transistors

(i.e. small area). However, in this chapter, we focus on two topologies including GDI and

SERF full adders.

Let us, first, explore several full adder topologies based on the GDI technique. Then,

different circuit topologies based on the SERF full adder are presented for ultra low supply

voltage applications. The multi threshold technique is used to improve the operation of the

SERF full adder design.

The SERF design uses only 10 transistors to implement a full adder. Although his circuit

operates properly at higher supply voltages, if the supply voltage is scaled further to

voltages lower than 0.3V, this circuit fails to work. Table.2.1 describes the behavior of this

circuit for different inputs. As it can be seen, the SERF adder (Fig.2.2 (a)) is confronted

with serious problems especially at lower supply voltages. Assume that one of the two

Fig.2.2. Different topologies for SERF full adder [17]

F

(d)

(c)

(a) (b)

Fig.2.3. Equivalent circuit in input vector ABC

in

=110

2.1. Full Adder Topologies

10

input vectors ABC

in

=110 and 111 are applied. As seen from Fig.2.2 (a), when A=1 and

B=1, the voltage at node F is at V

DD

-V

th

. Now if C

in

=0 then C

out

will be equal to V

DD

-2V

th

and the Sum signal is discharged to zero driven by a MOS transistor with its gate

connected to V

DD

-V

th

. When C

in

=1, C

out

is connected to V

DD

(or lower) and the signal

SUM raises to V

DD

-V

th

. Another problem with this design is the time in which the floating

node is connected to 0 (A=0, B=1 or A=1, B=0).When C

in

is 1, C

out

is charged to V

DD

,

but when C

in

=0, C

out

must be discharged to ground using a PMOS pass transistor that

cannot fully discharge the output. In this case, C

out

is discharged to V

tp

which is higher than

V

tn

(Where V

tp

and V

tn

are the threshold voltages of PMOS and NMOS transistors,

respectively). This problem is intensified, when the circuit operates at subthreshold

voltage. Let say A is at logic 1, current leaks to the C

out

node which makes C

out

to

increase even more than V

tp

in some cases depending on the sizing of the pass transistors.

In this case the Sum voltage depends on the C

in

state. For instance, if C

in

is 1, the Sum

output is charged to V

DD

-V

th

which is a problem in subthreshold region by assuming

V

DD

=0.3V while V

th

=0.25V. In this situation, output is charged to 0.05V that is assumed as

zero.

The most important problem with the SERF full adder is in the case when A=1, B=1 and

C

in

=0. For this input vector, as mentioned before the output signal reaches V

DD

-V

th

.

Simulation results show that at V

DD

=0.3V, the output signal reaches 0.1V which is not high

enough to change the state of the next stage. To eliminate these problems a new topology is

introduced. This limitation also causes a constraint for lowering the supply voltage. For

instance, to have a correct output for SUM it seems that the supply voltage cannot be

lowered less than V

DD

/2+2Vtn indicating that the supply voltage must be higher than

V

DD

/2+0.28V in a 65nm CMOS technology. However this limit depends on the circuit

design topology and also the sizing and the device types that are employed. To mitigate

this problem, the gates of pass-transistor (PT) for C

out

signal must be connected to V

DD

during the challenging state (A=B=1, C

in

=0). Then the supply voltage may be reduced to as

low as V

DD

/2+V

th

which is estimated to be V

DD

/2+0.14. For example when V

DD

=0.3, in

worst case C

out

will be V

DD

-V

th

=0.16V, which can be used as a high logic. In addition the

NMOS pass transistor may be upsized to further lower the supply voltage. It seems to be

possible to lower the supply voltage to 0.25V.

Fig.2.4. Equivalent circuit for related inputs (SUM)

Fig.2.5. SERF behavior

Chapter 2: Ultra Low Power Digital Circuit Blocks

11

Fig.2.6. SERF behavior Analysis

For input signals A=1, B=1, and C

in

=0, the equivalent circuit for SUM signal is shown in

Fig.2.3. As it can be seen the state of the output cannot be determined precisely, since two

PMOS devices and also the NMOS transistor are ON, then the output state is roughly

dependant on the transistor sizing. Consequently, the circuit fails to evaluate correctly in

some cases. Let us consider other SERF full adders in Fig.2.4 for input vector

ABC

in

=11X. As it can be seen in Fig.2.4, this topology consumes much power with the

input vector ABC

in

=110. At ultra low supply voltage the probability of failure is higher

than when operating at higher supply voltages. Fig.2.5 shows the behavior of the topology

in Fig.2.2 (c) during these two input vectors (ABC

in

=110 and ABC

in

=111).

In this topology the behavior of the circuit is improved compared with Fig.2.2 (b), so we

can reduce the supply voltage as much as V

th

compared to the circuit shown in Fig.2.2 (b).

In the topology of Fig.2.2 (d), there is the same problem for the SUM output signal. Fig.2.6

describes the behavior of this circuit. In Fig.2.6, if we add a circuitry, to connect the gates

of the pass transistors to V

DD

instead of V

DD

-V

th

leads to removing the power dissipating

path due to the completely turned-off PMOS transistors, results the output connects to

V

DD

-V

th

instead of V

DD

-2V

th

.

There are two possible solutions to improve the operation of the SERF circuit. The first

one is connecting the output of the XNOR gate (first stage) to V

DD

instead of V

DD

-V

th

(when the output of XNOR gate is high) and also modifying C

out

to be connected to V

DD

instead of V

DD

-V

th

or V

DD

-2V

th

. The multiplexer-based SERF adder circuit is presented in

[17]. In this circuit which is shown in Fig.2.7, all parts are implemented using a

multiplexer. Although this circuit consumes less power than previous SERF topologies, it

Fig.2.7. MUX-based SERF adder [17]

2.1. Full Adder Topologies

12

has some serious problems at lower supply voltages. Table.2.2 shows the truth table of this

circuit.

For the input vector ABC

in

=111, the output signals are limited to V

DD

-2V

tn

which

limits the supply voltage scaling for this circuit. The supply voltage for this circuit must be

higher than 2V

tn

+V

tp

. Therefore, in 65nm technology, the supply voltage must be higher

than 0.48 which is not sufficiently low for ultra low power applications. Therefore this

circuit does not work properly in subthreshold region. Furthermore for input vector 101,

C

out

is limited to V

DD

-2V

th

.

In this section we analyze the Gate-Diffusion Input (GDI) full adder design that is

proposed in [20]. The GDI technique is proposed by Morgenshtein et al. in [10]. This

technique reduces the power dissipation and also makes the circuit smaller. The advantage

of GDI technique two-transistor implementation of complex logic functions, and in-cell

swing restoration under certain operating conditions, are unique within existing low-power

design techniques [10]. Fig.2.8 shows the operation of GDI technique and also

implementation of a XOR gate using this technique. As it can be seen most logic functions

required can be implemented using a small number of devices. To implement a XNOR gate

using GDI, the places for applying B and B_bar can be changed. The problem with GDI-

based adder is the same as for the SERF adder. Fig.2.9 shows four topologies of GDI-based

full adder. We analyze these full adders with different inputs. Table.2.3 shows the results

for these full adders.

Table.2.2. Truth table of MUX-based SERF

Fig.2.8 (a) GDI technique (b) XOR gate using GDI

Chapter 2: Ultra Low Power Digital Circuit Blocks

13

These GDI-based full adders work better than SERF in most cases. However, there are

some limitations. For instance, for the input vector ABC

in

=001, suppose that the circuit

is working with V

DD

=0.3V and the threshold voltage for PMOS and NMOS circuit are -

0.15 and 0.14 respectively. In this case, Fig.2.10 illustrates the problem which is even more

degradation at lower supply voltages for the circuit from Fig.2.9(c). The SUM signal value

is not stable, because of insistent power dissipation and contention between NMOS and

PMOS to determine the X node state. Also in Fig.2.9(a), there are problems with

discharging the SUM node to zero. The SUM output is discharged only to 2V

tp

which is

high enough to be assumed as 1. However, this circuit dissipates less power than SERF

full adders. We can modify the SERF full adder to work at lower supply voltages and

alleviate the problem with these special input vectors for the GDI-based adder design. For

the GDI full adder, we can reduce the supply voltage lower than supply voltage for the

SERF circuit.

Fig.2.9. GDI XOR-based (a,b), and XNOR-based Full adder (c,d)

Fig.2.10. Failure in GDI full adder

2.1. Full Adder Topologies

14

Table.2.3. GDI Full-adder truth table

Fig.2.11. Proposed SERF full adder circuit

Fig.2.12. Modified SERF full adder (based on Fig.2.2 (d))

Chapter 2: Ultra Low Power Digital Circuit Blocks

15

Table.2.4. Truth table for full adder circuit Fig.2.11

g

Fig.2.13. Proposed SERF full adder

Fig.2.14. Modified GDI full adder (GDI#1)

M1

F

2.2. Proposed Full Adders

16

2.2. Proposed Full Adders (FA)

In this section some new full adders are proposed based on the SERF and GDI

techniques. At first to modify the SERF full adder for different inputs, we add an extra

circuit to the SERF adder as shown in Fig.2.11. By adding this circuit to the SERF, the F

node voltage for input vectors ABC

in

=(110, 111), is connected to V

DD

, which increases

the output by V

th

, so we can scale the supply voltage to V

tn

+V

tp

that is estimated to be

lower than 0.3V instead of 0.45V for the SERF full adder.

Another proposed idea is as follows: We use a different configuration for the C

out

signal

and a MUX to produce the SUM signal of the output of XNOR gate. This topology is

shown in Fig.2.12. For this circuit Table.2.4 shows that that the logic levels of Cout are

improved and the consuming path in SERF is mitigated. However this circuit uses one

transistor more than the SERF full adder.

Another idea that significantly improves the operation of the SERF design is using a

compound of the techniques proposed in Fig.2.11 and Fig.2.12. This proposed circuit is

shown in Fig.2.13. This circuit enables even more scaling of the supply voltage lower than

V

tn

+V

tp

which is estimated to be 0.3V. Furthermore, we may use the precise sizing to

enable the circuit to work at lower supply voltages. This circuit shows much better

functionality compared with other SERF adder topologies. In this circuit, when A=1, B=1,

Fig.2.15. Output waveforms of GDI#1 and test bench

Chapter 2: Ultra Low Power Digital Circuit Blocks

17

C

in

=0, there are no problems; because the F node is connected to 1, which eliminates the

power consuming path in Fig.2.14. Because the gates of the pass transistors are connected

to V

DD

, the PMOS transistor is off. Moreover, in the state when ABC

in

=111, the F node

is connected to V

DD

, and as a result, Sum is charged to V

DD

-V

th

and results C

out

connecting

to V

DD

.

Another circuit is a new modified GDI based full adder design. The technique is used to

improve the functionality of circuit shown in Fig.2.11 for lower supply voltages. The main

drawback with the GDI full adder is when both x and y inputs are at logic low (AB=00).

As it can be seen the main problem is with the output of first stage XNOR gate in the GDI

full adder. If we add a circuit to lower the output of first stage to logic zero instead of V

tp

,

the problem is resolved. Furthermore, the original circuit dissipates more power during this

state which is now reduced using proposed circuit. The proposed GDI full adder is shown

in Fig.2.14. The added circuit is shown in bold lines in Fig.2.14.

When y and x signals are 0, this turns on the added NMOS transistor and helps to

discharge F node voltage to zero. Therefore this alleviates the problem with this circuit

described in Fig2.10. Fig.2.15 shows the waveforms for proposed FA compared to

conventional FA in Fig.2.10. We can add another transistor to the GDI full adder that is

Fig.2.16. GDI #2 full adder circuit

Table.2.5. Power consumption of full adders

2.2. Proposed Full Adders

18

shown in Fig.2.16. In this topology, NMOS transistor M2 is added to connect the SUM

output signal to ground when G node voltage is high. This added NMOS transistor M2

enables this circuit to work at lower supply voltages.

The proposed full-adders modify the operation of GDI and SERF full adders at very low

supply voltages. Therefore, we consider new GDI full-adders as GDI#1 and GDI#2 and for

SERF full adders by referring to the corresponding figures.

2.2.1. Simulations and results

We simulated FA circuits for different ranges of frequencies from 100 KHz to 10 MHz to

find out which circuit performs well. We use the 65nm CMOS standard models from ST

microelectronic. Also we simulated these circuits to find the lowest supply voltages that

these circuits are able to work without failure. The results for all full adders are tabulated in

Table.2.5 to show which full adder is best suited for operation in ultra low supply voltage

applications.

For SERF full adder, the most important drawback is its limitation on supply voltage

scaling that which cannot be reduced below 2V

tn

+V

tp

. This problem is more challenging in

corners especially in SS corner (Slow NMOS, Slow PMOS).

The supply voltage at which SERF outputs are satisfactory is higher than 0.5V with

upsized transistors. The simulation results for different full adder circuits are shown in

Table.2.5.

As it can be seen in Table.2.5, the power consumption for SERF (Fig.2.13) full adder is

lower than other circuits. The supply voltage for this design is limited to voltages higher

than 0.3V. For these designs we can use the lower supply voltages in some cases, but we

have to use larger devices that increase the area significantly. To find the minimum supply

voltages for full adder designs, different inputs were applied at different frequency. We

considered the functionality of these circuits in different operating conditions. For instance,

as it is shown in Fig.2.15, the dotted region shows the failure in SUM signal for GDI full

adder at 0.3V supply voltage. In this case, for input vector ABC

in

=000, SUM should be

at zero logic. But it is discharged just to 0.16V, which can be assumed as high voltage

causing a failure in circuit. As Table.2.5 shows, for proposed full adder topologies, power

consumption is decreased significantly compared to conventional SERF and GDI full adder

counterparts. The mail reason of lower power consumption is using the lower supply

voltages that cause reduction in dynamic power (quadratic) and also subthreshold

Table.2.6 Simulation results (Delay and PDP)

Chapter 2: Ultra Low Power Digital Circuit Blocks

19

power consumption (exponential). Table.2.6 shows the results for delay comparison for

proposed circuits compared to other topologies in literature. As it is shown, the proposed

full adders improve the PDP in some cases by 2X times. For new GDI full adder designs,

in proposed circuits, the PDP is improved compared to conventional GDI full adder circuit

[10].

According to transistor level simulations, the power consumption is decreased with at least

62% for the SERF design and 86% for the GDI full adder design. The cost is a small area

overhead; the proposed circuits have a small area overhead up to 11% compared with

SERF and GDI full adders. Also the GDI technique showed that this logic can be suitable

for ultra low power applications.

In next section, due to the importance of leakage current mechanisms in ultra deep sub-

micron technologies, a new leakage tolerant logic circuit is proposed. Therefore, let us first

look at different sources of noises causing lower robustness in logic circuit design. As we

mentioned in chapter one, for ultra low voltage applications, I

n

/I

off

ratio decreases

significantly. Therefore, by applying some techniques to reduce leakage current, let say by

10 times, I

on

/I

off

increases by 10 times, results in improved performance, power, and robust

operation.

Fig.2.18. Proposed domino logic circuit-1 [30]

Fig.2.17. Te main sources of noise in domino logic circuit [26]

2.3. Leakage-Tolerant Domino Logic Circuit Design

20

2.3. Leakage-Tolerant Logic Circuit Design

High fan-in compact dynamic gates are often used in high performance critical units of

microprocessors. However, the use of wide dynamic gates is strongly affected by

subthreshold leakage and noise sources [25]. This is mainly due to decreased threshold

voltage that results in exponentially increased leakage currents in scaled technologies. To

reduce power consumption, supply voltage scaling is used across technology scaling.

However, threshold voltage needs to be scaled down as well to maintain transistor

overdrive for large ON currents. Less threshold voltage means smaller gate switching trip

point in domino circuits. Smaller trip points make the domino circuit more prone to input

noise. Moreover, excessive leakage can discharge the precharge (dynamic) node of a

domino circuit resulting in a logic failure (wrong evaluation). In addition to reduced trip

pint and increased leakage, other noise sources such as supply noise and crosstalk noise

also increase by technology scaling, further degrading the robustness of domino logic.

Fig.2.17 shows different noise sources and how they impact the robustness of the domino

logic [26]. Conventional approach for improving the robustness of domino circuits is

keeper transistor upsizing. However, as the keeper transistor is upsized, the contention

between keeper transistor and NMOS evaluation network increases in the evaluation phase.

Such current contention increases evaluation delay of the circuit and increases power

dissipation. Thus, keeper upsizing trades off delay and power to improve noise and leakage

immunity. Such trade-off is not acceptable because it may make the circuit too slow or too

power hungry.

There are techniques proposed in the literature to address this issue. High-speed domino

logic [27] and conditional keeper [28] are among the most effective solutions for

improving the robustness of domino logic. Fig.2.17. the main sources of noise in domino

logic circuit [26]. In this section, we propose new domino circuits for high fan-in and

high-speed applications in ultra deep submicron technologies. The proposed circuits

employ a footer transistor that is initially OFF in the evaluation phase to reduce leakage

and then turned ON to complete the evaluation. In order to avoid the delay penalty due to

an initially OFF footer transistor, an extra path for evaluation is provided that is controlled

by the output. According to simulations in a predictive 70nm process [29], the proposed

circuits increase noise immunity by more than 26X for wide OR gates and shows

performance improvement of up to 20% compared to conventional domino logic circuits.

The proposed circuits reduce the contention between keeper transistor and NMOS

evaluation transistors at the beginning of evaluation phase.

2.3.1. Proposed Domino Logic Circuit Design Using Feedback from Output

There are many proposed circuits that reduce leakage current and total power

consumption. One of the existing leakage tolerant domino circuits is high-speed domino

logic (HS). The description of this circuit has been explained in [27]. Another existing

leakage tolerant domino circuit is conditional keeper domino logic (CKL) [28]. In our

design, a conditional keeper that is turned on during the hold time is employed to dominate

the leakage through parallel NMOS network. The schematic of our proposed circuit is

shown in Fig.2.18 (referred as proposed circuit-1). The proposed circuit-1 employs

stacking effect (by adding the footer transistor MN1) for noise immunity improvement and

uses the steady state voltage of N_FOOT node at the beginning of evaluation phase to

reduce leakage of the evaluation network. Below the operation of the circuit is analyzed for

the different operational modes.

Chapter 2: Ultra Low Power Digital Circuit Blocks

21

a) Precharge mode:

When clock is low, the circuit is in the precharge phase. MP1 is turned on and the

dynamic node starts charging to V

DD

. In addition, PMOS keeper transistor (MP2) is turned

on helping the precharge. At the beginning of the precharge phase, MN1 is on. Thus, it

pulls the N_FOOT node to ground. Meanwhile, node GMN2 is low and MN2 is in the off

state. After the delay of the inverters (delay element), MN1 is turned off. In this case, the

voltage of N_FOOT rises to an intermediate voltage level. The evaluation transistors are

sized such that the DC voltage of GMN2 node does not exceed the threshold voltage of

MN2 to avoid any possibility of short circuit current in the precharge phase. We have

selected MN2 to be larger than other NMOS transistors.

b) All inputs at zero in evaluation

At the beginning of the evaluation phase, NMOS footer transistor MN1 is off. Thus, N-

FOOT node is floating. Therefore, in this case, its voltage reaches a DC voltage. If this

voltage exceeds |V

tn-MP3

|+V

OUT

, MP3 is turned on. In the other words:

3

3:

N FOOT tp MP OUT

if V V V MP ON

> +

(1)

In that case, the GMN2 node is charged to V

N-FOOT,

and therefore:

ON MN V V if

MN tn GMN

: 2

2 2

>

(2)

If condition (2) is satisfied, (MN2 is turned on), a wrong evolution occurs. However,

in our design we have sized MN1, MN2, MP3, and MP4 considering the voltage of GMN2.

The sidings are done in such a way that condition (1) and (2) do not happen. Therefore, the

DC voltage of N_FOOT acts as a source biasing for the evaluation network without

affecting the functionality of the circuit. This DC voltage reduces leakage of the evaluation

network substantially, resulting in significant leakage tolerance. Our proposed circuit has

significant immunity to input noise because due to the DC voltage of NMOS transistors

source terminals in the evaluation network, their threshold voltage increases. Thus, their

trip point increases and their subthreshold leakage current reduce significantly, due to

Fig.2.19. Waveforms for proposed Circuit-1

2.3. Leakage-Tolerant Domino Logic Circuit Design

22

stacking effect. In our proposed circuit, performance improvement is achieved by upsizing

MN2 transistor. This is further described in the following subsection.

c) An input switching high in evaluation phase:

The waveforms of the circuit in this mode are shown in Fig.2.19. As observed, the

increased voltage of N_FOOT node at the beginning of the evaluation phase causes MP3 to

be turned on. Therefore, the GMN2 node is charged to the voltage of N_FOOT node which

rises above the threshold voltage of MN2. Therefore, the NMOS transistor MN2 is turned

on at the onset of evaluation phase (when the footer transistor MN1 is off), connecting the

dynamic node to ground. After delay of the delay element, N_FOOT node is strongly at

zero voltage. Thus, the transistor MP3 switches to the off state. Since the output nod is at

high now, it turns on the MN3, and connects GMN2 node to ground turning MN2 off.

Fig.2.21. Proposed MUX-1

Fig.2.20. High speed proposed domino logic circuit-2

Chapter 2: Ultra Low Power Digital Circuit Blocks

23

However, the rest of evaluation phase (discharging of the dynamic node) completes

through the evaluation network and the footer transistor that is fully on. Here we have more

degree of freedom for increasing speed or enhancing noise immunity. For example, for

improving speed, upsizing of MP3, MN2, MN1, evaluation transistors, and MN1 are all

options.

To improve the operation of the proposed circuit-1 we use an extra circuit to improve the

evaluation speed. This circuit is shown in Fig.2.20 (referred as proposed circuit-2). After

the primary time of evaluation, the dynamic node starts to be discharged (when at least one

of inputs is at high). The input of small keeper transistor MP2 starts to go high. So, both

inputs of the NAND gate are at high logic, so the output of the NAND gate goes to low and

the gate of NMOS MD transistor start to going high that helps to discharging dynamic

node. Then the speed of our proposed circuit is improved significantly. In other times at

least one of the inputs of the NAND gate is 0, so the voltage of the MD transistor is low.

Therefore the MD transistor is switched off.

To show the efficacy of proposed domino logic circuit, a multiplexer and a comparator

designs based on the proposed domino logic design are presented.

Fig.2.22. Proposed comparator-1

Fig.2.23. Proposed Comparator-2

2.3. Leakage-Tolerant Domino Logic Circuit Design

24

2.3.1.1. Proposed Multiplexer

High fan-in dynamic MUXs are commonly used in register files for implementation of

bit-lines [31]. In register files, because of the fairly small size of the memory, the bit-lines

are implemented using wide domino MUX gates [32]. Multiplexers with a high fan in are

widely used in many applications, such as the column decoders of memories. In footless

domino logic MUX, the excessive leakage of the evaluation network can cause logic

failure during the read operation.

A method is proposed in [31] to improve the leakage-immunity of register file bit-lines

is pseudo static bit-line. In this technique, the subthreshold leakage is reduced

considerably. However, the technique either exhibits considerable increase in transistor

count and delay penalty due to the use of many static OR gates. The proposed technique

can be applied to the register file bit-line MUX as shown in the Fig.2.21. The worst case

scenario for noise at the inputs is when all the inputs from the memory cells are high, and