Professional Documents

Culture Documents

CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S Latches

CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S Latches

Uploaded by

Narendra BholeCopyright:

Available Formats

You might also like

- Clil Lesson Plan TemplateDocument5 pagesClil Lesson Plan Templatesandovalz24433% (3)

- 11 Online Trading Academy PDFDocument16 pages11 Online Trading Academy PDFNarendra Bhole100% (3)

- Troubleshooting & Repairing Consumer Electronics Without a SchematicFrom EverandTroubleshooting & Repairing Consumer Electronics Without a SchematicNo ratings yet

- CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDocument6 pagesCD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDouglas CorderoNo ratings yet

- 0 Ti 4 Kki 3 L 0243 Iulijdp 7 A 7 TapfyDocument8 pages0 Ti 4 Kki 3 L 0243 Iulijdp 7 A 7 TapfyjuenkkoNo ratings yet

- CD4023Document6 pagesCD4023Jules Le GrandNo ratings yet

- CD4011BCDocument10 pagesCD4011BCKike DavilaNo ratings yet

- CD 4050Document7 pagesCD 4050nicolaunmNo ratings yet

- NewDocument8 pagesNewxuankien181991No ratings yet

- CD4094BCDocument7 pagesCD4094BCEdgar MendezNo ratings yet

- CD 4069Document6 pagesCD 4069shaniimranNo ratings yet

- CD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesDocument6 pagesCD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesMerényi OszkárNo ratings yet

- 74AC02 - 74ACT02 Quad 2-Input NOR Gate: General Description FeaturesDocument7 pages74AC02 - 74ACT02 Quad 2-Input NOR Gate: General Description FeaturesAlexandre S. CorrêaNo ratings yet

- CD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesDocument8 pagesCD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesbanoluNo ratings yet

- CD4093 PDFDocument8 pagesCD4093 PDFIván IvanovNo ratings yet

- CD4028BC BCD-to-Decimal Decoder: General Description FeaturesDocument6 pagesCD4028BC BCD-to-Decimal Decoder: General Description Featuresmalirezazadeh5549No ratings yet

- Device Datasheet For CD4021Document7 pagesDevice Datasheet For CD4021bdfbNo ratings yet

- CD4020BC - CD4040BC - CD4060BC 14-Stage Ripple Carry Binary Counters - 12-Stage Ripple Carry Binary Counters - 14-Stage Ripple Carry Binary CountersDocument9 pagesCD4020BC - CD4040BC - CD4060BC 14-Stage Ripple Carry Binary Counters - 12-Stage Ripple Carry Binary Counters - 14-Stage Ripple Carry Binary CountersOsman KoçakNo ratings yet

- CD4511BCDocument8 pagesCD4511BCBiswajit SarkarNo ratings yet

- 4094BCDocument7 pages4094BCNelson RodriguezNo ratings yet

- 4096 Circuito IntegradoDocument7 pages4096 Circuito IntegradoalexmanriqueNo ratings yet

- 74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesDocument8 pages74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesAini NierisNo ratings yet

- CD4029BC Presettable Binary/Decade Up/Down CounterDocument10 pagesCD4029BC Presettable Binary/Decade Up/Down CounterIbrahimEssamNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- 74HC14 PDFDocument8 pages74HC14 PDFNielsy R. Aparicio QuirogaNo ratings yet

- 74 LV 00Document10 pages74 LV 00Brzata PticaNo ratings yet

- CD4071BC - CD4081BCDocument8 pagesCD4071BC - CD4081BCGustavo ZuñigaNo ratings yet

- Hoja de Datos cd4017Document9 pagesHoja de Datos cd4017FranciscoFloresNo ratings yet

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocument6 pagesCD40106BC Hex Schmitt Trigger: General Description Featuresgosa46No ratings yet

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849No ratings yet

- CD4017BC, CD4017BM, CD4022BC, CD4022BMDocument10 pagesCD4017BC, CD4017BM, CD4022BC, CD4022BMRajkumar DommetiNo ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- C.I 74HC175Document7 pagesC.I 74HC175DOMINGOS ALADIRNo ratings yet

- Octal Configurable Low/High Side Driver: DescriptionDocument18 pagesOctal Configurable Low/High Side Driver: DescriptionDan Esenther100% (1)

- MC33385 - Atm36bDocument11 pagesMC33385 - Atm36btason07No ratings yet

- DS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line ReceiversDocument8 pagesDS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line Receiversjnax101No ratings yet

- CD4027BM/CD4027BC Dual J-K Master/Slave Flip-Flop With Set and ResetDocument7 pagesCD4027BM/CD4027BC Dual J-K Master/Slave Flip-Flop With Set and ResetluckpoloNo ratings yet

- 74AC74Document9 pages74AC74ciernesNo ratings yet

- DM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesDocument6 pagesDM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesJonnathan AriasNo ratings yet

- 74AC04, 74ACT04 Hex Inverter: Features General DescriptionDocument10 pages74AC04, 74ACT04 Hex Inverter: Features General Descriptionarao_filhoNo ratings yet

- La 72730Document8 pagesLa 72730KHALILSAVNo ratings yet

- MC 14521Document12 pagesMC 14521rrebollarNo ratings yet

- S 24 Cs 08Document34 pagesS 24 Cs 08mj15015100% (1)

- 02 B - CD4001BCDocument6 pages02 B - CD4001BCtati_g10No ratings yet

- CD4015Document6 pagesCD4015Tecu CristiNo ratings yet

- 40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesDocument25 pages40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesNikole Cueva CevallosNo ratings yet

- Distributed byDocument42 pagesDistributed bydennyjoelNo ratings yet

- MM74HC14 Hex Inverting Schmitt Trigger: Features General DescriptionDocument10 pagesMM74HC14 Hex Inverting Schmitt Trigger: Features General Descriptiond_richard_dNo ratings yet

- 2114 Sram DatasheetDocument8 pages2114 Sram DatasheetntrscribeNo ratings yet

- 74HC04Document7 pages74HC04Brian DoyleNo ratings yet

- AZ324Document10 pagesAZ324Franklim Miranda Dos SantosNo ratings yet

- Datasheet 4511Document8 pagesDatasheet 4511Marcelo C. OliveiraNo ratings yet

- CD40174 40175Document6 pagesCD40174 40175scooby_maximoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Data Communication and Networking: For Under-graduate StudentsFrom EverandData Communication and Networking: For Under-graduate StudentsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Amibroker FileDocument9 pagesAmibroker FileNarendra BholeNo ratings yet

- Automatic Frequency Control of An Induction FurnaceDocument4 pagesAutomatic Frequency Control of An Induction FurnaceNarendra BholeNo ratings yet

- 4 Simple RTL (VHDL) Project With VivadoDocument6 pages4 Simple RTL (VHDL) Project With VivadoNarendra BholeNo ratings yet

- Modified Put Butterfly - FidelityDocument6 pagesModified Put Butterfly - FidelityNarendra BholeNo ratings yet

- Igbt Half Bridge: Inputs InputsDocument4 pagesIgbt Half Bridge: Inputs InputsNarendra BholeNo ratings yet

- Short Iron CondorDocument5 pagesShort Iron CondorNarendra Bhole100% (1)

- Inductance CalculatorDocument2 pagesInductance CalculatorNarendra BholeNo ratings yet

- Rahul Mohindar Oscillator: - Seasoned Trader - Panelist For CNBC and CNN IndiaDocument55 pagesRahul Mohindar Oscillator: - Seasoned Trader - Panelist For CNBC and CNN IndiaNarendra Bhole100% (1)

- AmiBroker Users' Knowledge Base AFL ProgrammingDocument18 pagesAmiBroker Users' Knowledge Base AFL ProgrammingNarendra BholeNo ratings yet

- Vibration Sensor/Transmitter: ApplicationsDocument2 pagesVibration Sensor/Transmitter: ApplicationsNarendra BholeNo ratings yet

- FractalDocument55 pagesFractalNarendra BholeNo ratings yet

- 189 Tony Crabels Intraday Signal ChartDocument13 pages189 Tony Crabels Intraday Signal ChartNarendra BholeNo ratings yet

- Demand Supply AflDocument2 pagesDemand Supply AflNarendra BholeNo ratings yet

- MT4Document17 pagesMT4Narendra BholeNo ratings yet

- Figure 1 - Terminal ConnectionsDocument6 pagesFigure 1 - Terminal ConnectionsNarendra BholeNo ratings yet

- Port Preparation:: Outline/Installation Drawing, Model Series 3030BDocument2 pagesPort Preparation:: Outline/Installation Drawing, Model Series 3030BNarendra BholeNo ratings yet

- Solid State Equipment For Bright Annealing of Stainless Steel PipesDocument1 pageSolid State Equipment For Bright Annealing of Stainless Steel PipesNarendra BholeNo ratings yet

- Grammar: Definite & Indefinite Articles: Unit 1: Our Cultural HeritageDocument2 pagesGrammar: Definite & Indefinite Articles: Unit 1: Our Cultural HeritageamalineNo ratings yet

- Critical Functions & Design Criteria For Geogrids Used in Reinforced Aggregate Raft Foundations For Christchurch Rebuilt - Jan 2013Document4 pagesCritical Functions & Design Criteria For Geogrids Used in Reinforced Aggregate Raft Foundations For Christchurch Rebuilt - Jan 2013Victor WongNo ratings yet

- Quiz 2 PDFDocument7 pagesQuiz 2 PDFRuth Montebon0% (1)

- 4 6041841339799176725 PDFDocument159 pages4 6041841339799176725 PDFFaez ArbabNo ratings yet

- Workshop Calculation (Unit 1)Document97 pagesWorkshop Calculation (Unit 1)Ajay PrasadNo ratings yet

- Electrical Work QuatationDocument3 pagesElectrical Work Quatationkiran100% (1)

- Acknowledgement: ReferencesDocument7 pagesAcknowledgement: Referencesdwayne420No ratings yet

- Mintmade FashionDocument15 pagesMintmade FashionJack ZNo ratings yet

- Commercial Audit Checklist ToolDocument27 pagesCommercial Audit Checklist ToolSouvik Ganguly0% (1)

- CV - 2022 12 06 072621Document2 pagesCV - 2022 12 06 072621Delima Acedilla Van JacobNo ratings yet

- Your Guide To Reading Your Electricity BillDocument2 pagesYour Guide To Reading Your Electricity BillMr SimpleNo ratings yet

- PR 6423/.. Series: Eddy Current Displacement SensorDocument4 pagesPR 6423/.. Series: Eddy Current Displacement SensorMohamad YusufNo ratings yet

- R and RC Firing CircuitsDocument3 pagesR and RC Firing CircuitsDeepa Mary Sobha70% (10)

- Fundamentals of Metal Joining Processes, Mechanism and Performance (Dheerendra Kumar Dwivedi) (Z-Library)Document449 pagesFundamentals of Metal Joining Processes, Mechanism and Performance (Dheerendra Kumar Dwivedi) (Z-Library)mekome7753No ratings yet

- MR - Mentoring EE Educators Towards PEEEngr. Cirilo Calibjo Nov. 27 2015Document74 pagesMR - Mentoring EE Educators Towards PEEEngr. Cirilo Calibjo Nov. 27 2015ramelNo ratings yet

- 10 de HSG Tap 3Document138 pages10 de HSG Tap 3Vân AnnhNo ratings yet

- Modelling of Triple Friction Pendulum Bearing in Sap2000 PDFDocument8 pagesModelling of Triple Friction Pendulum Bearing in Sap2000 PDFJ Guerhard GuerhardNo ratings yet

- Behance EgyptDocument12 pagesBehance Egyptdeepakshi rajputNo ratings yet

- Cisco901 HW OverDocument10 pagesCisco901 HW Overkala-majkaNo ratings yet

- Deepam Sir FileDocument3 pagesDeepam Sir FileGaurav GuptaNo ratings yet

- Alfonso Lopez CardiovascularDocument15 pagesAlfonso Lopez Cardiovascularjaniceli0207100% (1)

- Control 4Document17 pagesControl 4muhamed mahmoodNo ratings yet

- Laboratorios de Sensores PDFDocument238 pagesLaboratorios de Sensores PDFrimce77No ratings yet

- Alberts-Chapter 11-Membrane TransportDocument44 pagesAlberts-Chapter 11-Membrane TransportMayra SanchezNo ratings yet

- New Text DocumentDocument4 pagesNew Text DocumentGzim DragushaNo ratings yet

- Ideapad 100 15IBY 15IBD Platform Specifications PDFDocument2 pagesIdeapad 100 15IBY 15IBD Platform Specifications PDFmanocaoNo ratings yet

- The Rotator Cuff (Myofascial Techniques)Document4 pagesThe Rotator Cuff (Myofascial Techniques)Advanced-Trainings.com100% (3)

- Deborah Ohiani - MKT 2100 (Milestone 2)Document27 pagesDeborah Ohiani - MKT 2100 (Milestone 2)d2ohianiNo ratings yet

- Distribusi Nitrat, Oksigen Terlarut, Dan Suhu Di Perairan Socah-Kamal Kabupaten BangkalanDocument6 pagesDistribusi Nitrat, Oksigen Terlarut, Dan Suhu Di Perairan Socah-Kamal Kabupaten Bangkalanrobi gustiNo ratings yet

CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S Latches

CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S Latches

Uploaded by

Narendra BholeOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S Latches

CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S Latches

Uploaded by

Narendra BholeCopyright:

Available Formats

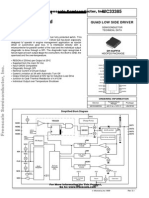

CD4043BC CD4044BC Quad 3-STATE NOR R/S Latches Quad 3-STATE NAND R/S Latches

October 1987 Revised March 2002

CD4043BC CD4044BC Quad 3-STATE NOR R/S Latches Quad 3-STATE NAND R/S Latches

General Description

The CD4043BC are quad cross-couple 3-STATE CMOS NOR latches, and the CD4044BC are quad cross-couple 3STATE CMOS NAND latches. Each latch has a separate Q output and individual SET and RESET inputs. There is a common 3-STATE ENABLE input for all four latches. A logic 1 on the ENABLE input connects the latch states to the Q outputs. A logic 0 on the ENABLE input disconnects the latch states from the Q outputs resulting in an open circuit condition on the Q output. The 3-STATE feature allows common bussing of the outputs.

Features

s Wide supply voltage range: s Low power: 100 nW (typ.) 3V to 15V s High noise immunity: 0.45 VDD (typ.) s Separate SET and RESET inputs for each latch s NOR and NAND configuration s 3-STATE output with common output enable

Applications

Multiple bus storage Strobed register Four bits of independent storage with output enable General digital logic

Ordering Code:

Order Number CD4043BCM CD4043BCN CD4044BCM CD4044BCSJ CD4044BCN Package Number M16A N16E M16A M16D N16E Package Description 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide

Devices also available in Tape and Reel. Specify by appending the suffix letter X to the ordering code.

Connection Diagrams

Pin Assignments for DIP, SOIC and SOP CD4043BC Pin Assignments for DIP and SOIC CD4044BC

Top View

Top View

2002 Fairchild Semiconductor Corporation

DS005967

www.fairchildsemi.com

CD4043BC CD4044BC

Block Diagrams

CD4043BC CD4044BC

Truth Tables

CD4043BC S X 0 1 0 1 R X 0 0 1 1 E 0 1 1 1 1 Q OC NC 1 0 S X 1 0 1 0 CD4044BC R X 1 1 0 0 E 0 1 1 1 1 Q OC NC 1 0

OC = 3-STATE NC = No change X = Dont care = Dominated by S = 1 input = Dominated by R = 0 input

www.fairchildsemi.com

CD4043BC CD4044BC

Absolute Maximum Ratings(Note 1)

(Note 2) Supply Voltage (VDD) Input Voltage (VIN) Storage Temperature Range (TS) Power Dissipation (PD) Dual-In-Line Small Outline Lead Temperature (TL) (Soldering, 10 seconds) 260C 700 mW 500 mW

Recommended Operating Conditions

(Note 2) Supply Voltage (VDD) Input Voltage (VIN) Operating Temperature Range (TA) CD4043BC, CD4044BC 3.0V to 15V 0 to VDD V

0.5V to +18V 0.5V to VDD +0.5V 65C to +150C

55C to +125C

Note 1: Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed; they are not meant to imply that the devices should be operated at these limits. The tables of Recommended Operating Conditions and Electrical Characteristics provide conditions for actual device operation. Note 2: VSS = 0V unless otherwise specified.

DC Electrical Characteristics

Symbol IDD Parameter Quiescent Device Current VOL LOW Level Output Voltage

(Note 2)

55C Min Max 5 10 20 0.05 0.05 0.05 4.95 9.95 14.95 1.5 3.0 4.0 3.5 7.0 11 0.64 1.6 4.2 0.64 1.6 4.2 0.1 0.1 3.5 7.0 11 0.51 1.3 3.4 0.51 1.3 3.4 4.95 9.95 14.95 Min +25C Typ 0.01 0.01 0.02 0 0 0 5.0 10 15 2.25 4.5 6.75 2.75 5.5 8.25 1.0 2.6 6.8 0.4 1.0 3.0 10.5 10.5 0.1 0.1 1.5 3.0 4.0 3.5 7.0 11 0.36 0.9 2.4 0.36 0.9 2.4 1.0 1.0 A mA mA V Max 5 10 20 0.05 0.05 0.05 4.95 9.95 14.95 1.5 3.0 4.0 V V +125C Min Max 150 300 600 0.05 0.05 0.05 V A Units

Conditions VDD = 5V, VIN = VDD or VSS VDD = 10V, VIN = VDD or VSS VDD = 15V, VIN = VDD or VSS |IO| 1 A, VIL = 0V, VIH = VDD VDD = 5.0V VDD = 10V VDD = 15V

VOH

HIGH Level Output Voltage

|IO| 1 A, VIL = 0V, VIH = VDD VDD = 5.0V VDD = 10V VDD = 15V

VIL

LOW Level Input Voltage

|IO| 1 A VDD = 5.0V, VO = 0.5V or 4.5V VDD = 10V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V

VIH

HIGH Level Input Voltage

|IO| 1 A VDD = 5.0V, VO = 0.5V or 4.5V VDD = 5.0V, VO = 1.0V or 9.0V VDD = 15V, VO = 1.5V or 13.5V

IOL

LOW Level Output Current (Note 3)

VIL = 0V, VIH = VDD VDD = 5.0V, VO = 0.4V VDD = 10V, VO = 0.5V VDD = 15V, VO = 1.5V VIL = 0V, VIH = VDD VDD = 5.0V, VO = 4.6V VDD = 10V, VO = 9.5V VDD = 15V, VO = 13.5V VDD = 15V, VIN = 0V VDD = 15V, VIN = 15V

IOH

HIGH Level Output Current (Note 3)

IIN

Input Current

Note 3: IOH and IOL are tested one output at a time.

www.fairchildsemi.com

CD4043BC CD4044BC

AC Electrical Characteristics

Symbol tPLH, tPHL Parameter Propagation Delay S or R to Q

(Note 4)

Conditions VDD = 5.0V VDD = 10V VDD = 15V Min Typ 175 75 60 115 55 40 100 50 40 100 50 40 80 40 20 5.0 Max 350 175 120 230 110 80 200 100 80 200 100 80 160 80 40 7.5 pF ns ns ns ns ns Units

TA = 25C, CL = 50 pF, RL = 200k, input tr = tf = 20 ns, unless otherwise noted

tPZH, tPHZ

Propagation Delay Enable to Q (HIGH)

VDD = 5.0V VDD = 10V VDD = 15V

tPZL, tPLZ

Propagation Delay Enable to Q (LOW)

VDD = 5.0V VDD = 10V VDD = 15V

tTHL, tTLH

Transition Time

VDD = 5.0V VDD = 10V VDD = 15V

tWO

Minimum SET or RESET Pulse Width

VDD = 5.0V VDD = 10V VDD = 15V

CIN

Input Capacitance

Note 4: AC Parameters are guaranteed by DC correlated testing.

Timing Waveforms

CD4043B CD4044B

Enable Timing

www.fairchildsemi.com

CD4043BC CD4044BC

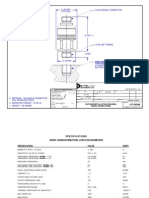

Physical Dimensions inches (millimeters) unless otherwise noted

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M16A

www.fairchildsemi.com

CD4043BC CD4044BC

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide Package Number M16D

www.fairchildsemi.com

CD4043BC CD4044BC Quad 3-STATE NOR R/S Latches Quad 3-STATE NAND R/S Latches

Physical Dimensions inches (millimeters) unless otherwise noted (Continued)

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications. LIFE SUPPORT POLICY FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user. 7 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com

www.fairchildsemi.com

You might also like

- Clil Lesson Plan TemplateDocument5 pagesClil Lesson Plan Templatesandovalz24433% (3)

- 11 Online Trading Academy PDFDocument16 pages11 Online Trading Academy PDFNarendra Bhole100% (3)

- Troubleshooting & Repairing Consumer Electronics Without a SchematicFrom EverandTroubleshooting & Repairing Consumer Electronics Without a SchematicNo ratings yet

- CD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDocument6 pagesCD4043BC - CD4044BC Quad 3-STATE NOR R/S Latches - Quad 3-STATE NAND R/S LatchesDouglas CorderoNo ratings yet

- 0 Ti 4 Kki 3 L 0243 Iulijdp 7 A 7 TapfyDocument8 pages0 Ti 4 Kki 3 L 0243 Iulijdp 7 A 7 TapfyjuenkkoNo ratings yet

- CD4023Document6 pagesCD4023Jules Le GrandNo ratings yet

- CD4011BCDocument10 pagesCD4011BCKike DavilaNo ratings yet

- CD 4050Document7 pagesCD 4050nicolaunmNo ratings yet

- NewDocument8 pagesNewxuankien181991No ratings yet

- CD4094BCDocument7 pagesCD4094BCEdgar MendezNo ratings yet

- CD 4069Document6 pagesCD 4069shaniimranNo ratings yet

- CD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesDocument6 pagesCD4015BC Dual 4-Bit Static Shift Register: General Description FeaturesMerényi OszkárNo ratings yet

- 74AC02 - 74ACT02 Quad 2-Input NOR Gate: General Description FeaturesDocument7 pages74AC02 - 74ACT02 Quad 2-Input NOR Gate: General Description FeaturesAlexandre S. CorrêaNo ratings yet

- CD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesDocument8 pagesCD4093BC Quad 2-Input NAND Schmitt Trigger: General Description FeaturesbanoluNo ratings yet

- CD4093 PDFDocument8 pagesCD4093 PDFIván IvanovNo ratings yet

- CD4028BC BCD-to-Decimal Decoder: General Description FeaturesDocument6 pagesCD4028BC BCD-to-Decimal Decoder: General Description Featuresmalirezazadeh5549No ratings yet

- Device Datasheet For CD4021Document7 pagesDevice Datasheet For CD4021bdfbNo ratings yet

- CD4020BC - CD4040BC - CD4060BC 14-Stage Ripple Carry Binary Counters - 12-Stage Ripple Carry Binary Counters - 14-Stage Ripple Carry Binary CountersDocument9 pagesCD4020BC - CD4040BC - CD4060BC 14-Stage Ripple Carry Binary Counters - 12-Stage Ripple Carry Binary Counters - 14-Stage Ripple Carry Binary CountersOsman KoçakNo ratings yet

- CD4511BCDocument8 pagesCD4511BCBiswajit SarkarNo ratings yet

- 4094BCDocument7 pages4094BCNelson RodriguezNo ratings yet

- 4096 Circuito IntegradoDocument7 pages4096 Circuito IntegradoalexmanriqueNo ratings yet

- 74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesDocument8 pages74AC00 - 74ACT00 Quad 2-Input NAND Gate: General Description FeaturesAini NierisNo ratings yet

- CD4029BC Presettable Binary/Decade Up/Down CounterDocument10 pagesCD4029BC Presettable Binary/Decade Up/Down CounterIbrahimEssamNo ratings yet

- CD4047Document9 pagesCD4047Haryadi VjNo ratings yet

- 74HC14 PDFDocument8 pages74HC14 PDFNielsy R. Aparicio QuirogaNo ratings yet

- 74 LV 00Document10 pages74 LV 00Brzata PticaNo ratings yet

- CD4071BC - CD4081BCDocument8 pagesCD4071BC - CD4081BCGustavo ZuñigaNo ratings yet

- Hoja de Datos cd4017Document9 pagesHoja de Datos cd4017FranciscoFloresNo ratings yet

- CD40106BC Hex Schmitt Trigger: General Description FeaturesDocument6 pagesCD40106BC Hex Schmitt Trigger: General Description Featuresgosa46No ratings yet

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849No ratings yet

- CD4017BC, CD4017BM, CD4022BC, CD4022BMDocument10 pagesCD4017BC, CD4017BM, CD4022BC, CD4022BMRajkumar DommetiNo ratings yet

- 74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsDocument11 pages74LCX374 Low Voltage Octal D-Type Flip-Flop With 5V Tolerant Inputs and OutputsRicardo MercadoNo ratings yet

- C.I 74HC175Document7 pagesC.I 74HC175DOMINGOS ALADIRNo ratings yet

- Octal Configurable Low/High Side Driver: DescriptionDocument18 pagesOctal Configurable Low/High Side Driver: DescriptionDan Esenther100% (1)

- MC33385 - Atm36bDocument11 pagesMC33385 - Atm36btason07No ratings yet

- DS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line ReceiversDocument8 pagesDS26LS32C/DS26LS32M/DS26LS32AC/DS26LS33C/ DS26LS33M/DS26LS33AC Quad Differential Line Receiversjnax101No ratings yet

- CD4027BM/CD4027BC Dual J-K Master/Slave Flip-Flop With Set and ResetDocument7 pagesCD4027BM/CD4027BC Dual J-K Master/Slave Flip-Flop With Set and ResetluckpoloNo ratings yet

- 74AC74Document9 pages74AC74ciernesNo ratings yet

- DM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesDocument6 pagesDM74LS244 Octal 3-STATE Buffer/Line Driver/Line Receiver: General Description FeaturesJonnathan AriasNo ratings yet

- 74AC04, 74ACT04 Hex Inverter: Features General DescriptionDocument10 pages74AC04, 74ACT04 Hex Inverter: Features General Descriptionarao_filhoNo ratings yet

- La 72730Document8 pagesLa 72730KHALILSAVNo ratings yet

- MC 14521Document12 pagesMC 14521rrebollarNo ratings yet

- S 24 Cs 08Document34 pagesS 24 Cs 08mj15015100% (1)

- 02 B - CD4001BCDocument6 pages02 B - CD4001BCtati_g10No ratings yet

- CD4015Document6 pagesCD4015Tecu CristiNo ratings yet

- 40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesDocument25 pages40V Precision Low Power Operational Amplifiers: ISL28117, ISL28217 FeaturesNikole Cueva CevallosNo ratings yet

- Distributed byDocument42 pagesDistributed bydennyjoelNo ratings yet

- MM74HC14 Hex Inverting Schmitt Trigger: Features General DescriptionDocument10 pagesMM74HC14 Hex Inverting Schmitt Trigger: Features General Descriptiond_richard_dNo ratings yet

- 2114 Sram DatasheetDocument8 pages2114 Sram DatasheetntrscribeNo ratings yet

- 74HC04Document7 pages74HC04Brian DoyleNo ratings yet

- AZ324Document10 pagesAZ324Franklim Miranda Dos SantosNo ratings yet

- Datasheet 4511Document8 pagesDatasheet 4511Marcelo C. OliveiraNo ratings yet

- CD40174 40175Document6 pagesCD40174 40175scooby_maximoNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Data Communication and Networking: For Under-graduate StudentsFrom EverandData Communication and Networking: For Under-graduate StudentsNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

- Amibroker FileDocument9 pagesAmibroker FileNarendra BholeNo ratings yet

- Automatic Frequency Control of An Induction FurnaceDocument4 pagesAutomatic Frequency Control of An Induction FurnaceNarendra BholeNo ratings yet

- 4 Simple RTL (VHDL) Project With VivadoDocument6 pages4 Simple RTL (VHDL) Project With VivadoNarendra BholeNo ratings yet

- Modified Put Butterfly - FidelityDocument6 pagesModified Put Butterfly - FidelityNarendra BholeNo ratings yet

- Igbt Half Bridge: Inputs InputsDocument4 pagesIgbt Half Bridge: Inputs InputsNarendra BholeNo ratings yet

- Short Iron CondorDocument5 pagesShort Iron CondorNarendra Bhole100% (1)

- Inductance CalculatorDocument2 pagesInductance CalculatorNarendra BholeNo ratings yet

- Rahul Mohindar Oscillator: - Seasoned Trader - Panelist For CNBC and CNN IndiaDocument55 pagesRahul Mohindar Oscillator: - Seasoned Trader - Panelist For CNBC and CNN IndiaNarendra Bhole100% (1)

- AmiBroker Users' Knowledge Base AFL ProgrammingDocument18 pagesAmiBroker Users' Knowledge Base AFL ProgrammingNarendra BholeNo ratings yet

- Vibration Sensor/Transmitter: ApplicationsDocument2 pagesVibration Sensor/Transmitter: ApplicationsNarendra BholeNo ratings yet

- FractalDocument55 pagesFractalNarendra BholeNo ratings yet

- 189 Tony Crabels Intraday Signal ChartDocument13 pages189 Tony Crabels Intraday Signal ChartNarendra BholeNo ratings yet

- Demand Supply AflDocument2 pagesDemand Supply AflNarendra BholeNo ratings yet

- MT4Document17 pagesMT4Narendra BholeNo ratings yet

- Figure 1 - Terminal ConnectionsDocument6 pagesFigure 1 - Terminal ConnectionsNarendra BholeNo ratings yet

- Port Preparation:: Outline/Installation Drawing, Model Series 3030BDocument2 pagesPort Preparation:: Outline/Installation Drawing, Model Series 3030BNarendra BholeNo ratings yet

- Solid State Equipment For Bright Annealing of Stainless Steel PipesDocument1 pageSolid State Equipment For Bright Annealing of Stainless Steel PipesNarendra BholeNo ratings yet

- Grammar: Definite & Indefinite Articles: Unit 1: Our Cultural HeritageDocument2 pagesGrammar: Definite & Indefinite Articles: Unit 1: Our Cultural HeritageamalineNo ratings yet

- Critical Functions & Design Criteria For Geogrids Used in Reinforced Aggregate Raft Foundations For Christchurch Rebuilt - Jan 2013Document4 pagesCritical Functions & Design Criteria For Geogrids Used in Reinforced Aggregate Raft Foundations For Christchurch Rebuilt - Jan 2013Victor WongNo ratings yet

- Quiz 2 PDFDocument7 pagesQuiz 2 PDFRuth Montebon0% (1)

- 4 6041841339799176725 PDFDocument159 pages4 6041841339799176725 PDFFaez ArbabNo ratings yet

- Workshop Calculation (Unit 1)Document97 pagesWorkshop Calculation (Unit 1)Ajay PrasadNo ratings yet

- Electrical Work QuatationDocument3 pagesElectrical Work Quatationkiran100% (1)

- Acknowledgement: ReferencesDocument7 pagesAcknowledgement: Referencesdwayne420No ratings yet

- Mintmade FashionDocument15 pagesMintmade FashionJack ZNo ratings yet

- Commercial Audit Checklist ToolDocument27 pagesCommercial Audit Checklist ToolSouvik Ganguly0% (1)

- CV - 2022 12 06 072621Document2 pagesCV - 2022 12 06 072621Delima Acedilla Van JacobNo ratings yet

- Your Guide To Reading Your Electricity BillDocument2 pagesYour Guide To Reading Your Electricity BillMr SimpleNo ratings yet

- PR 6423/.. Series: Eddy Current Displacement SensorDocument4 pagesPR 6423/.. Series: Eddy Current Displacement SensorMohamad YusufNo ratings yet

- R and RC Firing CircuitsDocument3 pagesR and RC Firing CircuitsDeepa Mary Sobha70% (10)

- Fundamentals of Metal Joining Processes, Mechanism and Performance (Dheerendra Kumar Dwivedi) (Z-Library)Document449 pagesFundamentals of Metal Joining Processes, Mechanism and Performance (Dheerendra Kumar Dwivedi) (Z-Library)mekome7753No ratings yet

- MR - Mentoring EE Educators Towards PEEEngr. Cirilo Calibjo Nov. 27 2015Document74 pagesMR - Mentoring EE Educators Towards PEEEngr. Cirilo Calibjo Nov. 27 2015ramelNo ratings yet

- 10 de HSG Tap 3Document138 pages10 de HSG Tap 3Vân AnnhNo ratings yet

- Modelling of Triple Friction Pendulum Bearing in Sap2000 PDFDocument8 pagesModelling of Triple Friction Pendulum Bearing in Sap2000 PDFJ Guerhard GuerhardNo ratings yet

- Behance EgyptDocument12 pagesBehance Egyptdeepakshi rajputNo ratings yet

- Cisco901 HW OverDocument10 pagesCisco901 HW Overkala-majkaNo ratings yet

- Deepam Sir FileDocument3 pagesDeepam Sir FileGaurav GuptaNo ratings yet

- Alfonso Lopez CardiovascularDocument15 pagesAlfonso Lopez Cardiovascularjaniceli0207100% (1)

- Control 4Document17 pagesControl 4muhamed mahmoodNo ratings yet

- Laboratorios de Sensores PDFDocument238 pagesLaboratorios de Sensores PDFrimce77No ratings yet

- Alberts-Chapter 11-Membrane TransportDocument44 pagesAlberts-Chapter 11-Membrane TransportMayra SanchezNo ratings yet

- New Text DocumentDocument4 pagesNew Text DocumentGzim DragushaNo ratings yet

- Ideapad 100 15IBY 15IBD Platform Specifications PDFDocument2 pagesIdeapad 100 15IBY 15IBD Platform Specifications PDFmanocaoNo ratings yet

- The Rotator Cuff (Myofascial Techniques)Document4 pagesThe Rotator Cuff (Myofascial Techniques)Advanced-Trainings.com100% (3)

- Deborah Ohiani - MKT 2100 (Milestone 2)Document27 pagesDeborah Ohiani - MKT 2100 (Milestone 2)d2ohianiNo ratings yet

- Distribusi Nitrat, Oksigen Terlarut, Dan Suhu Di Perairan Socah-Kamal Kabupaten BangkalanDocument6 pagesDistribusi Nitrat, Oksigen Terlarut, Dan Suhu Di Perairan Socah-Kamal Kabupaten Bangkalanrobi gustiNo ratings yet