Professional Documents

Culture Documents

Differential Amplifiers 10

Differential Amplifiers 10

Uploaded by

Miguel Ángel MerinoOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Differential Amplifiers 10

Differential Amplifiers 10

Uploaded by

Miguel Ángel MerinoCopyright:

Available Formats

1

Differential Amplifiers

1. General Considerations

2. Bipolar Differential Pair

3. MOS Differential Pair

4. Cascode Differential Amplifiers

5. Offset Voltage

6. Common-Mode Rejection

7. Distortion in Differential Pairs

8. Differential Pair with Active Load

Francisco Duque

E.I.I., UEx

2012-2013

Differential Amplifiers

2

1. General Considerations

Linear

System

Linearity principle

) (

1

t v

) (

2

t v

) ( ) (

2

t v k t v

o

=

) (

1

t v a

) (

2

t v b

) ( ) (

1

t v k t v

o

= ) ( ) (

1

t v a k t v

o

=

) ( ) (

2

t v b k t v

o

=

) ( ) (

2 1

t v b t v a +

| | ) ( ) ( ) (

2 1

t v b t v a k t v

o

+ =

Linear

System

Linear

System

Linear

System

Linear

System

Differential Amplifiers

3

1. General Considerations

Two-signals representation: CM and DM components

2

) ( ) (

) (

2 1

t v t v

t v

cm

+

=

) ( ) ( ) (

2 1

t v t v t v

dm

=

2

) (

) ( ) (

1

t v

t v t v

dm

cm

+ =

2

) (

) ( ) (

2

t v

t v t v

dm

cm

=

) (

2 ,

t v

i

) (

1 ,

t v

i

) (

1 ,

t v

o

) (

2 ,

t v

o

) (

,

t v

dm i

) (

,

t v

cm i

) (

,

t v

cm o

) (

,

t v

dm o

The response of any linear system with two input signals

can be described in terms of its response to CM input

signals (common-mode response) and its response to DM

input signals (differential response).

Linear

System

Linear

System

Differential Amplifiers

4

1. General Considerations

An audio amplifier is constructed above that takes on a

rectified AC voltage as its supply and amplifies an audio

signal from a microphone.

Audio amplifier example to understand the need

for differential circuits

Differential Amplifiers

5

(1) Humming Noise in Audio Amplifier Example

However, V

CC

contains a ripple from rectification that leaks

to the output and is perceived as a humming noise by the

user. V

out

is measured respect to ground and differs by R

C

I

C

from V

CC

.

C C CC out

I R V V =

Differential Amplifiers

6

(1) Supply Ripple Rejection

Now V

out

is not referenced to ground. Instead, is measured

respect to another point that itself experiences the same

supply ripple.

Since both node X and Y contain the ripple, their difference

will be free of ripple.

in v Y X

r Y

r in v X

v A v v

v v

v v A v

=

=

+ =

Perfect symmetrical circuit

(Q

1

=Q

2

and R

C1

=R

C2

).

Differential Amplifiers

7

(1) Ripple-Free Differential Output

Since the signal is taken as a difference between two nodes,

an amplifier A

1

that senses differential signals is needed.

Differential Amplifiers

8

(1) Common Inputs to Differential Amplifier

Signals cannot be applied in phase to the inputs of a differential

amplifier, since the outputs will also be in phase, producing

zero differential output.

0 =

+ =

+ =

Y X

r in v Y

r in v X

v v

v v A v

v v A v

Differential Amplifiers

9

(1) Differential Inputs to Differential Amplifier

When the inputs are applied differentially, the outputs are

180 out of phase; enhancing each other when sensed

differentially.

Of course, all CM signals still being removed.

in v Y X

r in v Y

r in v X

v A v v

v v A v

v v A v

2 =

+ =

+ =

Differential Amplifiers

10

(1) Differential Signals

A pair of differential signals can be generated, among other

ways, by a transformer.

Differential (DM) signals have the property that they share

the same average value to ground and are equal in

magnitude but opposite in phase.

Differential Amplifiers

11

(1) Single-ended vs Differential Signals

Single-ended signals (referenced to ground)

Differential (balanced) signals

CM

CM

V t V V

V t V V

+ =

+ =

e

e

si n

si n

0 2

0 1

Differential Amplifiers

12

(1) Differential Pair

With the addition of a tail current (I

EE

or I

SS

), the circuits

above operate as an elegant, yet robust differential pair.

Ideally, differential pairs are perfectly symmetric structures.

Bipolar differential pair

(Q

1

=Q

2

and R

C1

=R

C2

)

MOS differential pair

(M

1

=M

2

and R

D1

=R

D2

)

Differential Amplifiers

13

2. Bipolar Differential Pair

2

2

2 1

2 1

EE

C CC Y X

EE

C C

BE BE

I

R V V V

I

I I

V V

= =

= =

=

Q

1

and Q

2

operate in the active region

Qualitative Analysis: Common-Mode Rejection

If the circuit is perfectly symmetric (matched) there is not

response (differential output signal) to any common-mode

signal (input signal, supply noise, etc.).

CM

EE

C CC

V

I

R V >

2

Differential Amplifiers

14

(2) Common-Mode Rejection and Common-Mode

Voltage Range

Due to the fixed tail current source (ideal), the input common-

mode value can vary without changing the output common-

mode value. That is, the circuit rejects input CM variations.

To avoid saturation (Q

1

and Q

2

), the collector voltages must not

fall below the base voltages

CM

EE

C CC

V

I

R V >

2

Differential Amplifiers

15

(2) Differential Response (I)

CC Y

EE C CC X

C

EE C

V V

I R V V

I

I I

=

=

=

=

0

2

1

Response to a large positive input difference

EE C C

I I I = +

2 1

Differential Amplifiers

16

(2) Differential Response (II)

CC X

EE C CC Y

C

EE C

V V

I R V V

I

I I

=

=

=

=

0

1

2

Response to a large negative input difference

EE C C

I I I = +

2 1

Differential Amplifiers

17

(2) Differential Pair Characteristics

None-zero differential input produces variations in output

currents and voltages, whereas common-mode input

produces no variations.

2

EE

C CC

I

R V is called the output CM level.

Differential Amplifiers

18

(2) Small-Signal Analysis

Since the input (base) to Q

1

and Q

2

rises and falls by the same

amount, and their emitters are tied together, the rise in I

C1

has the

same magnitude as the fall in I

C2

.

I

I

I

I

I

I

EE

C

EE

C

A =

A + =

2

2

2

1

Response to small input differences (qualitatively

analysis)

Differential Amplifiers

19

For small changes at inputs, the g

m

s are the same, and the

respective increase and decrease of I

C1

and I

C2

are the same,

node P must stay constant to accommodate these changes.

Therefore, node P can be viewed as AC ground node.

V g I

V g I

V

m C

m C

P

A = A

A = A

= A

2

1

0

AC ground

(2) Small-Signal Analysis

Differential Amplifiers

20

(2) Small-Signal Differential Gain

Since the output changes by -2g

m

AVR

C

and input by 2AV, the small

signal gain is g

m

R

C

, similar to that of the CE stage. However, to

obtain same gain as the CE stage, power dissipation is doubled.

C m

C m

in

out

v

R g

V

R V g

V

V

A =

A

A

=

A

A

=

2

2

Differential Amplifiers

21

(2) Large Signal Analysis (I)

T

in in

EE

C

T

in in

T

in in

EE

C

V

V V

I

I

V

V V

V

V V

I

I

2 1

2

2 1

2 1

1

exp 1

exp 1

exp

+

=

=

EE C C

C

C

T in in

I I I

I

I

V V V

= +

=

2 1

2

1

2 1

l n

|

|

.

|

\

|

=

T

BE

S C

V

V

I I exp

Differential Amplifiers

22

(2) Large Signal Analysis (II)

T

in in

EE C

out out

V

V V

I R

V V

2

tanh

2 1

2 1

=

Input/Output Characteristics

Linear Region

(almost)

Differential Amplifiers

23

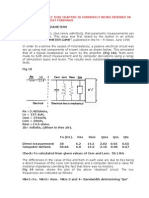

(2) Linear/Nonlinear Regions

The left column operates in linear region, whereas the right column

operates in nonlinear region.

EE C CC

I R V

CC

V

( ) 2

EE C CC

I R V

Differential Amplifiers

24

(2) Small-Signal Analysis

Differential Amplifiers

25

(2) Equivalent Half Circuit

Since V

P

is grounded, we can treat the differential pair as two CE

half circuits, with its gain equal to one half circuits single-ended

gain.

C m

in in

out out

R g

v v

v v

=

2 1

2 1

Differential Amplifiers

26

(2) Example: Intrinsic Differential Gain

O m

in in

out out

r g

v v

v v

=

2 1

2 1

The intrinsic gain of any circuit or device is the theoretical

maximum gain that it can provide. This is achieved when the load

has an infinite resistance (ideal current source).

Differential Amplifiers

27

(2) Extension of AC Ground Concept

It can be shown that if R

1

= R

2

, and points A and B go up and

down by the same amount respectively, V

X

does not move.

By extension, any node in the axis of symmetry of a perfectly

matched circuit is an AC Ground Node.

0

2 1

= A =

X

V R R

Differential Amplifiers

28

(2) Half Circuit (Example I)

( )

1 3 1 1

|| || R r r g A

O O m v

=

Equivalent half circuit

Application of the concept of AC ground

Differential Amplifiers

29

(2) Half Circuit (Example II)

( )

1 3 1 1

|| || R r r g A

O O m v

=

Equivalent half circuit

Application of the concept of AC ground

Differential Amplifiers

30

(2) Half Circuit (Example III)

m

E

C

v

g

R

R

A

1

+

=

Equivalent half circuit

Application of the concept of AC ground

Differential Amplifiers

31

(2) Half Circuit (Example IV)

m

E

C

v

g

R

R

A

1

2

+

=

Equivalent half circuit

Application of the concept of AC ground

Differential Amplifiers

32

3. MOS Differential Pair

Similar to its bipolar counterpart, MOS differential pair produces

zero differential output as V

CM

changes.

2

SS

D DD Y X

I

R V V V = =

Qualitative Analysis: Common-Mode Rejection

Differential Amplifiers

33

(3) Equilibrium Overdrive Voltage

The equilibrium overdrive voltage is defined as the overdrive

voltage (V

OV

= V

GS

V

TH

) seen by M

1

and M

2

when both of them

carry a current of I

SS

/2.

( )

|

SS

equil

TH GS

I

V V =

L

W

C

ox n

| =

( )

2

2

TH GS D

V V I =

|

Differential Amplifiers

34

(3) Minimum Common-Mode Output Voltage

In order to maintain M

1

and M

2

in saturation, the common-

mode output voltage cannot fall below the value above.

This value usually limits voltage gain.

TH CM

SS

D DD

V V

I

R V >

2

Differential Amplifiers

35

(3) Differential Response

Differential Amplifiers

36

(3) Small-Signal Response

Similar to its bipolar counterpart, the MOS differential pair

exhibits the same AC ground node (P) and small signal gain.

D m v

P

R g A

V

=

= A 0

Differential Amplifiers

37

(3) MOS Differential Pairs Large-Signal Response (I)

( )

SS D D

in in D D

I I I

V V I I

= +

=

2 1

2 1 , 2 1

2

|

( )

( )

( )

( )

2 , 1 , ,

2

2

, ,

2

2

2

, ,

1

2 /

1

2 2

2 /

1

2 2

in in dm i

equil

TH GS

dm i dm i

SS

SS

D

equil

TH GS

dm i dm i

SS

SS

D

V V V

V V

V V

I

I

I

V V

V V

I

I

I

=

=

+ =

|

|

Differential Amplifiers

38

(3) MOS Differential Pairs Large-Signal Response

(II)

( )

( )

2

2

,

, 2 1

2 /

1

equil

TH GS

dm i

dm i SS D D

V V

V

V I I I

= |

Differential Amplifiers

39

(3) Maximum Differential Input Voltage (III)

There exists a finite differential input voltage that completely

steers the tail current I

SS

from one transistor to the other. This

value is known as the maximum differential input voltage.

( )

equil

TH GS in in dm i

V V V V V = = 2

max

2 1

max

,

( )

equil

TH GS dm i

V V V > 2

,

) ; 0 (

2 1 SS D D

I I I

ZONE RATE SLEW

= =

Differential Amplifiers

40

(3) Contrast Between MOS and Bipolar Differential

Pairs

In a MOS differential pair, there exists a finite differential

input voltage to completely switch the current from one

transistor to the other, whereas, in a bipolar pair that

voltage is infinite.

MOS Bipolar

Differential Amplifiers

41

(3) The effects of Doubling the Tail Current

Since I

SS

is doubled and W/L is unchanged, the equilibrium

overdrive voltage for each transistor must increase by

to accommodate this change, thus AV

in,max

increases by

as well. Moreover, since I

SS

is doubled, the differential

output swing will double.

2

2

Differential Amplifiers

42

(3) The Effects of Doubling W/L

Since W/L is doubled and the tail current remains unchanged,

the equilibrium overdrive voltage will be lowered by

to

accommodate this change, thus AV

in,max

will be lowered by

as well. Moreover, the differential output swing will remain

unchanged since neither I

SS

nor R

D

has changed.

2

2

Differential Amplifiers

43

(3) Small-Signal Analysis of MOS Differential Pair

When the V

i,dm

is small compared to (V

GS

-V

TH

)

equil

=(I

SS

/|)

1/2

, the

output differential current is linearly proportional to it, and

small-signal model can be applied.

( )

( )

dm i SS

equil

TH GS

dm i

dm i SS D D

V I

V V

V

V I I I

,

2

2

,

, 2 1

2 /

1 ~

= | |

Differential Amplifiers

44

(3) AC Ground and Half Circuit

Applying the same analysis as the bipolar case, we will

arrive at the same conclusion that node P will not move for

small input signals and the concept of half circuit can be

used to calculate the gain.

C m v

P

R g A

V

=

= A 0

Differential Amplifiers

45

(3) MOS Differential Pair Half Circuit Example I

|

|

.

|

\

|

=

=

1 3

3

1

|| ||

1

0

O O

m

m v

r r

g

g A

Equivalent half circuit

Differential Amplifiers

46

(3) MOS Differential Pair Half Circuit Example II

3

1

0

m

m

v

g

g

A =

=

Equivalent half circuit

Differential Amplifiers

47

(3) MOS Differential Pair Half Circuit Example III

m SS

DD

v

g R

R

A

1 2

2

0

+

=

=

Differential Amplifiers

48

4. Cascode Differential Pair

( ) | |

1 3 3 1 3 1

||

O O O m m v

r r r r g g A + =

t

Bipolar Case

Differential Amplifiers

49

(4) Bipolar Telescopic Cascode

( ) | | | | ) || ( || ||

5 7 5 5 3 1 3 3 1 t t

r r r g r r r g g A

O O m O O m m v

~

Differential Amplifiers

50

(4) Example: Bipolar Telescopic Parasitic Resistance

| |

op O O m m v

O O m O op

R r r r g g A

R

r r

R

r r g r R

|| ) || (

2

|| ||

2

|| || 1

3 1 3 3 1

1

5 7

1

5 7 5 5

t

t t

=

+

(

|

.

|

\

|

+ =

Differential Amplifiers

51

(4) MOS Cascode Differential Pair

1 3 3 1 O m O m v

r g r g A ~

Differential Amplifiers

52

(4) MOS Telescopic Cascode

( ) | | ) ||(

7 5 5 1 3 3 1 O O m O O m m v

r r g r r g g A ~

Differential Amplifiers

53

(4) Example: MOS Telescopic Parasitic Resistance

( )

) || (

] 1 [ ||

1 3 3 1

7 7 5 1 5

O m O op m v

O O m O op

r g r R g A

r r g R r R

~

+ + =

Differential Amplifiers

54

5. Offset Voltage

Offset voltage is due to mismatches between components or

devices that ideally should be identical.

0

2 1

2 1

2 1

= =

=

= =

out out out

in in

D D D

V V V

V V

R R R

R

I

V V V

V V

R

R R

R

R R

SS

out out out

in in

D

D D

D

D D

A = =

=

A

=

A

+ =

2

2

2

2 1

2 1

2

1

Output offset voltage

Differential Amplifiers

55

(5) Input referred offset voltage

Input referred offset voltage (V

OS

) is the output offset voltage

divided by the small-signal gain.

V

OS

means the dc input differential voltage necessary to

compensate all the circuit mismatches and therefore, fix V

out

= 0.

D

D SS

D m

D

SS

v

out out

OS

R

R I

R g

R

I

A

V V

V

A

=

A

=

=

|

1

2 1 2

0

2 , 1 , .

= = =

out out out OS dm in

V V V V V

Differential Amplifiers

56

6. Common-Mode Rejection

If the tail current source is not ideal, then when a input CM

voltage is applied, the currents in Q

1

and Q

2

and hence output

CM voltage, will change.

m EE

C

CM in

CM out

g R

R

V

V

2 / 1

2 /

,

,

+

=

A

A

Effect of Finite Tail Impedance

Differential Amplifiers

57

(6) Input CM Noise with Ideal and Non-Ideal Tail

Current

As it can be seen, the differential output voltages for both cases

are the same. So, for small input CM noise the differential pair is

not affected.

=

EE

R =

EE

R

Differential Amplifiers

58

(6) CM to DM Conversion, A

CM-DM

If finite tail impedance and asymmetry are both present, then

the differential output signal will contain a portion of input

common-mode signal.

SS m

D

CM

out

R g

R

V

V

+

A

=

A

A

2 / 1

Differential Amplifiers

59

(6) Common-Mode Rejection Ratio (CMRR)

CMRR defines the ratio of wanted amplified differential input

signal to unwanted converted input common-mode noise that

appears at the output.

DM CM

DM

A

A

CMRR

=

Differential Amplifiers

60

General considerations for harmonic distortion

Transfer characteristic (input vs output) is not a straight line in

circuits with active devices.

Both, small-signal and large-signal, have nonlinearity problems.

7. Distortion in Differential Pairs

Nonlinear

System

) (t v

in

) (t v

out

2

2 1 in in out

v G v G v + =

Let us assume:

where G

1

and G

2

are constant.

( ) ( ) ( )

( ) ( ) t B t B B

t V G t V G v t V v

out in

1 2 1 1 0

1

2 2

1 2 1 1 1 1 1

2 cos cos

cos cos cos

e e

e e e

+ + =

= + = =

2

nd

harmonic distortion is introduced:

1

2

2

B

B

HD =

( ) o o 2 cos 1

2

1

cos

2

+ =

Differential Amplifiers

61

(7) High order harmonic distortion

Nonlinear

System

) (t v

in

) (t v

out

( )

( ) ( ) ( ) + + + + =

=

+ + + =

t B t B t B B v

t V v

v G v G v G v

out

in

in in in out

1 3 1 2 1 1 0

1 1

3

3

2

2 1

3 cos 2 cos cos

cos

e e e

e

- n

th

harmonic distortion:

1

B

B

HD

n

n

=

- Power delivered at the fundamental frequency:

L

R

B

P

=

2

2

1

1

- Total power output:

( ) ( )

1

2

3

2

2

2

3

2

2

2

1

1

2

1

P HD HD

R

B B B P

L

+ + + =

+ + + =

- Total Harmonic Distortion:

+ + + =

2

3

2

2

1 HD HD THD

Differential Amplifiers

62

(7) Distortion in MOS Differential Pair

|

|

.

|

\

|

= =

SS

i

i SS

SS

i

i SS D D D

I

V

V I

I

V

V I I I I

4 2

1

4

1

3 2

2 1

|

|

|

|

( ) x x x x x ~ =

2

1

1

16

1

8

1

2

1

1 1

3 2 5 . 0

( ) o o o 3 cos cos 3

4

1

cos

3

+ =

Differential Amplifiers

63

(7) Distortion in MOS Differential Pair

(

|

|

.

|

\

|

= =

=

t

I

A

t

I

A

A I I I I

t A V

SS SS

SS D D D

i

1

3

1

3

2 1

1

3 cos

16 2

1

cos

16 2

3

cos

e

|

e

|

|

e

0

1

2

2

= =

B

B

HD

( )

2

2

1

3

3

32

1

32

1

(

(

= =

equil

TH GS SS

V V

A

I

A

B

B

HD

|

Cancellation of even harmonics is a typical performance feature

of differential circuit structures.

Differential Amplifiers

64

Differential to Single-ended Conversion

Many circuits require a differential to single-ended

conversion, however, the above topology is not very good.

8. Differential Pair with Active Load

Differential Amplifiers

65

(8) Supply Noise Corruption

The most critical drawback of this topology is supply noise

corruption, since no common-mode cancellation mechanism

exists. Also, we lose half of the signal.

Differential Amplifiers

66

(8) Better Alternative

This circuit topology performs differential to single-ended

conversion with no loss of gain.

Differential Amplifiers

67

(8) Active Load

With current mirror used as the load, the signal current

produced by the Q

1

can be replicated onto Q

4

.

This type of load is different from the conventional static

load and is known as an active load.

Differential Amplifiers

68

(8) Differential Pair with Active Load

The input differential pair decreases the current drawn from

R

L

by AI and the active load pushes an extra AI into R

L

by

current mirror action; these effects enhance each other.

Differential Amplifiers

69

(8) Active Load vs. Static Load

The load on the left responds to the input signal and

enhances the single-ended output, whereas the load on the

right does not.

Differential Amplifiers

70

(8) MOS Differential Pair with Active Load

Similar to its bipolar counterpart, MOS differential pair can

also use active load to enhance its single-ended output.

Differential Amplifiers

71

(8) Asymmetric Differential Pair

Because of the vastly different resistance magnitude at the

drains of M

1

and M

2

, the voltage swings at these two nodes

are different and therefore node P cannot be viewed as a

virtual ground.

Differential Amplifiers

72

(8) Thevenin Equivalent of the Input Pair

oN Thev

in in oN mN Thev

r R

v v r g v

=

=

2

) (

2 1

Differential Amplifiers

73

(8) Simplified Differential Pair with Active Load

) || (

2 1

OP ON mN

in in

out

r r g

v v

v

=

Differential Amplifiers

74

I

A

(8) Proof of V

A

<<

V

out

OP mP

out

A

r g

v

v

2

~

A m

O

out

v g

r

v

I

4

4

=

You might also like

- Chapter 11 Part 4 Multistage Amplifier - Sem1 1617Document9 pagesChapter 11 Part 4 Multistage Amplifier - Sem1 1617Yue Kai100% (1)

- MH 02N 2Document36 pagesMH 02N 2ganeshNo ratings yet

- Impedance Matching Lab - 3Document5 pagesImpedance Matching Lab - 3Mihail100% (2)

- Printed Notes On Operational Amplifiers and Differential Amplifier and Numericals Based On The SameDocument98 pagesPrinted Notes On Operational Amplifiers and Differential Amplifier and Numericals Based On The SameDiptiNo ratings yet

- Opamp Lecture PDFDocument163 pagesOpamp Lecture PDFPriyatham KattaNo ratings yet

- Differential Amplifier PDFDocument42 pagesDifferential Amplifier PDFrsbecool100% (2)

- Chapter Two Differential Amplifiers 2nd LectureDocument35 pagesChapter Two Differential Amplifiers 2nd LectureTemesgen MekonenNo ratings yet

- Differential AmplifierDocument15 pagesDifferential AmplifierrppvchNo ratings yet

- BJT Single Stage CE AmplifierDocument10 pagesBJT Single Stage CE AmplifierVăn Công100% (1)

- Trapezoidal RuleDocument10 pagesTrapezoidal RuleRicardo Wan Aguero0% (1)

- Basics of Differential AmplifierDocument6 pagesBasics of Differential AmplifierveeranjaneyulugopuNo ratings yet

- Fourier Series Problems and SolutionDocument78 pagesFourier Series Problems and SolutionGellie Buenaventura100% (1)

- Passive Low Pass FilterDocument5 pagesPassive Low Pass FilterAnonymous SOQFPWB100% (1)

- From Unimap, Malaysia Louisiana State U HK City U Eastern Washington UDocument31 pagesFrom Unimap, Malaysia Louisiana State U HK City U Eastern Washington UKingLokeshNo ratings yet

- Transistor Active High Pass Filter Electronics NotesDocument2 pagesTransistor Active High Pass Filter Electronics NotesRenato DeákNo ratings yet

- Lecture 5: Transformers (Continued)Document16 pagesLecture 5: Transformers (Continued)Aldiansyah dtsNo ratings yet

- Chapter4 Semiconductor in Equilibrium - 2Document50 pagesChapter4 Semiconductor in Equilibrium - 2Mukesh KumarNo ratings yet

- Basic VLSI SlidesDocument91 pagesBasic VLSI SlidesDivya AhujaNo ratings yet

- Unit V - Active FiltersDocument14 pagesUnit V - Active Filterseshwar_worldNo ratings yet

- BJT AC DC & MultistageDocument42 pagesBJT AC DC & MultistageJose EspinoNo ratings yet

- Experiment No. 4 Common Emitter Amplifier AIM: Fig 1. Circuit DiagramDocument4 pagesExperiment No. 4 Common Emitter Amplifier AIM: Fig 1. Circuit Diagrampandiyarajan142611No ratings yet

- Chapter 6 Active-FiltersDocument39 pagesChapter 6 Active-FiltersIs Mohd100% (1)

- Iraudamp1 PDFDocument22 pagesIraudamp1 PDFamijoski6051No ratings yet

- Vented. Box Loudspeaker Systems Part I1: Large-Signal AnalysisDocument7 pagesVented. Box Loudspeaker Systems Part I1: Large-Signal AnalysisEclys MontenegroNo ratings yet

- Pro Co Rat AnalysisDocument16 pagesPro Co Rat AnalysisgianmarcoNo ratings yet

- Steber An LMS Impedance BridgeDocument7 pagesSteber An LMS Impedance BridgebigpriapNo ratings yet

- Differential and Multistage AmplifierDocument43 pagesDifferential and Multistage AmplifierΜαρια ΡοδακοπουλουNo ratings yet

- (F32FOU: Fourier Methods) : F32CO5: Wave PhenomenaDocument22 pages(F32FOU: Fourier Methods) : F32CO5: Wave PhenomenaNina BrownNo ratings yet

- Baxandall Tone ControlDocument7 pagesBaxandall Tone ControlSheeNo ratings yet

- Impedance Matching and The Smith Chart: The FundamentalsDocument18 pagesImpedance Matching and The Smith Chart: The FundamentalsKanwalAslamNo ratings yet

- The Jordan Loudspeaker Manual Chapter 6Document5 pagesThe Jordan Loudspeaker Manual Chapter 6Adam PaulNo ratings yet

- Lecture21 Multistage AmplifiersDocument10 pagesLecture21 Multistage AmplifierscitraumariNo ratings yet

- IntegratorDocument38 pagesIntegratorSyed AshmadNo ratings yet

- Wireless FM Microphone CircuitDocument2 pagesWireless FM Microphone Circuitcuongspvl2713No ratings yet

- 08-Com101 AMDocument11 pages08-Com101 AMHồng HoanNo ratings yet

- Astable MultivibratorDocument146 pagesAstable Multivibratorsantovaron123No ratings yet

- Time Dependent Perturbation TheoryDocument10 pagesTime Dependent Perturbation TheoryCarlos EduardoNo ratings yet

- Matlab 8Document12 pagesMatlab 8M Azeem100% (1)

- Precision RectifierDocument3 pagesPrecision RectifierQuentanahNo ratings yet

- 8237 Dma ControllerDocument14 pages8237 Dma ControllerSAIF ULLAH100% (1)

- 16.7 All-Pass Filter Design: Figure 16-41. Comparison of Q Between Passive and Active Band-Rejection FiltersDocument8 pages16.7 All-Pass Filter Design: Figure 16-41. Comparison of Q Between Passive and Active Band-Rejection FiltersseleneedithNo ratings yet

- Filter PDFDocument21 pagesFilter PDFNugraha PratamaNo ratings yet

- Transient of R.C. CircuitDocument9 pagesTransient of R.C. CircuitArinder SinghNo ratings yet

- Process Motion and Control PDFDocument8 pagesProcess Motion and Control PDFVaibhav SharmaNo ratings yet

- Stark Effect in Atomic SpectraDocument6 pagesStark Effect in Atomic Spectraflamesup41No ratings yet

- Unit - Iv MultivibratorsDocument41 pagesUnit - Iv MultivibratorsSanjana PulapaNo ratings yet

- Tuned Amplifier PDFDocument40 pagesTuned Amplifier PDFRichik KashyapNo ratings yet

- EE680Lab Experiment6-7Document21 pagesEE680Lab Experiment6-7Amro AbusailNo ratings yet

- Operational AmplifierDocument29 pagesOperational AmplifierTaha Al-abedNo ratings yet

- DTMF Encoding and DecodingDocument6 pagesDTMF Encoding and DecodingmastelecentroNo ratings yet

- Edc PDFDocument173 pagesEdc PDFsivaNo ratings yet

- Analog Circuits II Lab ManualDocument47 pagesAnalog Circuits II Lab ManualParesh SawantNo ratings yet

- Tuned Collector OscillatorDocument3 pagesTuned Collector OscillatorArvind Sharma100% (1)

- 14.4 Bode Plots: Frequency Response 589Document12 pages14.4 Bode Plots: Frequency Response 589Luis Lizana100% (1)

- BJT Diff AmplifierDocument15 pagesBJT Diff AmplifierAdrià Amézaga SàrriesNo ratings yet

- Controlled Rectifier Single Phase Full WaveDocument7 pagesControlled Rectifier Single Phase Full WaveJesus BecerraNo ratings yet

- Electronics CircuitDocument0 pagesElectronics Circuitwww.bhawesh.com.npNo ratings yet

- FALLSEM2012-13 CP0991 03-Aug-2012 RM01Document4 pagesFALLSEM2012-13 CP0991 03-Aug-2012 RM01Ankit BhattNo ratings yet

- Differential AmplifiersDocument8 pagesDifferential AmplifiersBhaskar YelamoluNo ratings yet

- PDF Microelectronic Circuits Adel S Sedra Ebook Full ChapterDocument53 pagesPDF Microelectronic Circuits Adel S Sedra Ebook Full Chapteranna.minich118100% (6)

- Band Gap ReferencesDocument115 pagesBand Gap ReferencesNam Luu Nguyen NhatNo ratings yet

- Lec 26Document5 pagesLec 26Piyush KumarNo ratings yet

- Ijert Ijert: Simulation of Two Stage Operational Amplifier Using 250nm and 350nm TechnologyDocument4 pagesIjert Ijert: Simulation of Two Stage Operational Amplifier Using 250nm and 350nm TechnologySYAMALANo ratings yet

- Differential and Multistage AmplifierDocument43 pagesDifferential and Multistage AmplifierΜαρια ΡοδακοπουλουNo ratings yet

- Bias Circuits For RF Devices: Iulian Rosu, YO3DAC / VA3IULDocument25 pagesBias Circuits For RF Devices: Iulian Rosu, YO3DAC / VA3IULRossi Paulo100% (1)

- Lesson Plan 1Document5 pagesLesson Plan 1G.NeelavathiNo ratings yet

- Differential AmplifierDocument7 pagesDifferential AmplifierTanvir Ahmed MunnaNo ratings yet

- Cascode High Swing PreciseDocument2 pagesCascode High Swing PreciselorisNo ratings yet

- Cmos Ota ThesisDocument5 pagesCmos Ota Thesislisabrownolathe100% (2)

- Power Amplifiers: Ranjith Office Level 4 - Building 193 - EEE BuildingDocument19 pagesPower Amplifiers: Ranjith Office Level 4 - Building 193 - EEE BuildingArambya Ankit KallurayaNo ratings yet

- Differential AmplifierDocument24 pagesDifferential Amplifierbommena vishwa tejaNo ratings yet

- Ald 1107Document6 pagesAld 1107tekellamerZ aka tekellamerNo ratings yet

- Quasi-Floating Gate Based High Precision Current Mirror: D. Rajesh, Dr. N. Raj, Dr. P. John PaulDocument12 pagesQuasi-Floating Gate Based High Precision Current Mirror: D. Rajesh, Dr. N. Raj, Dr. P. John PaulPeter HeinNo ratings yet

- A 1.8 Self-Biased Complementary Folded Cascode AmplifierDocument3 pagesA 1.8 Self-Biased Complementary Folded Cascode Amplifiernaxter25No ratings yet

- Third Year ECE Evaluation Scheme and Syllabus With COs PDFDocument28 pagesThird Year ECE Evaluation Scheme and Syllabus With COs PDFAnonymous eWMnRr70qNo ratings yet

- 電子學 (三) 蕭敏學1Document21 pages電子學 (三) 蕭敏學1scribbyscribNo ratings yet

- Designing of MOS Transistors in Two Stage OTA With Miller CompensationDocument7 pagesDesigning of MOS Transistors in Two Stage OTA With Miller CompensationjitendraNo ratings yet

- EE-313 Electronic Circuit Design Ver2 - Sp20Document5 pagesEE-313 Electronic Circuit Design Ver2 - Sp20Skiwordy MediaNo ratings yet

- Advanced Electronics Instrumentation MTEC-502-BDocument6 pagesAdvanced Electronics Instrumentation MTEC-502-BAnish BansalNo ratings yet

- Two Stage CompensationDocument26 pagesTwo Stage CompensationIndranil SarkarNo ratings yet

- CSD Exercise 3 v2Document8 pagesCSD Exercise 3 v2readerNo ratings yet

- GATE 2022: Battleground Test SeriesDocument13 pagesGATE 2022: Battleground Test SeriesAbdul SattarNo ratings yet

- Matching LayoutDocument41 pagesMatching Layoutvarun186No ratings yet

- Current MirrorsDocument15 pagesCurrent Mirrorsbommena vishwa tejaNo ratings yet

- ME VLSI & EmdDocument58 pagesME VLSI & EmdAnil V. WalkeNo ratings yet

- Analog Integrated CircuitsDocument47 pagesAnalog Integrated CircuitsDan GoleaNo ratings yet

- Operational AmplifierDocument25 pagesOperational AmplifierNeha KadamNo ratings yet

- Analog Circuits (Ecen 2101)Document5 pagesAnalog Circuits (Ecen 2101)sumitbhuia10No ratings yet

- M.tech Thesis VarunDocument78 pagesM.tech Thesis VarunAppala Naidu GottapuNo ratings yet