Professional Documents

Culture Documents

Final Report

Final Report

Uploaded by

Anand AnajiOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Final Report

Final Report

Uploaded by

Anand AnajiCopyright:

Available Formats

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Chapter 1 Introduction

1.1 Introduction and Motivation

Over the last two decades, the continuous shrinking in the feature size of MOSFETs has increasingly attracted the research and development of low-power radio frequency CMOS integrated circuits. For mobile wireless communications, low-power operations are of crucial importance for the mobile units as the battery lifetime is limited by the power consumption and the low power consumption also helps to reduce the operating temperature resulting in more stable performance. For the modern transceiver architecture, a fully integrated frequency synthesizer with low power voltage-controlled oscillators (VCO) for quadrature signal generation and low power frequency dividers with multi-channel selection is always a topic of interest in research. The existing wireless standards like Bluetooth and 802.11a/b/g offer relatively high data rates at the expenses of high power consumption and high cost. The IEEE 802.15.4 standard has been specifically designed to cater for the needs of low cost, low power, low data rate and short range wireless networks. Few frequency synthesizers based on this standard have been reported in literature and the frequency synthesizer reported in has the power consumption of 2.4 mW at 1.2V power supply. Most synthesizers have not scaled down the supply voltage to reduce the power consumption of digital blocks. It is believed that power consumption of the frequency synthesizer (mainly frequency divider) can be reduced significantly by further simplifying the circuit structures, and adapting some power saving techniques to the digital blocks such as frequency dividers.

1.2

Approach

The project gives detailed analysis, specifications and design of low power fully

programmable integer-N frequency divider which a critical block of frequency synthesizers for IEEE 802.15.4. The approach of the project is as follows:

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 1

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Design and Analysis of ultra-low power 2/3 TSPC prescaler A detailed analysis of power consumption and propagation speed of the dynamic logic flip-flops is carried out and an ultra-low power True-single-phase clock (TSPC) 2/3 prescaler is proposed which is verified in the design of TSPC 32/33 prescaler in 180nm CMOS technology. A low power TSPC 47/48 prescaler The design of a fully programmable 1 MHz resolution divider for the 2.4 GHz frequency synthesizer using a 32/33 prescaler, a 7-bit programmable P-counter and a 5-bit swallow S counter results in 1 MHz output with duty cycle less than 25%. In order to improve the duty cycle, a low power TSPC 47/48 prescaler is implemented without an additional flip-flop. This new design is similar to the design of 32/33 prescaler with an additional inverter.

1.3 Applications:

Frequency divider is a critical block of frequency synthesizer which has major applications in, Local oscillators for modulation and demodulation Phase locked loop (PLL) synthesizers and other counting circuits Radio receivers Mobile telephones GPS systems

1.4

Organization of the report

Chapter 1 gives an introduction about the programmable frequency dividers and its

principle in brief. Chapter 2 provides in detail the literature survey of CMOS logic family and also its electronic analysis. Chapter 3 describes steps in cadence tool to build the schematics and layouts and their verification using gpdk180 library of the EDA tool. Chapter 4 describes the implementation of the prescalers using cadence tools demonstrating the difference between the traditional and modified designs. Chapter 5 gives an exhaustive account of how the traditional prescaler is modified to obtain new designs. Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 2

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Chapter 2 Literature Survey

2.1 Logic family

A logic family of monolithic digital integrated circuit devices is a group of electronic logic gates constructed using one of several different designs, usually with compatible logic levels and power supply characteristics within a family were produced as individual components, each containing one or a few related basic logical functions, which could be used as building blocks to create systems or as so called glue to interconnect more complex integrated circuits. A logic family may also refer to a set of techniques used to implement logic within VLSI integrated circuits such as central processors, memories, or other complex functions. Packaged building block logic families which are compatible to the proposed design are CMOS (complementary metal oxide semiconductor logic) and TTL (Transistor Transistor Logic).

2.2 Comparison between TTL and CMOS logic families

TTL stands for Transistor-Transistor Logic. It is a classification of integrated circuits. The name is derived from the use of two Bipolar Junction Transistors or BJTs in the design of each logic gate. CMOS is also another classification of ICs that uses Field Effect Transistors in the design. A brief comparison between these logic families highlights the advantage of CMOS as follows:

2.2.1 Characteristics of CMOS logic family

Some important characteristics of the CMOS logic family are as given below Dissipates low power - The power dissipation is dependent on the power supply voltage, frequency, output load, and input rise time. At 1 MHz and 50 pF load, the power dissipation is typically 10 nW per gate [1]. Short propagation delays - Depending on the power supply, the propagation delays are usually around 25ns to 50ns.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 3

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Rise and fall are controlled - The rise and falls are usually ramps instead of step functions, and they are 20 to 40% longer than the propagation delays. Levels of the logic signal will be essentially equal to the power supplied since the input impedance is so high.

2.2.2 Characteristics of TTL logic family

Some important characteristics of the TTL logic family are as given below Power dissipation is usually 10 mW per gate. Propagation delays are 10 ns when driving a 15 pF/400 ohm load [2]. Voltage levels range from 0 to Vcc is typically 4.75V to 5.25V. Voltage range 0V to 0.8V creates logic level 0. Voltage range 2V to Vcc creates logic level 1.

2.2.3 Advantages of CMOS over TTL

Some important advantages of the CMOS over TTL logic family are as given below CMOS components are typically more expensive that TTL equivalents. However, CMOS technology is usually less expensive on a system level due to CMOS chips being smaller and requiring less regulation. CMOS allows much higher density of logic functions in a single chip compared to TTL. CMOS circuits do not draw as much power as TTL circuits while at rest. CMOS requires lower current draw requires less power supply distribution, therefore causing a simpler design. Due to longer rise and fall times, the transmission of digital signals becomes simpler and less expensive with CMOS chips. CMOS components are more susceptible to damage from electrostatic discharge than TTL components.

2.3 Electronic analysis of MOSFET

The voltage applied to the gate controls the flow of electrons from the source to the drain. A positive voltage (for NMOS) or negative voltage (for PMOS) applied to the gate attracts electrons (holes) to the interface between the gate dielectric and the semiconductor. These electrons form a conducting channel called the inversion layer. No gate current is Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 4

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

required to maintain the inversion layer at the interface since the gate oxide blocks any carrier flow. The net result is that the applied gate voltage controls the current between drain and source.

2.3.1 Pass Characteristics of NMOS-FET

The schematic diagram of NMOS-FET (nFET) pass transistor is as shown in the Fig. 2.1. The input pulse V1 has a voltage 1.8V and the output voltage Vout is measured across the capacitive load Cout. The value of capacitor represents the total capacitance at the output node and has several contributions.

Fig.2.1. Schematic Diagram of NMOS-FET Fig.2.2 summarizes the behavior of the device when NMOS is used to pass the voltage from left to right. Applying VDD to the gate ensures that the nFET is ON and the device acts like a closed switch. If a logic 0V is applied to source of NMOS, this results in an output is applied, Vout is

voltage of Vout= 0V as shown in Fig. 2.2. if input voltage of V 1 =V DD reduced to a value Vout=VDD VTn Vout =1.8V 0.53V Vout =1.273V Dept of Electronics & Communication, SIT Tumkur 2012-13

(2.1)

Page 5

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Which is less than the input voltage V 1 this is referred to as threshold voltage loss. It arises due to the fact that the minimum value of the gate-source voltage. So maintain an on state Gate to source voltage of VGSn=VTn= 0.53V. (2.2)

Fig.2.2. NMOS pass characteristic From the waveforms in Fig 2.2 it can be concluded that, NMOS-FET can pass strong logic 0 NMOS-FET can pass weak logic 1

2.3.2 Pass Characteristics of PMOS-FET

A pFET has opposite pass characteristics as of nFET. To examine the properties of PMOS, logic 0 is applied to Gate as shown in Fig.2.3. Fig.2.4 summarizes the behavior of the device when PMOS is used to pass the voltage from left to right. Applying logic 0 to the gate ensures that the pFET is ON and the device acts like a closed switch. If an input voltage of V1= 1.8 V is applied to source of PMOS, this results in an output voltage of Vout= 1.8 V as desired, this is shown in Fig.2.4. Decreasing the input voltage results in that value is being transmitted to the output side.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 6

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 2.3. Schematic diagram of pass PMOS-FET

However if input voltage of V 1 = 0 V is applied, Vout is not equal to 0 V, but Vout=V Tp = 0.619V (2.3)

This is also due to a threshold effect. In order to keep the pFET ON it requires a minimum source-gate voltage of V SGp =V Tp = 0.619V (2.4)

From the waveforms in Fig 2.4 it can be concluded that, PMOS-FET can pass strong logic 1 PMOS-FET can pass weak logic 0

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 7

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 2.4. PMOS Pass characteristic

Thus we can write following rules as a basis for our design: 1. Use pFETs to pass logic 1 voltages of V DD . 2. Use nFETs to pass logic 0 voltages of V SS = 0V. These allow us to build circuits that can pass the ideal logic voltages 0V and V DD to the output terminal.

2.4 Summary

In this chapter, with the availability of many logic families, CMOS logic was opted for the design part and implementation using Cadence.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 8

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Chapter 3 Implementation using Cadence Tools

Cadence on virtuoso platform provides tools for designing full-custom integrated circuits which includes schematic entry, behavioral modeling and circuit simulation. Cadence enables the realization of silicon chips, system-on-chip devices, and complete systems at lower costs with high quality [2].

3.1 Design Steps using Cadence Software

1. Create Library

In command Interpreter Window (CIW) or library manager execute: File New Library Attach design library to an existing technology library and select gpdk as shown in Fig. 3.1

Fig. 3.1 creating a new library from the CIW window

2. Schematic Entry

In CIW, execute: File New cell view. In the blank schematic window add components from the respective library and set their specifications to the requirement. Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 9

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Add wires to the schematic, check and save, as shown in Fig 3.2. The CIW window is checked for any errors or warnings in the schematic.

Fig. 3.2 Creation of TSPC schematic

3. Symbol creation

In the schematic window, execute: Create Cell view From Cell view. Fill in the Symbol Generation Options (which include the positions and direction of pins) appropriately, check and save, as shown in Fig 3.3.

Fig. 3.3 Creation of TSPC symbol

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 10

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.

Test schematic

In CIW, execute: File New Cell view A blank schematic window for the test schematic design appears. Add the components using create instance. Complete the connection, check and save, as shown in Fig. 3.4. The CIW window is observed for any errors.

Fig. 3.4 Creation of TSPC test schematic

5.

State)

Simulation with spectre

In the test schematic window, execute: Launch ADEL, as shown in Fig 3.5 Choose Analysis as per requirement and set the specifications. In the simulation window, execute: Outputs To be plotted select on schematic In the simulation window, execute: simulation Net List Observe the transient plots In the simulation window, execute: Session Save State ( to save the current working

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 11

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 3.5 Simulation with spectre in ADEL environment

6.

Delay calculation

From the graph obtained after simulation, execute: Tools Calculator, which opens up the window as shown in Fig. 3.6. Select the delay function from the list of functions provided. Clear buffer and stack. Provide the two necessary signal inputs for delay calculation from the graph or the schematic window. In the same window, execute: Apply Evaluate the buffer

Fig. 3.6 Delay calculation using the in-built calculator Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 12

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

3.2 Design methodology

CADENCE: Electronic design automation (EDA or ECAD) is a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits. The tools work together in a design flow that chip designers use to design and analyze entire semiconductor chips. One of the EDA softwares is CADENCE DESIGN SYSTEM.

3.2.1 Design specifications

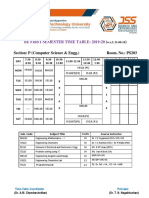

The bottomup design flow for a transistor-level circuit layout always starts with a set of design specifications. The specifications typically describe the expected functionality (Boolean operations) of the designed block, as well as the maximum allowable delay times, the silicon area and other properties such as power dissipation. Usually, the design specifications allow considerable freedom to the circuit designer on issues concerning the choice of a specific circuit topology, individual placement of the devices, the locations of input and output pins, and the overall aspect ratio (width-to-height ratio) of the final design. The basic components used, along with their specifications have been provided in Table. 3.1 Table.3.1 Design specifications of basic components used in simulation

Component

Specifications Width w = 3 um

Library

pMOS

Length l = 180nm Width w = 1.7um

gpdk 180

nMOS

Length l = 180nm Voltage V1 = 0 V

gpdk 180

Vpulse Vdc

Voltage V2 = 1.8 V Voltage Vdc = 1.8 V

analogLib analogLib

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 13

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

3.2.2 Selecting P/N ratio

The circuit is designed using standard PMOS and CMOS feature size 180nm with the PMOS to NMOS ratio being 2. Static CMOS gates are a ratio less circuit family, the gates will work correctly for any ratio of PMOS sizes to NMOS sizes. However, the ratio do influence switching threshold and delay, so it is important to optimize the P/N ratio for high speed designs. Using a higher or lower P/N ratio favors rising or falling outputs, respectively. For example, with a P/N ratio of 4/1, the input does not have to fall as far as V dd/2 before the output could switch. Such a circuit is called a high skewed gate and use it on paths where the critical transition is a rising output. Similarly, a 1/1 P/N ratio could be used in a low skewed gate for critical falling outputs.

3.2.3 Creating schematic

The method for describing the transistor level or gate level design is via the schematic editor. Schematic editors provide simple, intuitive means to draw, to place and to connect individual components that make up the design. The resulting schematic drawings must accurately describe the main electrical properties of all components and their interconnections. Power supply and ground connections, as well as all pins for the input and output signals of the circuit. This information is crucial for generating the corresponding netlist, which is used in later stages of the design. The generation of a complete circuit schematic is therefore the first important step of the transistor-level design flow. Usually, some properties of the components (e.g. transistor dimensions) and/or the interconnections between the devices are subsequently modified as a result of iterative optimization steps. These later modifications and improvements on the circuit structure must also be accurately reflected in the most current version of the corresponding schematic. An example of a TSPC schematic has been shown in Fig. 3.7.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 14

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 3.7 Schematic of TSPC circuit

3.2.4 Symbol creation

If a certain circuit design consists of smaller hierarchical components (or modules), it is usually very beneficial to identify such modules early in the design process and to assign each such module a corresponding symbol (or icon) to represent that circuit module. This step largely simplifies the schematic representation of the overall system. The symbol view of a circuit module is an icon that stands for the collection of all components within the module. A symbol view of the circuit is also required for some of the subsequent simulation steps, thus, the schematic capture of the circuit topology is usually followed by the creation of a symbol to represent the entire circuit. The shape of the icon to be used for the symbol may suggest the function of the module (e.g. logic gates AND, OR, NAND, NOR), but the default symbol icon is a simple rectangular box with input and output pins. Note that this icon can now be used as the building block of another module, and so on, allowing the circuit designer to create a system-level design consisting of multiple hierarchy levels.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 15

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

3.2.5 Simulation of schematic

After the transistor level description of a circuit is completed using the schematic editor, the electrical performance and the functionality of the circuit must be verified using a simulation tool. The detailed transistor level simulation of the design will be the first in depth validation of its operation; hence, it is extremely important to complete this step before proceeding with the subsequent design optimization steps. Based on simulation results, some of the device properties such as transistor width-to-length ratio are modified in order to optimize the performance. As the first step, the symbol of the component created is inserted and the inputs are provided with variable pulses to cover all combinations possible. Vdd supply is provided using Vdc = 1.8 V. the outputs are connected to output pins. Analog Design Environment (ADEL) is launched and transient analysis is chosen. This analysis is performed for a desired period with moderate accuracy. The outputs to be plotted are selected from schematic and the simulation is run for these specifications. The delay is then calculated from the response obtained.

3.2.6 Mask layout

Physical layout design is very tightly linked to overall circuit performance (area, speed and power dissipation) since the physical structure determines the transconductances of the transistors, the parasitic capacitances and resistances, and the silicon area which is used to realize a certain function. The physical (mask layout) design of CMOS logic gates is an iterative process which starts with the circuit topology and the initial sizing of the transistors.

3.2.7 Design Rule Check (DRC)

The created mask layout must conform to a complex set of design rules, in order to ensure a lower probability of fabrication defects. A tool built into the Layout Editor, called Design Rule Checker, is used to detect any design rule violations during and after the mask layout design.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 16

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

3.2.8 Extraction

The circuit extractor is capable of identifying the individual transistors and their interconnections on various layers, as well as the parasitic resistances and capacitances that are inevitably present between these layers. Thus, the extracted net-list can provide a very accurate estimation of the actual device dimensions and device parasitic that ultimately determine the circuit performance.

3.2.9 Layout versus Schematic check (LVS)

The design called Layout-versus-Schematic (LVS) Check will compare the original network with the one extracted from the mask layout, and prove that the two networks are indeed equivalent. The LVS step provides an additional level of confidence for the integrity of the design, and ensures that the mask layout is a correct realization of the intended circuit topology.

3.2.10 Post Layout Simulation

The electrical performance of a full-custom design can be best analyzed by performing a post-layout simulation on the extracted circuit net-list. At this point, the designer should have a complete mask layout of the intended circuit/system, and should have passed the DRC and LVS steps with no violations. The detailed (transistor-level) simulation performed using the extracted net-list will provide a clear assessment of the circuit speed, the influence of circuit parasitics

3.3

Discussion

In this chapter, the implementation details of the various designs of Prescaler using

Cadence has been discussed, clearly outlining the specifications needed for every circuit design. Care was taken to choose the P/N ratio as per the requirements, along with the other necessities. A comparison was also provided regarding the number of gates and transistors used.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 17

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Chapter 4 Analysis of Ultra Low Power Prescaler

The prescaler is one of the most critical blocks in the synthesizer since it operates at the highest frequency and consumes a large amount of power. Thus the power reduction in the first stage of the prescaler is important in realizing a low power frequency synthesizer. A dualmodulus prescaler such as divide-by-32/33, divide-by-64/65 and divide-by-128/129

usually consists of a synchronous divide-by-2/3 or divide-by-4/5 circuit combined with several asynchronous divide-by-2 circuits.

4.1

Prescaler

The high speed dual modulus prescaler is a critical functional block in frequency

synthesizers which uses wide-band pulse swallow frequency dividers operates the prescaler at the highest frequencies and consumes more power than other circuit blocks of the frequency synthesizer. In a pulse swallow frequency divider, the prescaler has two selectable division ratios and . It is combined with programmable counters P and S as in Fig. 4.1 to .

perform a programmable division ratio of

The prescaler is a synchronous circuit which is formed by D flip-flops and additional logic gates, due to the incorporation of additional logic gates between the flip-flops to achieve the two different division ratios, the speed of the prescaler is affected and the switching power increases. Various flip-flops have been proposed to improve the operating speed of dualmodulus prescalers. The optimization of the D flip-flop in the synchronous stage is essential to increase the operating frequency and reduce the power consumption. The high speed operation of MOS transistors is limited by their low transconductance. Therefore, dynamic and sequential circuit techniques or clocked logic gates such as, true single phase clocks must be used in designing synchronous circuits to reduce circuit complexity, increase operating speed and reduce power dissipation. The state of the art CMOS prescalers have achieved

maximum operating frequencies up to 2.4 GHz using current mode logic (CML) architectures at the expense of power consumption. The fastest frequency dividers were designed at fixed division ratios.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 18

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

The power consumption and frequency of operation of TSPC and E-TSPC 2/3 prescalers are analyzed and an ultra low power TSPC 2/3 prescaler is designed. Based on this design a 32/33 prescaler and 47/48 prescaler is then implemented, which is highly suitable for high resolution fully programmable frequency synthesizers.

Fig. 4.1 Topology of the Pulse Swallow frequency divider

4.1.1 Theory of operation

Prescaler divides the input frequency by control. Program counter divides the prescaler output by Swallow counter divides the prescaler output by Start from reset, prescaler divides by After (fixed). (fixed). or based on the modulus

until swallow counter is full. .

pulses at the input, the modulus control changes to

Continues to count until program counter is full. Total pulses at the input =

4.2

Synchronous 2/3 prescaler

An DMP (dual modulus prescaler) consists of a synchronous prescaler

followed by a series of asynchronous divide-by-2 circuits and additional logic gates to control the switching between the two different division ratios. Fig. 4.2 shows the evolution of a simple 2/3 synchronous prescaler from divide-by-2 and divide-by-3 circuits.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 19

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

When control logic signal MC goes high, the output of OR gate is always equal to logic 1 and the output of AND gate is always equal to the inverted output of DFF2 (Q2) such that the prescaler operates in the divide-by-2 mode as shown in Fig. 4.2 (a)

Fig. 4.2 a) Divide-by-2 circuit b) Divide-by-3 circuit c) Divide-by- 2 or 3 circuit When control logic signal MC goes low, the output of OR gate is always equal to Q1, such that prescaler operates in the divide-by-3 mode as shown in Fig. 3.1 (b). The output of the synchronous 2/3 prescaler is given by

(4.1)

Frequency dividers designed based on digital counters cannot be implemented by standard digital circuits. These digital counters cannot be synthesized directly using register transfer level (RTL) description which relies on standard cells as high frequency of operation requires accurate design and optimization. The main building block of the frequency dividers is D type edge-triggered flip-flop which are constructed using level triggered latches. The most commonly used logic circuits for high frequency dividers is either source-coupled logic (SCL) or current-mode logic (CML) circuits. Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 20

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.2.1 Current-mode logic (CML) dividers

The CML circuit is based on the use of differential stages with current steering topology. A divide-by-2 circuit implemented using the CML logic type is shown in Fig. 4.3 along with its equivalent transistor level schematic. A CML latch consists of NMOS differential pair transistors (Mn4, Mn5) and a regenerative pair (Mn1, Mn2). The loads are PMOS transistors (Mp1, Mp2) which are always operated in the triode region. When CLK is high, Mn6 turns-on and the differential pair transistors compare the input amplitudes at gate terminals and pass the result to the output nodes. When CLK is low, Mn3 turns-on and the regenerative pair transistors hold the output. The maximum operating frequency is decided by the differential pair transistors since they decide how fast the input amplitudes are sensed and transferred to the output nodes. The CML dividers have higher speed of operation and higher power consumption compared to that of the dynamic logic dividers.

Fig. 4.3 CML divide-by-2 and gate level schematic of CML latch One of the main advantages of CML logic circuits over dynamic logic circuits is the use of the differential topology, which makes the current drained by the supply less variable. Moreover, differential circuits reject disturbances coming from the substrate and power supply due to other blocks. The current steering topology as shown in Fig. 4.3 helps in lowering the voltage head Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 21

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

room. However, the current of the clock transistors are not controllable which results in larger power consumption. The CML logic circuit is very sensitive to the input amplitude and also requires buffers or level shifters at the output to drive the low frequency dynamic logic counters. Since the main interest lies in the design of low power synthesizer operating below 5 GHz, dynamic logic dividers are preferred over CML logic dividers.

4.2.2 Dynamic logic dividers

The CMOS latches eliminate the static current consumption and use fewer transistors than the CML latches do. They are slow due to the positive feedback (memory element) which introduces additional delay to the switching time. The switching speed of the static circuits depends on two factors namely, the current conduction level through a MOS transistor and parasitic capacitances. Since the parasitic capacitances cannot be controlled, the switching speed is only improved by the use of new and improved process. Alternatively, the memory element formed by a positive feedback can be replaced by a charge storing capacitance, which is called as dynamic memory. The dynamic logic circuit, instead of fighting the time constant limits induced by the RC parasitics, accepts the presence of capacitances and uses them as integral parts of the circuit.

Fig. 4.4 Clocked-CMOS (C2MOS) logic latch When CLK=1, both M3 and M2 are active IN=0 (1), the node S1 charges to 1 (0). When CLK=0, the first stage goes into high-impedance state and the second stage accepts the data at node S1 and passes it to the output node. Hence the output data is same as the input data. However, the output voltage can only be maintained so long as the voltage across node S1 Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 22

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler remains within an appropriate range. Fig. 4.4 shows a clocked-CMOS (C2MOS) logic latch. The main drawback of this topology is the requirement of complementary clock inputs for a single phase output. In an asynchronous chain, when a divide-by-2 is implemented, an additional inverter is need at the output to provide differential signals thus causing clock skew.

Fig. 4.5 Evolution of TSPC flip-flop from doubled p-C2MOS latch For this reason, domino logic circuits also a part of the dynamic logic circuit family. The original domino logic circuit requires a dual-phase clock, but a single-phase clock is developed using doubled p-C2MOS latch as shown in Fig. 4.5 which avoids the need of the dual-phase clock and clock skew problems. This architecture has higher speed and higher input sensitivity. The TSPC flip-flop has two modes of operation namely; hold mode and evaluation mode as shown in Fig. 4.6. In the hold mode (pre-charge phase), CLK=0and node S1 is precharged to a value depending on the input signal IN and node S2 is pre-charged to VDD. As transistors M7 and M8 is turned-off, output node OUT becomes floating. In the evaluation mode, CLK=1 and if the node S1 is pre-charged to VDD in the hold mode, node S2 is discharged and output node is pulled up by the transistor M7. If the node S1 is pre-charged to Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 23

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

0 during the hold mode, node S2 is not discharged, and output node is pulled down by the transistors M8 and M9 respectively.

Fig. 4.6 Operation of TSPC flip-flop a) hold mode b) evaluation mode A further modification of the TSPC circuit, which increases the achievable speed by a reduction of the stacked transistors, is the extended TSPC (E-TSPC) logic circuit. The E-TSPC circuit has static current, noise immunity problem which requires additional care in the design. The TSPC and E-TSPC are most suitable in the design of low power dividers for frequencies below 6 GHz applications. However, the choice between TSPC and E-TSPC circuits is very critical since the TSPC circuit has lower power consumption but operates at a lower frequency compared to that of the E-TSPC logic circuit.

4.2.3 Propagation speed analysis of TSPC and E-TSPC flip-flops

In this section, the maximum operating frequency of the TSPC and E-TSPC flip-flops are analyzed. In each stage, an E-TSPC flip-flop uses only two transistors while a TSPC flipflop uses three transistors. Of various dynamic logic CMOS circuits, TSPC and E-TSPC circuits operate with the single-phase clock to avoid clock skew problems. To compare the speed performance of TSPC and E-TSPC circuits, the first stage of both TSPC and E-TSPC circuits with their equivalent RC models are analyzed as shown in Fig. 4.7.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 24

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

(a) TSPC

(b) E-TSPC

Fig. 4.7 First stage and equivalent RC model of (a) TSPC (b) E-TSPC flip-flops

The charging and discharging time constants of the first stage of the TSPC flip-flop are manually calculated using the RC ladder method, as follows

(4.2) 2 2

1 3 : 2

(4.3) (4.4) (4.5)

: is

the total depletion capacitance between the series PMOS transistors and

is the fan-out

capacitance. The propagation delay of the first stage TSPC flip-flopis

0.69 1 : 1 2

(4.6)

The charging and discharging time constants of the first stage E-TSPC flip-flop are given by

2 2

3 1

(4.7) (4.8)

The propagation delay of the first stage TSPC flip-flop is given by

0.69 2 : 2 2

(4.9)

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 25

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

The output load capacitance of E-TSPC stage is lower than that of TSPC due to the reduced fan-out. The charging time constant of E-TSPC is smaller than TSPC from (4.4) and (4.8), the propagation delay of TSPC stage is higher than that of the E-TSPC stage and thus it proves TSPC flip-flop has a lower operating frequency compared to that of the E-TSPC flip flop. If speed is the critical parameter in the design, E-TSPC logic circuits are chosen over other dynamic logic circuits. However, it suffers from static power dissipation which is discussed in the next section.

4.2.4 Power consumption analysis of TSPC and E-TSPC flip-flops

In digital circuits, the power consumption is divided in to three parts namely; switching power, short-circuit power and leakage power. The total power consumption of a digital circuit is given by

01

(4.10)

The first term represents the switching power consumption, where CL is the load capacitance; fclk is the clock frequency and 10 is the node transition activity factor, the average number of transitions in one clock period. The second term is due to conduction of current directly from the supply to ground when PMOS and NMOS are active simultaneously. The third term is due to the leakage current, which arises from the substrate injection and subthreshold effects. Circuit diagram, waveform, schematic and layout of TSPC and E-TSPC flipflop are as shown in Fig. 4.8 and Fig. 4.9 respectively. The load capacitance at each output node of TSPC flip-flop in divide-by-2 mode is given by

1 2 3

3 4 7

2 2 2

3 4 7

2 5 8

2 2 2

2 5 8

5 7 1 9 3

(4.11) (4.12) (4.13)

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 26

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

(a) TSPC

(b) E-TSPC

Fig. 4.8 (a) Divide-by-2 circuit (a) TSPC (b) E-TSPC

Fig. 4.8 (b) Waveform of TSPC flip-flop Table.4.1 Delay and power consumption of TSPC flip-flop Parameters Operating voltage (V) Max. operating freq.(MHz) Output frequency (MHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (uW) With parasitics 1.8 2.5 1.25 37 88 62.5 64.71 Without parasitic 1.8 2.5 1.25 27 73 50 45.93

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 27

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.8 (c) Schematic diagram of TSPC flip-flop

Fig. 4.8 (d) Layout of TSPC flip-flop

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 28

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.2 Circuit inventory of TSPC flip-flop LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor Nmos Pmos VIEW symbol symbol ivpcell ivpcell TOTAL 142 47 5 4

Fig. 4.9 (a) Schematic of E-TSPC flip-flop

Fig. 4.9 (b) Waveform of E-TSPC flip-flop Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 29

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.3 Delay and power consumption of E-TSPC flip-flop Parameters Operating voltage (V) Max. operating freq.(MHz) Output frequency (MHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 1.25 50 20 35 1.175 Without parasitics 1.8 2.5 1.25 40 15 27.5 1.173

Fig. 4.9 (c) Layout of E-TSPC flip-flop

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 30

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.4 Circuit inventory of E-TSPC flip-flop LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor Nmos Pmos VIEW symbol symbol ivpcell ivpcell TOTAL 121 37 3 3

The load capacitance at each output node of E-TSPC flip-flop in divide-by-2mode is given by

1 2 3 1 4 5

2 2 2

1 4 5

2 3 6

2 2 2

2 3 6

3 6 1

(4.14) (4.15) (4.16)

From the above equations it is clear that the capacitance at the each output node of the TSPC circuit is higher than that of the E-TSPC circuit. Since the switching power is linearly related to the load capacitance, TSPC circuits cause more switching power than E TSPC circuits. However, the switching power can be reduced by optimization techniques such as reducing the number of switching stages and the width of the transistors. In TSPC circuits, one of the transistors in each stage is always off, hence there is no short-circuit power consumption. The TSPC short-circuit power is smaller than the E-TSPC short circuit power. The timing diagram of Fig. 4.10 illustrates the operation of a divide-by-2 ETSPC circuit. The shaded part shows the duration where the short-circuit current exists in the ETSPC divide by-2 circuit. To analyze E-TSPC short-circuit, a single stage of an E-TSPC circuit is simulated with PMOS and NMOS transistors active and the PMOS transistor width is increased for a constant NMOS transistor width in 0.18um technology.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 31

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.10 Divide-by-2 operation of an E-TSPC circuit The short circuit power consumption for different ratios of PMOS to NMOS transistor widths is plotted in Fig. 4.11 for the values which are tabulated in Table.5. As the PMOS to NMOS width ratio increases, both the short-circuit power and the output voltage increases. As a result power consumption also increases since it is directly proportional to input voltage.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 32

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.5 Short circuit power in a single stage E-TSPC NMOS width (um) 1 PMOS width (um) 1 2 3 4 5 2 2 4 6 8 10 3 3 6 9 12 15 1.8 1.8 Amplitude (V) 1.8 Current (mA) 0.234 0.448 0.587 0.605 0.610 0.459 0.854 1.132 1.160 1.170 0.684 1.321 1.678 1.724 1.753 Power consumption (mW) 0.421 0.807 1.057 1.089 1.090 0.827 1.538 2.037 2.088 2.106 1.232 2.370 3.020 3.103 3.155

Even though the propagation delay of E-TSPC logic is lower than that of TSPC logic, its large short-circuit power and considerable amount of switching power makes the E-TSPC logic less suitable of low power applications compared to TSPC below 5GHz operation. Power consumption of TSPC and E-TSPC flip flop is shown in Fig. 4.12. Based on this analysis, TSPC logic is chosen for the design of low power divider.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 33

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Short circuit power in a single stage of E-TSPC circuit

power consumption (mW) 3.5 3 2.5 2 1.5 1 0.5 0 1 2 3 4 5 Ratio of PMOS to NMOS width

width of NMOS= 1um width of NMOS= 2um

width of NMOS= 3um

Fig. 4.11 Short circuit power in a single stage of E-TSPC circuit

Power consumption of TSPC and E-TSPC flip-flop (mW)

1.4 1.175 1.2

1

0.8 0.6 0.4 0.2 0 TSPC E-TSPC 0.0647

Fig. 4.12 Power consumption of TSPC and E-TSPC flip-flop

4.2.5 E-TSPC based 2/3 prescaler

The control logic signal MC changes the operation between divide-by-2 and divide-by-3 modes. If MC =1, the 2/3 prescaler operates in the divide-by-3 mode where the two DFFs actively participate in the operation. If MC =0, the 2/3 prescaler operates in the divide-by-2 mode, where PMOS transistor M2 is always turned-on suppressing the switching activities in DFF1 such that the nodes S1, S2 and S3 remain at logic 1, 0 and 1 respectively. Thus the switching power is saved in DFF1 during the divide-by-2 operation. However, there always

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 34

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

exists very high short-circuit power in the first stage of the DFF1 and improper device sizing can still result in switching activities in the DFF1 during the divide-by-2 operation.

Circuit diagram, waveform, schematic and layout of E-TSPC divide-by-2 and divide-by-3 are as shown in Fig. 4.13 and Fig. 4.14 respectively.

Fig. 4.13 (a) E-TSPC 2/3 prescaler

Fig. 4.13 (b) Schematic diagram of E-TSPC divide-by-2 prescaler

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 35

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.13 (c) Waveform of E-TSPC divide-by-2 prescaler Table.4.6 Delay and power consumption of E-TSPC divide-by-2 prescaler Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 1.25 31 72 51.5 2.722 Without parasitic 1.8 2.5 1.25 27 60 43.5 2.655

Fig. 4.13 (d) Layout of E-TSPC divide-by-2 prescaler Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 36

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.7 Circuit inventory of E-TSPC 2/3 prescaler in divide-by-2 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 344 110 7 9

Fig. 4.14 (a) Schematic diagram of E-TSPC divide-by-3 prescaler

Fig. 4.14 (b) Waveforms of E-TSPC divide-by-3 prescaler

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 37

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.8 Delay and power consumption of E-TSPC divide-by-3 prescaler Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (uW) With parasitics 1.8 2.5 0.833 32 78 55 2.569 Without parasitics 1.8 2.5 0.833 28 66 47 2.541

Fig. 4.14 (c) Layout of E-TSPC divide-by-3 prescaler

Table.4.9 Circuit inventory of E-TSPC 2/3 prescaler in divide-by-3 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 346 110 7 9

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 38

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.3 Conventional synchronous TSPC 2/3 prescaler

The conventional TSPC 2/3 prescaler consists of two D flip-flops, an OR gate and an AND gate. Due to the large load on DFF2 and difficulty to embed the OR and AND gates into the DFF which introduces additional delay limits the speed of conventional 2/3 prescaler and also causes substantial power dissipation. Circuit diagram, schematic, waveform and layout of Conventional TSPC divide-by-2 and divide-by-3 prescaler are as shown in Fig. 4.15 and Fig. 4.16 respectively. The total load capacitance at the output node Qb of the conventional 2/3 prescaler is given by

30 19 31 20

2(

30

31 )

(4.17)

Fig. 4.15 (a) Conventional TSPC 2/3 prescaler and its equivalent gate level schematic Addition of an OR gate and an AND gate in the critical path introduces the additional delay and limits the maximum operating speed of the circuit. The propagation delay of the TSPC 2/3 prescaler is equal to the sum of propagation delay of DFF1, DFF2and logic gates, where the propagation delay of each DFF is equal to the sum of delay of the each stage.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 39

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

The total propagation delay is given by

_1

_2

(4.18)

The propagation delay equations shows that the maximum operating frequency of the conventional 2/3 prescaler is limited due to the logic OR and logic AND gates. The conventional TSPC 2/3 prescaler has 12 stages and each stage has a switching output node. The switching power with 12 switching nodes is given by

12 <1

(4.19)

Where

is the capacitance of the each output node of DFF1, DFF2 and logic gates. The short

circuit power of the conventional 2/3 prescaler is almost negligible and power consumption is mainly due to the switching power due to large capacitance at the output of each stage.

One of the main advantages of domino logic is that the logic gates can be embedded into the flip-flop, which can reduce the additional propagation delay.

4.3.1 Divide-by-2 operation

Fig. 4.15 (b) Schematic of conventional TSPC 2/3 prescaler

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 40

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.15 (c) Waveforms of Conventional TSPC 2/3 prescaler in Divide by-2 mode Table.4.10 Delay and power consumption of Conventional TSPC 2/3 in Divide by-2 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 1.25 41 58 49.5 1.421 Without parasitic 1.8 2.5 1.25 30 34 32 0.978

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 41

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.15 (d) Layout of Conventional TSPC 2/3 prescaler in Divide by-2 mode Table.4.11 Circuit inventory of Conventional TSPC 2/3 prescaler in divide-by-2 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 626 216 18 16

4.3.2 Divide-by-3 operation

Fig. 4.16 (a) Schematic of Conventional TSPC 2/3 prescaler in Divide by-3 mode

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 42

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.16 (b) Waveforms of Conventional TSPC 2/3 prescaler in Divide by-3 mode Table.4.12 Delay and power consumption of Conventional TSPC in Divide-by-3 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 0.833 45 66 55.5 1.433 Without parasitics 1.8 2.5 0.833 30 35 32.5 1.138

Fig. 4.16 (c) Layout of Conventional TSPC 2/3 prescaler in Divide by-3 mode Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 43

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.13 Circuit inventory of Conventional TSPC 2/3 prescaler in divide-by-3 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 615 218 18 16

4.4 TSPC 2/3 Prescaler: Design-I

The conventional TSPC 2/3 prescaler consumes large power and has low operating frequency due to its large load capacitance. An improved speed and low power 2/3 prescaler consists of two D flip-flops and two NOR gates embedded into the flip-flops as shown in Fig. 4.17. Circuit diagram, schematic, waveform and layout of Design-I divide-by-2 and divide-by-3 prescaler are as shown in Fig. 4.18 and Fig. 4.29 respectively.

Fig. 4.17 Design-I TSPC 2/3 prescaler circuit and equivalent gate level schematic

The first NOR gate is embedded into the third stage of DFF1 using a single NMOS transistor M10, whose drain is connected to node S3 of DFF1 and the other NOR gate is embedded into the first stage of DFF2. By doing so, an extra inverter driven by node S3 of Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 44

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

DFF1 and additional stages introduced by the logic gates between DFF1 and DFF2 of the conventional TSPC 2/3 prescaler is eliminated, reducing the number of switching nodes to 7 in the proposed prescaler. The load capacitance of the proposed 2/3 prescaler is given by

_;

19

20

2(

19

20 )

15

11 (4.20)

4.4.1 Divide-by-2 operation

When MC=1, transistor M10 turns-on and node S3 switches to logic 0 irrespective of the data at node S2. The second NOR gate output is always equal to the inverted output of DFF2 as shown in Fig. 4.19 (a), which is equivalent to simple DFF with its complimentary output connected to the input as shown in Fig. 4.7 (a). Thus the prescaler act as divide-by-2 when MC=1. Here, even though the output of DFF2 is connected in feedback to the input of DFF1, the switching data at node S1 and S2 is blocked by the transistor M10 to reach to the node S3. Thus the switching power at the node S3 is always zero.

Fig. 4.18 (a) Divide-by-2 operation of 2/3 prescaler unit

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 45

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.18 (c) Schematic of Design-I 2/3 prescaler in Divide-by-2 mode

Fig. 4.18 (b) Waveform of Design-I 2/3 prescaler in divide-by-2 mode Table.4.14 Delay and power consumption of Design-I 2/3 prescaler in divide-by-2 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 4.5 2.25 49 69 59 1.412 Without parasitics 1.8 4.5 2.25 48 69 58.5 1.213

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 46

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.18 (d) layout of Design-I 2/3 prescaler in Divide-by-2 mode Table.4.15 Circuit inventory of Design-I 2/3 prescaler in divide-by-2 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 426 142 14 9

However, there exists switching power in the first two stages of the DFF at nodes S1 and S2 due to the feedback action of the DFF2 output which switches continuously. The total power of the prescaler in divide-by-2 mode of operation is equal to the sum of switching power of DFF2 and the switching power of first two stages of DFF1which is less than the conventional 2/3 prescaler.

4.4.2 Divide-by-3 operation

When MC=0, transistor M10 turns-off and the inverted data at node S2 is passed to the node S3. The second NOR gate output is always equal to the inverted output of DFF2. Fig. 4.20 shows the circuit of the proposed 2/3 prescaler unit in divide-by-3 mode of operation. The combination of inverter and NOR gate is equivalent to logic AND gate with the other input Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 47

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

inverted as shown in Fig. 4.20. Thus the prescaler act as divide-by-3 when MC=0. There is continuous switching activity at each node and the switching power is given by the sum of switching power of both the DFF1 and DFF2 respectively.

Fig. 4.19 (a) Divide-by-3 operation of the Design-I 2/3 prescaler

Fig. 4.19 (b) Schematic of Design-I 2/3 prescaler in Divide-by-3 mode

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 48

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.19 (c) Waveforms of Design-I 2/3 prescaler in Divide-by-3 mode Table.4.16 Delay and power consumption of Design-I 2/3 prescaler in divide-by-3 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 4.5 1.5 34 45 39.5 1.341 Without parasitics 1.8 4.5 1.5 28 32 30 0.8951

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 49

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.19 (d) Layout of Divide-by-3 operation of Design-I 2/3 prescaler Table.4.17 Circuit inventory of Design-I 2/3 prescaler in divide-by-3 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 441 145 14 9

4.4.3 Propagation delay of TSPC 2/3 prescaler: Design-I

The propagation delay of the proposed 2/3 prescaler is calculated using the RC delay model method which is used to calculate the propagation delay of the conventional2/3 prescaler as discussed in section 4.2. However, in divide-by-2 mode of operation, since the node S3 always remains at logic 0 and blocks the data from DFF1 to propagate to the DFF2. The total propagation delay of the proposed 2/3 prescaler individe-by-2 mode of operation is equal to the propagation delay of DFF2 which is given by

_2

(4.21)

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 50

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

The propagation delay of the remaining stages of the DFF2 is similar to the propagation delay of the DFF2 in conventional 2/3 prescaler. In divide-by-3 mode of operation, since both DFF1 and DFF2 are active, the propagation delay is equal to the sum of propagation delay of embedded NOR gate DFF1 and DFF2 respectively, which is given by

;;3

_1

_2

(4.22)

Since the NOR gates are embedded in to the flip-flop, the propagation delay of entire 2/3 prescaler is reduced by delay equal to 7 stages as proved by the RC delay model. Since the number of stages in the proposed Design-I prescaler is reduced to 7, the switching power is given by

;;

7 <1

(4.23)

Where

is the load capacitance at each output node of DFF1 and DFF2. The reduction of the

switching power in the proposed design compared to that of the conventional 2/3 prescaler when both circuits are designed with same transistor sizes is given by

_

12 <1

7 <1

(4.24)

In this analysis, both the conventional 2/3 prescaler and Design-I prescaler are designed using same width of 3 um for PMOS and 1.7 um for NMOS transistors. The node capacitances at each output node for both circuits are assumed to be same, since all the devices has same aspect ratio. The Design-I prescaler reduces the area since it uses only 23 transistors to perform divide-by-2 and divide-by-3 compared to the conventional 2/3 which uses as many as 32 transistors. The output Q drives transistors M11 and M14 of DFF2 and Qb drives transistors M1 and M3 such that loading on Q is reduced compared to conventional prescaler. The simulation results show that the conventional TSPC 2/3 prescaler can operate up to maximum frequency of 2.5 GHz. The Design-I 2/3 prescaler has maximum operating frequency of 4.5 GHz. The simulation results indicate that the Design-I prescaler saves nearly % power in divide-by-3 mode and nearly 19% power in divide-by-2 mode compared to conventional 2/3 prescaler respectively.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 51

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.4.4 Short-circuit power of the Design-I 2/3 prescaler

The short-circuit power in TSPC is almost negligible since one of the transistors in each stage is always off. However, this is not true when a logic gate is embedded in to the TSPC logic. During the divide-by-2 mode when control logic signal MC =1, the transistor M10 turnson as shown in Fig. 4.17 and Fig. 4.19 (a) allowing a direct path from supply to ground when transistor M7 turns-on. This direct path results in the high short circuit power in the third stage of DFF1. In the Fig. 4.20, it is shown that node S2 goes low for half of the input clock period during which M7 turns-on, creating a direct path from supply to ground since M10 is always turned-on during thedivide-by-2 operation. The shadow lines indicate the period during which short circuit power is exhibited in the 3rd stage of DFF1.

Fig. 4.20 Short circuit power analysis However in divide-by-2 mode, the power consumption of the prescaler is given by the sum of switching power in DFF1 and DFF2, short circuit power in 3rd stage ofDFF1 and short circuit power in DFF2. Since short circuit power is very small in TSPC circuits.

The power consumption in divide-by-2 mode is given by

2 3_;

_1_; _3_1_;

_2_;

(4.25)

Page 52

Dept of Electronics & Communication, SIT Tumkur 2012-13

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Where,

_1_;

3 <1 4 <1

(4.26)

_2_;

(4.27)

Based on the short-circuit power analysis of single stage discussed in the section 4.2.4, a simple simulation is done to analyze the power consumption of DFF1 and DFF2. The simulation results indicate that the Design-I prescaler saves nearly 65% power in divide-by-3 mode and nearly 54% power in divide-by-2 mode compared to E-TSPC 2/3 prescaler respectively. In order to overcome the short circuit power problem in 3rd stage of DFF1, an improved 2/3 prescaler is designed which is called as Design-II 2/3 prescaler.

4.5

TSPC 2/3 Prescaler: Design-II

A further improved version of Design-I prescaler is as shown in the Fig. 4.21. In the

Design-II prescaler, an extra PMOS transistor M1a is connected between the power supply and DFF1 whose input is the controlled by the logic signal MC. As discussed in the section 4.2, during the divide-by-2 operation, one of the inputs of second NOR gate is always zero since transistor M10 blocks the data at the input of DFF1 to propagate to the output node. Here, DFF1 is not actively participating in the divide-by-2 operation however; it contributes to the power consumption due to the continuous switching at the nodes S1and S2 respectively. Circuit diagram, schematic, waveform and layout of Design-II divide-by-2 and divide-by-3 prescaler are as shown in Fig. 4.22 and Fig. 4.23 respectively.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 53

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.21 Design-I TSPC 2/3 prescaler circuit

4.5.1 Divide-by-2 operation

In this new design, when the control logic signal MC=1 during the divide-by-2 mode, the PMOS transistor M1a is turned-off and DFF1 is disconnected from the power supply. Fig. 4.23 shows the simplified schematic of the Design-II prescaler in the divide-by-2 mode of operation. Even though M10 is always turned-on, the source of M7 is at virtual ground and shortcircuit power is completely avoided. Even if the output Qb switches continuously, the nodes S1, S2 and S3 always remain at logic0 and thus the switching activities are blocked in DFF1 resulting in zero switching power.

Fig. 4.22 (a) Design-II TSPC 2/3 prescaler: divide-by-2 operation The total power consumption of the Design-II prescaler is equal to the switching power of DFF2 which is given by Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 54

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

2 3_

_2_

(4.28)

_2_

4 <1

(4.29)

Fig. 4.22 (b) Schematic of Design-II 2/3 prescaler in Divide-by-2 mode

Fig. 4.22 (c) Waveforms of Design-II 2/3 prescaler in Divide-by-2 mode

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 55

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.18 Delay and power consumption of Design-II 2/3 prescaler in divide-by-2 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 4.5 2.25 34 45 39.5 1.039 Without parasitics 1.8 4.5 2.25 26 29 27.5 0.631

Fig. 4.22 (d) Layout of Design-II 2/3 prescaler in Divide-by-2 mode Table.4.19 Circuit inventory of Design-II 2/3 prescaler in divide-by-2 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 418 119 14 9

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 56

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.5.2 Divide-by-3 operation

Fig. 4.23 (a) Schematic of Design-II 2/3 prescaler in Divide-by-3 mode

Fig. 4.23 (b) Waveforms of Design-II 2/3 prescaler in Divide-by-3 mode

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 57

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.20 Delay and power consumption of Design-II 2/3 prescaler in divide-by-3 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 4.5 0.833 34 45 39.5 1.338 Without parasitic 1.8 4.5 0.833 26 29 27.5 0.893

Fig. 4.23 (c) Layout of Design-II 2/3 prescaler in Divide-by-3 mode Table.4.21 Circuit inventory of Design-II 2/3 prescaler in divide-by-3 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 409 119 14 9

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 58

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.5.3 Power saving analysis in Divide-by-2 operation

The percentage of power saved by the Design-II prescaler in the divide-by-2 mode is ratio of the difference in power consumed by Design-I and Design-II prescalers to the power consumed by Design-I prescaler given by

2 3_ ;2 3_ 2 3_

2 3_%

00

(4.30)

Since both circuits use same flip-flop DFF2, which consumes the same power in both the circuits during divide-by-2 and divide-by-3 modes, the power saved by the Design-II prescaler is given by subtracting (4.25) from (4.28).

2 3_;

2 3_; ;3;1_;

;1_;

(4.31)

The flip-flops DFF1, DFF2 of Design-I prescaler are simulated with separate power supply to find out the approximate relation between the power consumption of both D flip-flops during the divide-by-2 operation. From the theoretical analysis it is found that the power consumed by the DFF1 during divide-by-2 operation is almost twice of the power consumed by DFF2. This assumption makes (4.31) simplified and the power consumed in thedivide-by-2 mode is rewritten as

;1_; ;3;1_; ;2_;

;2_;

(4.32)

Thus substituting (4.32) and (4.33) in (4.30), the amount of power saved by the Design-II 2/3 prescaler is 76% in divide-by-2 mode and 65% in divide-by-3 mode compared to E-TSPC 2/3 prescaler. Thus the power consumed in the divide-by-2 mode by the Design-I prescaler is rewritten as

2 3_;

;2_;

;2_;

(4.33)

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 59

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

4.6 Analysis of TSPC 32/33 (N/N+1) Prescaler

To verify the advantages of the proposed ultra-low power prescaler of Design-II, a divide 32/33 dual modulus unit is implemented with the 2/3 prescaler of Design-II as shown in Fig. 4.24. In this 32/33 prescaler, the proposed 2/3 prescaler unit is followed by four stages of the toggled TSPC divide-by-2 units. Schematic, waveform and layout of TSPC 32/33 prescaler are as shown in Fig. 4.25 and Fig. 4.26 respectively.

Fig. 4.24 TSPC 32/33 prescaler using Design-II 2/3 prescaler

4.6.1 Divide-by-32 operation

When the control signal MOD is 1, the output of NOR2 always remains at logic 0 and forces the output of NAND2 to logic 1 irrespective of data on Qb1. Since MC is always equal to logic 1, the Design-II prescaler remains in divide-by-2. Thus the 32/33 prescaler acts as divide-by-32 circuit. Since control logic signal MC is logically high, DFF1 in the Design-II 2/3 prescaler is completely turned-off for the entire 32 input clock cycles. The 32/33 prescaler consists of both the synchronous (Design-II prescaler) and asynchronous (toggle divide-by-2) circuits and thus the power and speed is traded-off as discussed in the design of digital counters earlier.

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 60

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.25 (a) Schematic of TSPC 32/33 prescaler in divide-by-32 mode

Fig. 4.25 (b) Waveforms of TSPC 32/33 prescaler in Divide-by-32 mode Table.4.22 Delay and power consumption of TSPC 32/33 prescaler in Divide-by-32 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (uW) With parasitics 1.8 2.5 0.078 160 110 135 733.1 Without parasitic 1.8 2.5 0.078 170 120 145 733.1

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 61

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.25 (c) Layout of TSPC 32/33 prescaler in Divide-by-32 mode Table.4.23 Circuit inventory of TSPC 32/33 prescaler in divide-by-32 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor Nmos Pmos VIEW symbol symbol ivpcell ivpcell TOTAL 409 119 14 9 and the four asynchronous

If we denote the synchronous 2/3 prescaler as

dividers whose division ratio equal to 16 by AD, the division ratio in this mode (MOD=1) is given by

32

(4.34)

The total power consumed by the 32/33 prescaler using Design-I 2/3 prescaler during divide-by-32 is equal to the sum of switching and short circuit power of the DFF1, DFF2 over 32 clock cycles, power consumed by four asynchronous divide-by-2 circuits, and the power consumed by the logic gates.

32_1 _2 _1 _3_1 __16

(4.35)

Page 62

Dept of Electronics & Communication, SIT Tumkur 2012-13

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

The power consumed by the four asynchronous divide-by-2 circuits is given by

41 2 1

2

__16

4 ;1

(4.36)

Here,

is the frequency of the output signal from the 2/3 prescaler which can be half or one-

third of the input clock signal and is the total short-circuit current of the each asynchronous divide-by-2 circuit. Each of the asynchronous divider toggles at half the operating frequency of the preceding divide-by-2 circuit. Similarly, the power consumed by the 32/33 prescaler during the divide-by-32 operation using the Design-II prescaler is equal to the sum of switching and short circuit power of DFF2 over 32 clock cycles (DFF1 turned-off) and the power consumed by the 4 asynchronous dividers and logic gates. The power saved by the 32/33 prescaler during divide-by-32 mode using Design-II prescaler is equal to the amount of power consumed by DFF1 of the Design-I prescaler. Here, the power consumed by DFF1 always refers to the Design-I prescaler since power consumed by DFF1 of Design-II prescaler is always zero.

32_ _1 _3_1

(4.37)

4.6.2 Divide-by-33 operation

The dual-modulus 32/33 prescaler operates as divide-by-33 when MOD=0. By using the combination of logic NOR and NAND gates, the asynchronous divide-by-16 counter is made to count an extra input clock. The control signal MC is given by

(4.38)

Fig. 4.26 (a) Schematic of TSPC 32/33 prescaler in Divide-by-33 mode Dept of Electronics & Communication, SIT Tumkur 2012-13 Page 63

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.26 (b) Waveforms of TSPC 32/33 prescaler in Divide-by-33 mode Table.4.24 Delay and power consumption of TSPC 32/33 prescaler in Divide-by-33 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 0.075 150 130 140 1.046 Without parasitics 1.8 2.5 0.075 140 110 125 0.894

Table.4.25 Circuit inventory of TSPC 32/33 prescaler in divide-by-33 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 1536 455 46 37

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 64

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.26 (c) Layout of TSPC 32/33 prescaler in Divide-by-33 mode In the initial state, the Design-II 2/3 prescaler will be in divide-by-2 mode (MC=1) and the asynchronous divide-by-16 starts counting the output pulses of 2/3 prescaler from 0000 to 1111. When the asynchronous counter value reaches 1110, the logic signal MC goes low (MC=0) and the Design-II 2/3 prescaler operates in divide-by-3 mode, where the asynchronous counter counts an extra input clock pulse. During this operation, the 2/3 prescaler operates in divide-by-2 mode for 30 input clock cycles and for the remaining 3 input clock cycles; it operates in divide-by-3 mode. The division of the 32/33 prescaler in this mode is given by

33

(4.39)

where AD=16, MOD=0 and M=2. The total power consumed by the 32/33 prescaler using Design-I prescaler during the divide-by-33 operation is equal to the sum of switching power of the flip-flops DFF1, DFF2, short circuit power in the 3rd stage of DFF1 over 30 clock cycles, power consumed by four asynchronous divide-by-2 circuits and the power consumed by the digital gates.

32_1 __16 30 33 _3_1 _2 _1

(4.40)

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 65

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Similarly, the power consumed by the 32/33 prescaler using Design-II prescaler during the divide-by-33 operation is equal to the sum of the switching, of DFF2; switching power of DFF1 over 3 clock cycles, power consumed by the 4 asynchronous dividers and digital logic gates.

32_1 3 33 _1 _2 __16

(4.41)

Since power consumed by DFF2, 4 asynchronous dividers and the logic gates are same in both cases, the total amount of power saved by the 32/33 prescaler during the divide-by-33 using Design-II prescaler is equal to 1.4 times the power consumed during divide-by-32.

4.7

Proposed TSPC 47/48 prescaler

The proposed 47/48 prescaler circuit as shown in Fig. 4.27 is similar to the 32/33 prescaler except for an additional inverter which is added between the output of the NAND2 gate and the control signal (MC) input of the 2/3 prescaler. The 47/48 prescaler consists of Design-II 2/3 prescaler, four asynchronous divide-by-2 circuits and additional logic gates to control the division ratio between 47 and 48. Schematic, waveform and layout of TSPC 47/48 prescaler are as shown in Fig. 4.28 and Fig. 4.30 respectively.

Fig. 4.27 TSPC 47/48 prescaler using Design-II 2/3 prescaler

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 66

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

When MC=0, the 2/3 prescaler of the 32/33 prescaler operates in divide-by-3 mode whereas the 2/3 prescaler in the proposed 47/48 prescaler operates in divide-by-2 mode. Thus the inverter swaps the operation modes of the 2/3 prescaler.

4.7.1 Divide-by-47 operation

The proposed 47/48 prescaler operates as divide-by-47 when MOD=0. By using the combination of logic NOR and NAND gates, the asynchronous divide-by-16 counter is made to count an extra input clock. In the initial state, the 2/3 prescaler will be in divide-by-3 mode (MC=1) and the asynchronous divide-by-16 starts counting the output pulses of 2/3 prescaler from 0000 to 1111. When the asynchronous counter value reaches 1110, the logic signal MC goes low (MC=0) and 2/3 prescaler operates in divide-by-2 mode, where the asynchronous counter counts an extra input clock pulse. During this operation, the 2/3 prescaler operates in the divide-by-3 mode for 45 input clock cycles and in the divide-2 mode for 2 input clock cycles. The division ratio of the 47/48 prescaler in this mode is given by

48

2 2

(4.42)

Fig. 4.28 (a) Schematic of TSPC 47/48 prescaler in Divide-by-47 mode

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 67

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.28 (b) Waveforms of TSPC 47/48 prescaler in Divide-by-47 mode Table.4.26 Delay and power consumption of TSPC 47/48 prescaler in Divide-by-47 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 0.053 240 140 190 1.141 Without parasitics 1.8 2.5 0.053 140 110 125 0.887

Table.4.27 Circuit inventory of TSPC 47/48 prescaler in divide-by-47 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor Nmos Pmos VIEW Symbol Symbol Ivpcell Ivpcell TOTAL 1566 469 47 38

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 68

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.28 (c) Layout of TSPC 47/48 prescaler in Divide-by-47 mode

4.7.2 Divide-by-48 operation

When the control signal MOD is 1, the output of NOR2 in Fig.4.28 always remains at logic 0 and forces the output of NAND2 to logic 1 irrespective of data on Qb1. Since MC is always equal to logic 1 ( =0), the 2/3 prescaler remains in divide-by-3 mode. The equivalent circuit of inverter and the 2/3 prescaler is equal to divide-by-3 counter as shown in Fig. 4.29. Thus the 47/48 prescaler operates in divide-by-48 mode when MOD=1. If we denote the synchronous 2/3 prescaler as (MOD=1) is given by and the four asynchronous dividers whose division ratio equal to 16 by AD, the division ratio of the 47/48 prescaler in this mode

48

0 2 0 2

(4.43)

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 69

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Fig. 4.29 Divide-by-48 mode of operation

Fig. 4.30 (a) Schematic of TSPC 47/48 prescaler in Divide-by-48 mode

Fig. 4.30 (b) Waveforms of TSPC 47/48 prescaler in Divide-by-48 mode

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 70

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Table.4.28 Delay and power consumption of TSPC 47/48 prescaler in Divide-by-48 mode Parameters Operating voltage (V) Max. operating freq.(GHz) Output frequency (GHz) tpHL(ps) tpLH (ps) tp (ps) Power consumption (mW) With parasitics 1.8 2.5 0.052 230 130 180 1.141 Without parasitics 1.8 2.5 0.052 140 110 125 0.877

Fig. 4.30 (c) Layout of TSPC 47/48 prescaler in Divide-by-48 mode Table.4.29 Circuit inventory of TSPC 47/48 prescaler in divide-by-48 mode LIBRARY analogLib analogLib gpdk180 gpdk180 CELL Pcapacitor Presistor nmos pmos VIEW symbol symbol ivpcell ivpcell TOTAL 1572 462 47 38

Dept of Electronics & Communication, SIT Tumkur 2012-13

Page 71

Analysis of Ultra Low Power True Single Phase Clock CMOS 2/3 Prescaler

Chapter 5 Ultra Low Power Fully Programmable Dividers

5.1 Introduction