Professional Documents

Culture Documents

Treesa s2

Treesa s2

Uploaded by

jayalakshmisnairOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Treesa s2

Treesa s2

Uploaded by

jayalakshmisnairCopyright:

Available Formats

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSII: EXPRESS BRIEFS, VOL. 59, NO.

3, MARCH 2012

173

Low-Voltage CMOS Differential Logic Style With Supply Voltage Approaching Device Threshold

Jong-Woo Kim, Joo-Seong Kim, and Bai-Sun Kong

AbstractThis brief describes a novel low-voltage CMOS differential logic operating with supply voltage approaching the MOS threshold voltage. The proposed logic style improves switching speed by boosting the gatesource voltage of transistors along timing-critical signal paths. The logic style also minimizes area overhead by allowing a single boosting circuit to be shared by complementary outputs. Test sets of logic gates were designed in a 0.18-m CMOS process, whose comparison results indicated that the energydelay product of the proposed logic style was improved by up to 86% compared with conventional logic styles at supply voltage ranging from 0.4 to 1.2 V. The experimental result for a 64-bit adder designed using the proposed logic style revealed an addition time of 4.8 ns at 0.5-V supply with 31 pJ at 100 MHz. Index TermsAdder, low power, low voltage, voltage boosting.

I. I NTRODUCTION

ROWING need for portable devices has provoked ever increasing concern on energy-efcient design. Since the energy consumption of modern digital CMOS circuits has been traditionally dominated by switching energy having quadratic dependence on supply voltage, voltage scaling is an effective way to minimize the overall energy consumption of system-ona-chip [1]. In the extreme case, circuits can be made to be operated in the subthreshold region for maximum energy efciency [2], [3]. However, the approach is limited to be only used in a low-end design, where speed is a secondary concern, because of severe speed degradation due to small switching current and high performance variability due to process, temperature, and threshold voltage variations [4]. For medium- and highend designs, where speed performance and energy efciency are both important, that much aggressive voltage scaling is not acceptable, and instead, a near-threshold voltage design is more suitable for achieving relatively high energy efciency without severe speed degradation. As the supply voltage scales down toward the threshold voltage, the speed performance of conventional CMOS circuits, such as static CMOS logic, differential cascode voltage switch (DCVS) logic [5] [see Fig. 1(a)], and domino CMOS logic [6]

Fig. 1. Conventional digital CMOS circuits. (a) DCVS. (b) Domino CMOS logic. (c) BDL.

Manuscript received July 15, 2011; revised October 28, 2011; accepted January 12, 2012. Date of publication February 20, 2012; date of current version March 16, 2012. This work was supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education, Science and Technology (2010-0013702). This paper was recommended by Associate Editor Y. Ha. The authors are with the School of Information and Communication Engineering, Sungkyunkwan University, Gyunggi, 440-746, Korea (e-mail: bskong@skku.edu). Color versions of one or more of the gures in this paper are available online at http://ieeexplore.ieee.org. Digital Object Identier 10.1109/TCSII.2012.2184380

[see Fig. 1(b)], is still severely degraded due to the reduced overdrive voltage (VGS VTH ) of transistors. To overcome this problem, a bootstrapped CMOS large capacitive-load driver [7] was proposed. It can improve the switching speed at low supply voltage by allowing the voltage of some internal nodes to be boosted beyond the supply rails. However, since the circuit was proposed for use as a large capacitive-load driver, logic functions cannot be efciently embedded into the circuit. For fast logic operation at low supply voltage, CMOS bootstrapped dynamic logic (BDL) [8] [see Fig. 1(c)] was proposed. However, the speed of this logic style was not so much improved since the latency of bulky bootstrapping circuit was superimposed on the overall latency of the circuit. Moreover, logic composition of this logic style is constrained since it is congured as a singleended structure. Although some recent circuit techniques adopting bootstrapped operation have been proposed, they are all not for logic composition but for large capacitance driving [9], [10]. To overcome the aforementioned problems and to further improve the switching performance, a novel boosting CMOS differential logic style is proposed in this brief. Section II describes the circuit structure and operation of the proposed logic style. In Section III, comparison results for some representative logic gates are presented to assess the performance of the proposed logic style. Section IV describes the experimental result for 64-bit adders as a design example to prove the practicality of the proposed logic style. Finally, we present the conclusion in Section V.

1549-7747/$31.00 2012 IEEE

174

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSII: EXPRESS BRIEFS, VOL. 59, NO. 3, MARCH 2012

Fig. 3. Boosting capacitance and boosted voltage of a two-input XOR/XNOR BCDL gate to provide a minimum EDP.

Fig. 2. Proposed BCDL. (a) Structure. (b) Simulated waveforms.

II. C IRCUIT S TRUCTURE AND O PERATION Fig. 2(a) shows a generic structure of the proposed logic style, i.e., boosted CMOS differential logic (BCDL). It consists of a precharged differential logic block and a voltage-boosting block. The voltage-boosting block, which is shown in the dotted box at the lower part of the circuit, is composed of transistors MN2, MN3, and MP3 and boosting capacitor CBOOT and is used to boost the voltage of NP below the ground. The precharged differential logic block, which is composed of a differential logic tree with bottom transistor MN1, precharge transistors MP1 and MP2, and output inverters, receives the boosted voltage at NP and swiftly evaluates the output logic values. Let us explain the operation of BCDL. It has two phases of operation, namely, a precharge phase and a boosted evaluation phase. The circuit is in the precharge phase when CLK is low. During this phase, the precharged differential logic block is separated from the voltage-boosting block since MN1 is fully off. Precharge nodes P and PB in the differential logic block are then precharged to the supply voltage by MP1 and MP2, letting outputs OUT and OUTB identically low. At the same time, transistors MP3 and MN2 in the voltage-boosting block turn on, allowing NS and NP to be high and low, respectively. Then, a voltage identical to the supply voltage is applied across CBOOT . When CLK changes to high, the circuit goes into the boosted evaluation phase. The simulated waveforms of BCDL in this phase are shown in Fig. 2(b), where a supply voltage of 0.5 V is used. Since CLK goes high, MN1 turns on and connects the differential logic tree to the voltage-boosting block. At the

same time, NS is pulled down toward the ground, allowing NP and NT to be boosted below the ground by capacitive coupling through CBOOT . As shown in Fig. 2(b), NP temporally reaches 250 mV and settles at around 200 mV by the boosting action. Then, the gatesource voltages of MN1 and transistors that are on in the logic tree are enlarged, resulting in an increased driving strength of these transistors. Moreover, a slightly forward sourcebody voltage established in these transistors by boosting source voltages below the ground leads to a reduction in threshold voltages of these transistors, further increasing their driving strength. In turn, the boosted voltage at NT is then transferred to P or PB through the logic tree, depending on input data. [In Fig. 2(b), input data are such that PB is pulled down below the ground.] Then, the gatesource voltage of the driver pMOS transistor is also enlarged, enhancing its driving strength. All these driving strength-enhancing effects by boosting are combined together along the timing-critical signal paths from the inputs to the outputs via precharge nodes, resulting in signicantly improved switching speed at a low-voltage region. III. S IMULATION C OMPARISON To assess the performance of the proposed circuit technique, various multi-input logic gates are designed using the conventional and proposed logic styles in a 0.18-m CMOS process. The nominal threshold voltages of p- and n-channel MOS transistors are 0.45 and 0.42 V, respectively. The boosting capacitor was implemented using the gate-oxide capacitance of a pMOS transistor. Transistor widths in each logic gate and the amount of boosting capacitance were individually optimized at each supply voltage for each logic style to provide a minimum energydelay product (EDP). Fig. 3 shows the resulting optimal boosting capacitance and the associated boosted voltage of a two-input XOR/XNOR BCDL gate for supply voltage ranging from 0.4 to 1.2 V. As shown in Fig. 3, a relatively constant boosted voltage around 200 mV was found to be optimal since it results in a minimum EDP with a good tradeoff between switching speed and noise margin. For a shallower boosted voltage, noise margin becomes better, but speed enhancement is not enough due to insufcient bootstrapping. For a deeper boosted voltage, speed becomes better, but noise margin is degraded, and energy efciency becomes worse due to an increase in leakage. The size of the boosting capacitor then to generate the optimal boosted voltage

KIM et al.: CMOS DIFFERENTIAL LOGIC STYLE WITH SUPPLY VOLTAGE APPROACHING DEVICE THRESHOLD

175

Fig. 5. Simulated comparison of XOR/XNOR gates. (a) Delay versus fan-in number. (b) Delay versus load capacitance.

Fig. 4. Simulated comparison of XOR/XNOR gates. (a) Delay versus supply. (b) Energy versus supply. (c) EDP versus supply.

increases as the supply voltage is lowered, as indicated in Fig. 3, since a larger-sized capacitor is required to get the same boosted voltage from a lower supply. Fig. 4 compares the propagation delay, energy consumption, and EDP of various two-input XOR/XNOR gates with 40-fF load capacitance at each output by varying the supply voltage from 0.4 to 1.2 V. For the static CMOS gate, the inverting (XNOR) output was obtained by an inverter from the noninverting (XOR) output. Domino CMOS and BDL are singleended logic styles; therefore, for these logic gates, only the non-inverting outputs are available. (Inverting outputs of these logic gates having a one-to-zero transition cannot be used due to the well-known constraint on outputs [5], [6].) For the BCDL gate, the optimal boosting capacitor sizes depicted in Fig. 3

were used. As shown in Fig. 4(a), the conventional nonboosted logic gates, such as static CMOS, domino CMOS, and DCVS, have an increasing delay as the supply voltage approaches the device threshold. The BDL gate, although better than other conventional logic gates, provides not so much improvement on delay at low supply voltages due to increasing latency of bootstrapping circuit. Meanwhile, the proposed BCDL gate has a signicantly reduced propagation delay compared with the static CMOS, domino CMOS, DCVS, and BDL gates, providing up to 89%, 82%, 83%, and 79% improvements, respectively. As for energy consumption depicted in Fig. 4(b), the BDL gate shows the worst performance. The BCDL gate, showing the lowest energy consumption above 0.9-V supply, becomes worse than the conventional logic gates, except for BDL under 0.5-V supply. This is attributed to the fact that a larger optimum-sized boosting capacitor was used at lower supply voltages, resulting in increased energy consumption for boosting operation. As shown in Fig. 4(c), where EDP performance is compared, the proposed BCDL gate is superior to conventional logic gates. Numerically, the BCDL gate provides up to 86%, 74%, 81%, and 86% improvements on EDP, as compared with static CMOS, domino CMOS, DCVS, and BDL gates at 0.4-V supply, respectively. The minimum EDP of the BCDL gate occurring at around 0.6 V is reduced by up to 60%, as compared with those of conventional logic gates occurring at higher supply voltages. Fig. 5 shows the propagation delay of XOR/XNOR gates depending on fan-in number and load capacitance at a supply

176

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMSII: EXPRESS BRIEFS, VOL. 59, NO. 3, MARCH 2012

TABLE I S IMULATED D ELAY, E NERGY, AND EDP OF L OGIC G ATES

Fig. 7.

Structure of an 8-bit ripple carry chain in a 64-bit BCDL adder.

voltage of 0.5 V. As shown in Fig. 5(a), BCDL gates provide up to an 84% improvement for the fan-in number ranging from 2 to 6, as compared with conventional logic gates. Fig. 5(b) shows the propagation delay of the logic gates versus load capacitance where the load capacitance ranges from 20 to 100 fF, where BCDL gates provide up to an 80% improvement. These results indicate that BCDL retains the advantage in terms of speed for increased logic complexity and load capacitance. Table I summarizes the simulated performance of various logic gates designed with the conventional and proposed logic styles. The simulation was executed at 100-MHz frequency with 0.5-V supply. The propagation delay was measured at the worst case with 40-fF load capacitance. Clocking energy was also included in the measurement. As before, for singleended logic styles, such as domino CMOS and BDL, only the non-inverting outputs are available. For AND/NAND and OR/ NOR gates having the same input counts designed with differential logic styles, the numerical data are all the same since the structures of the logic gates are exactly identical to each other. For all the logic gate types, the delay of BCDL gates is smaller than those of conventional gates, showing up to an 81% improvement. Although BCDL gates has larger energy than domino CMOS and DCVS gates due to the extra circuit to perform the boosting operation, it consumes still less energy than BDL gates. As for EDP, BCDL gates show the best performance, achieving up to an 85% improvement over the conventional logic gates. IV. E XPERIMENTAL R ESULT To demonstrate practical applicability of the proposed logic style, a set of 64-bit adders were designed, whose overall block diagram is shown in Fig. 6. The 64-bit adder consisting of eight 8-bit adder subsections adopts the carry selection scheme for high-speed carry propagation. An 8-bit ripple carry chain was used in the BCDL adder to allow boosting operation at each

Fig. 8.

Addition time of 64-bit adders.

carry chain stage, whereas an 8-bit Manchester carry chain was used in the DCVS and BDL adders for high-speed carry propagation. Fig. 7 shows the structure of the 8-bit ripple carry chain used in the 64-bit BCDL adder. At 0.5-V supply voltage, the 8-bit carry chain in the BCDL adder requires 2.13 ns for propagating a carry value from the lowest to the highest bit positions, whereas the 8-bit carry chains in the DCVS and BDL adders require 8.95 and 7.49 ns, respectively, indicating 76% and 72% improvements. As shown in Fig. 6, the outgoing carry from each 8-bit subsection goes into block-carry generators (BCG). There is a pair of BCGs in each 8-bit subsection in the upper half of the adder, and block carries are selected using the carry bit propagated from the lower half. Fig. 8 compares the simulated addition times of the adders. The 64-bit BCDL adder achieves 4.69 ns at 0.5-V supply. It indicates 75% and 71% improvements, as compared with the 64-bit DCVS and BDL adders having 18.74 and 16.41 ns, respectively. The layout picture of the 64-bit BCDL adder occupying 1.39 0.39 mm2 is shown in Fig. 9(a) (64-bit DCVS and BDL adders occupy 1.16 0.41 and 1.61 1.41 mm2 , respectively). Measured waveforms are also shown in Fig. 9(b), indicating that the propagation delay from C0 to C64 is around 4.8 ns, which matches well with the simulation result in Fig. 8. The measured propagation delay and switching energy of the BCDL adder depending on supply voltage are summarized in Table II.

KIM et al.: CMOS DIFFERENTIAL LOGIC STYLE WITH SUPPLY VOLTAGE APPROACHING DEVICE THRESHOLD

177

Fig. 6.

Block diagram of a set of 64-bit BCDL adders.

logic styles at supply voltage ranging from 0.4 to 1.2 V. The experimental result for a 64-bit BCDL adder designed with the proposed logic style revealed an addition time of 4.8 ns at 0.5 V with 31 pJ at 100 MHz.

ACKNOWLEDGMENT Design tools and IC fabrication were supported by the IC Design Education Center, Korean Advanced Institute of Science and Technology. R EFERENCES

[1] M. Pedram and J. M. Rabaey, Power-Aware Design Methodologies. Boston, MA: Kluwer, 2002. [2] A. Wang and A. Chandrakasan, A 180 mV FFT processor using subthreshold circuit techniques, in Proc. IEEE ISSCC, 2004, pp. 292295. [3] B. Zhai, L. Nazhandali, J. Olson, A. Reeves, M. Minuth, R. Helfand, P. Sanjay, D. Blaauw, and T. Austin, A 2.60 pJ/Inst subthreshold sensor processor for optimal energy efciency, in Proc. IEEE VLSI Symp., 2006, pp. 154155. [4] D. Bol, D. Flandre, and J.-D. Legat, Technology avor selection and adaptive techniques for timing-constrained 45 nm subthreshold circuits, in Proc. ACM ISLPED, 2009, pp. 2126. [5] L. G. Heller, W. Grifn, J. Davis, and N. Thoma, Cascode voltage switch logic: A differential CMOS logic family, in Proc. IEEE ISSCC Dig. Tech. Papers, Feb. 1984, pp. 1617. [6] R. H. Krambeck, C. M. Lee, and H.-F. S. Law, High-speed compact circuits with CMOS, IEEE J. Solid-State Circuits, vol. SSC-17, no. 3, pp. 614619, Jun. 1982. [7] J. H. Lou and J. B Kuo, A 1.5V full-swing bootstrapped CMOS large capacitive-load driver circuit suitable for low-voltage CMOS VLSI, IEEE J. Solid-State Circuits, vol. 32, no. 1, pp. 119121, Jan. 1997. [8] J. H. Lou and J. B. Kuo, A 1.5-V CMOS all-N-logic true-single-phase bootstrapped dynamic-logic circuit suitable for low supply voltage and high-speed pipelined system operation, IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 46, no. 5, pp. 628631, May 1999. [9] J. Garcia, J. A. Montiel-Nelson, and S. Nooshabadi, A single-capacitor bootstrapped power-efcient CMOS driver, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 53, no. 9, pp. 877881, Sep. 2006. [10] J.-W. Kim and B.-S. Kong, Low-voltage bootstrapped CMOS drivers with efcient conditional bootstrapping, IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 55, no. 6, pp. 556560, Jun. 2008.

Fig. 9. (a) Layout picture and (b) measured waveforms of a 64-bit BCDL adder. TABLE II M EASURED D ELAY AND E NERGY OF A 64-B IT BCDL A DDER

V. C ONCLUSION In this brief, a novel CMOS differential logic style with voltage boosting has been described. The BCDL provides higher switching speed than the conventional logic style at low supply voltage. The BCDL also minimizes area overhead by allowing a single boosting circuit to be shared by complementary outputs. Comparison results in a 0.180-m CMOS process indicated that the energydelay product of the proposed logic style was improved by up to 86% compared with conventional

You might also like

- MB Manual A520i-Ac e 1401 PDFDocument42 pagesMB Manual A520i-Ac e 1401 PDFPatrick OlaliaNo ratings yet

- Cigre Tf21-05id44ver24Document10 pagesCigre Tf21-05id44ver24salekojic5332No ratings yet

- Analysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologyDocument11 pagesAnalysis, Design, and Implementation of A High-Efficiency Full-Wave Rectifier in Standard CMOS TechnologymohsinmanzoorNo ratings yet

- Power Efficient Binary To XS3 Converter PDFDocument6 pagesPower Efficient Binary To XS3 Converter PDFvishal malik 215No ratings yet

- Op Amp PaperDocument6 pagesOp Amp PaperSrinivasu IrlapatiNo ratings yet

- A Low-Power and High-Speed Voltage Level Shifter Based On A Regulated Cross-Coupled Pull-Up NetworkDocument5 pagesA Low-Power and High-Speed Voltage Level Shifter Based On A Regulated Cross-Coupled Pull-Up Network15022000rskushalNo ratings yet

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersDocument4 pagesA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyNo ratings yet

- CMOS Low-Power Analog Circuit DesignDocument55 pagesCMOS Low-Power Analog Circuit DesignRajesh_Nagaraj_9325No ratings yet

- Dheeraj ReportDocument15 pagesDheeraj ReportGirdhar Gopal GautamNo ratings yet

- Speed-Power-Accuracy TradeoffDocument8 pagesSpeed-Power-Accuracy TradeoffbackspaceTABNo ratings yet

- Fassio 2020Document5 pagesFassio 2020Vani YamaniNo ratings yet

- Bandwidth Enhacement by Inductor + Current FeedbackDocument14 pagesBandwidth Enhacement by Inductor + Current FeedbackSumant AroraNo ratings yet

- Cmos Fuladers (Pass Transistors) PDFDocument6 pagesCmos Fuladers (Pass Transistors) PDFswathiNo ratings yet

- Evaluation of Modern MOSFET Models For Bulk-Driven ApplicationsDocument4 pagesEvaluation of Modern MOSFET Models For Bulk-Driven Applications1zxcNo ratings yet

- Double Tail Dynamic CompDocument10 pagesDouble Tail Dynamic CompBhura AnushaNo ratings yet

- Final ProjectDocument5 pagesFinal Projectnksharma.naveen1855No ratings yet

- Subthreshold Source-Coupled Logic Circuits For Ultra-Low-Power ApplicationsDocument12 pagesSubthreshold Source-Coupled Logic Circuits For Ultra-Low-Power ApplicationsSonu SangwanNo ratings yet

- Low Power Full AdderDocument6 pagesLow Power Full Adderdurairajmary100% (1)

- Design and Simulation of RF Energy Extracting Circuits and SystemDocument28 pagesDesign and Simulation of RF Energy Extracting Circuits and SystemHaresh SinghNo ratings yet

- Minimization of Redundant Internal Voltage Swing in Cmos Full-AdderDocument4 pagesMinimization of Redundant Internal Voltage Swing in Cmos Full-AdderAnonymous JnvCyu85No ratings yet

- Low-Power Domino Circuits Using NMOS Pull-Up On Off-Critical PathsDocument6 pagesLow-Power Domino Circuits Using NMOS Pull-Up On Off-Critical PathsSurya Ganesh PenagantiNo ratings yet

- A 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyDocument4 pagesA 1.8Ghz Cmos: Low-Power Truly-Modular Programmable Divider in Standard TechnologyMuhammad_Swilam_2010No ratings yet

- Ijoer Aug 2015 19 PDFDocument7 pagesIjoer Aug 2015 19 PDFEngineering JournalNo ratings yet

- Maximum Leakage Power Estimation For CMOS CircuitsDocument9 pagesMaximum Leakage Power Estimation For CMOS Circuitsowais74No ratings yet

- A Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsDocument12 pagesA Novel Method For Analysis of Power Consumption in VLSI Global InterconnectsPranay KumarNo ratings yet

- Digital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik RoyDocument6 pagesDigital CMOS Logic Operation in The Sub-Threshold Region: Hendrawan Soeleman and Kaushik Royphanindra21No ratings yet

- 2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsDocument5 pages2007 07 A Multi-Mode Power Gating Structure For Low-Voltage Deep-Submicron CMOS ICsKuldeep SinghNo ratings yet

- High PSRR Voltage Reference Circuit With Dual-Output For Low Power ApplicationsDocument4 pagesHigh PSRR Voltage Reference Circuit With Dual-Output For Low Power Applicationsmd istiyakNo ratings yet

- 01012833, Technical PaperDocument4 pages01012833, Technical Paperindresh.vermaNo ratings yet

- Analysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyDocument7 pagesAnalysis and Optimization of Active Power and Delay of 10T Full Adder Using Power Gating Technique at 45 NM TechnologyInternational Organization of Scientific Research (IOSR)No ratings yet

- Basic Design of SCLDocument4 pagesBasic Design of SCLDunna SrinivasraoNo ratings yet

- Design of Power Efficient CMOS Based Oscillator Circuit With Varactor Tuning ControlDocument8 pagesDesign of Power Efficient CMOS Based Oscillator Circuit With Varactor Tuning ControlDEEPAK PRAJAPATINo ratings yet

- Analysis of Cmos and Mtcmos Circuits Using 250 Nano Meter TechnologyDocument11 pagesAnalysis of Cmos and Mtcmos Circuits Using 250 Nano Meter TechnologyCS & ITNo ratings yet

- ContentDocument6 pagesContentashwingeorge101No ratings yet

- Low-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationDocument4 pagesLow-Voltage CMOS Analog Bootstrapped Switch For Sample-and-Hold Circuit: Design and Chip CharacterizationwhamcNo ratings yet

- Geometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS InverterDocument4 pagesGeometric Programming Based Power-Delay Optimization Using Transistor-Sizing For Submicron and Deep Submicron CMOS Invertersuchi87No ratings yet

- Vlsi DesignDocument31 pagesVlsi Designajas777BNo ratings yet

- Analysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorDocument10 pagesAnalysis and Design of A Low-Voltage Low-Power Double-Tail ComparatorSrinivasAnchalaNo ratings yet

- The Impact of Transistor Sizing On Power Efficiency in Submicron CMOS CircuitsDocument4 pagesThe Impact of Transistor Sizing On Power Efficiency in Submicron CMOS Circuitsramu143416305No ratings yet

- Minimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueDocument7 pagesMinimization Leakage Current of Full Adder Using Deep Sub-Micron CMOS TechniqueInternational Journal of Application or Innovation in Engineering & ManagementNo ratings yet

- 05682957Document4 pages05682957Praveenkumar ViswanathanNo ratings yet

- A 93.7% Peak Efficiency DC-DC Buck Converter With All-Pass Network Based Passive Level Shifter in 55 NM CMOSDocument4 pagesA 93.7% Peak Efficiency DC-DC Buck Converter With All-Pass Network Based Passive Level Shifter in 55 NM CMOSRaghvendra DeshpandeNo ratings yet

- Welcome To International Journal of Engineering Research and Development (IJERD)Document6 pagesWelcome To International Journal of Engineering Research and Development (IJERD)IJERDNo ratings yet

- Abstract: Ultra-Low Power Phase Locked LoopsDocument4 pagesAbstract: Ultra-Low Power Phase Locked LoopsRizwan Shaik PeerlaNo ratings yet

- Domino Logic CircuitsDocument4 pagesDomino Logic CircuitsSahil BansalNo ratings yet

- A Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierDocument5 pagesA Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierMiguel BrunoNo ratings yet

- Design and Analysis of CMOS and Adiabatic 4-Bit Binary MultiplierDocument4 pagesDesign and Analysis of CMOS and Adiabatic 4-Bit Binary MultipliervaseemalikhanNo ratings yet

- A Bi-Phase MEMS Resonator ModulatorDocument3 pagesA Bi-Phase MEMS Resonator ModulatormenguemengueNo ratings yet

- Low Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingDocument4 pagesLow Power CMOS Digital Circuit Design Methodologies With Reduced Voltage SwingMaheshNo ratings yet

- Regular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI CircuitsDocument3 pagesRegular Correspondence: Compact High-Frequency Output Buffer For Testing of Analog CMOS VLSI CircuitsSaranya ChakrabortyNo ratings yet

- Techniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionDocument4 pagesTechniques For Low Power VLSI Design: A Novel Analysis of Leakage Power ReductionSaranya RamaswamyNo ratings yet

- Jlpea 10 00005 v2Document11 pagesJlpea 10 00005 v2erikboutNo ratings yet

- SurajpaperDocument79 pagesSurajpaperSooraj SattirajuNo ratings yet

- LPVLSI III UnitDocument19 pagesLPVLSI III UnitrakeshNo ratings yet

- Design and Implementation of A High Dimming Ratio LED Drive ControllerDocument6 pagesDesign and Implementation of A High Dimming Ratio LED Drive ControllerBlai VsNo ratings yet

- Robust Subthreshold Circuit Designing Using Sub-Threshold Source Coupled Logic (STSCL)Document5 pagesRobust Subthreshold Circuit Designing Using Sub-Threshold Source Coupled Logic (STSCL)Sonu SangwanNo ratings yet

- A Comparative Study Between Different Types of Adders and MultipliersDocument5 pagesA Comparative Study Between Different Types of Adders and MultipliersVivek SinghNo ratings yet

- FISAC2 200907012 - PrajwalprabhuDocument22 pagesFISAC2 200907012 - PrajwalprabhuPrajwal PrabhuNo ratings yet

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Document16 pages1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraNo ratings yet

- Power Systems-On-Chip: Practical Aspects of DesignFrom EverandPower Systems-On-Chip: Practical Aspects of DesignBruno AllardNo ratings yet

- Array MultiplierDocument2 pagesArray MultiplierjayalakshmisnairNo ratings yet

- Low Power 6-Transistor Latch Design For Portable DevicesDocument16 pagesLow Power 6-Transistor Latch Design For Portable DevicesjayalakshmisnairNo ratings yet

- Shema FirstDocument10 pagesShema FirstjayalakshmisnairNo ratings yet

- Powe Efficient PLLDocument12 pagesPowe Efficient PLLjayalakshmisnairNo ratings yet

- 97.1.2 Relationship of 1000BASE-T1 To Other StandardsDocument6 pages97.1.2 Relationship of 1000BASE-T1 To Other StandardsAbhishek BhattacharjeeNo ratings yet

- Ladder-Logic TutorialDocument3 pagesLadder-Logic TutorialShesharam ChouhanNo ratings yet

- Microprogramming - Programmable Digital Microcircuits - CERN (1982) (Motorola 68000)Document34 pagesMicroprogramming - Programmable Digital Microcircuits - CERN (1982) (Motorola 68000)Effervescent FlufferNo ratings yet

- Allen Bradley ContactorDocument20 pagesAllen Bradley ContactorWilfer Vidal VimieiroNo ratings yet

- Electrical Completion Form OccupancyDocument2 pagesElectrical Completion Form OccupancyMader rosieNo ratings yet

- Lecture8 - PIPE CABLE ELECTROMAGNETIC LOCATORDocument39 pagesLecture8 - PIPE CABLE ELECTROMAGNETIC LOCATORMuhamadSadiq100% (1)

- Air 3246Document36 pagesAir 3246Doc All TelecomNo ratings yet

- AP2400-IDU, A07 DS 1-0-2 (Indoor Router, GA)Document2 pagesAP2400-IDU, A07 DS 1-0-2 (Indoor Router, GA)hrga hrgaNo ratings yet

- Transient Simulation of Silicon Devices and CircuitsDocument16 pagesTransient Simulation of Silicon Devices and CircuitsKonstantine TsitsilonisNo ratings yet

- DLD Project Presentation Light DetectorDocument10 pagesDLD Project Presentation Light DetectorMd Mamun HossainNo ratings yet

- SoundLink RevolveDocument33 pagesSoundLink RevolveVicente FernandezNo ratings yet

- Battery Managment SystemDocument22 pagesBattery Managment SystemJuan Pablo VillegasNo ratings yet

- New Mobility Concepts: Soc Classification Level 1 © Nokia Siemens NetworksDocument54 pagesNew Mobility Concepts: Soc Classification Level 1 © Nokia Siemens NetworksTry TestNo ratings yet

- Week 1 ENA SlidesDocument56 pagesWeek 1 ENA SlidesUzair KhawajaNo ratings yet

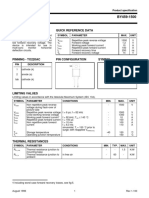

- Rectifier Diode BY459-1500 Fast, High-Voltage: General Description Quick Reference DataDocument6 pagesRectifier Diode BY459-1500 Fast, High-Voltage: General Description Quick Reference DataRusmiyanto YantoNo ratings yet

- Miller 198449 BoardDocument80 pagesMiller 198449 BoardMario Emilio Castro TineoNo ratings yet

- Components of The ComputerDocument21 pagesComponents of The Computertheresaho823No ratings yet

- FRS20DDDocument102 pagesFRS20DDgermanaolxNo ratings yet

- Retrofit BMW F10 DEC Switch For Normal Sport ModesDocument3 pagesRetrofit BMW F10 DEC Switch For Normal Sport Modesobd365No ratings yet

- DC Motor DrivesDocument26 pagesDC Motor DrivesSudhir P BhatNo ratings yet

- Digital Electronics Interview Questions PDFDocument3 pagesDigital Electronics Interview Questions PDFSanjeev100% (2)

- AFFD Clipsal Detector de ArcoDocument4 pagesAFFD Clipsal Detector de ArcoGabriel210364No ratings yet

- Data SheetDocument76 pagesData SheetjonathanNo ratings yet

- 4-20ma Signal SplitterDocument8 pages4-20ma Signal SplitterChandra SekarNo ratings yet

- Intelligent Detector Bases: FeaturesDocument3 pagesIntelligent Detector Bases: FeaturesMarcelo FradeNo ratings yet

- Catalog 12 PagesDocument12 pagesCatalog 12 PagesueksinNo ratings yet

- Mmo 68247664 1552290576 4588 968Document519 pagesMmo 68247664 1552290576 4588 968Fendy KwanNo ratings yet

- Design of Microstrip Patch Antenna For Wireless Communication DevicesDocument6 pagesDesign of Microstrip Patch Antenna For Wireless Communication Devicesekrem akarNo ratings yet