Professional Documents

Culture Documents

LSK489

LSK489

Uploaded by

tarpinoOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LSK489

LSK489

Uploaded by

tarpinoCopyright:

Available Formats

LSK489

LOW NOISE, LOW CAPACITANCE MONOLITHIC DUAL N-CHANNEL JFET

FEATURES ULTRA LOW NOISE LOW INPUT CAPACITANCE en = 1.8nV/Hz Ciss = 4pF

Features

Reduced Noise due to process improvement Monolithic Design High slew rate Low offset/drift voltage Low gate leakage lgss & lg High CMRR 102 dB

Benefits

Tight differential voltage match vs. current Improved op amp speed settling time accuracy Minimum Input Error trimming error voltage Lower intermodulation distortion

Applications

Wide band differential Amps High speed temperature compensated single ended input amplifier amps High speed comparators Impedance Converters

Description

The LSK 489 series of high performance monolithic dual JFETs features extremely low noise, tight offset voltage and low drift over temperature specifications, and is targeted for use in a wide range or precision instrumentation applications. This series has a wide selection of offset and drift specifications. The SST series SO-8 package provided ease of manufacturing and the symmetrical pinout prevents improper orientation. The SO-8 package is available with tape and reel options for compatibility with automatic assembly methods. (See packaging data)

ABSOLUTE MAXIMUM RATINGS @ 25 C (unless otherwise stated) Maximum Temperatures Storage Temperature Junction Operating Temperature

SOIC-A -55 to +150C -55 to +150C

4

TO-71 TOP VIEW

Maximum Power Dissipation, TA = 25C Continuous Power Dissipation, per side Power Dissipation, total Maximum Currents Gate Forward Current Maximum Voltages Gate to Source Gate to Drain VGSO = 60V VGDO = 60V IG(F) = 10mA

5

300mW 500mW SOT-23 TOP VIEW

* For equivalent single version, see LSK186

Linear Integrated Systems

4042 Clipper Court Fremont, CA 94538 Tel: 510 490-9160 Fax: 510 353-0261

Doc 201151 06/18/2013 Rev#A28 ECN# LSK489

MATCHING CHARACTERISTICS @ 25C (unless otherwise stated) SYMBOL

VGS1 VGS2

IDSS1 IDSS2

CHARACTERISTIC Differential Gate to Source Cutoff Voltage Gate to Source Saturation Current Ratio COMMON MODE REJECTION RATIO -20 logVGS1-2/VDS

MIN

TYP

MAX 20

UNITS

mV

CONDITIONS VDS = 10V, ID = 1mA VDS = 10V, VGS = 0V

0.9 95 102

1.0 dB

CMRR

VDS = 10V to 20V, ID = 200A

SYMBOL en en CISS CRSS

CHARACTERISTIC Noise Voltage Noise Voltage Common Source Input Capacitance Common Source Reverse Transfer Capacitance

MIN

TYP 1.8 2.8 4

MAX 2.0 3.5 8 3

UNITS nV/Hz nV/Hz pF pF

CONDITIONS VDS = 15V, ID = 2.0mA, f = 1kHz, NBW = 1Hz VDS = 15V, ID = 2.0mA, f = 10Hz, NBW = 1Hz VDS = 15V, ID = 500A, f = 1MHz

ELECTRICAL CHARACTERISTICS @ 25C (unless otherwise stated) SYMBOL BVGSS V(BR)G1 - G2 VGS(OFF) VGS IDSS IG IGSS Gfs Gfs GOS GOS NF

2

CHARACTERISTIC Gate to Source Breakdown Voltage Gate to Gate Breakdown Voltage Gate to Source Pinch-off Voltage Gate to Source Operating Voltage Drain to Source Saturation Current Gate Operating Current Gate to Source Leakage Current Full Conductance Transconductance Transconductance Full Output Conductance Output Conductance Noise Figure

MIN -60 30 -1.5 -0.5 2.5

TYP 45

MAX

UNITS V V

CONDITIONS VDS = 0, ID = -1nA IG= 1A, ID=IS=0 A (Open Circuit) VDS = 15V, ID = 1nA VDS = 15V, ID = 500A VDG = 15V, VGS = 0 VDG = 15V, ID = 200A TA = 125C VDG = -15V, VDS = 0 VDG = 15V, VGS = 0, f = 1kHz VDG = 15V, ID = 500A VDG = 15V, VGS = 0 VDG = 15V, ID = 200A VDS = 15V, VGS = 0, RG = 10M, f = 100Hz, NBW = 6Hz

-3.5 -3.5 5 -2 -0.8 15 -25 -10 -100

V V mA pA nA pA S S

1500 1000 1500 40 1.8 2.7 0.5

S S dB

Linear Integrated Systems

4042 Clipper Court Fremont, CA 94538 Tel: 510 490-9160 Fax: 510 353-0261

Doc 201151 06/18/2013 Rev#A28 ECN# LSK489

PACKAGE DIMENSIONS

SOT-23

Six Lead

0.95

1

1.90

6

5

0.35 0.50

2.80 3.00

0.210 0.170

3

1.50 1.75 2.60 3.00

0.90 1.30

0.09 0.20

0.00 0.15

0.10 0.60 DIMENSIONS IN MILLIMETERS

DIMENSIONS IN INCHES

All dimensions in inches.

1. Absolute maximum ratings are limiting values above which serviceability may be impaired. 2. Pulse width 2ms. 3. All MIN/TYP/MAX Limits are absolute values. Negative signs indicate electrical polarity only. 4. Derate 2.4 mW/C above 25C. 5. Derate 4 mW/C above 25C. Information furnished by Linear Integrated Systems is believed to be accurate and reliable. However, no responsibility is assumed for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Linear Integrated Systems.

Linear Integrated Systems

4042 Clipper Court Fremont, CA 94538 Tel: 510 490-9160 Fax: 510 353-0261

Doc 201151 06/18/2013 Rev#A28 ECN# LSK489

Typical Characteristics

Linear Integrated Systems

4042 Clipper Court Fremont, CA 94538 Tel: 510 490-9160 Fax: 510 353-0261

Doc 201151 06/18/2013 Rev#A28 ECN# LSK489

Typical Characteristics (Contd)

Linear Integrated Systems

4042 Clipper Court Fremont, CA 94538 Tel: 510 490-9160 Fax: 510 353-0261

Doc 201151 06/18/2013 Rev#A28 ECN# LSK489

Typical Characteristics (Contd)

Linear Integrated Systems (LIS) is a 25-year-old, third-generation precision semiconductor company providing high-quality discrete components. Expertise brought to LIS is based on processes and products developed at Amelco, Union Carbide, Intersil and Micro Power Systems by company President John H. Hall. Hall, a protg of Silicon Valley legend Dr. Jean Hoerni, was the director of IC Development at Union Carbide, co-founder and vice president of R&D at Intersil, and founder/president of Micro Power Systems.

Linear Integrated Systems

4042 Clipper Court Fremont, CA 94538 Tel: 510 490-9160 Fax: 510 353-0261

Doc 201151 06/18/2013 Rev#A28 ECN# LSK489

You might also like

- Motorola RF Device DatabookDocument1,182 pagesMotorola RF Device Databooktarpino100% (1)

- Mta Series 980 Service ManualDocument130 pagesMta Series 980 Service ManualtarpinoNo ratings yet

- Prathama Solarconnect Energy Private Limited: Short Circuit Study ReportDocument18 pagesPrathama Solarconnect Energy Private Limited: Short Circuit Study Reportramesh cuppuNo ratings yet

- 3BSE020924R5021 CIO ModulesTUsDocument600 pages3BSE020924R5021 CIO ModulesTUsDiego Carlos GarciaNo ratings yet

- Foot Step Power GenerationDocument32 pagesFoot Step Power GenerationCUBE Engineering SolutionsNo ratings yet

- 9-0-9 Step Down TransformerDocument20 pages9-0-9 Step Down TransformerSarthak JoshiNo ratings yet

- Ad 847Document12 pagesAd 847SaadAhmedBeihaqiNo ratings yet

- Features Description: D D D D D D D D D D D DDocument16 pagesFeatures Description: D D D D D D D D D D D D1eugen1No ratings yet

- 10.709 Gbps Laser Diode Driver Chipset: A To 1200 ADocument12 pages10.709 Gbps Laser Diode Driver Chipset: A To 1200 ABanyugeaNo ratings yet

- Complete Dual 18-Bit 16 Audio DAC AD1865 : Oversampling Per Channel 5 Volt OperationDocument13 pagesComplete Dual 18-Bit 16 Audio DAC AD1865 : Oversampling Per Channel 5 Volt OperationDarek BratnyNo ratings yet

- LC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778Document12 pagesLC Mos, High Speed 1-, 4-& 8-Channel 10-Bit Adcs Ad7776/Ad7777/Ad7778tarpinoNo ratings yet

- Triple Differential Driver With Sync-On-Common-Mode AD8134: Features Functional Block DiagramDocument20 pagesTriple Differential Driver With Sync-On-Common-Mode AD8134: Features Functional Block DiagramSerkan şahinNo ratings yet

- Ad 630Document13 pagesAd 630Antonio PerezNo ratings yet

- Datasheet - IRF540Document9 pagesDatasheet - IRF540THiz OCtavvNo ratings yet

- LC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Document8 pagesLC MOS Precision Quad SPST Switches ADG411/ADG412/ADG413: 615 V Analog Signal Range V) MW)Fer TgNo ratings yet

- Rclamp 7535 MDocument9 pagesRclamp 7535 MAlan jorgeNo ratings yet

- Ca3306 (A, C)Document17 pagesCa3306 (A, C)notaden1849No ratings yet

- PCM3002 PCM3003: Features DescriptionDocument24 pagesPCM3002 PCM3003: Features DescriptionAishwarya VasudevenNo ratings yet

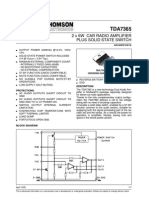

- 2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionDocument8 pages2 X 6W Car Radio Amplifier Plus Solid State Switch: Protections DescriptionMiloud ChouguiNo ratings yet

- Iso122sensor de TensionDocument15 pagesIso122sensor de TensionRichard ZerpaNo ratings yet

- Fet 60NF06Document9 pagesFet 60NF06Anh Nguyễn HoàngNo ratings yet

- Adxl 278Document12 pagesAdxl 278Dav1t1No ratings yet

- OP37Document16 pagesOP37Josef StevanusNo ratings yet

- Micropower, Single-Supply, Cmos: Ina321 Ina2321Document23 pagesMicropower, Single-Supply, Cmos: Ina321 Ina2321James LivingstonNo ratings yet

- Low Noise, Low Gain Drift, G 2000 Instrumentation AmplifierDocument20 pagesLow Noise, Low Gain Drift, G 2000 Instrumentation AmplifiervabecompNo ratings yet

- PA2756GR: Mos Field Effect TransistorDocument7 pagesPA2756GR: Mos Field Effect TransistorRjibNo ratings yet

- Datasheet 53315Document30 pagesDatasheet 53315Bladimir AngamarcaNo ratings yet

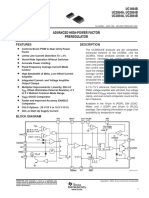

- Features Description: LTC3864 60V Low I Step-Down DC/DC Controller With 100% Duty Cycle CapabilityDocument28 pagesFeatures Description: LTC3864 60V Low I Step-Down DC/DC Controller With 100% Duty Cycle CapabilityDolly Arthur SiregarNo ratings yet

- Ls 5912Document2 pagesLs 5912Milorad RumenicNo ratings yet

- +2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsDocument20 pages+2.7 V To +5.5 V, 350 KSPS, 10-Bit 4-/8-Channel Sampling AdcsAbhishek ChaudharyNo ratings yet

- LC MOS 8-Channel, 12-Bit High Speed Data Acquisition System: S Conversion TimeDocument20 pagesLC MOS 8-Channel, 12-Bit High Speed Data Acquisition System: S Conversion Timeharsh.nsit2007752No ratings yet

- Obsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)Document8 pagesObsolete Product(s) - Obsolete Product(s) Obsolete Product(s) - Obsolete Product(s)bagaswaraarieNo ratings yet

- DAC0808 DatasheetDocument12 pagesDAC0808 DatasheetRicky CoxNo ratings yet

- Altivar ATV61HU55N4 CatalogueDocument4 pagesAltivar ATV61HU55N4 CatalogueEugen Marius BadescuNo ratings yet

- AD780Document10 pagesAD780game___overNo ratings yet

- Features Description: Lt3763 60V High Current Step-Down Led Driver ControllerDocument30 pagesFeatures Description: Lt3763 60V High Current Step-Down Led Driver Controllerjinxy06No ratings yet

- IRF520Document8 pagesIRF520Anhell AzolNo ratings yet

- Iso 122Document18 pagesIso 122rnjlmv83100% (1)

- Four-Channel, Simultaneous Sampling, Fast, 14-Bit ADCDocument19 pagesFour-Channel, Simultaneous Sampling, Fast, 14-Bit ADCsaiprathimaNo ratings yet

- LT 1248 FDDocument12 pagesLT 1248 FDAtiqurrehman UmairNo ratings yet

- AD7533Document12 pagesAD7533Jose David Medina MartinezNo ratings yet

- Allegro ACS 709Document17 pagesAllegro ACS 709David ZammitNo ratings yet

- ATV61HD30N4Document4 pagesATV61HD30N4BlAdE 12No ratings yet

- RCB600 :: ROAL Living EnergyDocument10 pagesRCB600 :: ROAL Living EnergyroalscribdNo ratings yet

- Ad 844Document12 pagesAd 844Marciel DervansokiNo ratings yet

- ADP3180Document20 pagesADP3180chrizzcloNo ratings yet

- LC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828Document16 pagesLC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828meroka2000No ratings yet

- ACS712 DatasheetDocument15 pagesACS712 DatasheetHernan PorriniNo ratings yet

- STD17NF03Document9 pagesSTD17NF03VeronicaNo ratings yet

- LandisGyr ZXG300 TechData EN1Document6 pagesLandisGyr ZXG300 TechData EN1Atok Lukmanul KhakimNo ratings yet

- ATV71HC20N4 DocumentDocument8 pagesATV71HC20N4 DocumentToth VasileNo ratings yet

- ST3232 Data SheetDocument12 pagesST3232 Data SheetcredioNo ratings yet

- N-Channel Dual JFET: CorporationDocument2 pagesN-Channel Dual JFET: CorporationtarpinoNo ratings yet

- 4MSPS, 24-Bit Analog-to-Digital Converter: Features DescriptionDocument37 pages4MSPS, 24-Bit Analog-to-Digital Converter: Features DescriptionEric ChenNo ratings yet

- Ad848 9Document8 pagesAd848 9samNo ratings yet

- Ad 421Document14 pagesAd 421Vishal Devrao JadhavNo ratings yet

- ACS714Document15 pagesACS714connect2nsNo ratings yet

- Ad1864n KDocument13 pagesAd1864n KmrtuktukNo ratings yet

- Ad8421 PDFDocument28 pagesAd8421 PDFsoft4gsmNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- High-Performance D/A-Converters: Application to Digital TransceiversFrom EverandHigh-Performance D/A-Converters: Application to Digital TransceiversNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)

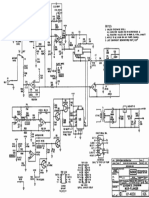

- Kikusui 418B Service ManualDocument15 pagesKikusui 418B Service Manualtarpino100% (2)

- MXR Distortion + SchematicDocument1 pageMXR Distortion + SchematictarpinoNo ratings yet

- MXR Flanger Factory SchematicDocument1 pageMXR Flanger Factory SchematictarpinoNo ratings yet

- Low Noise Analog MEMS Microphone and PreampDocument5 pagesLow Noise Analog MEMS Microphone and PreamptarpinoNo ratings yet

- Dod 250 SchematicDocument1 pageDod 250 SchematictarpinoNo ratings yet

- This Datasheet Has Been Downloaded From at ThisDocument2 pagesThis Datasheet Has Been Downloaded From at ThistarpinoNo ratings yet

- MXR Dyna Comp Factory SchematicDocument1 pageMXR Dyna Comp Factory SchematictarpinoNo ratings yet

- Silver Fox Octaver PCBDocument1 pageSilver Fox Octaver PCBtarpinoNo ratings yet

- Genelec S30 Service ManualDocument13 pagesGenelec S30 Service Manualtarpino100% (1)

- Subminiature Relays Type ESH Monostable: Ordering Key ESH B 001 12 Product DescriptionDocument2 pagesSubminiature Relays Type ESH Monostable: Ordering Key ESH B 001 12 Product DescriptiontarpinoNo ratings yet

- 2N4416Document2 pages2N4416tarpinoNo ratings yet

- ADP3338 Data SheetsDocument16 pagesADP3338 Data SheetstarpinoNo ratings yet

- This Datasheet Has Been Downloaded From at ThisDocument2 pagesThis Datasheet Has Been Downloaded From at ThistarpinoNo ratings yet

- This Datasheet Has Been Downloaded From at ThisDocument8 pagesThis Datasheet Has Been Downloaded From at ThistarpinoNo ratings yet

- This Datasheet Has Been Downloaded From at ThisDocument2 pagesThis Datasheet Has Been Downloaded From at ThistarpinoNo ratings yet

- SP791 Data SheetsDocument19 pagesSP791 Data SheetstarpinoNo ratings yet

- VCR11NDocument1 pageVCR11NtarpinoNo ratings yet

- WL005 - WL10: Silicon Bridge Rectifiers WOBDocument3 pagesWL005 - WL10: Silicon Bridge Rectifiers WOBtarpinoNo ratings yet

- SR502 - SR506: High Current Schottky Barrier Rectifier FeaturesDocument2 pagesSR502 - SR506: High Current Schottky Barrier Rectifier FeaturestarpinoNo ratings yet

- 456 22651 0 BDW83CDocument4 pages456 22651 0 BDW83CtarpinoNo ratings yet

- Ultra Low V 0.52 V at I 5 A: Vishay General SemiconductorDocument4 pagesUltra Low V 0.52 V at I 5 A: Vishay General SemiconductortarpinoNo ratings yet

- PN2222ADocument8 pagesPN2222AtarpinoNo ratings yet

- Opa 134 DatasheetDocument19 pagesOpa 134 DatasheetNikos SpirouNo ratings yet

- TM1 RM1Document16 pagesTM1 RM1Nikulas HawlaNo ratings yet

- Basis Stator Earth Fault ProtectionDocument18 pagesBasis Stator Earth Fault ProtectionNguyen Xuan TungNo ratings yet

- Ex No: 1 DateDocument4 pagesEx No: 1 DateVignesh AadhiNo ratings yet

- Chapter 1 - ADocument23 pagesChapter 1 - AAHMAD ASRI ABD SAMATNo ratings yet

- T.L.E 7 and 8 Week 5Document15 pagesT.L.E 7 and 8 Week 5Eleonor DistrajoNo ratings yet

- Yamaha MCR-840 Service ManualDocument84 pagesYamaha MCR-840 Service ManualHadi Nur LettoNo ratings yet

- Ansi Relay FunctionsDocument1 pageAnsi Relay FunctionsJitendra PatilNo ratings yet

- Trafo Erection and MAINTENANCEDocument23 pagesTrafo Erection and MAINTENANCEgm29No ratings yet

- BTL-ID Physio Pricelist 2017 v100Document9 pagesBTL-ID Physio Pricelist 2017 v100Immanuel PanjiNo ratings yet

- Yuasa NPL Range: VRLA BatteriesDocument2 pagesYuasa NPL Range: VRLA BatteriesVuro BegaNo ratings yet

- Advance Communication System Lectures Part 1Document36 pagesAdvance Communication System Lectures Part 1Shahzad Khalid ChNo ratings yet

- L&T Switchboards Tested For ASTA Certification (Jan - Mar 03)Document4 pagesL&T Switchboards Tested For ASTA Certification (Jan - Mar 03)santhoshNo ratings yet

- Zener Diode AppliationsDocument19 pagesZener Diode AppliationsKartik GuptaNo ratings yet

- Ac NeetDocument36 pagesAc NeetDeepNo ratings yet

- Mbus 2Document8 pagesMbus 2jhaNo ratings yet

- The Ideal Diode Equation LessonDocument2 pagesThe Ideal Diode Equation LessonsamiNo ratings yet

- Installation and Service InstructionsDocument8 pagesInstallation and Service Instructionsrommel duranNo ratings yet

- TECHNICAL INFORMATION FTL8x PDFDocument32 pagesTECHNICAL INFORMATION FTL8x PDFhamr01No ratings yet

- A Review in Solar Powered Auto IrrigationDocument2 pagesA Review in Solar Powered Auto IrrigationAnjo PepitoNo ratings yet

- Gujarat Technological University: InstructionsDocument3 pagesGujarat Technological University: InstructionsParshwa ConsultancyNo ratings yet

- WST 2100 Pbach R Me 0042Document206 pagesWST 2100 Pbach R Me 0042teamlc100% (1)

- New Microsoft Word DocumentDocument2 pagesNew Microsoft Word DocumentraviNo ratings yet

- MICRF102: General DescriptionDocument12 pagesMICRF102: General Descriptionzbhp zNo ratings yet

- Cotech EMT707CTL Energy Meter - Priza ProgramabilaDocument5 pagesCotech EMT707CTL Energy Meter - Priza ProgramabilaConstantinNo ratings yet

- Tracer AN Series: EpeverDocument3 pagesTracer AN Series: EpevertalibanindonesiaNo ratings yet

- MFJ Super Hi-Q Loop AntennaDocument16 pagesMFJ Super Hi-Q Loop Antennaag1tatorNo ratings yet